# Amorphous Transition-Metal-Oxides for Transparent Flexible Displays: Device Fabrication and Characterization

by

## Alireza Tari

A thesis

presented to the University of Waterloo

in fulfillment of the

thesis requirement for the degree of

Doctor of Philosophy

in

Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2016

© Alireza Tari 2016

# **Author's Declaration**

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

### **Abstract**

This Ph.D. dissertation presents the development and demonstration of optically transparent back-channel etched flexible InGaZnO (IGZO) thin-film transistors (TFTs) using a conventional TFT process flow implemented at low-temperatures. The study includes the development of the transition metal oxide (TMO) channel layers by relating the materials properties, surface topography, and chemical composition of the channel layer to the process integration of IGZO TFTs. Investigation of the process parameters included process temperature and post processing thermal-anneal on the electronic properties of the semiconductor and the effect of the chemical composition of the gate-dielectric layer on the active channel layer of TMO TFTs.

A bi-layer  $SiO_x/SiN_x$  gate dielectric was found to be an effective structure for high-performance IGZO-based TFTs compared to single dielectric layers. The  $SiO_x$  capping layer within the dual dielectric structure was found to be an effective hydrogen (H) diffusion barrier, preventing H contamination into the overlying semiconducting IGZO layer during the IGZO deposition, minimizing the generation of H induce oxygen vacancy (V<sub>o</sub>) formation in the active IGZO channel. A low-temperature, 150°C plasma-enhanced chemical vapor deposition (PECVD) process was used to produce TFTs having field-effect mobility,  $\mu$ , of 5.7 cm<sup>2</sup>/V.sec, sub-threshold swing, S.S., of 0.54 V/decade, and  $I_{on/off} > 10^6$ .

The same dual-dielectric stack was also found to be an effective passivation layer for back-channel etched IGZO TFTs. A low-temperature approach employing a thin room-temperature-deposited e-beam  $SiO_x$  barrier layer directly deposited onto the IGZO back-channel to prevent both the plasma damage and unintentional hydrogen (H) doping of the IGZO channel region.

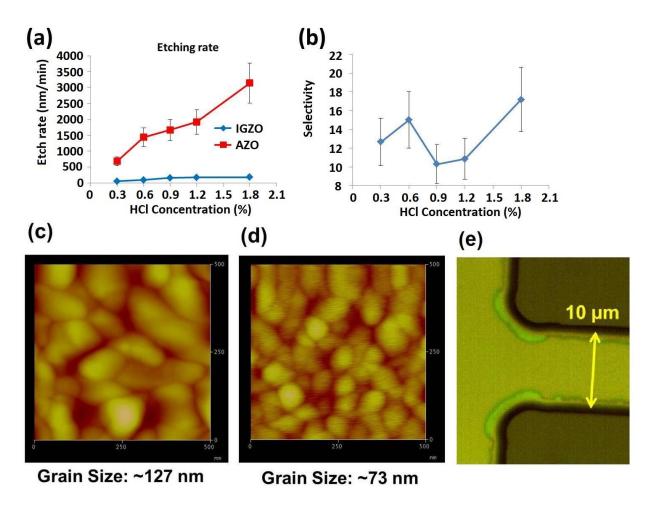

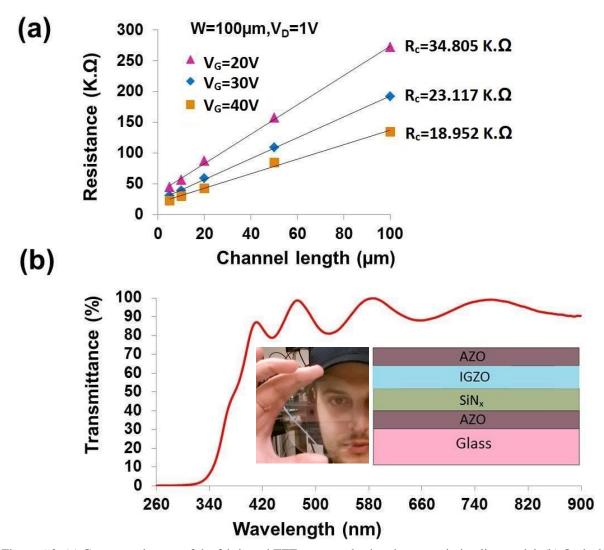

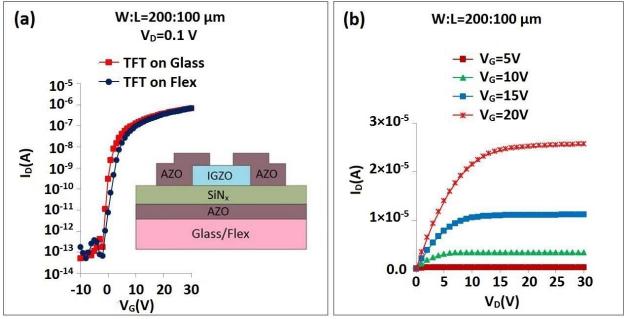

In order to complete the process integration for fully transparent flexible TFTs, the development of the dielectric layers of the TFT structure were augmented by an investigation of ohmic transparent contacts patterned using selective wet-chemical etching. A high-selectivity wetetch patterning process was developed to take advantage of the etch-rate differences between polycrystalline Al-doped ZnO (AZO) and amorphous (IGZO) TMO thin-films. This patterning technique resulted in the fabrication of back-channel etched flexible transparent IGZO TFTs using a conventional TFT process flow implemented at low-temperatures. A selectivity of nearly 20 was found for dilute HCl solution in water for patterning AZO source/drain electrodes on IGZO channel layers. The resulting patterned electrodes had a low contact resistance of < 19 K $\Omega$  and

high optical transparency of ~85%. The transparent back-channel etched flexible IGZO TFTs exhibited a  $\mu$  of ~9.3 cm<sup>2</sup>/V.sec, V<sub>T</sub> of <5 V, and I<sub>on/off</sub> ratio of ~10<sup>7</sup>.

Finally, the integration of the transparent semiconductor, dielectric, and conductive electrodes onto a flexible platform was demonstrated. Through a combination of the low-temperature processes developed in this work, the integration of transparent flexible TFTs onto polyethylene naphthalate (PEN) substrates was accomplished. The flexible IGZO TFTs had current-voltage (I-V) characteristics similar to their rigid counterparts. The fully encapsulated transparent devices had  $\mu$  of ~6.7 cm<sup>2</sup>/V.sec,  $V_T$  of ~1 V, and  $I_{on/off}$  ratio of >10<sup>6</sup>.

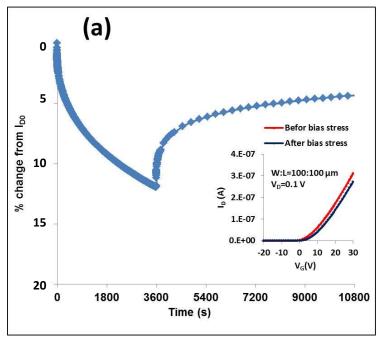

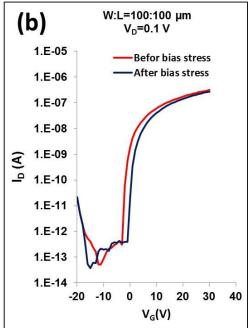

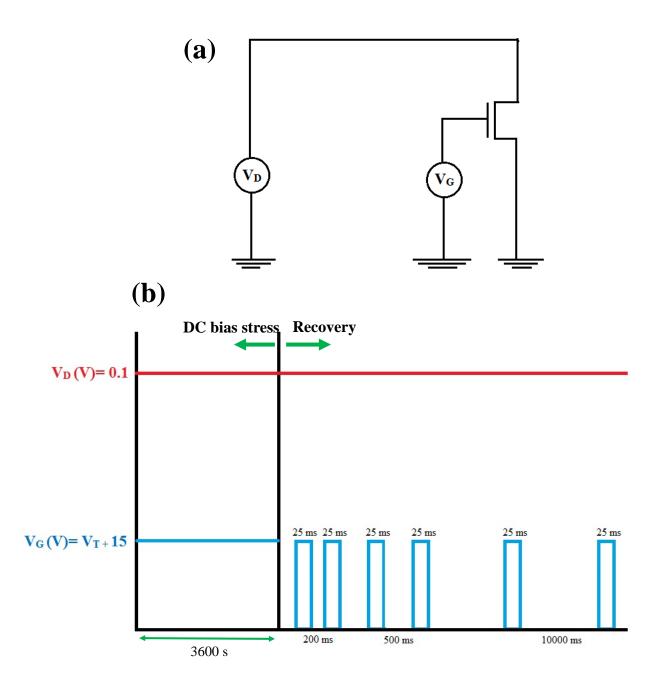

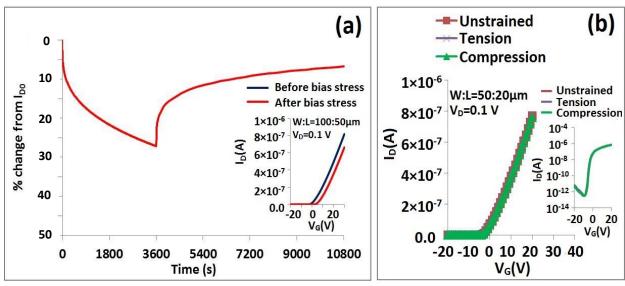

Electrical stability measurements of the flexible devices under tensile and compressive mechanical strain showed no appreciable change in the I-V characteristics during bending. The electrical characteristics under mechanical bending suggest that carrier transport is unaffected during mechanical strain due to the overlapping spherical s-orbitals in the IGZO conduction band. Testing under dc gate bias conditions, the electrical stability of the TFTs showed a positive V<sub>T</sub> shift of 3.8 V after 3600 s without any change in subthreshold-swing (S.S.). Pulsed-gate recovery measurements also showed rapid recovery of the drain current, both of which suggest that the dominant aging mechanisms is charge trapping in the back-channel etched transparent flexible IGZO TFTs.

## Acknowledgements

First of all, I would like to express my deepest appreciation and love to my mom, dad, and my sister, for their continuous and unconditional support and love. Without their assistance and understanding, it would have never been possible for me to accomplish this achievement.

I am proud that I have the kindest and the most honest father in the world, *Mr. Khosrow Tari*, who always stands behind me in difficult situations that I face. He has always been supportive and given me confidence. I will never forget times that he prioritized my education over his leisure time. I will never forget the life lessons he taught me. I love you forever, Dad.

I am proud to have the most compassionate, most patient, most understanding, and the kindest mom in the world, *Mrs. Farideh Khalili*. Honestly, I do not know what I can write here to express the support and help she provided me from my early childhood until now. I can never forget how hard she tried to show me the moral path of thinking. I can never forget how supportive she was in the risky decisions that I took. I cannot forget how generous she has been thorough my life. She knows me and my character better than anyone in the world, and knows how much I love her.

I would like to thank my younger, beautiful sister, *Miss Matin Tari*. Honestly, at the time that I emigrated to Canada, I was so worried and not sure that she could fill my role in the family. However, after a few months in Canada, surprisingly, I saw that she took all my responsibilities and played a better role than me. To be honest, she had a prominent role in my progress during my Ph.D. studies. Her presence next to the family let me focus on my Ph.D. studies more comfortably and without being so worried. I am proud of her and will never forget her support.

It gives me pleasure to extend my sincere thanks to my understanding and down-to-earth supervisor, *Dr. William S. Wong*. I should be frank with myself. Although it was not that easy for me, I learned a lot from him. He showed me how to present my data correctly. He showed me how to write journal papers scientifically. He showed me how to manage people with different skill sets efficiently. Thank you for all the lessons and all the support you provided during the years of my Ph.D. studies. I will never forget these years in my life.

I would like to express my gratitude to the most compassionate aunt (*Khale Faty*) and the most understanding uncle (*Amoo Amir*) in the world. You supported me since the first day I entered Canada. You did not let me feel homesick while I was far from my parents. You were exactly like my mom and dad. I am indebted to you for the rest of my life. I love you both.

I also want to thank my grandparents who always motivated and supported me in my long education journey. *Maman Bozarg joon*, I will love you forever. You were the most compassionate grandma in the world. I will never forget you and your memory. Rest in peace.

*Khale Mozhgan joon*, I cannot forget your kindness to me and my family during all the years of my studies. Thank you for all your support, *Khale joon*.

*Soheil* and *Setareh*, I am proud that I have such nice cousins. You were one of the main reasons that I had lots of fun here in Canada. To be honest, by having you next to me, I had much more confidence while I was pursing my Ph.D. studies. You are the most supportive, kind, generous, and down-to-earth cousins in the world. I love both of you.

I would like to thank my old friends *Hamed Akbari*, *Nina Taheri*, and *Ali Mazahery*. Thanks for always being supportive in all the situations I faced during the years of my Ph.D. studies. I think no one can destroy our relationships. You are clear, frank, generous, and trustworthy. You are unique. You know how much I love you.

I would also like to thank my university friends who gave me the chance to live in a very nice and active community in Waterloo. Sina Ghanbarzadeh, Omid Rezai, Babak Shokouhi, Pooya Mahboubi, Afshin Zamani, Azadeh Peivandi, Saeedeh Ghaffari, Navid Jahed, Alireza Khosropour, Mahyar Mazloumi, Farzin Misami, Alireza Zandieh, Milad Khoshnegar, Kazem Jeddi, Kaveh Sarikhani, and Shiva Abbaszadeh not only were you helpful, but also, by making lots of good memories for me, you offered me the opportunity to be more productive in my Ph.D. studies and research.

I would like to thank my Ph.D. defense committee members, *Dr. Becky Peterson, Dr. Karim Karim, Dr. Siva Sivoththaman, Dr. Yuning Li,* for taking the time to review my dissertation and provide constructive feedback. I would also like to acknowledge the friendship and assistance of *Dr. Mohammad-Reza Esmaeili-Rad, Dr. Nikolas Papadopoulos, Dr. Czang-Ho Lee,* and *Dr. Feng Chen* for all their training, unconditional scientific support, and advice. I would also like to thank *Richard Barber* for his troubleshooting in the Giga-to-Nanoelectronics (G2N) Centre during my Ph.D. research. Lastly and very importantly, I am honored to express my gratitude to all of our research group members for their continuous support during my Ph.D. studies. I believe that I was very lucky to work in a research group with such nice and down-to-earth members. *Melissa Chow, Bright Iheanacho, Minoli Pathirane, Maofeng Yang, Lilei Hu, and Qing Li,* without your help this Ph.D. study would have been much more challenging for me. Thank you all.

# **Dedication**

To my lovely uncle, Mr. Saeed Khalili, who showed me the meaning of life and taught me a lot.

Rest in Peace, Dayi Joon. I love you forever.

# **Table of Contents**

| List of Figures                                                                                                                                                         | X    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| List of Tables                                                                                                                                                          | xiii |

| 1. Introduction                                                                                                                                                         | 1    |

| 1.1. Introduction                                                                                                                                                       | 1    |

| 1.2. Organization of dissertation                                                                                                                                       | 7    |

| 2. Background Review                                                                                                                                                    | 10   |

| 2.1. Brief Background on Thin-Film Transistors                                                                                                                          | 10   |

| 2.2. Thin-film deposition and patterning techniques                                                                                                                     | 14   |

| 2.2.1. Sputtering                                                                                                                                                       | 15   |

| 2.2.2. Plasma-enhanced chemical vapor deposition (PECVD)                                                                                                                | 16   |

| 2.2.3. Electron beam evaporation (EBE)                                                                                                                                  | 18   |

| 2.2.4. Thin-film patterning                                                                                                                                             | 19   |

| 2.3. Flexible Electronics                                                                                                                                               | 20   |

| 2.4. Metal oxide-based TFTs                                                                                                                                             | 24   |

| 2.4.1. Channel Layer Materials                                                                                                                                          | 24   |

| 2.4.1.1. ZnO                                                                                                                                                            | 24   |

| 2.4.1.2. InGaZnO (IGZO)                                                                                                                                                 | 26   |

| 2.4.2. Electrical dependence on the chemical composition of the ZnO-based channel layer in Mo                                                                           |      |

| 2.4.2.1. Oxygen deficiency                                                                                                                                              | 31   |

| 2.4.2.2. Hydrogen (H)                                                                                                                                                   | 34   |

| 3. Effect of material structure, surface topography, and chemical composition of ZnO and IGZO charles on the current-voltage (I-V) characteristics of ZnO and IGZO TFTs |      |

| 3.1. Introduction                                                                                                                                                       | 36   |

| 3.2. Experimental                                                                                                                                                       | 37   |

| 3.3. Results                                                                                                                                                            | 38   |

| 3.3.1. The effects of different sputtering deposition parameters on the resistivity of the metal ox channel layers                                                      |      |

| 3.3.2. Effect of the crystalline structure, surface topography, and chemical composition of ZnO channel layer on the I-V characteristics of ZnO TFTs                    | 40   |

| 3.3.2.1. Channel layer deposition temperature                                                                                                                           | 41   |

| 3.3.2.2. Low-temperature thermal annealing                                                                              | 51   |

|-------------------------------------------------------------------------------------------------------------------------|------|

| 3.3.3. Effect of chemical composition and surface topography of IGZO channel layer on the characteristics of IGZO TFTs  |      |

| 3.4. Conclusion                                                                                                         | 67   |

| 4. Electrical dependence on the chemical composition of the gate dielectric in indium gallium zin thin-film transistors |      |

| 4.1. Introduction                                                                                                       | 68   |

| 4.2. Experiments                                                                                                        | 70   |

| 4.3. Results and discussion                                                                                             | 70   |

| 4.4. Conclusions                                                                                                        | 78   |

| 5. Controlled conductivity of sputtered IGZO for low-temperature transparent thin-film transistor                       | ·s80 |

| 5.1. Introduction                                                                                                       | 80   |

| 5.2. Experimental                                                                                                       | 81   |

| 5.3. Results and discussion                                                                                             | 81   |

| 5.4. Conclusions                                                                                                        | 88   |

| 6. Selective wet-etch processing of optically transparent flexible IGZO TFTs                                            | 90   |

| 6.1. Introduction                                                                                                       | 90   |

| 6.2. Experimental                                                                                                       | 91   |

| 6.3. Results and discussion                                                                                             | 91   |

| 6.4. Conclusions                                                                                                        | 99   |

| 7. SiO <sub>x</sub> thin-film plasma damage and hydrogen diffusion barriers for high-performance flexible               |      |

| transparent IGZO TFTs and circuits                                                                                      | 101  |

| 7.1. Introduction                                                                                                       | 101  |

| 7.2. Experimental                                                                                                       | 103  |

| 7.3. Results and discussion                                                                                             | 106  |

| 7.4. Conclusions                                                                                                        | 113  |

| 8. Conclusion and future work                                                                                           | 114  |

| 8.1. Conclusion                                                                                                         | 114  |

| 8.2. Future work                                                                                                        | 117  |

| References                                                                                                              | 120  |

# **List of Figures**

| Figure 2-1 Typical thin-film transistor (TFT) structure.                                                       | . 10 |

|----------------------------------------------------------------------------------------------------------------|------|

| Figure 2-2 Band diagrams of an n-type accumulation mode TFT under various gate bias conditions; a)             | No   |

| gate bias, b) Negative gate bias c) Positive gate bias                                                         | . 12 |

| Figure 2-3 Transfer characteristics of IGZO TFTs in in the (a) log and (b) linear scales. (c) output           |      |

| characteristics, W/L=100/100 µm.                                                                               | . 14 |

| Figure 2-4 The AJA sputtering system used in this research to deposit MO-thin-films                            | .16  |

| Figure 2-5 PECVD system used in this research to deposit insulator materials.                                  | . 18 |

| Figure 2-6 EBE system used in this research.                                                                   | . 19 |

| Figure 2-7 A schematic illustration of ZnO crystal structure (wurtzite). The Zn and O atoms are marked         | l as |

| well in the schematic with ash and blue circles, respectively [45].                                            | . 25 |

| Figure 2-8 Different formation mechanisms of bandgaps in covalent (a) and ionic (b,c) semiconductors           |      |

| [4]                                                                                                            | . 28 |

| Figure 2-9 Illustrative images of carrier conduction paths in (a) c-Si, (b) a-Si, (c) crystalline oxide, and   | (d)  |

| amorphous oxide                                                                                                |      |

| Figure 2-10 Percolation mechanisms in IGZO.                                                                    | . 29 |

| Figure 2-11 Polyhedral views of crystal structures of (a) In2O3, (b) InGaZnO4, (c) amorphous IGZO.             |      |

| [Red and gray polyhedra show (InOn) and (Zn/GaOn) polyhedra. In2O3 and c-IGZO are made of the                  |      |

| edge-sharing network of (InO6) octahedra and the corner-sharing sharing network between (InO6) and             |      |

| $(Zn/GaO_5)$ polyhedra. In amorphous IGZO, the edge-sharing network structures are preserved.], (d) CB         | M    |

| wave function in amorphous IGZO is drawn superimposed on (c) by green surfaces [4]                             |      |

| Figure 3-1 The AFM images of ZnO thin-films deposited under different deposition recipes                       | .40  |

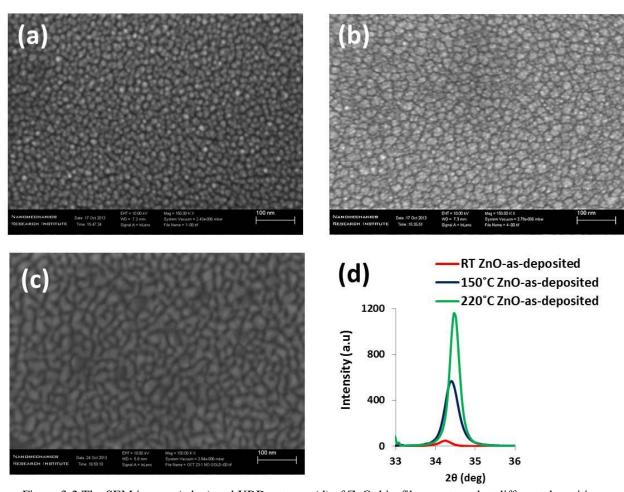

| Figure 3-2 The SEM images (a,b,c) and XRD patterns (d) of ZnO thin-films sputtered at different                |      |

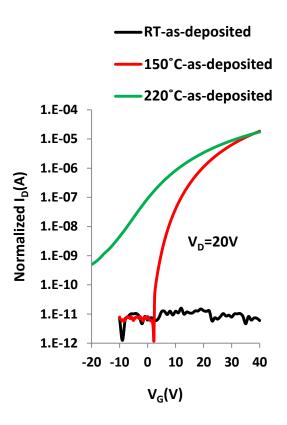

| deposition temperatures.                                                                                       | .41  |

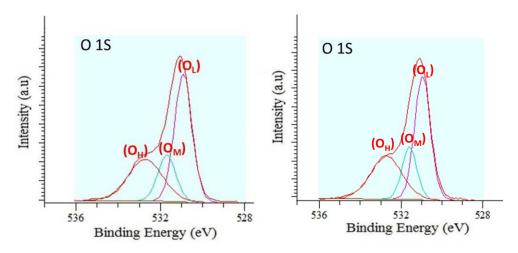

| Figure 3-3 O 1s XPS spectra of (a) 150 °C and (b) 220 °C ZnO films after surface contamination                 |      |

| cleaning.                                                                                                      |      |

| Figure 3-4 XPS depth profiles of zinc (Zn), oxygen (O), and oxygen vacancy ( $V_0$ ) for as-deposited 150      | °C   |

| and 220°C ZnO thin-films.                                                                                      | 45   |

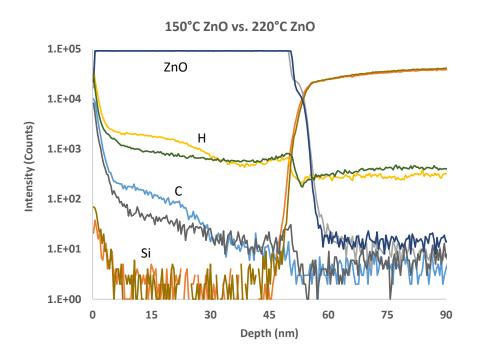

| Figure 3-5 SIMS depth profiles of hydrogen (H), zinc oxide (ZnO), silicon (Si), and carbon (C) for as-         |      |

| deposited 150°C and 220°C ZnO thin-films.                                                                      | 46   |

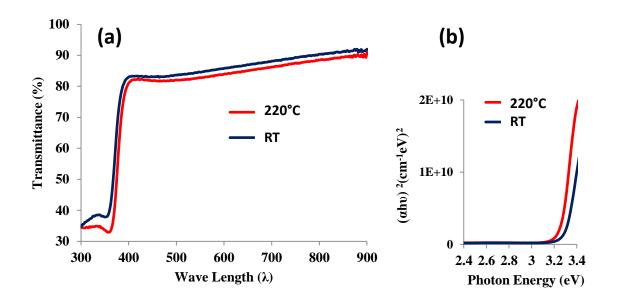

| Figure 3-6 Optical transmittance (a) and the band-gap energy (b) of the ZnO thin-films deposited at            |      |

| different temperature                                                                                          | .47  |

| Figure 3-7 Transfer characteristics of the TFTs consisted of ZnO channel layers deposited at different         |      |

| temperatures                                                                                                   | .49  |

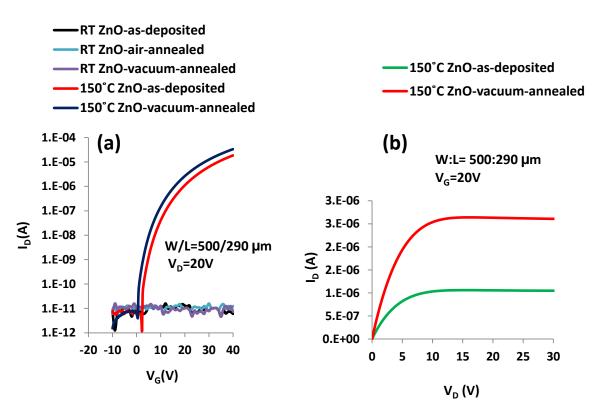

| Figure 3-8 Transfer, and (b) out-put characteristics of the ZnO TFTs under different channel layer             |      |

| deposition temperature and annealing conditions.                                                               |      |

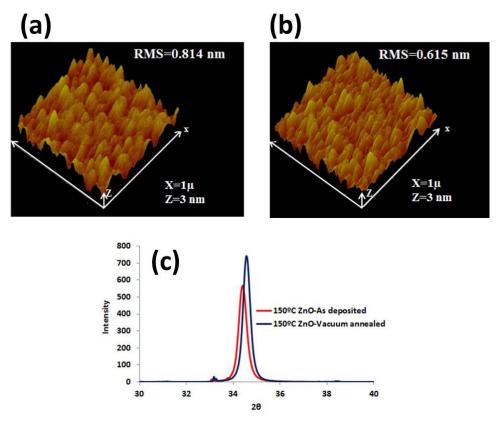

| Figure 3-9 AFM images of surface morphology of the (a) as-deposited, and (b) vacuum-annealed ZnO               |      |

| films, and (c) XRD patterns of the as-deposited and vacuum-annealed ZnO films deposited at 150°C               |      |

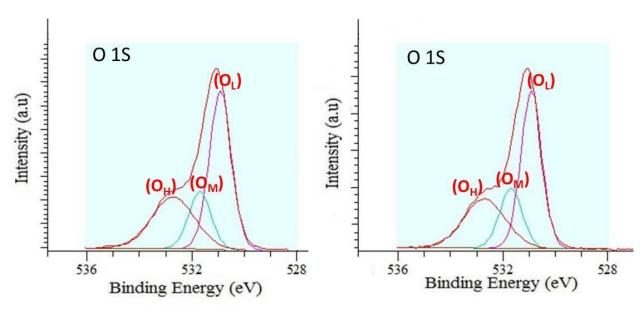

| Figure 3-10 O 1s XPS spectra of (a) as-deposited and (b) vacuum-annealed 150°C ZnO films after surface.        |      |

| contamination cleaning.                                                                                        | 54   |

| Figure 3-11 XPS depth profiles of zinc (Zn), oxygen (O), and oxygen vacancy (V <sub>o</sub> ) for as-deposited |      |

| 150°C and vacuum-annealed 150°C ZnO thin-films.                                                                | 56   |

| Figure 3-12 SIMS depth profiles of hydrogen (H), zinc oxide (ZnO), silicon (Si), and carbon (C) for as-                                                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| deposited 150°C and vacuum-annealed 150°C ZnO thin-films                                                                                                                                     |

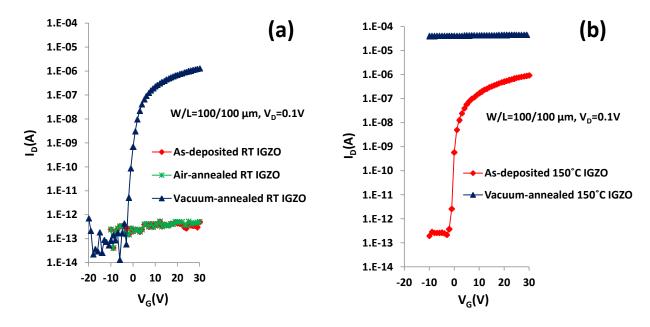

| Figure 3-13 The effect of the post-annealing process on the transfer characteristics of the IGZO TFTs with (a) RT, and (b) 150°C channel layers.                                             |

| · · · · · · · · · · · · · · · · · · ·                                                                                                                                                        |

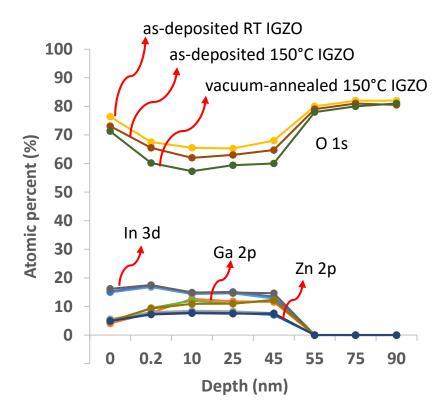

| Figure 3-14 XPS depth profiles of indium (In), gallium (Ga), zinc (Zn), and oxygen (O) for as-deposited RT IGZO, as-deposited 150°C IGZO, and vacuum-annealed 150°C IGZO thin-films          |

| -                                                                                                                                                                                            |

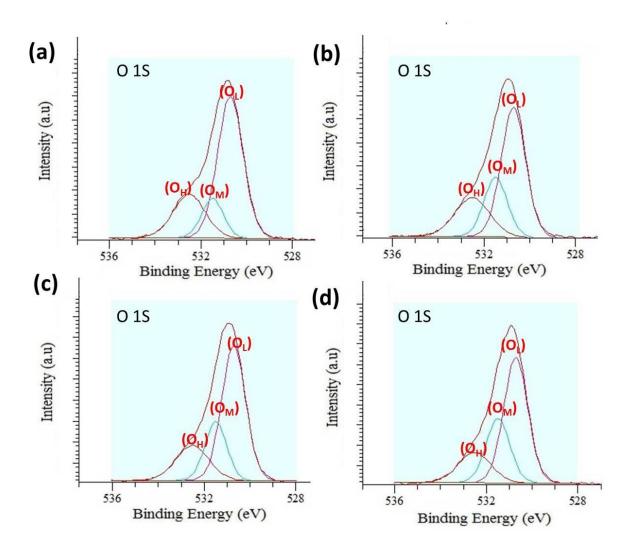

| Figure 3-15 O 1s XPS spectra of the (a) as-deposited RT IGZO, (b) vacuum-annealed RT IGZO, (c) as-deposited 150°C IGZO, and (d) vacuum-annealed 150°C IGZO films after surface contamination |

| cleaning61                                                                                                                                                                                   |

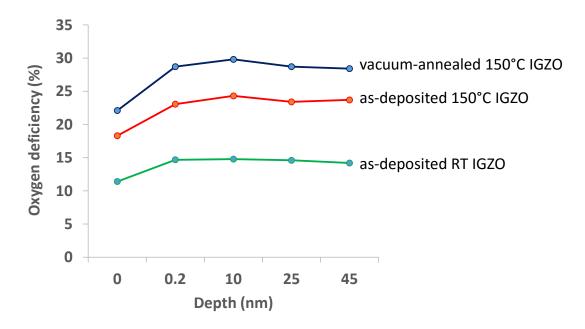

| Figure 3-16 Concentration of oxygen deficiency (%) at different depths in as-deposited RT IGZO, as-                                                                                          |

| deposited 150°C IGZO, and vacuum-annealed 150°C IGZO thin-films                                                                                                                              |

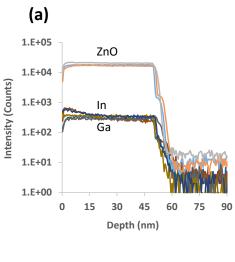

| Figure 3-17 SIMS depth profiles of (a) zinc oxide (ZnO), indium (In), and gallium (Ga), and (b) hydrogen                                                                                     |

| (H) and silicon (Si) in as-deposited RT IGZO, as-deposited 150°C IGZO, and vacuum-annealed 150°C                                                                                             |

| IGZO thin-films                                                                                                                                                                              |

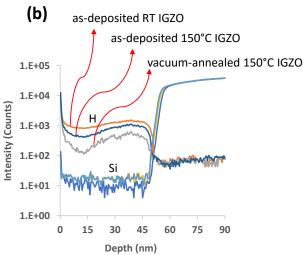

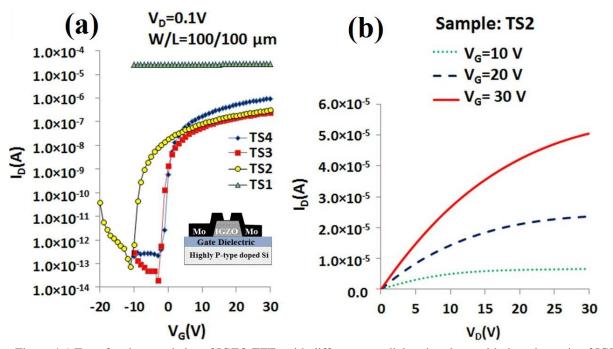

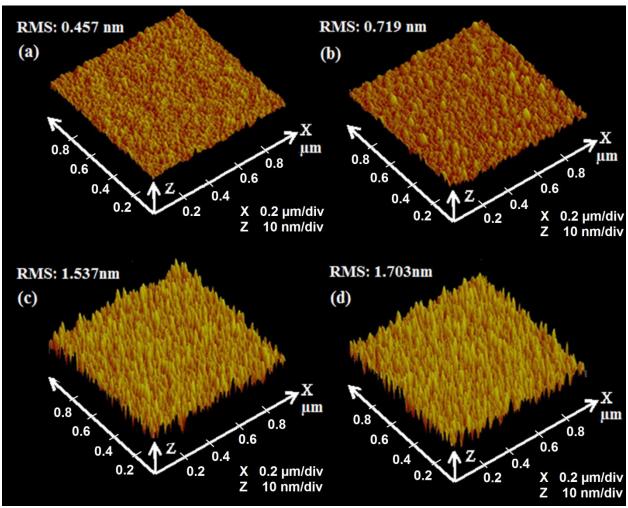

| Figure 3-18 AFM images of surface morphology of the (a) as-deposited RT-IGZO, (b) air-annealed RT-                                                                                           |

| IGZO, and (c) vacuum-annealed RT-IGZO, and (d) as-deposited 150°C-IGZO films                                                                                                                 |

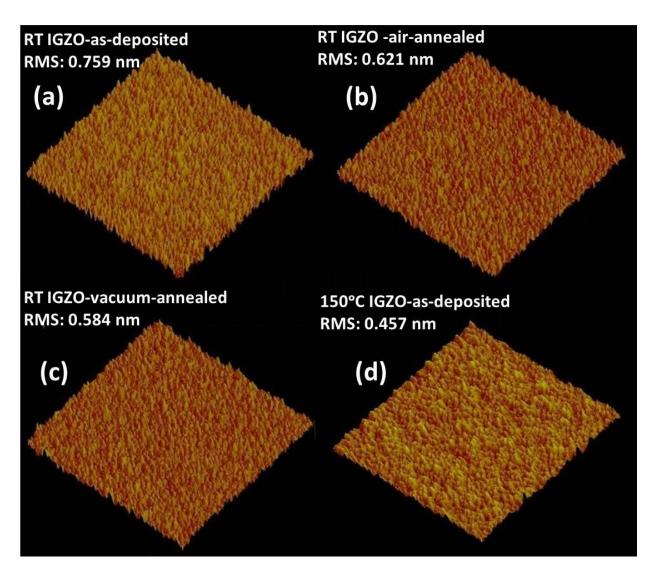

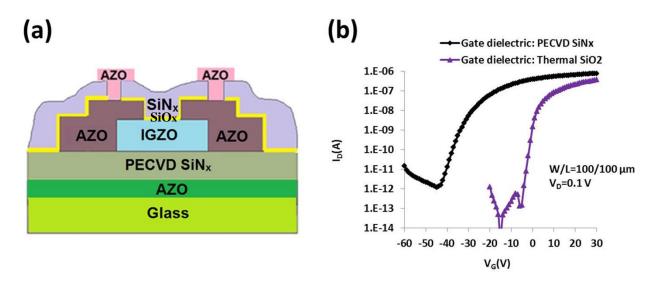

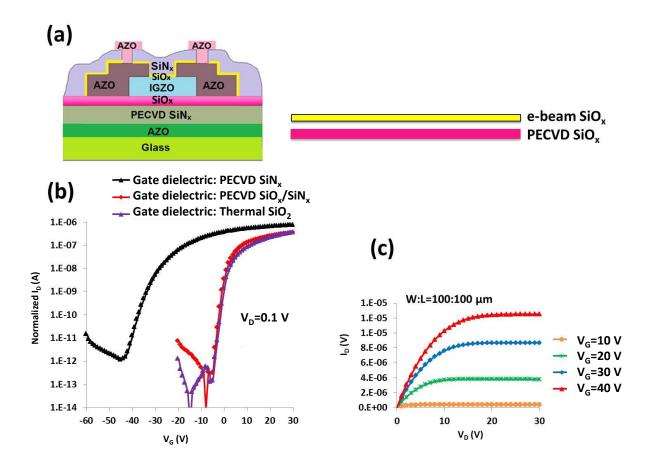

| Figure 4-1 Transfer characteristics of IGZO TFTs with different gate dielectrics along with the schematic                                                                                    |

| of IGZO TFT structure (inset), (b) Output characteristics of IGZO TFTs with 150°C PECVD SiO <sub>x</sub> /SiN <sub>x</sub>                                                                   |

| gate dielectrics (TS2)                                                                                                                                                                       |

| Figure 4-2 AFM images of surface morphology of the IGZO films deposited onto the different gate                                                                                              |

| dielectrics of (a) Thermal SiO <sub>2</sub> , (b) $150^{\circ}$ C PECVD SiN <sub>x</sub> , (c) $260^{\circ}$ C PECVD SiO <sub>x</sub> /SiN <sub>x</sub> , and (d) $150^{\circ}$ C            |

| PECVD SiO <sub>x</sub> /SiN <sub>x</sub>                                                                                                                                                     |

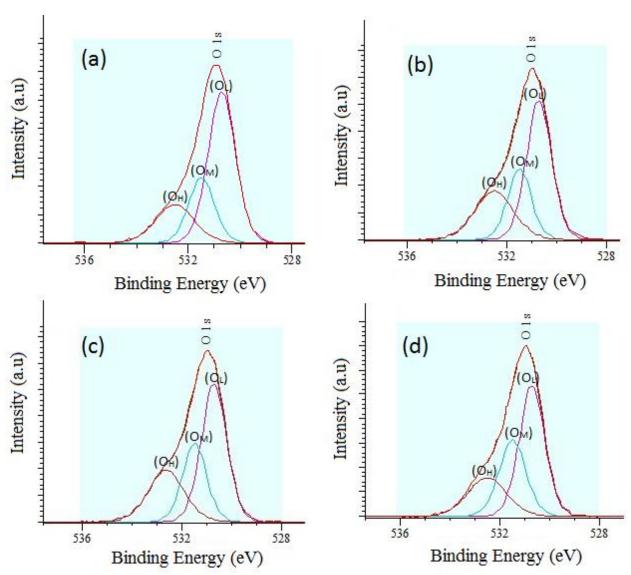

| Figure 4-3 O 1s XPS spectra of IGZO films deposited onto the different gate dielectrics: (a) Thermal                                                                                         |

| SiO <sub>2</sub> , (b) 260°C PECVD SiO <sub>x</sub> /SiN <sub>x</sub> , (c) 150°C PECVD SiO <sub>x</sub> /SiN <sub>x</sub> , and (d) 150°C SiN <sub>x</sub> , after surface                  |

| contamination cleaning74                                                                                                                                                                     |

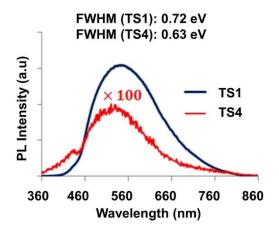

| Figure 4-4 Photoluminescence emission spectra for the IGZO films deposited onto the different gate                                                                                           |

| dielectrics: thermal SiO2 (TS4) and 150°C PECVD SiNx(TS1)                                                                                                                                    |

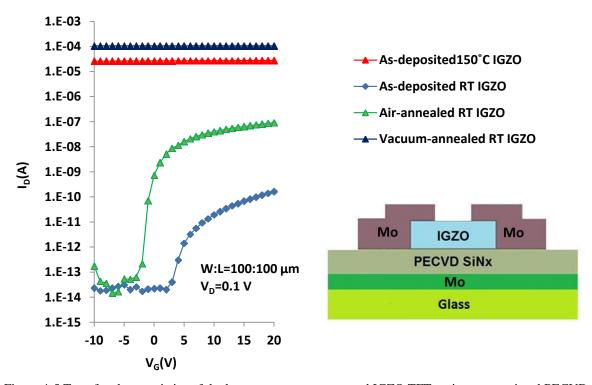

| Figure 4-5 Transfer characteristics of the low-temperature processed IGZO TFTs using conventional                                                                                            |

| PECVD gate dielectrics. (inset) The cross-section of the fabricated IGZO TFTs with a bottom gate                                                                                             |

| structure                                                                                                                                                                                    |

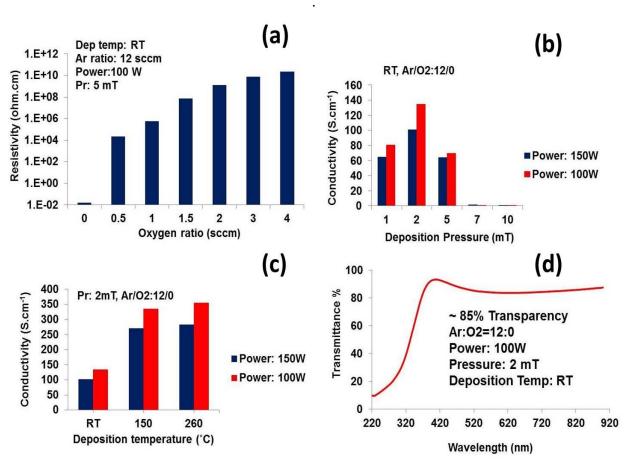

| Figure 5-1 The effects of (a) oxygen ratio, (b) deposition pressure, and (c) deposition temperature on the                                                                                   |

| electrical properties of IGZO thin-films. (d) The optical transmittance of the highly-conductive IGZO                                                                                        |

| thin-film deposited using the optimum recipe at RT.                                                                                                                                          |

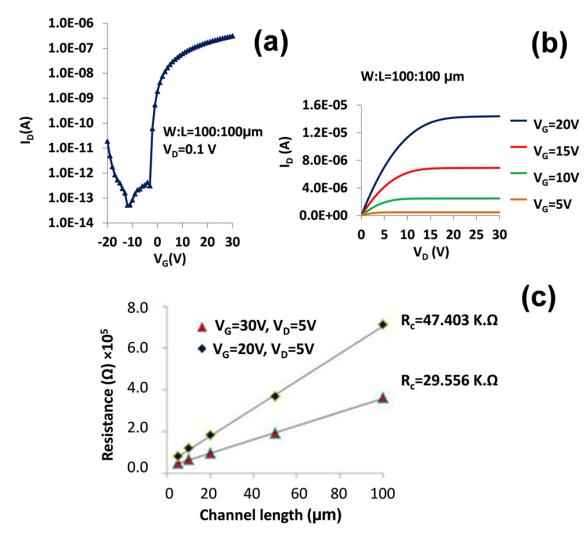

| Figure 5-2 Transfer (a) and output (b) characteristics of the lift-off processed transparent IGZO TFTs. (c)                                                                                  |

| Contact resistance of the fabricated TFTs extracted using the transmission line model                                                                                                        |

| Figure 5-3 Degradation in $I_D$ with bias stress ( $V_{ov}=10~V$ and $V_D=0.1~V$ ) with TFT transfer curves before                                                                           |

| and after bias stress in linear (inset) and log(b) scales                                                                                                                                    |

| Figure 6-1 Comparison between polycrystalline AZO and amorphous IGZO in terms of (a) etching rate,                                                                                           |

| and (b) selectivity. ((c) and (d)) AFM characterization of AZO thin-films with two different grain sizes;                                                                                    |

| the smaller grain films have faster etch rates. (e) Optical micrographs of a patterned AZO structure after                                                                                   |

| showing the lateral etching of the AZO underneath a patterned photoresist layer at 70% over-etching                                                                                          |

| process in 0.3% HCl solution                                                                                                                                                                 |

| Figure 6-2 (a) Contact resistance of the fabricated TFTs extracted using the transmission line model. (I                       | <b>b</b> ) |

|--------------------------------------------------------------------------------------------------------------------------------|------------|

| Optical transmittance of the fabricated device                                                                                 | .94        |

| Figure 6-3 (a) Transfer characteristics of the flexible transparent IGZO TFTs along with the schematic                         | of         |

| the IGZO TFT structure (inset), (b) output characteristics.                                                                    | . 95       |

| Figure 6-4 (a) Connection setup and (b) schematic of applied gate voltage $(V_G)$ and drain voltage $(V_D)$                    |            |

| and the recovery test during the bias stress measurements                                                                      | . 97       |

| Figure 6-5 Degradation in I <sub>D</sub> with bias stress (Vov=15 V and V <sub>D</sub> =0.1 V) with TFT transfer curves before | re         |

| and after bias stress (inset). (b) Transfer characteristics for transparent TFTs showing instantaneous                         |            |

| effects of applied strain                                                                                                      | .98        |

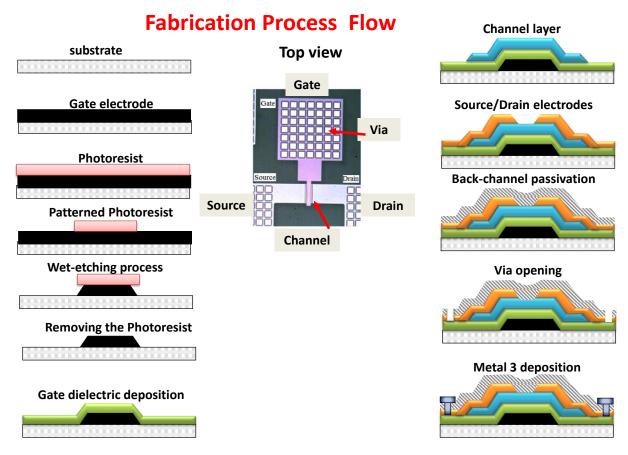

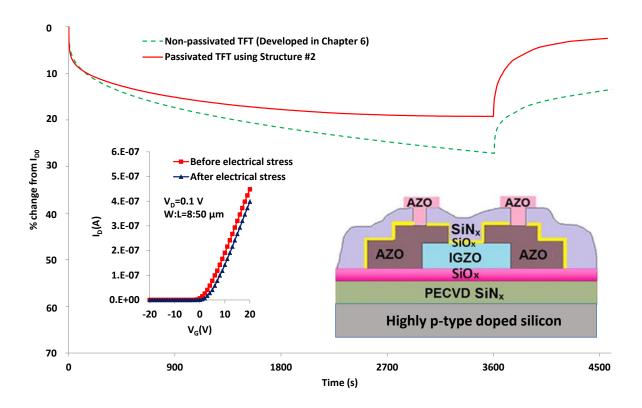

| Figure 7-1 Fabrication process flow.                                                                                           | 105        |

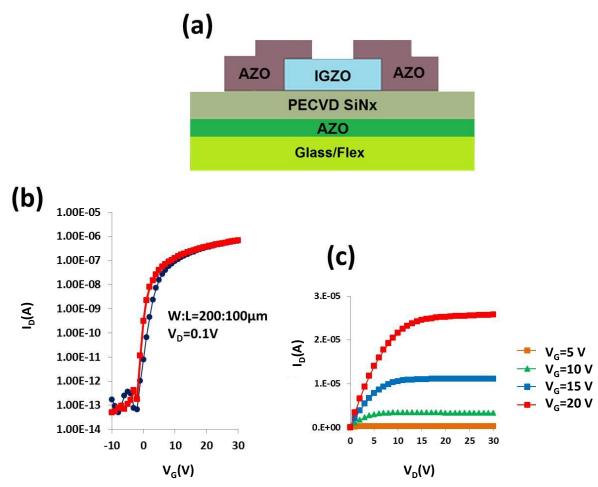

| Figure 7-2 The cross-section (a), transfer (b), and output characteristics (c) of the flexible transparent                     |            |

| IGZO TFTs.                                                                                                                     | 106        |

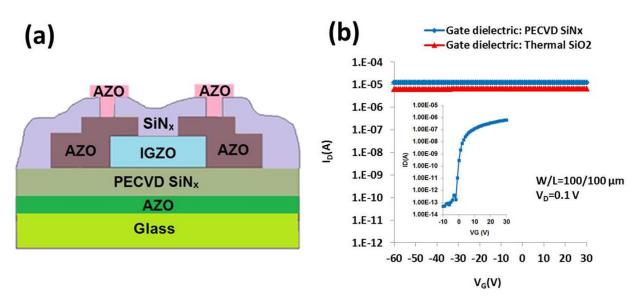

| Figure 7-3 The cross-section (a), and transfer characteristics (b) of the bottom-gate low-temperature                          |            |

| processed PECVD passivated transparent IGZO TFTs; with the TFT transfer curve before passivation                               |            |

| deposition (inset)                                                                                                             | 107        |

| Figure 7-4 The cross-section (a), and the transfer characteristics (b) of the passivated low-temperature                       |            |

| processed transparent IGZO TFTs with back-channel damage barrier structure                                                     | 108        |

# **List of Tables**

| Table 1-1 Device characteristics of the previous works on IGZO TFTs.                                   | 5     |

|--------------------------------------------------------------------------------------------------------|-------|

| Table 1-2 Some of the processing steps and device characteristics of the previous works on flexible IC | βZO   |

| TFTs. (Y stands for Yes, N stands for No, and NA stands for Not Applicable)                            | 6     |

| Table 2-1 Materials, deposition and patterning techniques, maximum process temperature and optical     |       |

| transparency of the previous works on flexible IGZO TFTs.                                              | 23    |

| Table 2-2 Some of the basic properties of zinc oxide material.                                         | 25    |

| Table 3-1 ZnO films with different deposition recipes.                                                 | 39    |

| Table 4-1 TFT I-V performance characteristics and XPS results.                                         | 72    |

| Table 7-1 Thin film materials, deposition and patterning techniques used in this chapter to fabricate  |       |

| optically transparent flexible IGZO TFTs.                                                              | . 105 |

## **Chapter 1**

## 1. Introduction

#### 1.1. Introduction

Transparent flexible electronics have recently received great attention in active-matrix organic light-emitting diode (AMOLED) displays for large-area electronics applications ranging from heads-up displays and smart windows to flexible sensor arrays [1]. One of the main challenges in this area is fabricating high-performance transparent flexible thin-film transistor (TFTs).

Different active layer materials such as amorphous silicon (a-Si), low temperature polysilicon (LTPS), and organic semiconductors can be used as active layers of TFTs. A-Si has the advantages of both uniformity over a large-area and maturity in its fabrication process. However, due to the insufficient field-effect mobility of this material system, it is not possible to apply this class of TFTs to fabricating large-area (> 70 inches) OLED and high performance (resolution:  $4000 \times 2000$  pixels, frame rate: 240Hz) LCD displays, which require a field-effect mobility of at least 3 cm<sup>2</sup>/V.sec [2]. The electrical instability of a-Si is another drawback that restricts its application in the display industry. LTPS has been found to be a promising alternative for a-Si in the fabrication of AMOLED displays of mobile devices such as cellular phones, laptops, and navigation tools, due to its superior field-effect mobility ( $\mu$ ) and electrical stability. However, the electrical properties of LTPS suffer from large-area nonuniformity. Thus, in LTPS-based AMOLED displays, even of a small size (< 5 inches), uniform image quality requires the presence of compensation pixel circuits [2]. Higher processing cost is another limitation for developing LTPS-based displays [3]. On the other hand, due to the poor electrical stability and field-effect

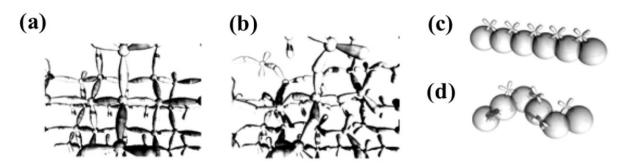

mobility of organic materials, there is less possibility of this class of TFTs being used as an alternative for a-Si and LTPS in the near future. Several research groups have reported that grain boundary is the dominant factor in the deterioration of short-range uniformity, as is the case in polycrystalline silicon (p-Si) TFTs [4]. Hence, high-field-effect mobility amorphous semiconductors will be an ideal candidate in developing high-performance large-area electronics. However, researchers used to believe that the field-effect mobility of metal-oxide semiconductors significantly deteriorates after switching from crystalline structure to the amorphous phase. This degradation had been attributed to the strong scattering from the disordered structures, and deterioration of  $\mu$  from 1500 cm²/V.sec in crystalline silicon (c-Si) structures to less than 2 cm²/V.sec in amorphous structures had been considered the main proof for this assumption.

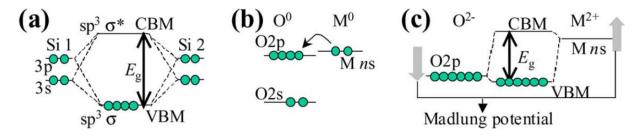

However, in 1996, Hosono *et al.* changed this understanding by demonstrating high carrier mobility amorphous metal oxides (MO) composed of heavy metal cations [5, 6]. They later completed this study and demonstrated that these MOs, by taking advantage of the spherical shape of the s-orbitals in the conduction band, are insensitive to spatial directionality and exhibit large band-dispersion and overlaps even in amorphous structures. In turn, this large band dispersion results in high mobility in the amorphous structure of this material system [4]. This phenomenon is in contrast with the electronic structure of covalent semiconductors, whose valence band maximum (VBM) and conduction band minimum (CBM) are made up from the anti-bonding ( $sp^3\sigma^*$ ) and bonding ( $sp^3\sigma$ ) states of hybridized orbitals, respectively, and are highly sensitive to spatial directionality. Large spatial directionality results in the formation of the strained chemical bonds and large amount of traps and scattering centers in amorphous structures, and explains why much lower field-effect mobility is observed in conventional amorphous structures such as hydrogenated amorphous silicon (a-Si:H) than in crystalline ones [4].

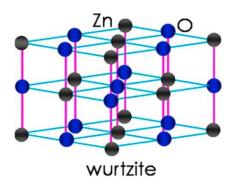

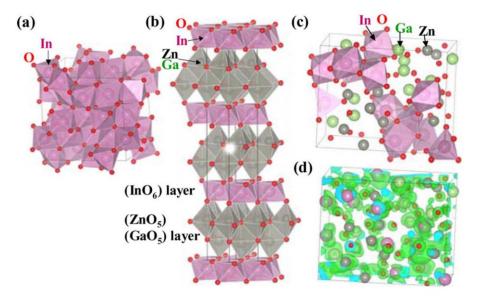

The above unique electronic properties of metal oxides have attracted much interest in several transition metal oxides such as In<sub>2</sub>O<sub>3</sub>, ZnO, and SnO<sub>2</sub>, all of which have large spherical shape s-orbitals in their conduction bands. These oxides in nature are polycrystalline and cannot be considered as an appropriate TFT channel layer material due to their poor electrical uniformity. However, taking advantage of different crystalline structures and different coordination numbers to the oxygen, each multi-component of the above mentioned oxides can result in the formation of amorphous structures with a large spherical shape s-orbital in their conduction band [2]. As an example, ZnO and In<sub>2</sub>O<sub>3</sub>, by having wurtzite and bixbyite structures, respectively, and demonstrating different coordination numbers to oxygen as ZnO<sub>4</sub> and InO<sub>6</sub>, can result in the formation of a high field-effect mobility amorphous InZnO (IZO) structure. This structure can be considered as both transparent electrodes and semiconductor channel layers, depending on its chemical composition. The higher the In content, the higher the electrical conductivity. Although amorphous IZO shows high field-effect mobility (> 20 cm<sup>2</sup>/V.sec) and superior uniformity in its electrical properties, the presence of high carrier concentration in this material system even at low In content results in a large off-current (I<sub>off</sub>) and small I<sub>on/off</sub> ratio, which hinders its application as a TFT channel layer. This problem has been overcome by the incorporation of Ga into the IZO structure and results in the formation of an amorphous InGaZnO (IGZO) channel layer. Nomura et al. [7] showed that Ga ions tightly bind oxygen ions, thereby supressing the formation of oxygen deficiency, which are considered to be shallow donors in the IGZO channel layer material. IGZO TFTs have superior field-effect mobility and electrical stability than those of a-Si. The superior electrical stability is due to the presence of lower density of states in their sub-bandgap energy [4]. Amorphous metal oxides also have much better electrical uniformity than LTPS. As a consequence of these benefits, the semiconducting oxides have been suggested as one of the most promising

candidates for large-area electronics during the past few years. Metal oxides also demonstrate high optical transparency due to their large band-gap energy, which makes them one of the key components in the field of transparent electronics. Their amorphous structure is also better suited for large-area processes due to absence of the grain boundaries [4]. All of these unique advantages have resulted in such rapid development of IGZO TFT technology that almost eight years after Hosono *et al.* [7] introduced high-performance working-TFTs based on amorphous IGZO active layer in 2004, Sharp demonstrated the first IGZO TFT-based LCD display [8]. However, a large number of scientific reports have continued to be published since demonstration of the first LCD panels incorporating IGZO TFTs that continue to address remaining problematic areas. According to the Scopus database results, there was an upward (~27%) trend in the number of such publications from 2013 to 2014. Both the volume and the upward trend of these publications suggest that although many developments have occurred in the field of MO TFTs, some issues remain in developing a conventional and low-temperature process for fabrication of large-area flexible transparent electronics based on IGZO TFTs.

Reports have shown the out-diffusion of hydrogen (H) atoms from plasma-enhanced chemical vapor deposition (PECVD) dielectrics into adjacent IGZO channel layers during deposition [9, 10] results in the formation of shallow donors [11, 12] and a degradation of the TFT I-V characteristics. In addition, ion bombardment of the IGZO channel layer during the plasma-enhanced processing is found to result in the formation of shallow donors due to creation of oxygen deficiencies, which increases the channel conductivity in MO-TFTs and degradation of the TFT characteristics [12-15]. Thus, tuning the hydrogen and oxygen concentration of IGZO channel layers is one of the key points in developing high-performance IGZO TFTs. High-temperature deposition and high-temperature post-annealing have been identified as key solutions in adjusting the hydrogen [16]

and oxygen [17] concentration of IGZO channel layers. Lack of high-selectivity etchants between the transparent conductive oxides and semiconductors is another issue which hinders conventional wet-etch patterning of source/drain (s/d) electrodes. Table 1-1 exhibits the I-V characteristics of relatively high-temperature ( $\geq 250^{\circ}$ C) processed IGZO TFTs fabricated on rigid substrates. As can be seen, there is a large variation in terms of field-effect mobility (0.07 <  $\mu$  < 21.8), threshold-voltage (-9.5 < V<sub>T</sub> < 11), subthreshold-swing (0.17 < S.S. < 7.37), on-off ratios (10<sup>4</sup> < I<sub>on/off</sub> < 10<sup>10</sup>), and off-current (10<sup>-9</sup> < I<sub>off.</sub> < 10<sup>-13</sup>), mainly arising from different deposition and annealing temperature, different annealing environments, different materials and device structures.

Table 1-1 Device characteristics of the previous works on IGZO TFTs.

| Reference #: | μ (cm²/V.sec) | V <sub>T</sub> (V) | S.S. (V/decade) | Ion/off (A)                          | I <sub>off</sub> (A)                   |

|--------------|---------------|--------------------|-----------------|--------------------------------------|----------------------------------------|

| [18]         | 11.4-21.8     | 0.83-3.0           | 0.17            | ~10 <sup>7</sup>                     | ~10-11                                 |

| [19]         | 2.4-4.21      | 2.9-5.8            | 0.4-1.51        | ~106                                 | ~10 <sup>-12</sup>                     |

| [20]         | 6.6           | 2.43-5.44          | 1.098-1.283     | ~10 <sup>7</sup>                     | ~10 <sup>-13</sup>                     |

| [21]         | 7.2           | -9.5               | 0.3             | ~107                                 | ~10 <sup>-13</sup>                     |

| [22]         | 0.072         | 28                 | 1.4             | ~104                                 | ~10-9                                  |

| [23]         | 21.79         | -0.15              | 0.26            | ~108                                 | ~10-11                                 |

| [24]         | 1.4-3.1       | 7-11               | 2.4-4.4         | ~10 <sup>5</sup>                     | ~10-9                                  |

| [25]         | 0.18-9.36     | 2.22               | 0.21-7.37       | ~10 <sup>4</sup> to 10 <sup>10</sup> | ~10 <sup>-9</sup> to 10 <sup>-12</sup> |

Recently, a few research groups have reported the feasibility of fabricating high-performance *flexible* IGZO TFTs. Table 1-2 shows recent work on flexibles IGZO TFTs on different flexible substrates such as polymeric substrates, metal foils, and flexible glasses. It also compares these studies in terms of the conventional dielectric layers used, optical transparency, source/drain

patterning techniques, and their electrical stability, to the current manufacturing specifications of the display industry.

Table 1-2 Some of the processing steps and device characteristics of the previous works on flexible IGZO TFTs. (Y stands for Yes, N stands for No, and NA stands for Not Applicable).

|                                                          | Reference #: |      |      |      |      |      |      |      |      |      |      |      |

|----------------------------------------------------------|--------------|------|------|------|------|------|------|------|------|------|------|------|

|                                                          | [26]         | [27] | [28] | [29] | [30] | [31] | [32] | [33] | [34] | [35] | [36] | [37] |

| Using conventional PECVD dielectric materials?           | Y            | N    | N    | N    | Y    | N    | N    | N    | N    | N    | Y    | N    |

| Low-temperature (≤220°C) process?                        | N            | Y    | Y    | NA   | N    | Y    | Y    | Y    | Y    | NA   | Y    | Y    |

| Transparent?                                             | Y            | N    | N    | N    | N    | N    | N    | N    | N    | N    | N    | N    |

| Conventional wet/dry etching patterning?                 | N            | N    | N    | NA   | N    | N    | NA   | N    | N    | N    | N    | N    |

| Long-term bias instability measurements (Aging test)?    | Y            | N    | N    | N    | N    | N    | Y    | N    | N    | Y    | N    | Y    |

| Long-term bias instability measurements (Recovery test)? | N            | N    | N    | N    | N    | N    | N    | N    | N    | N    | N    | N    |

The results show that almost all these flexible TFTs suffer from the poor optical transparency and a lack of a direct wet/dry etching process for TFT manufacturing. In addition, it can be seen that only a few groups have used conventional PECVD nitride and oxide dielectric layers while almost all reports use high-melting point substrates and a high-temperature process in order to fabricated high-performance devices. There is also a lack of understanding with regards to the electrical stability of these devices where long-term aging and recovery tests would provide insight to the operational lifetimes for flexible MO-TFTs.

A closer look at the findings of these reports concludes that their fabrication processes involve three main approaches: (a) non-conventional dielectric materials and deposition techniques, (b) applying high-temperature processes that limit fabrication to high melting-point substrates such as metal foil, polyimide, and flexible glass substrates, and (c) the requirement for lift-off patterning or shadow-mask techniques to define device features.

Passivation materials such as SiO<sub>2</sub>/TiO<sub>2</sub>/SiO<sub>2</sub> and HfO<sub>2</sub>/TiO<sub>2</sub>/HfO<sub>2</sub> [29], TiO<sub>2</sub> [38], MgO<sub>0.3</sub>BST<sub>0.7</sub> [39], and Y<sub>2</sub>O<sub>3</sub> [7] typically require advanced deposition techniques such atomic layer deposition (ALD) [35] that are not compatible with the current large-area electronic process tools. Additionally, high-melting point substrates such as metal foil [40] and polyimide [19] are not transparent, preventing their application in the field of transparent electronics. Alternative flexible platforms such as thin-glass substrates [26] are highly brittle and are not appropriate solutions for large-area manufacturing due to potential low yield due to substrate fracture. Finally, the lack of a reliable high-selectivity etchant has also hindered the development of transparent electronics where many research groups are using either lift-off or shadow-mask methods, which are not favorable patterning techniques in industry. The opaque electrodes used in many studies are another bottleneck to developing transparent flexible electronics. Greater understanding of the electrical instability of the flexible TFTs is also needed.

Thus, it is clear that if large-area flexible transparent electronics based on IGZO TFT backplanes are to be developed, it will be critical to overcome the engineering and scientific challenges to enable low-temperature fabrication processes for high-performance flexible transparent IGZO TFTs that take advantage of the current device structure, processing equipment, and process flows that enable the current state-of-the-art large-area electronic systems.

### 1.2. Organization of dissertation

This Ph.D. dissertation studies the factors that affect transition-metal-oxide transistor performance, covering different aspects demonstrating the relationship between materials processing and characterization, device processing and characterization, to integrate these transparent metal-oxide devices onto flexible platforms. Finally, it describes a novel back-end encapsulation process for passivating the device and demonstrates its performance under mechanical bending. These factors,

which are explained below, culminate in the demonstration of optically transparent back-channel etched flexible IGZO TFTs using a conventional TFT process flow implemented at low-temperatures.

Chapter 2 briefly reviews the device physics of thin-film transistors, device operation, thin-film deposition, patterning techniques, and then introduces metal oxide (MO)-TFTs to provide the necessary background for the experimental work of the thesis. The beginning of Chapter 3 investigates the effects of different sputtering deposition parameters on the electrical properties of the metal-oxide channel layers followed by studies into the electrical dependence on the material properties, surface topography, and chemical composition of the metal oxide channel layer for ZnO and IGZO TFTs as a function of deposition temperature and annealing environments. The current-voltage (I-V) characteristics of the fabricated TFTs are correlated to the surface morphology, structural characteristics, and the chemical composition of the TFT channel layers. Chapter 4 considers the effect of the chemical composition of the plasma-enhanced chemical vapor deposition (PECVD) and thermally grown gate dielectrics on the surface roughness and chemical composition of the channel layer and their effect on TFT performance. In the end, a lowtemperature (≤ 150°C) process is developed to fabricate high-performance opaque IGZO TFTs using conventional PECVD gate dielectrics. In Chapter 5, optically transparent high-performance IGZO TFTs are fabricated using IGZO contacts and a lift-off patterning technique. Applying sputtered IGZO as the source/drain electrodes gives the opportunity to deposit channel layers and contact electrodes using the same sputtering target in IGZO TFT fabrication, which results in a simplified fabrication process and with higher-quality electrical contacts between the semiconductor and source/drain electrodes. The conductivity of IGZO thin-films is tuned by controlling the sputtering power, pressure, and temperature during the film deposition.

Transmission line measurement (TLM) is also used to determine the contact resistance of the IGZO electrodes. In order to better understand the electrical instability of the fabricated TFTs, dc gate-bias stress measurements and pulsed-gate recovery tests are also carried out. Chapter 6 demonstrates the feasibility of fabricating optically transparent flexible IGZO TFTs using a weterch patterning technique. Contact resistance is again studied using the TLM method. In addition, the electrical instability of the fabricated TFTs is investigated using dc gate-bias stress and pulsed-gate recovery measurements. Furthermore, the effect of mechanical bending on the TFT I-V characteristics is measured under uniaxial tensile and compressive strain applied along the channel length of the devices (parallel to I<sub>D</sub>) by bending the samples in concave and convex sample holders at room temperature. In Chapter 7, a simple, low-temperature, and relatively low-cost approach is demonstrated to passivate back-channel etched transparent IGZO TFTs. Finally, Chapter 8 summarizes the contribution of this Ph.D. thesis to the field of flexible transparent electronics and points out suggestions for future work.

## Chapter 2

## 2. Background Review

### 2.1. Brief Background on Thin-Film Transistors

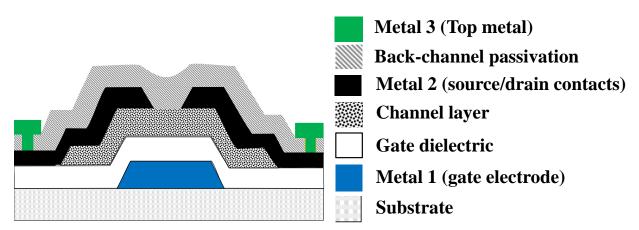

Typical thin-film transistors (TFTs) are composed of a gate, gate dielectric, active layer, back channel passivation and source/drain (s/d) electrodes. Figure 2-1 shows a schematic of a TFT device. In a n-type (p-type) TFTs when an appropriate positive (negative) gate voltage ( $V_G$ ) applies, the conductivity of channel layers increases. (Note: in this dissertation, all fabricated TFTs are based on an n-channel device.)

Figure 2-1 Typical thin-film transistor (TFT) structure.

In an n-type TFT, applying a negative  $V_G$  leads to the formation of an electric field, which in turn, results in the formation of a depletion region in the channel layer. In this case, the semiconductor layer acts like a high resistance (insulating) material where current flow between the source and drain contacts reduced to very low values (ideally,  $I_D < 10^{-12}$  A) and the transistor is considered to be Off.

In contrast, when a positive potential is applied to the gate electrode in an n-channel TFT, an accumulation of electrons occurs in the channel layer within 5 to 15 nm of the gate dielectric, and the conductivity of channel layer increases in this region. In this case, when the applied  $V_G$  is greater than the threshold voltage ( $V_T$ ) (the minimum potential required to turn the device strongly ON), electrons can flow from the grounded source to the biased drain [41].

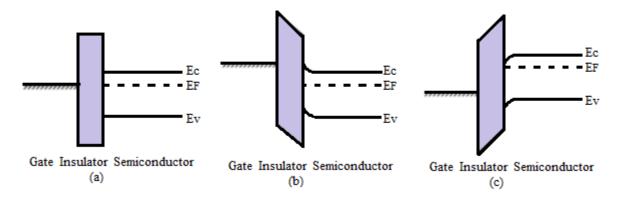

Band diagrams of a TFT in accumulation mode under various gate bias conditions can be seen in Figure 2-2. When no gate voltage is applied (ideal condition) the band diagram is assumed to be flat, Figure 2-2 (a). Applying a negative gate bias results in the formation of a depletion region (depleted of mobile charge) in TFT channel layer. Depletion of mobile charge gives rises to the creation of a positive charge region which results in a positive (upward) bending of the valence and conduction bands, as it can be seen in Figure 2-2 (b). In contrast, a positive gate bias attracts (accumulates) electrons to the gate dielectric/channel layer interface. As it is illustrated in Figure 2-2 (c), the negative charges which are created in channel layer leads to a negative (downward) bending of the valence and conduction band. Based on the type of the gate bias (positive or negative), TFTs can be classified into two categories: a) enhancement mode, and b) depletion mode devices. In enhancement mode devices, a positive gate voltage is needed to accumulate the channel layer and turn the device on. In contrast, for the depletion mode, a negative gate voltage is needed to turn on the device [41].

Figure 2-2 Band diagrams of an n-type accumulation mode TFT under various gate bias conditions; a) No gate bias, b) Negative gate bias c) Positive gate bias.

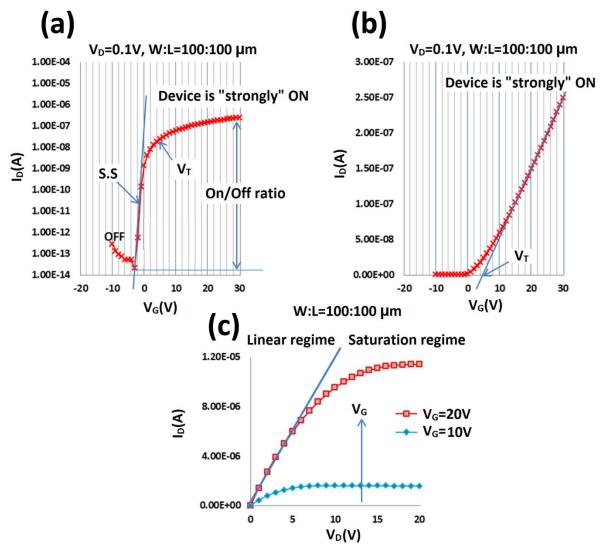

Both drain voltage (V<sub>D</sub>) and gate voltage (V<sub>G</sub>) can be controlled independently. When the  $V_G$  is held constant and the  $V_D$  is swept, the output characteristics of the device are generated. By sweeping the V<sub>G</sub>, with V<sub>D</sub> constant, the generation of the transfer I-V characteristics may be obtained, as is shown in Figure 2-3(a,b). The ratio of the maximum drain current (sometimes referred to as the on-current (I<sub>on</sub>)) divided by the minimum drain current (leakage current or I<sub>off</sub>) is commonly referred to the I<sub>on/off</sub> ratio. The majority of the high-performance MO-TFTs introduced in the previous chapter (Chapter 1) usually demonstrate I<sub>on/off</sub> ratio >10<sup>5</sup>. Subthreshold Swing (S.S.) is another parameter which determines the electrical performance of TFTs. S.S. can be calculated by inverting the maximum slope of the transfer characteristics, and it shows the V<sub>G</sub> required to induce a decade increase in the I<sub>D</sub>. Small values of S.S. result in higher speeds and lower power consumption in the fabricated device. Since both interface and bulk traps degrade S.S. in MO TFTs, optimizing the fabrication process flow plays a dominant role in developing high-speed and low-power consumption MO-TFT switches for large-area electronics, especially portable devices. According to the finding of this Ph.D. study and the findings of the other research groups, it seems that the majority of MO-TFTs demonstrate S.S. in the range of ~0.2 and ~4 V/decade, depending on the fabrication process flow, deposition and annealing temperature, annealing environment, and the applied materials.

When  $V_D < V_{G^-}V_T$ , TFT works in linear mode and when  $V_D > V_{G^-}V_T$  device works in the saturation mode [41]. The linear and saturation mobility of TFTs can be determined using the gradual-channel approximation (Eq. 2.1 and 2.2):

$$I_{D} = \frac{W}{L} \mu C[(V_G - V_T)V_D - \frac{{V_D}^2}{2}] \qquad \text{Linear } (V_G - V_T) > V_D$$

(2.1)

$$I_{D} = \frac{W}{L} \mu C \left[ \frac{(V_G - V_T)^2}{2} \right]$$

Saturation  $(V_G - V_T) < V_D$  (2.2)

where  $\mu$  is the field-effect mobility, C is the specific capacitance of the gate dielectric, (W/L) is the channel width to length aspect ratio of the device,  $V_T$  is the threshold voltage,  $V_G$  is the gate voltage, and  $V_D$  is the drain to source voltage.

At a low  $V_D$ , the squared term in equation (2.1) is insignificant and the device behaves like a variable resistor with the  $I_D$  proportional to the  $V_D$ . As  $V_D$  increases, electrons in the region surrounding the drain are depleted; creating a pinch-off point and the  $I_D$  will be constant for increasing  $V_D$ . The device is operating in saturation when  $V_G$ - $V_T$  <  $V_D$ . In saturation mode, the device functions as a constant current source where the drive current is dependent on the gate voltage.  $V_T$  can be determined using different methods such as linear extrapolation of the  $I_D$ - $V_G$  plot in linear mode, as illustrated in Figure 2-3 (b), or of the  $I_D^{1/2}$ - $V_G$  plot in saturation mode [41].

Figure 2-3 Transfer characteristics of IGZO TFTs in in the (a) log and (b) linear scales. (c) output characteristics,  $W/L=100/100~\mu m$ .

## 2.2. Thin-film deposition and patterning techniques

In order to fabricate thin-film transistors (TFTs), several thin-film layers need to be deposited and patterned back to back. In this section, the main thin-film deposition methods and thin-film patterning techniques, which are used in this Ph.D. research, are briefly introduced.

#### 2.2.1. Sputtering

All the semiconductors and transparent conducting oxides studied in this Ph.D. research are deposited using sputtering and a general overview of this deposition technique is given in this subsection. A simple structure for a sputtering system consists of a simple Direct Current (DC) diode. In this structure, the material source (sputtering target) is placed on the negative electrode, while the substrate is placed on the positive electrode. The anode is usually grounded, and the cathode is placed within the vacuum chamber. The chamber is backfilled with an inert gas and a DC field between the anode and cathode is applied. Due to the applied electric field, electrons and ionized gas species are attracted toward the positive (substrate) and negative (sputtering target) electrodes, respectively. Positively charged ions strike the target material on the cathode electrode that results in the emission of secondary electrons from the target surface, which sustains the glow discharge. Due to the much smaller mass of the electrons than that of the ions, the secondary electrons are quickly accelerated away from the target surface, resulting in the formation of a high-field region, which is called the Crooke's dark space, in front of the target material [42]. In this dark region, which accounts for most of the voltage drop between the substrate and target material, positively charged ions accelerate toward the target material (cathode electrode) and result in the ejection of atoms from the target and deposition on the substrate. It should be mentioned that DC configurations are only applicable when the target materials are conductive and the secondary electrons have a chance to continuously sustain the glow discharge. In the case of non-conductive materials, the presence of an alternating current (AC) field is necessary. The applied AC field, by formation of a self-biased voltage located in front of the target material, results in a deposition mechanisms similar to the DC configuration. The short positive portion of the excitation, by attracting the electrons towards the target, can replenish the lost secondary electrons and results in

sustaining the glow discharge when an insulating target materials are used. It is worth noting that in practical applications, in order to increase the chance of ionization, strong magnets usually are put behind the sputtering target (cathode) to gyrate electrons in loops parallel to and confined near the target material.

In some cases such as oxide deposition, reactive sputtering can be used in order to adjust the material and electrical properties of the sputtered films. In reactive sputtering, in addition to an inert gas, a reactive gas such as oxygen can also be employed. Figure 2-4 shows the AJA sputtering system used in this research to deposit channel layers and contact electrodes.

Figure 2-4 The AJA sputtering system used in this research to deposit MO-thin-films.

### 2.2.2. Plasma-enhanced chemical vapor deposition (PECVD)

Dielectric materials are one of the key elements of TFT structures, and they are usually used as gate dielectrics and passivation layers in TFT fabrication processes. Since the ultimate goal of this Ph.D. study is integration of our fabricated TFTs on a flexible platform, finding a low-temperature deposition technique was one of the first steps in our device fabrication process. PECVD is one

the sub-branches of the chemical vapor deposition (CVD) process, in which purely thermal energy is employed to generate the reactive species. However, in the PECVD process, high-quality films can be deposited at much lower substrate temperatures than those of the conventional CVD process, by using glow discharge during the deposition process. In addition, PECVD technique is currently being used in the a-Si and LTPS TFT industries, which makes this deposition technique one of the most favorable compared to other unit-process techniques such as ALD. Due to the above advantages, PECVD was chosen for deposition of the gate dielectric in this research. However, current display industries usually use a relatively high-temperature (~300°C) process for deposition of high quality PECVD SiN<sub>x</sub> or SiO<sub>x</sub> dielectrics. However, this approach is not compatible with the low-melting point conventional polymeric substrates. Hence, understanding the problems involved in fabrication of TFTs using low-temperature conventional PECVD nitride and oxide dielectrics and proposing a solution will be very helpful in developing the next generation of large-area flexible electronics. Figure 2-5 exhibits the PECVD system used in this research to deposit insulator materials.

Figure 2-5 PECVD system used in this research to deposit insulator materials.

### 2.2.3. Electron beam evaporation (EBE)

It is reported that hydrogen (H) and oxygen deficiencies are two of the main sources of the unintentional doping of metal oxide channel layers, which could result in a highly conductive channel layer and degradation of TFT performance. Plasma damage has been found to be one of the main origins of oxygen deficiency formation. On the other hand, H-based gases such as SiH<sub>4</sub>, and NH<sub>3</sub> are recognized as among the main causes for the unintentional doping of H during fabrication. Both are considered big issues for the PECVD deposition technique, which takes advantage of both glow discharge and H-rich gases for deposition of conventional nitride and oxide materials. Hence, in this study, in order to prevent unintentional doping of the IGZO channel layer, and to get away from plasma damage and hydrogen contamination during the deposition, electron beam evaporation (EBE) technique was selected. In this method the deposition of thin-films involves the evaporation of materials from a solid into a vapor that condenses back to the solid

state to form a thin-film on a separate substrate. There is no need to use glow discharge and H-based gasses. It is worth noting that in EBE deposition technique a high energy electron beam is used to heat the source material. Figure 2-6 shows the EBE system used in this Ph.D. study to deposit the oxide dielectric layer.

Figure 2-6 EBE system used in this research.

#### 2.2.4. Thin-film patterning

Fabricating semiconductor devices requires that deposited thin-films be patterned. Common thin-film patterning techniques include (1) photolithography, (2) lift-off processes, and (3) shadow mask patterning. When an appropriate etching-process is available, having etch-selectivity between different layers, photolithographically patterned etch masks provide a direct approach to pattern different layers in a device structure. However, when a suitable etch-process is not available and the etch-selectivity between the device layers is poor, a lift-off patterning technique needs to be employed. As an example, MO-TFT device fabrication process typically do not have high etch

selectivity between the oxide semiconductor and the gate dielectric for TFT fabrication. This property of the two layers prevents the use of conventional photolithographic patterning and etching to define different layers in the device structure. This problem is magnified when the layers used for electrical contact to the semiconductor are the same such as the use of semiconducting IGZO channel layer and conducting IGZO transparent contacts that will be described in later chapters. In order to fabricate optically transparent IGZO TFTs using IGZO transparent contacts, a lift-off process for the source and drain patterning is typically required. Alternatively, shadow mask patterning, which is not the focus of this research, may be used to define the patterns in which a physical mask is used to block the path of incoming atoms during the deposition process and to define the patterns. However, the resolution of this technique is not as good as photo lithographically defined etch masks.

#### 2.3. Flexible Electronics

Flexible electronics is an emerging technology consisting of robust, light weight, conformal, bendable, and low-cost electronic systems. Due to these unique properties, flexible electronics enables applications in advanced large-area electronics for displays, sensors, medical devices, solar cells, and smart electronic textiles that can bend and fold [43, 44]. The first step in the fabrication of flexible transparent electronic devices is choosing an appropriate flexible substrate. The ideal flexible substrate needs to be rollable, low cost and transparent. In addition, it needs to be resistant against chemical attack, have low permeability to water and oxygen, and to be dimensionally stable under thermal processing steps.

Flexible substrates can be divided into three main categories: (1) metal foils [40], (2) flexible glasses [26], (3) and polymeric substrates [19]. Metal foils can tolerate much higher processing temperature and much higher dimensional stability than polymeric substrates [45]. They have

strong resistance to water vapor and oxygen diffusion. In addition, metal foils have a low coefficient of thermal expansion (CTE). All these advantages make this category of flexible substrates one of the most promising candidates in the field of flexible electronics where optical transparency is not required. However, due to the relatively rough surface of metal foils (originated from rolling mill marks) and their high conductivity, they need to be coated by an insulating spinon-glass (SOG) planarization layer before being applied as flexible substrates in device fabrication processes. Another category of flexible substrate is thin glass sheets (thickness < 100 µm). Flexible glass substrates offer superior optical transparency and perfect barrier layer properties against water vapor and oxygen atoms [45]. They have a low CTE and demonstrate ultra-smooth surface topography. However, this class of flexible substrates is highly sensitive to breaking and cracking, preventing their application in mass-production of large-area flexible electronics. The third category of flexible substrates is the polymeric substrates, among which polyethylene terephthalate (PET), polycarbonate (PC), polyethylene napthalate (PEN), and polyethersulfone (PES) have been extensively studied as flexible substrates for the development of flexible devices. Of the abovementioned candidates, PEN substrates are favored due to its high Young's module, high transparency, compatibility with microfabrication processes, and low cost. In addition, its thermal and dimensional properties are better than those of PET substrates. However, due to the low thermal resistance and high thermal expansion of polymeric substrates, the maximum process temperature needs to be lower than 150°C if it is to be used for low-cost transparent organic substrates.

Having a low-temperature processed high-performance TFT is one of the most challenging areas in developing large-area flexible electronics. Several reports have demonstrated fabrication of TFTs on flexible substrates based on different channel layer materials such as amorphous silicon

(a-Si), organic semiconductors, low-temperature polycrystalline silicon (LTPS) and metal semiconducting oxides. However, many of these materials do not possess all the ideal requirements for high-performance large-area advanced devices [2, 46-48]. Organic and a-Si based TFTs are not acceptable due to their low field-effect mobility. On the other hand, although LTPS demonstrates high mobility, its processing complexity and cost along with its nonuniform grain size over large areas make LTPS a less than optimal choice for low-cost high-performance flexible electronics. On the other hand, MO TFTs have demonstrated acceptable electrical characteristics with high field-effect mobility, low threshold voltages and excellent uniformity even when deposited at relatively low temperatures. Recently, a few research groups have reported the feasibility of fabricating flexible metal-oxide based TFTs. Table 2-1 compares these studies in terms of the type of flexible substrate, dielectric material used, gate dielectric deposition technique, optical transparency, maximum process temperature, and source/drain patterning techniques. Taking advantages of both the function of transparency and the superior electrical properties of MO TFTs at low temperature, MO TFTs are one of the most promising candidates for the development of large-area transparent flexible electronics.

Table 2-1 Materials, deposition and patterning techniques, maximum process temperature and optical transparency of the previous works on flexible IGZO TFTs.

| Type of substrates?          | Polymeric substrates                                        | Metal foils      | Flexible         | Glossy paper                        |

|------------------------------|-------------------------------------------------------------|------------------|------------------|-------------------------------------|

|                              |                                                             | [40]             | glasses [26]     | [49]                                |

|                              |                                                             |                  |                  |                                     |

| Type of gate dielectrics?    | Al <sub>2</sub> O <sub>3</sub> : [28, 35, 50],              | SiO <sub>x</sub> | SiN <sub>x</sub> | Methyl-siloxane<br>based dielectric |

|                              | SiN <sub>x</sub> :[19],                                     |                  |                  |                                     |

|                              | SiO <sub>x</sub> :[51],                                     |                  |                  |                                     |

|                              | HfO <sub>2</sub> /TiO <sub>2</sub> /HfO <sub>2</sub> : [29] |                  |                  |                                     |

|                              |                                                             |                  |                  |                                     |

| Deposition technique?        | ALD: [28, 35, 50],                                          | PECVD            | PECVD            | Spin coating                        |

|                              | PECVD: [19],                                                |                  |                  |                                     |

|                              | e-beam evaporation: [29]                                    |                  |                  |                                     |

| Optically transparent?       | No                                                          | No               | Yes              | No                                  |

|                              |                                                             |                  |                  |                                     |

| Maximum process temperature? | 150°C: [28, 35, 50],                                        | 300°C            | 300°C            | 150°C                               |

|                              | 200°C: [51],                                                |                  |                  |                                     |

|                              | 350°C: [19]                                                 |                  |                  |                                     |

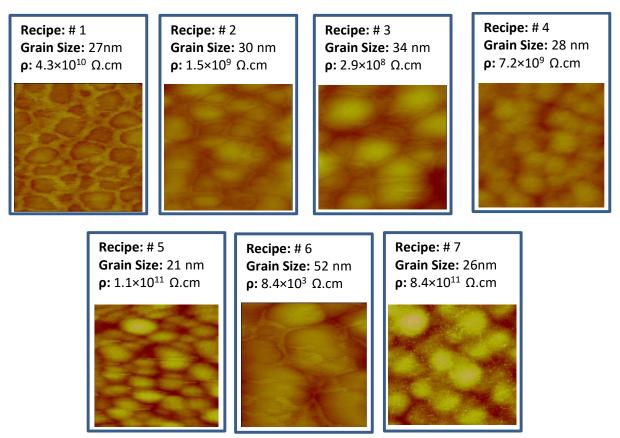

| Patterning approach?         | Wet or dry etching:<br>No[28, 35, 50, 51],                  | Not applicable   | No               | Not applicable                      |