# Predictable Cache Coherence Protocols for Mixed-Time-Criticality Multi-core Systems

by

Nivedita Sritharan

A thesis

presented to the University of Waterloo

in fulfillment of the

thesis requirement for the degree of

Master of Applied Science

in

Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2017

© Nivedita Sritharan 2017

This thesis consists of material all of which I authored or co-authored: see Statement of Contributions included in the thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### **Statement of Contributions**

In Chapters 6, 7, 8, Hassan, M., Kaushik, A. M. and Patel, H., aided in formalising the idea of HourGlass, provided inputs on the architectural details of the protocol and timing analysis. Hassan, M. aided in writing the analysis for HourGlass(H-DD-WC-0). Kaushik, A. M., helped in Section 7.1 of Chapter 7.

#### Abstract

Modern real-time systems consist of a combination of hard real-time, firm real-time and soft real-time tasks. Hard real-time (HRT) tasks mandate strict timing requirements by requiring that a static timing analysis can be performed to compute a worst-case latency (WCL) bound. Firm real-time (FRT) and soft real-time (SRT) tasks, on the other hand, do not impose such stringent requirements. Instead, they tolerate infrequent violations of deadlines in favour of improved average-case performance. When deploying such a system on a multi-core platform, the hardware resources such as the main memory, caches and shared bus are shared between the tasks. This results in interference by FRT or SRT tasks on HRT tasks, which complicates the timing analysis for HRT tasks, and potentially yields unbounded WCL. This thesis presents a time-based cache coherence protocol, HourGlass, to predictably share data in a multi-core system across different criticality tasks. HourGlass is derived from the conventional Modified Shared Invalid (MSI) cache coherence protocol, and it is equipped with a timer mechanism that allows the cores to hold a valid copy of data in its private cache for certain duration. HourGlass is designed to ensure WCL bounds for HRT tasks, and it also provides performance improvements for FRT and SRT tasks. Such a coherence protocol encourages a trade-off between the WCL bounds for hard real-time tasks, and performance offered to firm or soft real-time tasks with the help of timer mechanisms. HourGlass was prototyped in gem5, a micro-architectural simulator, and evaluated with multi-threaded benchmarks.

#### Acknowledgements

I express my deep gratitude to my supervisor, Professor Hiren Patel, for his patience, encouragement, and training during my graduate studies. This thesis would not be possible without his support and guidance. I thank my readers for reviewing this thesis and providing valuable feedback: Professor Rodolfo Pellizzoni and Professor Nachiket Kapre.

I thank my colleagues in the Computer Architecture and Embedded Systems Research (CAESR) group at University of Waterloo for the valuable discussions, guidance and support: Yunling Cui, Mohammed Hassan, Anirudh M. Kaushik, and Paulos Tegegn.

I thank my parents for their endless support and encouragement throughout my life. I am grateful to them for always believing in me and helping me in fulfilling my dreams. I am thankful to my grandparents, who supported me in all my decisions and showered me with blessings and love.

I also thank my brother, Nikhil, without whose constant encouragement I would not have pursued my graduate studies. I am also grateful to my family, who were always there for me when I was homesick: Renuka, Kemburaj, Anu, Prabakaran, Kunal, Akkilaa, Vishal, Janani, Ajit, Krithika.

Special thanks to my wonderful friends here at Waterloo, who provided great moral support and made my stay here more lively and enjoyable: Kritika, Arshee, Jacqueline, Meghana, Namrah and Rabeeah.

Finally, I thank the Almighty for giving me the strength to complete my graduate studies.

#### Dedication

This thesis is dedicated to my parents, Radhika Sritharan and V. Sritharan, who have supported and encouraged me throughout my life. This thesis is possible only because of their constant love and sacrifices.

## Table of Contents

| List of Tables |       |                                           | X  |  |

|----------------|-------|-------------------------------------------|----|--|

| Li             | st of | Figures                                   | xi |  |

| 1              | Intr  | roduction                                 | 1  |  |

| 2              | Rel   | ated Work                                 | 4  |  |

|                | 2.1   | Real-time systems                         | 4  |  |

|                | 2.2   | Mixed time-criticality systems            | 5  |  |

|                | 2.3   | Bus arbitration                           | 6  |  |

|                | 2.4   | Time-based coherence protocol             | 7  |  |

| 3              | Bac   | kground                                   | 9  |  |

|                | 3.1   | Cache coherence                           | 9  |  |

|                |       | 3.1.1 Coherence protocol                  | 11 |  |

|                | 3.2   | Mixed time-criticality multi-core systems | 13 |  |

|                |       | 3.2.1 Arbitration schemes                 | 14 |  |

| 4              | Sys   | tem Model                                 | 16 |  |

| 5 | Bus | Arbitration schemes                                                           | <b>2</b> 0 |

|---|-----|-------------------------------------------------------------------------------|------------|

|   | 5.1 | Dedicated slots for all cores (ALL-DD)                                        | 21         |

|   | 5.2 | Dedicated slots for HRT cores with Non work conserving arbitration (H-DD-NWC) | 22         |

|   | 5.3 | Dedicated slots for HRT cores with Work-conserving arbitration (H-DD-WC)      | 23         |

| 6 | Use | of Criticality-aware Bus Arbitration and Timers - an Illustration             | <b>25</b>  |

| 7 | Ηοι | ırGlass                                                                       | 30         |

|   | 7.1 | Architectural Modifications                                                   | 30         |

|   |     | 7.1.1 Architectural modifications to shared bus                               | 31         |

|   |     | 7.1.2 Architectural modifications to cache controllers                        | 33         |

|   |     | 7.1.3 Hardware overhead                                                       | 35         |

|   | 7.2 | Cache Coherence Protocol Modifications                                        | 35         |

|   |     | 7.2.1 Modifications for Criticality awareness                                 | 37         |

|   |     | 7.2.2 Support for Timers                                                      | 39         |

|   |     | 7.2.3 Illustrative Examples                                                   | 40         |

| 8 | Tim | ning Analysis                                                                 | 47         |

|   | 8.1 | Timing Analysis for HourGlass(H-DD-NWC)                                       | 49         |

|   |     | 8.1.1 Bound for HRT cores                                                     | 50         |

|   |     | 8.1.2 Bound for FRT cores                                                     | 60         |

|   | 8.2 | Timing Analysis for HourGlass(H-DD-WC)                                        | 71         |

|   |     | 8.2.1 Bound for HRT cores                                                     | 71         |

|   |     | 8.2.2 Bound for FRT cores                                                     | 78         |

| 9 | Eva | luation                                                                       | 86         |

|   | 9.1 | Data correctness and protocol verification                                    | 87         |

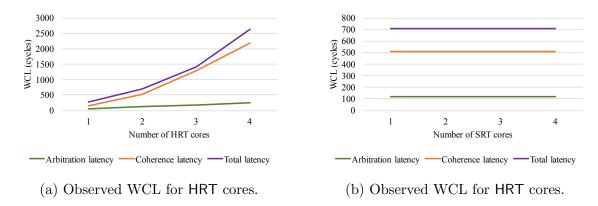

|   | 9.2 | Bounding memory access latencies                                              | 87         |

| 9.3    | Comparison of per request WCL bounds of HourGlass with other approaches | 89  |

|--------|-------------------------------------------------------------------------|-----|

| 9.4    | Comparison with other approaches                                        | 91  |

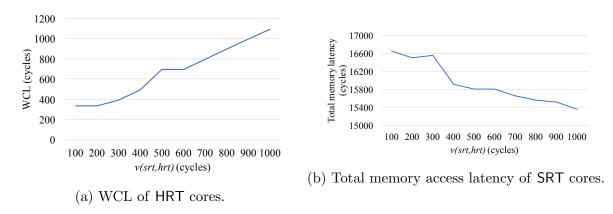

| 9.5    | Effect of timers on the performance of {FRT,SRT} cores                  | 95  |

|        | 9.5.1 Effect on HourGlass(H-DD-NWC)                                     | 97  |

|        | 9.5.2 Effect on HourGlass(H-DD-WC)                                      | 98  |

|        | 9.5.3 Effect on HourGlass(H-DD-WC-0)                                    | 98  |

| 9.6    | Scalability                                                             | 99  |

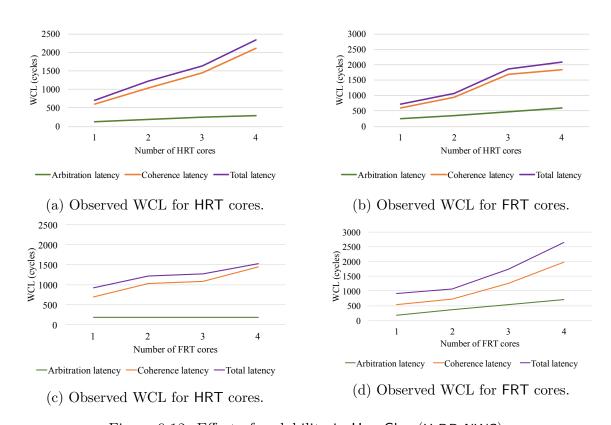

|        | 9.6.1 Effect on HourGlass(H-DD-NWC)                                     | 99  |

|        | 9.6.2 Effect on HourGlass(H-DD-WC)                                      | 100 |

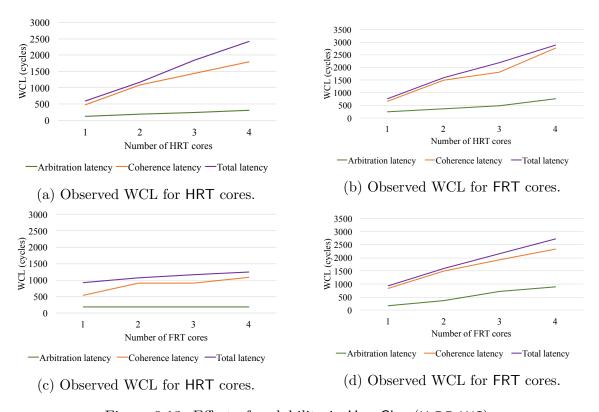

|        | 9.6.3 Effect on HourGlass(H-DD-WC-0)                                    | 101 |

| 10 Coı | nclusion and Future Work                                                | 103 |

| Refere | ences                                                                   | 105 |

## List of Tables

| 7.1 | State transitions at the private cache                                                                     | 36 |

|-----|------------------------------------------------------------------------------------------------------------|----|

| 7.2 | Different state transitions based on core criticality and issuance of requests in slack or dedicated slots | 38 |

| 7.3 | State transitions at the shared memory                                                                     | 38 |

| A1  | HourGlass configurations                                                                                   | 89 |

## List of Figures

| 3.1 | Cache Coherence Protocol                                                  | 10 |

|-----|---------------------------------------------------------------------------|----|

| 3.2 | MSI Cache Coherence Protocol                                              | 12 |

| 3.3 | Cache Coherence Protocol with states                                      | 13 |

| 3.4 | Mixed time-criticality multi-core system                                  | 14 |

| 4.1 | Mixed time-criticality multi-core system                                  | 17 |

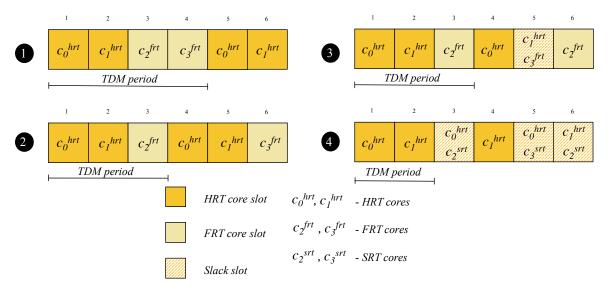

| 5.1 | Bus arbitration schemes                                                   | 21 |

| 6.1 | PMSI cache coherence protocol with fixed priority arbitration             | 26 |

| 6.2 | Proposed solution with timers for SRT cores                               | 28 |

| 6.3 | Proposed solution with timers for HRT cores                               | 29 |

| 7.1 | Architectural Modifications.                                              | 31 |

| 7.2 | Multiple pending requests from HRT and SRT cores                          | 41 |

| 7.3 | Multiple sharers.                                                         | 43 |

| 7.4 | Multiple pending requests in HourGlass(H-DD-WC)                           | 44 |

| 8.1 | Different latency components per request of a core                        | 48 |

| 8.2 | Illustration for the latency due to data transfer at requesting core slot | 49 |

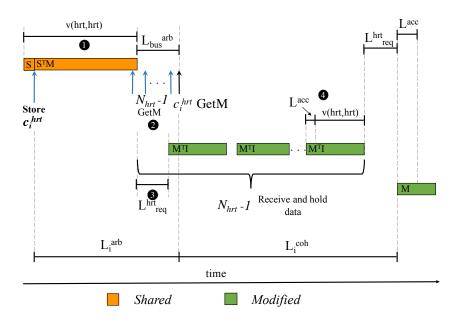

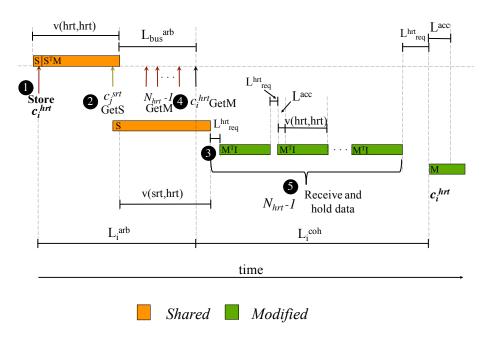

| 8.3 | Critical Instance for H-DD-NWC HRT core - Read-Write Unshared             | 52 |

| 8.4 | Critical Instance for H-DD-NWC HRT core - Read-Write Shared               | 56 |

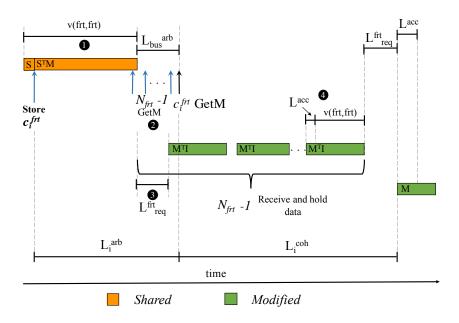

| 8.5 | Critical Instance for H-DD-NWC FRT core - Read-Write Unshared             | 63 |

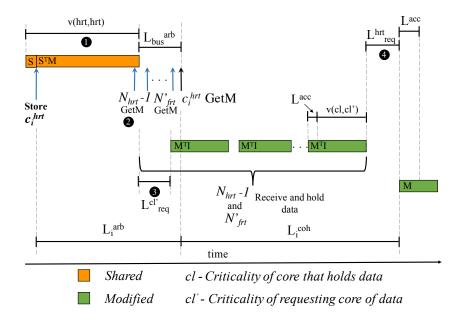

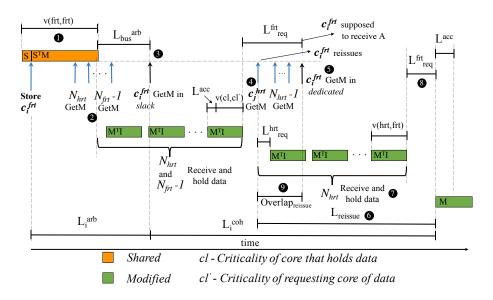

| 8.6  | Critical Instance for H-DD-NWC FRT core - Read-Write Shared             | 67  |

|------|-------------------------------------------------------------------------|-----|

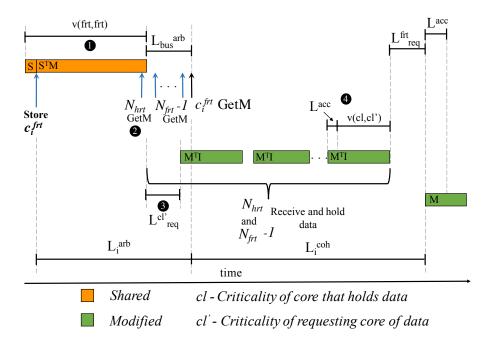

| 8.7  | Critical Instance for H-DD-WC-0 HRT core - Read-Write Shared            | 72  |

| 8.8  | Critical Instance for H-DD-WC FRT core - Read-Write Shared              | 80  |

|      |                                                                         |     |

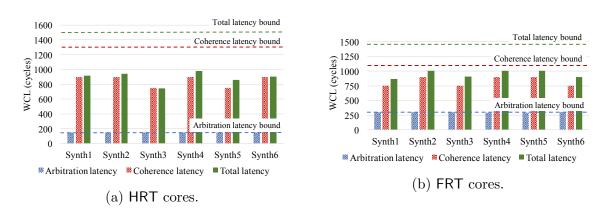

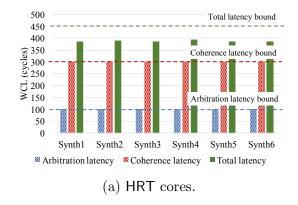

| 9.1  | Observed WCL components for HourGlass(H-DD-NWC)                         | 87  |

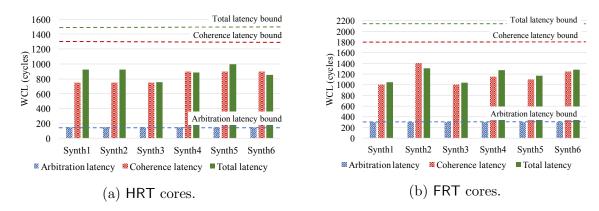

| 9.2  | Observed WCL components for $HourGlass(H-DD-WC)$                        | 88  |

| 9.3  | Observed WCL components for $HourGlass(H\text{-}DD\text{-}WC\text{-}0)$ | 88  |

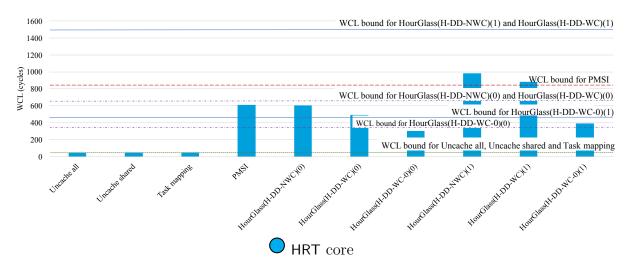

| 9.4  | Observed per request WCL of HRT cores for all real-time approaches      | 90  |

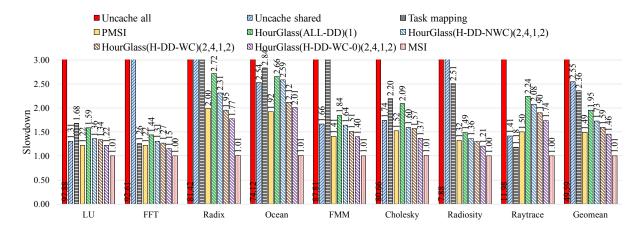

| 9.5  | Total execution time slowdown compared to MESI protocol                 | 91  |

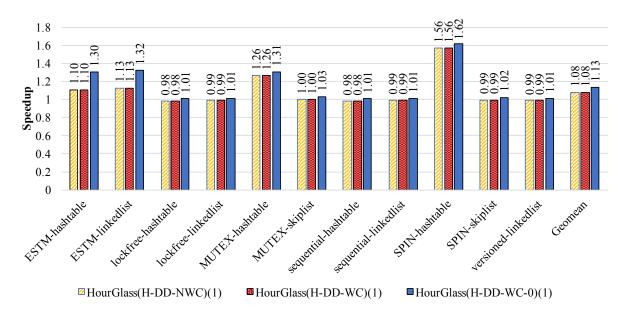

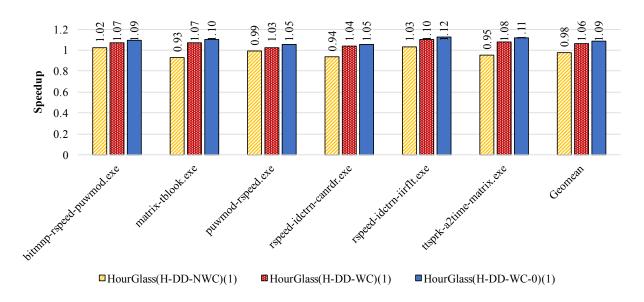

| 9.6  | Speedup compared to PMSI protocol - Synchrobench                        | 93  |

| 9.7  | Speedup compared to PMSI protocol - AutoBench 2.0                       | 94  |

| 9.8  | Speedup compared to PMSI protocol - Synthetic benchmarks                | 94  |

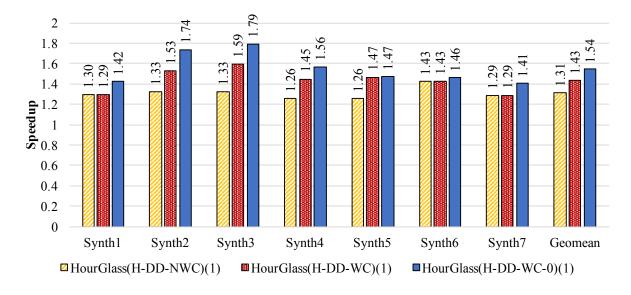

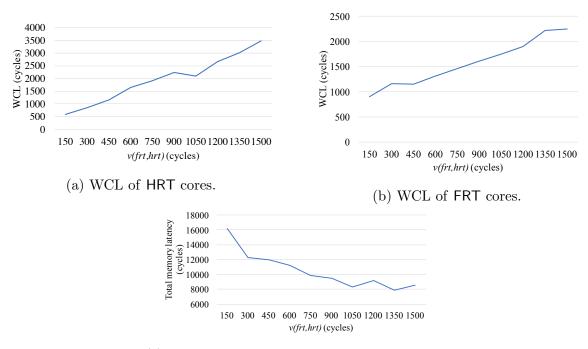

| 9.9  | Effect of timers in $HourGlass(H-DD-NWC)$                               | 96  |

| 9.10 | Effect of timers in $HourGlass(H-DD-WC)$                                | 97  |

| 9.11 | Effect of timers in HourGlass(H-DD-WC-0)                                | 98  |

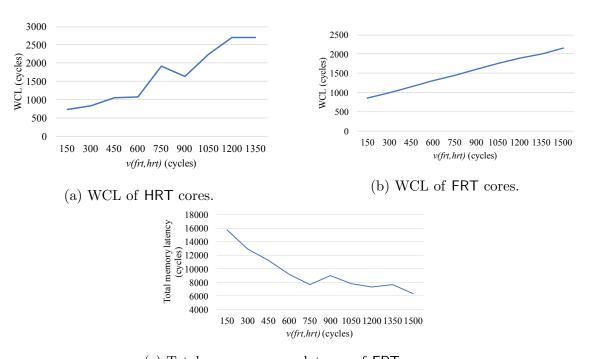

| 9.12 | Effect of scalability in HourGlass(H-DD-NWC)                            | 99  |

| 9.13 | Effect of scalability in $HourGlass(H-DD-WC)$                           | 101 |

| 9.14 | Effect of scalability in HourGlass(H-DD-WC-0)                           | 102 |

## Chapter 1

## Introduction

Modern real-time systems consist of a combination of tasks that may be of different criticality levels. These tasks may further share the underlying hardware resources when deployed on a computing platform. For certification, it is imperative to guarantee that tasks deemed to be of high criticality such as hard real-time tasks, never exceed their temporal requirements. Naturally, exceeding the temporal requirements for such hard real-time tasks (HRT) may render the system in a state with the potential for catastrophic consequences. However, modern real-time systems also consist of tasks that do not require such strict temporal requirements, but instead, those may only require best-effort service. Classical examples of such tasks include firm real-time tasks (FRT) and soft real-time tasks (SRT). A real-time system with a combination of HRT, FRT and SRT tasks is what we refer to as a mixed time-criticality system. Example domains include avionics and automotive (DO 178C and ISO 26262) [8], which have further extended the MCS model to multiple criticality levels. For instance, the Anti-lock Braking System (ABS) of the automotive is required to respond within a certain time duration, otherwise leading to life-threatening consequences (hard real-time). The automotive navigation system is required to provide results within a certain time duration, otherwise the result is invalid (firm real-time). However, they do not lead to life-threatening consequences like HRT tasks. The infotainment system, on the other hand, only requires best-effort service for the user and do not require any timing requirements (soft real-time).

As demands for more functionality and better performance from mixed time-criticality systems increase, there is noticeable interest in leveraging multi-core platforms to deploy such applications (Freescale P4080, [3]). The use of multi-core platforms reduces hardware cost, and it also offers true parallelism that applications can exploit for better performance. However, a primary concern in mixed time-criticality multi-core systems is the interference

caused between HRT, FRT and SRT tasks that share the hardware resources. This is because the FRT and SRT tasks, that do not have strict timing requirements, interfere with the HRT tasks. The contributing interference may originate from one or many of the hardware components such as the main memory, last-level caches, and shared buses. This interference can either cause the HRT tasks to miss their timing guarantees or the FRT and SRT tasks to contribute to the worst-case execution time (WCET) of HRT tasks. This significantly complicates the WCET analysis for HRT tasks because a static analysis of the HRT tasks must incorporate the effect of the FRT and SRT tasks' execution. Consequently, there is considerable interest in devising strategies to mitigate the impact of the interference such that HRT tasks are guaranteed to meet their requirements.

Multi-core platforms also introduce additional sources of interference. One such interference occurs when multiple tasks deployed on different cores access data that is temporarily stored in the private cache of a core. Since multiple threads may update the shared data, ensuring that any read of the shared data receives the most up-to-date write to the shared data is essential for correct execution. This involves transferring the data from one private cache, through the bus, to the requesting core's cache. Since the worst-case latency (WCL) to access data is a component of the task's WCET, predictably managing shared data across multiple tasks deployed on different cores remains a challenging problem [8].

General purpose micro-architectures use cache coherence in such scenarios. Cache coherence is a mechanism that maintains data coherently across the private caches of the cores to ensure correct and high performance execution of the application. However, conventional cache coherence protocols do not manage predictable transfer of shared data across the cores. Hence, prior work has focused on disabling caches to predictably share data across multiple cores [18, 24], or only caching non-shared data [10]. Another alternate solution in [10, 9, 16] proposed OS scheduler modifications to map tasks that share data to the same core and thereby avoid simultaneous caching of shared data across the cores. Though these solutions are suitable for real-time systems as they guarantee timing requirements for HRT tasks, they do not offer significant performance benefits. Recently, a hardware-based cache coherence protocol to predictably manage accesses to shared data in multi-cores called PMSI [21] was proposed. PMSI improved the average-case performance compared to other predictable approaches by allowing simultaneous cached shared data accesses. Thus cache coherence is a good solution to provide performance benefits for real-time systems. However, PMSI does not differentiate between different criticality tasks. It provides strict timing guarantees for all tasks (HRT, FRT or SRT). As a result, a FRT or SRT task would cost HRT tasks an opportunity for tighter worst-case latency bounds by providing unnecessary strict timing guarantees for FRT or SRT tasks. Furthermore, PMSI does not offer any mechanisms to encourage FRT and SRT tasks to improve their average-case performance. Hence, it is beneficial to provide support that allows simultaneous caching of shared data in a multi-core while being criticality-aware, such that HRT tasks have worst-case bounds, and FRT and SRT tasks are provided with performance benefits.

In this thesis, I propose HourGlass, a predictable cache coherence protocol that is criticality-aware. Specifically, HourGlass differentiates between HRT and FRT or SRT tasks and ensures that different requirements of these tasks are met. For HRT tasks, HourGlass ensures worst-case latency bounds. For FRT tasks, HourGlass provides timing guarantees but a looser bound compared to HRT tasks and also support to improve the average-case performance. For SRT tasks, HourGlass provides no guarantees but has support to improve the average-case performance. HourGlass is equipped with a timer-based mechanism to allow for FRT and SRT tasks to improve their performance. The timers allow for a trade-off between potentially improving performance of FRT or SRT tasks while loosening the WCL bounds of HRT tasks. This is acceptable as long as the HRT tasks continue to meet their temporal requirements. Further, HourGlass also has support that allows predictable sharing of data across HRT and FRT or SRT tasks. Most work do not focus on sharing data across different criticality tasks, however, this is conservative. As long as HRT tasks are guaranteed to meet the timing requirements, it is beneficial to support such accesses.

This thesis is organized into several sections as follows: In Chapter 2, I discuss the related work in mixed time-criticality systems and timer-mechanisms in cache coherence protocols. In Chapter 6, I discuss the motivation for HourGlass compared to the existing predictable cache coherence protocol PMSI. I also discuss different versions of HourGlass obtained by changing the criticality-aware bus arbitration. Chapter 5 gives an account of the different arbitration schemes considered in this work. Chapter 7 gives a detailed description of the hardware modifications and cache coherence protocol modifications required for HourGlass. I also provide a timing analysis for all versions of HourGlass, and describe the various latency components that contribute to the WCL of requests from HRT and FRT tasks in Chapter 8. I prototype HourGlass in gem5 [7], a cycle accurate micro-architectural simulator, and evaluate with multi-threaded benchmarks from SPLASH-2 [31] and synthetic benchmarks that exhibit maximum data sharing (Chapter 9). It is observed that the WCL of all memory requests from HRT tasks are within their analytical bounds, and that timers do encourage a trade-off between performance improvement from FRT or SRT tasks and WCL for HRT tasks.

## Chapter 2

## Related Work

#### 2.1 Real-time systems

Real-time systems ensure that the application does not only function correctly, but also meets the timing requirements. Tasks in the application should complete before a fixed worst-case execution deadline [21]. With increasing demand for real-time systems in several domains with importance to performance and cost-efficiency, there is a shift to multi-core systems. Multi-core real-time platforms contain interconnects, caches, and main memory that are shared by all the cores in the platform. Typical real-time models assume task isolation where there is no sharing of data across the tasks. This requires partioning of the memory based on the number of tasks. Authors in [21] identified that task isolation suffers from limitations such as memory underutilization and does not scale with increasing number of cores. Thus there is need for sharing data across the tasks for performance and cost efficiency. This further complicates the timing analysis for the accesses by the cores due to interference when multiple cores access the shared memory.

Prior work on sharing data across the cores focussed on bypassing the cache hierarchy to access shared data [18, 24]. Alternate solutions proposed in [10, 9, 16] make operating system (OS) changes to include data-sharing aware scheduler policies that identify tasks that share data. The tasks that share data are mapped to the same core and thereby avoid simultaneous access to shared data by multiple cores. Authors in [26] modified the application such that accesses to shared data are protected using lock mechanisms. As a result, shared data is accessed by only one core at any time instance. This approach, in the worst-case will lead to sequential execution of tasks, thereby overriding the effect of parallelism.

Hassan et al. [21] proposed a novel hardware cache coherence protocol Predictable Modified Shared Invalid Cache Coherence Protocol (PMSI) to manage shared data accesses. Compared to prior approaches that either bypass the cache or make application or OS modifications, PMSI allowed simultaneous access to shared data by multiple tasks, resulting in improved average-case execution time. It is a modified version of the standard MSI protocol that allows for sharing of data in a predictable manner. However, this thesis proposes a cache coherence protocol for a different platform of embedded systems - mixed time-criticality systems, that has a combination of hard real-time (HRT) and firm real-time (FRT) or soft real-time (SRT) tasks. PMSI does not differentiate between HRT and FRT or SRT tasks and assumes all tasks to be HRT, thereby providing timing guarantees for all tasks, even though SRT tasks do not require guarantees. Hence, I present HourGlass, that is criticality-aware with support for two time-criticality levels, which offers tighter worst-case latencies for HRT tasks.

#### 2.2 Mixed time-criticality systems

In recent years, work on real-time systems has shifted on allowing tasks of different levels of criticality to share a common hardware platform [6, 8]. Tasks are of different criticality levels based on the levels of safety assurance required by the system (DO 178C and ISO 26262) [8]. If we consider only the timing requirements of the tasks, the system includes a combination of tasks of different time-criticality levels: hard real-time (HRT), firm real-time (FRT) and soft real-time (SRT). For example, consider the automotive and avionics industries. The Anti-lock Braking Systems (ABS) of the automobile (hard real-time task) is strictly required to meet the deadline, otherwise leading to catastrophic behaviour. The automotive navigation system (firm real-time task), allows for infrequent misses to meet the deadline for better average-case performance; however the result is not valid. The entertainment system (soft real-time task), on the other hand, is not required to meet strict timing requirements, but only better average-case performance [5]. Such a system, that has a combination of different time-criticality levels deployed on the same platform, is termed as mixed time-criticality system [15].

Multi-core platform in mixed time-criticality systems form the topic of interest in recent embedded and real-time systems to benefit performance and efficiency. With tasks of different levels of criticality, co-existing on the same platform, allowing data sharing across different levels is an important concern. Most works focussed on disallowing data sharing across different criticality levels in order to maintain isolation of tasks of different criticality levels [8]. However, isolating tasks based on criticality on a multi-core platform is not

trivial, as it requires partitioning mechanisms at the cache and memory level [14]. Also, disallowing data sharing across criticality levels is an unnecessary restriction, that degrades the performance [34]. Alternatively, there are solutions that allow data sharing across criticality levels [14, 10, 34]. As long as the HRT tasks meet the required deadline, there is prospect in supporting data sharing across criticality levels.

In [10], Chisholm et al. studied the tradeoffs caused by data sharing across criticality levels through shared memory and propose techniques to reduce them. They proposed methods to bypass LLC (Last Level Cache) for data accessed by tasks of different criticality levels and accessed data from DRAM, eliminating unpredictable LLC interference across the tasks. They also proposed techniques to assign the tasks that share data to the same core, thereby avoiding concurrent access to the shared data, as a core executes only one task at a time. Giannopoulou et al. in [14] proposed time-triggered scheduling strategy that allows tasks of same criticality to access the shared resources (caches, memory bus) at a time to prevent tasks of different criticality levels from affecting the response time of HRT tasks. Zhao et al. proposed highest-locker criticality, priority-ceiling protocol (HLC-PCP) that used semaphores to access shared data. If a task, say SRT, wants to access the data that is shared by a HRT task, then the SRT task acquires the priority of the HRT task till it accesses the data, and then its priority is restored. They also showed that the blocking of shared resources by different criticality levels is bounded and hence there is predictable data sharing across criticality levels. These prior work focussed on adding modifications to the scheduling mechanisms [34, 14] or to the OS [10]. While these mechanisms work well for systems that do not use caches for shared data, for better performance there is a need for a mechanism that makes use of caches for shared data. In this work, I propose a hardware cache coherence protocol along with a predictable arbitration scheme that handles data sharing in a predictable manner in a mixed time-criticality system. I assume a system model similar to [13], where tasks of same criticality are mapped to the same core. Hence the core inherits the criticality of the tasks that are mapped to it.

#### 2.3 Bus arbitration

Bus arbiters for mixed time-criticality systems are different from those for real-time systems, as they must support tasks of different criticality levels in a predictable way. There are several research efforts that provide explicit support for different criticalities in bus arbiters [25, 19, 12, 11]. Paolieri et al. [25] presented a dual-criticality arbitration where HRT tasks (HRT) used round-robin arbitration, and whenever there were no requests from HRT, SRT tasks are serviced yielding a worst-case bound for HRT. Hassan et al. [19] pre-

sented CArb, a statically scheduled two-level bus arbitration scheme that used harmonic weighted round-robin (HWRR) arbitration. The first level performed HWRR amongst criticality classes, and the second among tasks within a criticality class. CArb is not only criticality-aware, but also requirement-aware as it allocates services to tasks based on their requirements. Cilku et al. [12, 11] proposed a two-layer arbiter that distinguished between memory requests from HRT and FRT tasks. Their approach used TDM arbitration such that HRT tasks were pre-assigned slots in the TDM schedule after which a fixed number of slots were reserved to service requests from FRT tasks. Within the slots reserved for FRT tasks, round-robin was performed. Gomony et al. [15] proposed work-conserving arbitration scheme by allocating slack slots to FRT tasks to improve the average-case performance. HourGlass takes inspiration from Paolieri et al. [25], Cilku et al. [12, 11] and Gomony et al. [15]. I consider different combination of arbitration schemes that are criticality-aware and provide varying worst-case latency bounds for the cores, that is explained in Chapter 5.

#### 2.4 Time-based coherence protocol

Several works on timestamp-based cache coherence protocols were proposed such as [27, 28, 32] as alternative techniques to the standard directory-based protocols to reduce network traffic and address the scalability issue of directory protocols. Shim et al. presented Library Cache Coherence (LCC) in [27] where the cache lines are held for a certain time duration, which is maintained by a global timer. In the presence of multiple sharers, a write to a cache line is stalled until the cache lines held by the sharers invalidate after their timer duration. This timestamp-based configuration reduced the network traffic for directory protocols. Singh et al. in [28] proposed time-based cache coherence called Temporal Coherence (TC) to minimize the network traffic overheads for Graphics Processing Unit (GPU) architecture. While LCC focussed on a time-based coherence for a system that implemented sequential consistency, TC focussed on Release Consistency model. TC used timestamp-based fence instructions to avoid the stalling of writes. Yu et al. proposed a novel cache coherence protocol Tardis [32], that is simpler and more scalable compared to the standard directory protocol. Tardis is similar to LCC, but it does not require a globally synchronized clock. It maintains sequential consistency by storing the logical time of the read and write accesses. These prior work on time-based coherence used timers to reduce network traffic for general-purpose multi-core systems and GPU architecture. However, in HourGlass, we use the timer concept to provide differential services to the cores based on their criticality, focusing on providing improved average-case performance for FRT or SRT tasks. A cache line is held for a pre-defined time duration by a core in its private cache, even if it is requested by other cores, so that repeated reads or writes to the cache line from the core are cache hits, thus improving the performance of FRT and SRT tasks.

## Chapter 3

## Background

This chapter gives a brief introduction of cache coherence in a multi-core system and the conventional cache coherence protocol. This also provides a background on the mixed time-criticality multi-core system and the bus arbitration schemes used in this work.

#### 3.1 Cache coherence

Multi-core systems share data between cores by accessing addresses within a shared address space. Modern multi-core platforms implement private cache hierarchies that exploit spatial and temporal locality to improve the application's performance. Hence, shared or private data may reside in the private cache hierarchy of multiple cores, allowing multiple copies of the data to co-exist across the cores simultaneously. For correct execution of parallel programs with shared data, it is essential that any core performing a read operation on the shared data obtains the most recent write to the shared data. Since multiple copies of the shared data are privately cached across multiple cores, there must be a mechanism to ensure that reads to the shared data receive the most up-to-date data. This is known as keeping data values coherent across multiple cores. A mechanism known as cache coherence is a solution that keeps shared data values coherent across multiple cores [29].

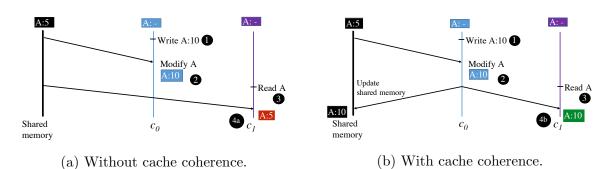

Figure 3.1a presents an example illustrating the need for a cache coherence protocol. This example shows two cores  $c_0$  and  $c_1$  accessing shared data A. Initially, the shared data variable A has a value of 5 in the shared memory and it is not cached in any of the private caches. ① Core  $c_0$  performs a write operation on A with a value of 10. This is a miss in  $c_0$ 's private cache requiring the shared memory to respond with A ②, which is later modified

Figure 3.1: Cache Coherence Protocol.

by  $c_0$  with the value of 10. Next,  $\mathfrak{F}$  core  $c_1$  performs a read operation on cache line A, which is a miss in its private cache. Without cache coherence, either the shared memory or  $c_0$  may respond to  $c_1$ 's request. In order to ensure that  $c_1$  reads the most up-to-date value of the shared data, the correct response should be from  $c_0$ 's private cache. Figure 3.1a presents a situation without cache coherence where the shared memory responds to the read by  $c_1$   $\mathfrak{F}$  a. This provides  $c_1$  with a stale value 5 of  $\mathfrak{F}$ . This results in the presence of two different copies of the same cache line in the system at the same time. This clearly indicates a need for a set of rules that ensures the value written by  $c_0$  is read by  $c_1$ .  $\mathfrak{F}$  Figure 3.1b continues the example assuming the existence of a cache coherence protocol. With the presence of a cache coherence protocol,  $c_0$ , on seeing a read request from another core, provides  $c_1$  with the latest value 10.  $c_0$  also writes back the value to the shared memory to maintain a coherent view of  $\mathfrak{F}$  across the system.

There are software and hardware techniques to implement cache coherence. Software approaches for cache coherence require additional software instructions to be added to manage the various copies of shared data explicitly by invalidating the data in the cache [2]. These additional instructions impact the performance [23]. It requires the programmer or the compiler to analyze the shared data and invalidate them in a timely manner to ensure the correct functioning of the application [2, 30]. On the other hand, a hardware implementation of cache coherence does not require any application or compiler modifications and is independent of the application. A hardware cache controller implements a protocol that enforces strict rules governing the coherent view of multiple cached copies of data across multiple cores. Hardware cache coherence works at the granularity of cache lines, which is the unit of data transfer in the memory hierarchy. Based on the implementation, hardware cache coherence can be realized either as a snoopy-bus-based protocol or a directory-based protocol [29]. In a snoopy bus-based protocol, each core broadcasts coherence messages to the shared bus on any read/write request. All the cores snoop the bus to observe the activ-

ity of all the cores. Directory-based cache coherence protocol uses a centralized directory that acts as an interconnect across multiple cores to maintain coherence. The cores and the shared memory communicate only via the directory. This work focuses on hardware cache coherence that use a snoopy shared bus implementation, which is appropriate for current multi-core platforms with eight cores or less (Freescale P4080, [3]) used in real-time multi-core systems.

#### 3.1.1 Coherence protocol

A cache coherence protocol is an implementation of a set of rules that ensures data coherence. This set of rules identifies states that denote the read and write permissions of cache lines, and transitions between these states that occur due to activities of other cores in the system on the same cache line. The Modified-Shared-Invalid (MSI) cache coherence protocol is a fundamental cache coherence protocol that several modern cache coherence protocols are based upon such as the MESIF, and MOESI protocols [29]. MSI consists of three stable states. The semantics for each of these states are as follows: 1) Invalid (I) indicates that the cache line does not have valid data. 2) Modified (M) represents that the core has modified the cache line data; hence, it has the most up-to-date data. Only one core can have a cache line in the modified state. 3) Shared (S) identifies that the cache line was read, but not modified. Multiple cores may have the same cache line in the shared state. This allows read hits in their respective private caches.

Cache coherence protocol also consists of transient states, which are intermediate states between stable states. These states represent whether the core is waiting for a data response, or waiting for the memory requests to be ordered on the shared bus. For instance, the transient state  $IM^{AD}$  is an intermediate state between the invalid (I) state and modified (M) state, when a write request is issued on the bus by a core with a cache line in I state. Here A denotes that the core is waiting for its coherence message to be broadcasted and D denotes that it is waiting for data response. A cache line changes states based on the activities of the cores. Once the write request is observed on the bus, it moves to another intermediate state  $IM^D$  denoting that the core awaits only a data response. Transitions between states occur by exchanging coherence messages between the cores and shared memory.

When discussing coherence activities, I refer to the *private core* to identify the core whose cache controller is under consideration, and *remote cores* as all other cores. Since every private cache implements the same set of rules in its cache controller, I distinguish requests made by the private core and those by the remote cores. To accomplish this, a

core views coherence messages on the bus as either Own or Other coherence messages. Own denotes that the cache controller observes a coherence message generated by its private core, and Other as a coherence message generated by remote cores.

#### MSI Cache Coherence Protocol

Figure 3.2: MSI Cache Coherence Protocol.

Figure 3.2 shows the state-transition diagram for the standard Modified-Shared-Invalid (MSI) cache coherence protocol. Recall that cores observe the memory activities of other cores in a snoopy bus based cache coherence implementation. Hence, the coherence messages are differentiated as Other and Own to distinguish messages generated by the private core versus the remote cores. The labels on the transitions denote requests generated either by the private core (read/write) or by remote cores resulting in coherence messages across the snooping bus. For example, a GetM(A) coherence message generated on a store request denotes that the private core wishes to perform a write on data A. Similarly, a GetS(A) coherence message is generated on a load request, and denotes a read by the private core on data A. A PutM(A) coherence message is generated during write-backs of dirty cache lines.

Consider the previous example scenario along with the information on different states as shown in Figure 3.3.  $c_0$  has the cache line A in a stable *modified* (M) state once it receives the data from the shared memory 2. Next, 3  $c_1$ , on observing a miss in its

Figure 3.3: Cache Coherence Protocol with states.

private cache for the read operation of A, broadcasts the message GetS(A) on the bus. As a result,  $c_0$  observes this coherence message as OtherGetS(A) and so responds with the upto-date value of A to  $c_1$  and moves to shared(S) state.  $c_1$ , on the other hand, observes the coherence message as OwnGetS(A) and moves to a transient state  $IS^D$ . Once it receives the correct data from  $c_1$ ,  $c_0$  completes the read operation and moves to shared state.

#### 3.2 Mixed time-criticality multi-core systems

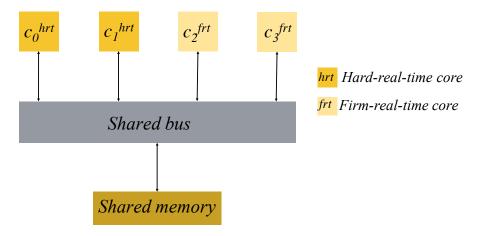

Recent work on multi-core real-time systems propose tasks of different criticality levels to share the same platform [6]. The tasks are either hard real-time (HRT), firm real-time (FRT) or soft real-time (SRT). These tasks have different requirements, based on their criticality, that must be guaranteed. For example, the deadline by which the task should finish may vary for different criticality levels. Hard real-time (HRT) tasks have strict timing requirements and it is necessary that the tasks complete before the pre-determined deadline. Firm real-time (FRT) tasks, on the other hand, are not required to always meet their deadlines. Instead they can tolerate occasional missed deadlines at the expense of degraded performance. These firm real-time tasks benefit from improved average-case performance. SRT tasks do not have any strict guaranteed requirements, but instead, may require best-effort service such as improved average-case performance. Such a system that has a combination of tasks, that have different timing requirements, are termed as mixed time-criticality systems. I focus on a mixed time-criticality system that consists of a combination of two time-criticality levels: HRT and FRT tasks or HRT and SRT tasks sharing the same platform. The cores in the multi-core system are differentiated as HRT

and FRT or SRT cores, where HRT tasks are mapped to HRT cores and FRT or SRT tasks are mapped to FRT or SRT cores. Figure 3.4 shows a four-core system with two HRT cores and two FRT cores. They are connected via a snoopy shared bus to the memory. Here shared memory represents the DRAM main memory.

Figure 3.4: Mixed time-criticality multi-core system.

#### 3.2.1 Arbitration schemes

There needs to be a predictable arbitration at the shared bus to decide which task in a real-time application gains access to the hardware resources (for example, the shared memory) via the bus. Time-division multiplexing (TDM) is one of the predictable arbitration schemes that provides timing isolation across the tasks [12] by assigning a dedicated time slot for each core. But with different levels of criticality, different arbitration schemes can be proposed by assigning varying number of guaranteed slots to the tasks based on their criticality. Chapter 2 discusses some prior work on bus-arbiter schemes in [25, 19, 12, 11] to support different criticality tasks to access the shared bus. Another way for a bus arbitration scheme would be to assign all HRT cores with a guaranteed slot, as they are always required to meet their timing requirements. On the other hand, since FRT cores tolerate some misses to timing deadlines, they can be assigned fewer slots and serviced in a roundrobin manner. The TDM arbitration can be work-conserving or non-work-conserving. Work-conserving TDM allows a core to use the slot of another core's dedicated slot if the other core has no pending request (slack slot). Non-work-conserving, on the other hand, leaves the slack slots idle. Work-conserving TDM is useful to improve performance as slack slots are used to service other pending requests. HRT cores are required only to meet the timing requirements, whereas the FRT or SRT cores require better average-case performance. Hence, the slack slots can be used to service requests from FRT or SRT cores to improve their performance [15].

## Chapter 4

## System Model

This work assumes a mixed-time-criticality multi-core real-time system consisting of a combination of tasks that have two different timing requirements. It assumes the task set to be  $\Gamma = \{\tau_1, \tau_2, \dots, \tau_m\}$  with m number of tasks, where  $\tau_i$  is a task that has pre-determined requirements to be met depending on its time-criticality and i indicates the task identifier. Based on their timing requirements, the tasks can be hard real-time, firm real-time or soft real-time tasks. Hard real-time (HRT) tasks mandate strict timing requirements and require that they always complete their execution before the deadline. Firm real-time (FRT) tasks, on the other hand, are not required to always meet their deadlines. Instead they can tolerate occasional missed deadlines at the expense of degraded performance. This allows firm real-time tasks to leverage techniques that improve its performance. Soft real-time (SRT) tasks are those that do no require any strict timing guarantees, but only benefit from improved average-case performance. I assume that the system consists of a combination of 2 levels of time-criticality -  $cl_1$  and  $cl_2$ , where  $cl_1$  are HRT tasks and  $cl_2$  are either FRT or SRT tasks. It can either have FRT tasks or SRT tasks along with HRT tasks based on the requirements of the second level for that application.

The multi-core platform has N in-order cores  $\{c_0, c_1, \ldots, c_{N-1}\}$ . Each core has its own private instruction cache (L1-I\$) and data cache (L1-D\$). The shared memory is assumed to be the main memory. The cores and the shared memory are interconnected with a snooping bus, which exchanges cache coherence messages between them. Additionally, there is a common cache data bus connecting the cores to support cache-to-cache transfers. It is assumed that once a data transfer over the bus starts, it cannot be preempted.

This work assumes that a single task is mapped onto a single core for the duration of the application's execution. Each core is associated with a logic that programs whether the core is a HRT, FRT or SRT core, based on the criticality of the task mapped to it. Each core in the multi-core system is characterized by the criticality of its task (cl) and the core identifier,  $c_i^{cl}$  where  $cl \in \{\text{hrt}, \text{frt}, \text{srt}\}$  and i indicates the core identifier. Memory request from HRT cores must have WCL guarantees per request whereas memory requests from FRT or SRT cores have no strict timing guarantees. However, FRT and SRT cores benefit from improved average-case performance. I denote the number of HRT cores as  $N_{\text{hrt}}$ , FRT cores as  $N_{\text{frt}}$  and SRT cores as  $N_{\text{srt}}$ . Since the system assumes only two levels of criticality, it is seen that  $N = N_{cl_1} + N_{cl_2}$ , where  $cl_1 \in \text{hrt}$  and  $cl_2 \in \{\text{frt}, \text{srt}\}$ . The number of HRT and FRT or SRT cores are set based on the number of tasks of different criticality required for the application. Each core is then programmed to be HRT, FRT or SRT based on the  $N_{\text{hrt}}$ ,  $N_{\text{frt}}$  or  $N_{\text{srt}}$ . HRT tasks are mapped to cores that are programmed as HRT, whereas FRT or SRT tasks are mapped to FRT or SRT cores. Hence, the core acquires the criticality of the task that is mapped to it and so tasks and cores are used interchangeably in this thesis. The tasks distributed across the multiple cores with different criticality levels can share data.

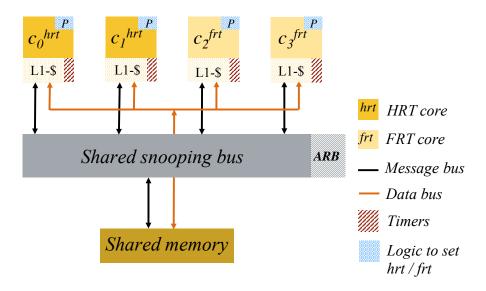

Figure 4.1 illustrates a system model assumed for this work. It consists of two HRT tasks and two FRT tasks, mapped on a four-core system. Hence two cores are programmed as HRT and two cores as FRT. Each core has a private L1 cache and the cores and shared memory are connected via the snoopy bus and the common data bus. The shared memory is the DRAM main memory.

Figure 4.1: Mixed time-criticality multi-core system.

The shared snooping bus uses a predictable arbitration scheme to arbitrate accesses to the shared memory from different cores. I assume Time Division Multiplexing (TDM) for predictable arbitration of memory accesses, although HourGlass can be extended to support any other predictable arbitration scheme. Some TDM slots are pre-assigned for certain cores, and these are termed as *dedicated* slots. In the *dedicated* slots, only the core that is assigned that slot can make a request. If the dedicated core has no pending request, then that slot is idle and is called a *slack* slot.

Chapter 5 describes the different arbitration schemes considered in this work. ALL-DD allocates dedicated slots for all the cores, irrespective of whether they are HRT, FRT or SRT. H-DD-NWC, in order to get tighter worst-case latency bounds for HRT cores, allocates dedicated slots for all the HRT cores, but only fewer dedicated slots to FRT cores. Among the few dedicated slots, the FRT cores are serviced in round-robin and the slack slots remain idle. To improve the performance of FRT cores, H-DD-NWC is modified to allow the slack slots to be utilized by the FRT cores to issue requests. This scheme is given by H-DD-WC. A special case of H-DD-WC is where no slots are dedicated to the second criticality level. This arbitration, H-DD-WC-0, can be utilized for SRT cores, that do not require a guaranteed bound. All HRT cores are assigned dedicated slots, whereas SRT cores use only the slack slots of HRT cores. Based on the arbitration scheme used, different version of HourGlass is chosen. In order to characterize this, I represent HourGlass as a function of the arbitration scheme chosen (arb) - HourGlass(arb). The hardware for arbitration is present at the shared bus, as shown in Figure 4.1. The bus arbitrates memory requests, data responses, and coherence messages.

I assume the TDM slot-width SW to be large enough to complete one data transfer from the shared memory to the private cache of a core, and the transfer of any necessary coherence messages. The transfer of coherence messages and data responses begin at the start of a TDM slot. I also assume that a core can issue only one memory request in its designated TDM slot. Further, a core is allowed to have only one pending request to the bus. The bus arbiter also supports fixed-priority arbitration to handle multiple pending requests from different cores. Requests from HRT cores are prioritized over the requests from FRT and SRT cores. Multiple pending requests from cores of the same criticality are serviced in First-Come First-Serve (FCFS) manner.

Each core contains timers that enable holding onto the cache line for a fixed time duration (cycles) even when it is requested by a remote core as shown in Figure 4.1. Once the timers expire, the private core responds to the coherence messages from the requesting remote cores. Two timers are associated with each cache line for a core. The countdown timers are denoted as  $t_n(A, c_n^{cl}, c_m^{cl})$  where  $t_n$  identifies the current value of the timers for a cache line A present in  $c_n$  where  $n, m \in \{0, 1, ..., N-1\}$  and  $cl \in \{\text{hrt}, \text{frt}, \text{srt}\}$ .  $c_n$  denotes

the core that has a valid copy of the cache line, and  $c_m$  denotes the requesting core. For example, assume that  $c_i$  is a HRT core, and  $c_j$  is a SRT core. Then,  $t_i(A, c_i^{\mathsf{hrt}}, c_j^{\mathsf{srt}})$  denotes the timer configuration for cache line A when a HRT core  $c_i^{\mathsf{hrt}}$  has the cache line A, and observes a memory request from a SRT core  $c_i^{\mathsf{srt}}$  for the same cache line A. Since there are two time-criticality levels -  $cl_1$  (HRT) and  $cl_2$  (frt or srt), a valid cache line in a  $cl_1$  core,  $c_i^{cl_1}$ , may receive requests for the cache line from a core of either criticality  $(cl_1 \text{ or } cl_2)$  resulting in two timer configurations  $t_i(A, c_i^{cl_1}, c_k^{cl_1})$ , and  $t_i(A, c_i^{cl_1}, c_l^{cl_2})$  where A is the cache line that is requested,  $c_k$  is a HRT core and  $c_l$  is either a FRT or SRT core. Notice that these two timer configurations identify the requesting core to be either of the two criticality levels. Similarly, a request to a valid cache line in a core of  $cl_2$  criticality  $c_i^{cl_2}$  also has two timer configurations  $t_j(A, c_j^{cl_2}, c_i^{cl_1})$ , and  $t_j(A, c_j^{cl_2}, c_l^{cl_2})$  where  $c_l$  is another  $cl_2$  core and A is the cache line. The timers are initialized with timeout values on receiving a valid copy of the cache line. I denote v(hrt, hrt) as the initial timeout value for a cache line present in the private cache of a HRT core, and requested by another HRT core, and  $v(hrt, cl_2)$ , where  $cl_2$  is either FRT or SRT, as the initial timeout value for a cache line present in the private cache of a HRT core, and requested by a FRT or SRT core. Similarly  $v(cl_2, hrt)$  and  $v(cl_2, cl_2)$ represent the initial timeout values for cache lines present in the private cache of a  $cl_2$  core, and requested by another HRT core and  $cl_2$  core respectively, where  $cl_2$  is either FRT or SRT. The timer configurations are set based on the requirements of the application, and they are not changed during application execution. Moreover, the timers are private to the core; hence, their values are not communicated to other cores.

In HourGlass, I assume that lock variables are not shared between the two criticality levels (HRT and FRT or HRT and SRT). Though HourGlass guarantees per request worst-case latency for HRT tasks, it is necessary to guarantee that the critical section of the task is also bounded in order to have a guaranteed bound for the task. There can be a case when a SRT core obtains the lock and does not release it as the requests are not predictable for SRT tasks. Other mixed criticality work use wait-free buffers to handle this. With the provision of timers in HourGlass, HourGlass can be extended to support sharing of locks across criticality levels. A core, on obtaining a lock variable, holds it for a particular time duration. This time duration can be set based on the upper bound on the duration of critical section for all HRT tasks. If SRT cores still hold the lock variables after this time duration, then they are released, thus providing guarantees for HRT tasks. In this thesis, for experimentation, I assume that FRT and SRT cores have an upper bound on the critical section that requires locking the mutex variables. Thus, this guarantees bounds for HRT tasks.

## Chapter 5

## Bus Arbitration schemes

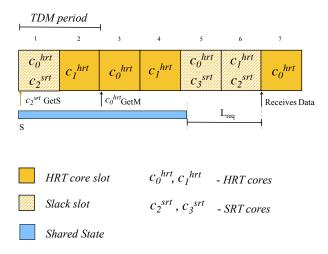

The cores in a multi-core platform access the shared memory and DRAM via the interconnecting shared bus. Read/write requests or cache coherence messages are broadcasted to other cores and shared memory using the shared bus. A bus arbiter arbitrates requests from all the cores, such that no core is starved from accessing the bus. For this, there needs to be a predictable bus arbitration scheme in order to avoid unbounded interference from different cores accessing the bus. HourGlass uses Time Division Multiplexing (TDM) for predictable arbitration of requests across the cores. TDM allocates slots of fixed time duration to each core in order to access the shared bus. It provides temporal isolation across the cores. I discuss different arbitration mechanisms that can be used in mixed time-criticality systems, that have different timing requirements for the tasks/cores. Memory requests from HRT cores must have worst-case latency (WCL) guarantees per request, whereas memory requests from FRT cores tolerate infrequent violations of timing guarantees. SRT cores, on the other hand, do not require strict timing guarantees. However, FRT and SRT cores benefit from improved average-case performance. In this thesis, for analysis and evaluation, I allocate only one slot per core in a TDM schedule. However, each core can be allocated more than one slot in a TDM schedule. Figure 5.1 illustrates the allocation of TDM slots to the cores for all the arbitration schemes discussed here. The example in the figure considers a system with four cores with two HRT cores and two FRT or SRT cores. As discussed in Chapter 4, the total number of cores in the system is represented as N, number of HRT cores as  $N_{\mathsf{hrt}}$ , number of FRT or SRT cores as  $N_{\mathsf{frt}}$  or  $N_{\mathsf{srt}}.$

Figure 5.1: Bus arbitration schemes.

### 5.1 Dedicated slots for all cores (ALL-DD)

ALL-DD allocates a dedicated TDM slot for each core, irrespective of its time-criticality. Assuming that the system has two levels of time-criticality with HRT and FRT cores, every HRT and FRT core is guaranteed a dedicated slot. Figure 5.1  $\bigcirc$  illustrates the allocation of slots using ALL-DD. The TDM repeats its schedule after this fixed allocation of slots to cores. The TDM period P is given by,

$$P = N \times SW$$

where N is the number of cores in the system and SW is the fixed slot width.

In Figure 5.1  $\bigcirc$  , each core is allocated a dedicated slot and TDM period P is 4 TDM slots. The TDM slot width SW is large enough to broadcast necessary coherence messages and complete one memory transfer. The worst-case arbitration latency  $(WCL_{arb})$  for any core is given by the time the core takes to gain access to the bus again after it has just missed its slot. The worst-case arbitration latency for HRT and FRT cores are as follows:

$$WCL_{arb}^{\mathsf{hrt}} = N \times SW$$

$$WCL_{arb}^{\mathsf{frt}} = N \times SW \tag{5.1}$$

In the worst-case, the request issued by a core  $c_i$  just missed its slot; hence, it has to wait for its next slot, which is after a TDM period. In ALL-DD, HRT and FRT cores have the same worst-case arbitration latency. This arbitration scheme makes no distinction between HRT and FRT cores, and this is a good policy for a real-time system with cores of same criticality level (for example, PMSI). However, for a system with different criticality levels, the arbiter should also be criticality-aware. HRT cores are required to have tight bounds, whereas FRT cores require performance improvements compared to guaranteed bounds. ALL-DD allocates dedicated slots for each FRT core, thus treating the FRT core as a HRT core. FRT cores are provided with strict timing guarantees which is not necessary; they benefit from improved performance. To this end, I discuss another arbitration scheme, H-DD-NWC.

## 5.2 Dedicated slots for HRT cores with Non work conserving arbitration (H-DD-NWC)

H-DD-NWC is criticality-aware and assumes a dual-layer arbiter similar to [12], with a fixed priority arbitration that gives priority to HRT cores. It allocates a dedicated slot for each HRT core, and few fixed number of dedicated slots to FRT cores. As a result, the WCL for HRT cores is tighter when compared to ALL-DD. Consider the number of slots allocated for all FRT cores be denoted as  $N_s^{\rm frt}$ , where  $N_s^{\rm frt} < N_{\rm frt}$ . Among the slots for FRT cores, Round-Robin (RR) arbitration is used, that ensures FRT cores are not starved. RR provides services to FRT cores based on pending FRT requests. If a FRT core has no pending request, then the next FRT core in the round-robin order is given access to the bus. This helps with the average-case performance improvement for FRT cores. In this arbitration, if the dedicated core does not have any pending request to be broadcasted on the bus, then that slot remains idle. Such an arbitration is non work conserving and the idle slot is termed as slack slot. The TDM period P for this arbitration is given by

$$P = (N_{\mathsf{hrt}} + N_s^{\mathsf{frt}}) \times SW$$

In Figure 5.1 ②, 2 slots are allocated to two HRT cores and 1 slot is allocated for FRT cores. The TDM period P is thus 3 TDM slots. Worst-case arbitration latency for the cores is given as follows:

$$WCL_{arb}^{\mathsf{hrt}} = (N_{\mathsf{hrt}} + N_s^{\mathsf{frt}}) \times SW$$

$$WCL_{arb}^{\mathsf{frt}} = \left\lceil \frac{N_{\mathsf{frt}}}{N_s^{\mathsf{frt}}} \right\rceil \times P \tag{5.2}$$

where P is the TDM period.

All the HRT cores are guaranteed a dedicated slot, and hence the worst-case arbitration latency for HRT cores is the TDM period. However, only  $N_s^{\mathsf{frt}}$  slots are allocated for FRT cores per TDM period. The remaining FRT cores are granted access to the bus in the next TDM period and hence  $WCL_{arb}^{\mathsf{frt}}$  is in terms of P.

# 5.3 Dedicated slots for HRT cores with Work-conserving arbitration (H-DD-WC)

The TDM arbitration in ALL-DD and H-DD-NWC assume non-work-conserving arbitration, where *slack* slots (no pending request in a *dedicated* slot from its dedicated core) remain idle. From experiments, it is observed that the HRT cores have low slot utilization resulting in more *slack* slots. Work-conserving TDM allows a core to use the slot of another core's dedicated slot if it is a *slack* slot and thus improves performance. However, HRT cores are needed only to meet guaranteed timing requirements, but not improved performance. The FRT and SRT cores, on the other hand, benefit from improved average-case performance. Hence, it makes sense to allow these cores to make use of the *slack* slots to improve their average-case performance.

FRT cores allow for occasional violation of worst-case latency bounds, but it is required to meet the bound for valid outcome. Hence, I assume an arbitration that considers the same policy as H-DD-NWC, along with work-conserving arbitration. All the HRT cores are allocated dedicated slots, whereas fixed number of dedicated slots are allocated to FRT cores. However, the slack slots of HRT cores are utilized to service requests from FRT cores. In Figure 5.1 illustrates this scheme. In the 5th TDM slot,  $c_1^{\rm hrt}$  has no pending request and hence this slack slot is used by FRT core  $c_3^{\rm frt}$ . By RR, the arbiter grants the 6th TDM slot to the next FRT core,  $c_2^{\rm frt}$ .

The TDM period P and the worst-case latency bound for HRT and FRT cores are the same as H-DD-NWC given by Equations 5.2. In the worst-case, there are no slack slots and hence the FRT cores are issued only in the dedicated slots.

SRT cores, on the other hand, do not require any guaranteed timing requirements. SRT cores only require better performance. Hence, I consider a special case of H-DD-WC, where dedicated slots are allocated only to HRT cores. I term this arbitration where no slots are dedicated to SRT cores as **H-DD-WC-0**. By not allocating dedicated slots for SRT cores, the TDM period is less and thus the worst-case latency bound for HRT cores is tighter.

Dedicated TDM slots are allocated only to HRT cores and the SRT cores are granted access only in *slack* slots of HRT cores.

Now the TDM period P is given by

$$P = N_{\mathsf{hrt}} \times SW$$

4 in Figure 5.1 shows an example using H-DD-WC-0. Since there are only 2 HRT cores, the TDM period is 2 TDM slots. Worst-case arbitration latency is given by

$$WCL_{arb}^{\mathsf{hrt}} = N_{\mathsf{hrt}} \times SW$$

(5.3)

The SRT cores, will not have a guaranteed bound, as they are not allocated a dedicated slot. The SRT cores access the bus depending on the availability of slack slots.

# Chapter 6

# Use of Criticality-aware Bus Arbitration and Timers - an Illustration

Cache coherence maintains a coherent view of multiple copies of shared data by propagating changes of one copy to the other copies systematically. However, conventional cache coherence protocols [29] do not distinguish between different time-criticality levels across the cores. Also, conventional cache coherence protocols lead to unpredictable scenarios, which is not suitable for real-time systems that require strict timing guarantees [21]. In [21], the authors propose invariants for predictable cache coherence and propose a protocol PMSI. However, in mixed-time-criticality systems, HRT, FRT and SRT cores have different timing requirements. Recall that HRT cores have strict timing requirements, whereas FRT and SRT cores benefit from improved performance, and allow occasional misses to deadlines. Hence, it is essential to differentiate requests from HRT, FRT or SRT cores in mixed time-criticality systems. It is necessary to reduce the interference suffered by HRT cores originating from other criticality levels to assist in tighter worst-case bounds while encouraging FRT or SRT cores to improve their average-case performance.

PMSI does not differentiate requests from HRT, FRT and SRT cores. Therefore, a FRT or SRT core in PMSI would be treated as a HRT core. This means the coherence state of a shared cache line in a HRT core is affected by the activities of the other criticality level by the mere fact that a TDM slot must be assigned to the FRT or SRT core. Consequently, introducing criticality-awareness in cache coherence can provide tighter worst-case bounds for HRT cores. An alternative is to make modifications to PMSI to support the two different

time-criticality levels considered for that application. Suppose that the bus arbitration policy is changed to distinguish requests from HRT and FRT or SRT cores. H-DD-NWC and H-DD-WC presented in Section 4 are criticality-aware. In contrast to the TDM arbitration used in PMSI, criticality-aware arbitration pre-allocates few slots (in case of FRT tasks) or no slots (in case of SRT tasks) to obtain tighter WCL bounds for HRT cores and allows FRT or SRT cores to utilize the *slack* slots in round-robin fashion to improve their performance. Chapter 5 gives a detailed account of the different arbitration schemes and their benefits over the conventional TDM arbitration.

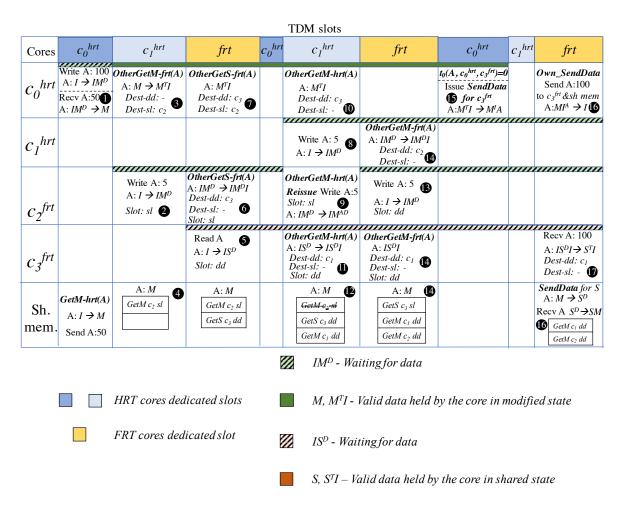

Assume that PMSI uses one of the criticality-aware arbitration schemes. The FRT cores do not always get a *dedicated* slot every TDM period when H-DD-NWC or H-DD-WC is used. In case of H-DD-WC-0, the SRT cores are never allocated a *dedicated* slot. Hence conventional PMSI will not be predictable with this arbitration, when a HRT core requests for a cache line that is held by a SRT core. This is explained in detail in Chapter 7. So, PMSI requires architectural and coherence protocol changes in order to support this criticality-aware bus arbitration. For the sake of simplicity, let us assume that PMSI also supports cache-to-cache transfers between cores, which it originally does not as presented by Hassan et al. [21]. Figure 6.1 illustrates this implementation of PMSI using H-DD-WC-0 arbitration, that provides for tighter worst-case latency (WCL) bounds for HRT cores by not allocating any TDM slots to SRT cores.

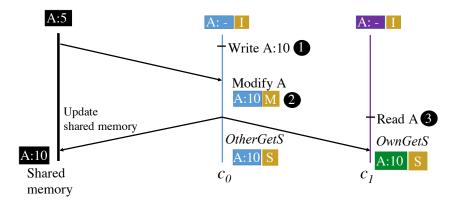

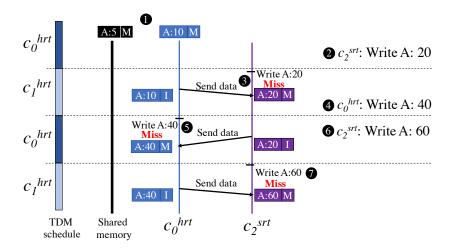

Figure 6.1: PMSI cache coherence protocol with fixed priority arbitration.

Figure 6.1 assumes a four-core multi-core system of HRT cores  $c_0^{\mathsf{hrt}}$ ,  $c_1^{\mathsf{hrt}}$ , and SRT cores  $c_2^{\mathsf{srt}}$ ,  $c_3^{\mathsf{srt}}$ . It shows the core activity for HRT core  $c_0^{\mathsf{hrt}}$  and SRT core  $c_2^{\mathsf{srt}}$ . Initially,  $c_0^{\mathsf{hrt}}$  has

data A in modified state **1**. At **2**,  $c_2^{\mathsf{srt}}$  has a write request. Since,  $c_1^{\mathsf{hrt}}$  does not have a pending memory request, the arbiter uses the slack slot to issue  $c_2^{\mathsf{srt}}$ 's write request to A. Since  $c_0^{\mathsf{hrt}}$  has the most up-to-date copy of A, it sends A to  $c_2^{\mathsf{srt}}$ , and invalidates its copy **3**. At **4**,  $c_0^{\mathsf{hrt}}$  has a write request to A. At **5**,  $c_0^{\mathsf{hrt}}$ 's write request is placed on the shared bus, and  $c_2^{\mathsf{srt}}$  sends the up-to-date data to  $c_0^{\mathsf{hrt}}$ , and invalidates its copy. At **6**,  $c_2^{\mathsf{srt}}$  has a write request to A. Since,  $c_1^{\mathsf{hrt}}$  does not have a pending request, the bus arbitration grants this slack slot to  $c_2^{\mathsf{srt}}$ 's pending write request, and completes its write request at **7**. Note that this example performs coherence correctly, but it requires only two TDM slots to be assigned to the HRT cores, as only the HRT cores require timing guarantees. With conventional PMSI, all four cores would need to be assigned at least one slot. Although this is a simple example, it illustrates that one can obtain tighter WCL bounds on HRT cores by using a criticality-aware bus arbitration.

Note that H-DD-WC-0 arbitration only ensures WCL bounds for HRT cores, and no guarantees on WCL or performance for SRT cores. The requests from SRT cores are satisfied depending on the availability of slack slots. It is desirable to provide SRT cores a mechanism to improve its performance while still ensuring WCL bounds for HRT cores. For example, in Figure 6.1, consider that the first write request to A from  $c_2^{\rm srt}$  (2) is succeeded by multiple read and write requests to A from  $c_2^{\rm srt}$  (not shown). Currently, requests from HRT cores to the same data results in  $c_2^{\rm srt}$ 's copy of A to be invalidated. This in turn results in cache misses for succeeding requests to A for the  $c_2^{\rm srt}$ . Further, consider that at 7,  $c_1^{\rm hrt}$  has some pending request and so  $c_1^{\rm hrt}$ 's slot cannot be utilized by  $c_2^{\rm srt}$ . The multiple read and write requests to A from  $c_2^{\rm srt}$  can be satisfied only when  $c_2^{\rm srt}$  obtains a slack slot. A mechanism that I propose in this work is to allow cores to hold shared data in their private caches for a pre-defined time duration. The time duration still guarantees WCL bounds for HRT cores, but it allows SRT cores to leverage cache hits for repeated data accesses resulting in reduced total memory access latency and thus improving performance.

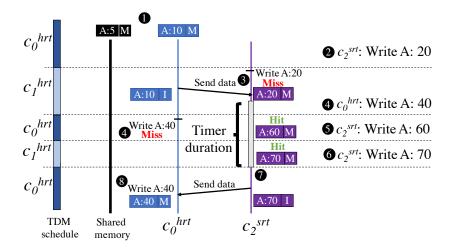

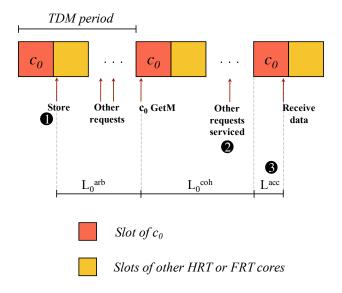

Figure 6.2 shows the use of timers with the criticality-aware bus arbitration policy: H-DD-WC-0. This assumes that only the SRT cores have timers. The initial states (1), 2) are similar to the example in Figure 6.1. At 3,  $c_2^{\rm srt}$ 's write request is satisfied in the slack slot of  $c_1^{\rm hrt}$ . The difference from the previous example is that  $c_2^{\rm srt}$  holds A for a time duration of 1 TDM period. In other words, at the end of the next slot of  $c_1^{\rm hrt}$ ,  $c_2^{\rm srt}$  self-invalidates its copy of A in its private cache. During this time period, successive write requests from  $c_2^{\rm srt}$  to A are cache hits 5,6 resulting in reduced memory access latency for SRT cores. During this timer period, the response for the write request from  $c_0^{\rm hrt}$  4 is deferred until the end of the timer duration or timeout 7. At the end of the timer duration,  $c_2^{\rm srt}$  invalidates its copy of A (8), and sends it to the first pending HRT core, which is  $c_0^{\rm hrt}$ . The use of timers

Figure 6.2: Proposed solution with timers for SRT cores.

for SRT cores results in improved average-case performance, while still guaranteeing WCL bound for HRT cores. Note that there is no reordering of memory requests, but there is only a change in the interleaving of requests between two different cores. The memory requests from a single core are still satisfied in order. So the usage of timers is valid under sequential consistency [29]. It is observed that the WCL bound for HRT cores depends on the value of timers set initially for the SRT cores, but it is still a guaranteed bound as the value is constant throughout the progress of the application. The timers, thus, introduce a trade-off between the WCL of memory requests from HRT cores, and performance of SRT cores.

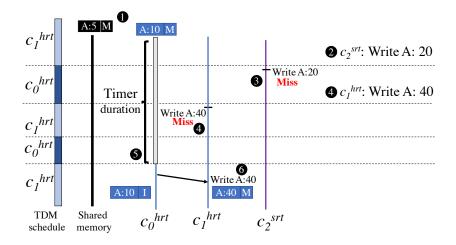

Mixed time-criticality systems also require that there is less interference suffered by HRT cores due to SRT cores. By assuming timers for HRT cores, a HRT core also holds data for some time duration. It gives some buffer time within which HRT and SRT cores can make requests. If there is no HRT core requesting for the same data in that buffer time, then SRT cores can obtain the data. However if there are HRT and SRT cores requesting for the same data, then by fixed priority arbitration, HRT cores are serviced before SRT cores. Figure 6.3 illustrates a scenario where HRT cores also have timers. Initially  $\bigcirc$ ,  $c_0^{\text{hrt}}$  holds the cache line A in modified state. At  $\bigcirc$ ,  $c_2^{\text{srt}}$  has a write request to A. This write is broadcasted in  $c_0^{\text{hrt}}$ 's slack slot at  $\bigcirc$ . Now  $c_1^{\text{hrt}}$  also requests for write on A, that is broadcasted in the next slot of  $c_1^{\text{hrt}}$   $\bigcirc$ . If  $c_0^{\text{hrt}}$  does not hold A for some time duration, then  $c_2^{\text{srt}}$  would have obtained A at  $\bigcirc$  and holds for some time duration (1 TDM period as in the example in Figure 6.2). Now  $c_1^{\text{hrt}}$ 's write is interfered by  $c_2^{\text{srt}}$ 's write and it has to

Figure 6.3: Proposed solution with timers for HRT cores.

wait for  $c_2^{\mathsf{srt}}$ 's timer to expire before it can receive A. Though this will not affect the WCL bound of  $c_1^{\mathsf{hrt}}$ , it is beneficial to have support to quantify this interference from SRT cores. If  $c_0^{\mathsf{hrt}}$  holds A for some time duration, say 2 TDM periods, then it expires at the end of  $c_0^{\mathsf{hrt}}$ 's slot  $\bullet$ . Now,  $c_0^{\mathsf{hrt}}$  observes two pending requests, and by fixed-priority arbitration,  $c_0^{\mathsf{hrt}}$  receives A before  $c_2^{\mathsf{srt}}$   $\bullet$ . Thus,  $c_1^{\mathsf{hrt}}$  receives A that is not modified by a SRT core,  $c_2^{\mathsf{srt}}$ . This amount of interference allowed by memory requests of SRT cores on HRT cores can be quantified based on the timer duration. For example, setting the timer duration, that a HRT core holds data, to a high value may prohibit any interference from SRT cores. This is beneficial in applications where it is required to prevent a less secure SRT core from interfering with a HRT core, until it is complete. The presence of timers for HRT cores also lead to increase in number of  $\mathit{slack}$  slots, as each HRT core should wait for the timers of other HRT cores to timeout. This allows more FRT or SRT cores to access the bus, thereby improving the performance of FRT or SRT cores.

I propose HourGlass that includes all these changes to support criticality-aware fixed priority arbitration and timers. HourGlass is a novel predictable cache coherence protocol compared to PMSI and is useful for mixed time-criticality systems. It provides provisions to improve the average-case performance of SRT cores by increasing the number of cache hits, with an increase in WCL bound for HRT cores.

# Chapter 7

# **HourGlass**

HourGlass is a predictable time-based cache coherence protocol for mixed-time-criticality systems. HourGlass is derived from the conventional MSI cache coherence protocol. It is designed such that there is a per request worst-case latency bound for HRT cores as all HRT cores are allocated dedicated slots. For FRT cores, few TDM slots are allocated. So there is a per-request worst-case latency bound for FRT cores. It is a looser bound compared to the HRT cores, but it has a guaranteed bound. Since FRT cores utilize the slack slots of HRT cores, it also provides improved average-case performance. For SRT cores, no TDM slots are guaranteed and so they do not have a worst-case latency bound, but benefit from improved performance due to the use of slack slots. For predictability of any core (observed request latency is always within the derived worst-case request latency bound), HourGlass must satisfy the invariants described in PMSI [21]. However, with different criticality levels co-existing on the same platform, the HRT cores must be prioritized over the FRT or SRT cores. HourGlass requires architectural changes and cache coherence protocol changes to support this criticality-aware cache coherence.

# 7.1 Architectural Modifications

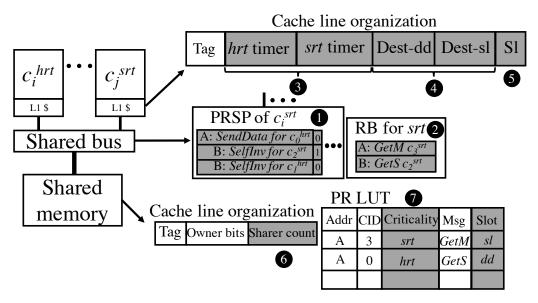

Figure 7.1 shows the architectural modifications necessary to support HourGlass(arb). There is a need for modifications in the architecture of the shared bus and the cache controller, as explained in Sections 7.1.1 and 7.1.2.

Figure 7.1: Architectural Modifications.

#### 7.1.1 Architectural modifications to shared bus

The arbiter assigns dedicated slots to all the HRT cores and few dedicated slots to FRT cores or no dedicated slots to SRT cores, depending on the arbitration scheme chosen. The slack slots of HRT cores are utilized by FRT or SRT cores. I assume that the hardware support to handle this arbitration across the requests from different cores, is already available in the shared bus. For instance, the shared bus can have a pending request queue for each core, from which the arbiter chooses the request from the corresponding core for that TDM slot.

FRT cores can broadcast their requests on the bus in the dedicated slots for FRT cores or in slack slots of HRT cores. SRT cores broadcast their requests only in the slack slots of HRT cores. It is therefore required to identify the FRT or SRT cores utilizing the slack slots. This is required because the requests from FRT or SRT cores broadcasted in the slack slots lead to unpredictable behaviour for requests from HRT cores. There can be more pending requests (FRT or SRT) than the number of dedicated slots in the TDM schedule, leading to unbounded request latency for HRT cores. As a result, it is required that the requests broadcasted in the slack slots are cancelled and reissued in the presence of a pending request from HRT core. To this end, the arbiter must append the information on whether it is a slack or dedicated slot in the coherence message with a bit isSlackSlot, before broadcasting it. With this information, HourGlass takes appropriate state transitions.