# MEMS Switches Implemented in Different Technologies for RF Applications

by

#### Ahmed Abdel Aziz

A thesis

presented to the University of Waterloo

in fulfillment of the

thesis requirement for the degree of

Doctor of Philosophy

in

Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2018

© Ahmed Abdel Aziz 2018

# **Examining Committee Membership**

The following served on the Examining Committee for this thesis. The decision of the Examining Committee is by majority vote.

External Examiner NAME: Luc G. Fréchette

Title: Professor, Université de Sherbrooke

Supervisor(s) NAME: Raafat R. Mansour

Title: Professor

Internal Member NAME: Siva Sivoththaman

Title: Professor

Internal Member NAME: Christopher Backhouse

Title: Professor

Internal-external Member NAME: Patricia Nieva

Title: Professor

### **Author's Declaration**

I hereby declare that I am the sole author of the thesis. This is a true copy of the thesis, including any required final revisions, as accepted by the examiners. I understand that the thesis may be made electronically available to the public.

#### **Abstract**

Microfabrication technologies allow building micro-scale and nano-scale mechanical switches. Despite the fact that the solid-state switches exhibit superior performance as compared to their micro-mechanical competitors in terms of speed and lifetime, mechanical switches exhibit various attractive features such as low power consumption, high linearity, high isolation and low loss.

This work summarizes the design, fabrication and testing of several micro-mechanical switches for Radio Frequency (RF) applications and using different microelectromechanical systems (MEMS) technologies. The implementation is carried out through four approaches for realizing MEMS switches.

In the first approach, the switches are built by post-processing chips fabricated in a standard complementary metal-oxide semiconductor (CMOS) fabrication process. The structural layers of the electrostatic MEMS switches are implemented in the four metal layers of the back end of line (BEOL) in the standard CMOS 0.35µm process. In addition, an enhanced post-processing technique is developed and implemented successfully. The switches presented include a compact 4-bit capacitor bank, a compact 4-bit phase shifter / delay line, a W-band single pole single through (SPST) series capacitive switch, SPST shunt capacitive switches with enhanced capacitance density, and a proposed compact T-switch cell with metal-to-metal contact switches.

In the second approach, a standard multi-user MEMS process is implemented. Electrothermal and electrostatic MEMS switches designed, fabricated and tested for low-frequency high-power RF applications using the MetalMUMPs process. The devices include a 3-bit capacitor bank, a compact discrete capacitor bank that can be configured for 2-bit / 3-bit operation depending on the stroke of the electrothermal actuators, and a novel rotor-based electrostatic multi-port switch.

In the third approach, an in-house university-based microfabrication process is developed in order to build reliable MEMS switches. The UWMEMS process, which was developed at the Center for Integrated RF Engineering (CIRFE), is used in this research to fabricate novel switch configurations. Moreover, the capabilities of the standard UWMEMS process are further expanded in order to allow for building geometric confinement (GC) or anchorless switches and other novel switches. The gold-based UWMEMS switches presented include compact T-switches, R-switches and C-switches, GC SPST shunt and series switches. Additionally, other novel switch architectures such as the hybrid self-actuation switch (HSAS) and thermally-restored switches (TRS).

In the fourth approach, which is a hybrid approach between the first and third approaches, the MEMS switches are built and packaged in one fabrication process, and without the need for sacrificial layer, by means of a wafer-level packaging technique. Adopting silicon wafers for the microfabrication necessitates using silicon-core switching, which offers few attractive advantages as compared to the metal-based

switches implemented by the third approach. The designed switches to be fabricated in a state-of-the-art industrial facility include a variety of simple SPST contact-type switches as well as compact designs of T-switch, C-switch, a novel four-port gimbal-based switch (G-switch) introduced in this work, SP4T cells, and a seesaw push-pull SPST switch design is included.

### Acknowledgement

First, I must thank my dear supervisor Prof. Raafat R. Mansour for his encouragement, support, and what he has taught me over the past years as well as for giving me the chance to learn much more about the field of RF engineering, especially the typical considerations for its corresponding microfabrication and/or post-processing. In addition, I should thank him very much for allowing me not only to take the responsibility of running and further developing the UWMEMS process for several years, but also for training many of my colleagues. This certainly enriched my past experience in process technology along with my mentoring, teaching and leadership skills.

Second, I must also thank Prof. Patricia Nieva, Prof. Siva Sivoththaman and Prof. Chris Backhouse for the advising and cooperation in helping me finish the program. I should also thank Prof. Luc G. Fréchette for his time and efforts.

Third, I would like to thank Prof. Eihab Abdel-Rahman for the many interesting discussions and what he taught me in two of his graduate courses on modeling and nonlinear dynamics. I am also grateful and thankful to his research group for their help and support, especially Dr. Mahmoud Khater. I have definitely learned much from the collaboration with Prof. Abdel-Rahman's group.

Fourth, I should thank my colleagues at the Center for Integrated RF Engineering (CIRFE) who have helped or supported me, and I cannot continue writing without mentioning the names of Dr. Siamak Fouladi, Sormeh Setoodeh, Dr. Mostafa Azizi, Geoffrey Lee, Dr. Sara Attar, and Dr. Niladri Sarkar.

Fifth, I should thank a lot Dr. Ahmed Abdellatif as well as Dr. Suren Gigoyan at the Center for Intelligent Antenna and Radio Systems (CIARS) for what I have learned from them during our fruitful collaboration. Besides, I should thank Prof. Maher Bakri-Kassem at the American University of Sharjah (AUS), UAE, for his engagement in the collaboration between us on several designs in different fabrication technologies, especially those making use of my expanded version of the UWMEMS process.

Last but not least, I am greatly indebted to my family in terms of being able to proceed in my graduate program, especially my mother. As a matter of fact, I cannot imagine being in the program if it was not for making her happy and satisfied as she has always wished. Similarly, I am indebted by all means to the acquired knowledge and extensive training in microfabrication and MEMS that I had at the Yousef Jameel Science and Technology Research Center (YJ-STRC) in the American University in Cairo (AUC) in Egypt (2005-2010) and the Interuniversity Microelectronics Center (IMEC) in Belgium (2006-2008) by my first microfabrication, MEMS and post-processing teacher Prof. Sherif Sedky, Provost of AUC.

# **Dedication**

All my time and efforts in the past years is dedicated to the love of my family.

# **Table of Contents**

| Examining Committee Membership                              | ii   |

|-------------------------------------------------------------|------|

| Author's Declaration                                        | iii  |

| Abstract                                                    | iv   |

| Acknowledgement                                             | vi   |

| Dedication                                                  | vii  |

| Table of Contents                                           | viii |

| List of Figures                                             | xi   |

| List of Tables                                              | xxii |

| Chapter 1 : Introduction                                    | 1    |

| 1.1 Motivation                                              | 1    |

| 1.2 Thesis Main Objectives                                  | 3    |

| 1.3 Thesis Outline                                          | 4    |

| Chapter 2 : The Need for RF MEMS Switches                   | 5    |

| 2.1 Mechanical Switches                                     | 5    |

| 2.1.1 Metallic Contact                                      | 8    |

| 2.1.2 Actuation Force, Contact Force and Restoring Force    | 12   |

| 2.1.3 Mechanical Properties of the Switching Beam           | 14   |

| 2.1.4 Dielectric Material for Electrostatic Actuation       | 16   |

| 2.2 Mechanical Switches in RF Applications                  | 17   |

| 2.2.1 Series RF MEMS Switch                                 | 19   |

| 2.2.2 Shunt RF MEMS Switch                                  | 20   |

| Chapter 3: RF CMOS-MEMS Switches                            | 23   |

| 3.1 Design and Fabrication of CMOS-MEMS Capacitive Switches | 23   |

| 3.1.1 Compact CMOS-MEMS Digital Capacitor Bank              | 23   |

| 3.1.2 CMOS-MEMS Digital Phase Shifter / Delay Line                                                        | 29  |

|-----------------------------------------------------------------------------------------------------------|-----|

| 3.1.3 CMOS-MEMS W-band Switch                                                                             | 33  |

| 3.1.4 Capacitive Switching with Improved Capacitance Density                                              | 35  |

| 3.2 Design and Fabrication of CMOS-MEMS Metal-Contact Switches                                            | 39  |

| 3.2.1 Compact CMOS-MEMS T-Switch                                                                          | 40  |

| Chapter 4: MEMS Switches Using MetalMUMPs Process                                                         | 48  |

| 4.1 Advantages of Using MetalMUMPs Process                                                                | 48  |

| 4.2 MetalMUMPs Devices Fabricated                                                                         | 49  |

| 4.2.1 Compact RF MEMS Discrete Capacitor Bank                                                             | 49  |

| 4.2.2 Low-Frequency High-Power 3-Bit Capacitor Bank                                                       | 61  |

| 4.2.3 Rotor-based RF MEMS Switch                                                                          | 67  |

| Chapter 5 : RF Switches Implemented in Standard UWMEMS and a New Post-Processi More Complex Architectures |     |

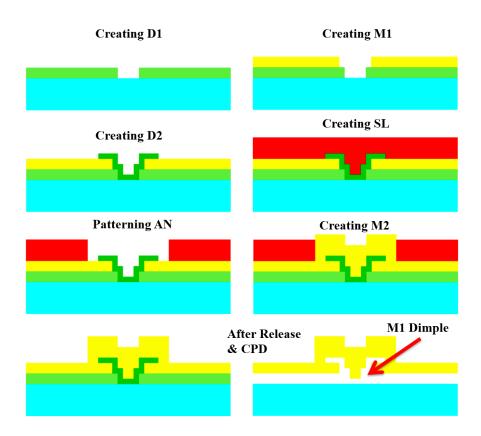

| 5.1 Overview of the UWMEMS Process                                                                        | 73  |

| 5.2 RF Switches in Standard UWMEMS Fabrication and Post-Processing                                        | 74  |

| 5.2.1 Four-Port Switching Cells for Switch Matrices                                                       | 74  |

| 5.2.2 Self-Actuation Switches                                                                             | 80  |

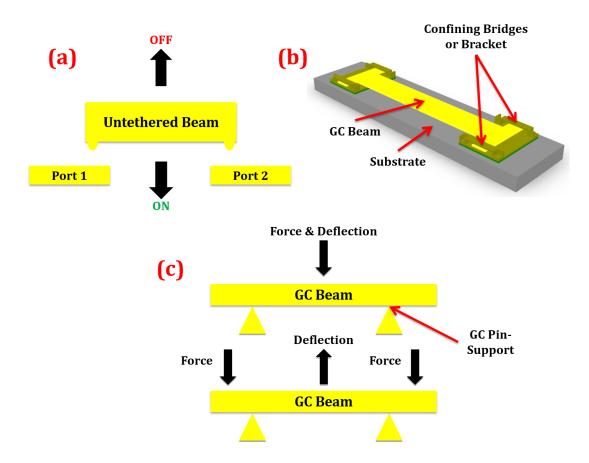

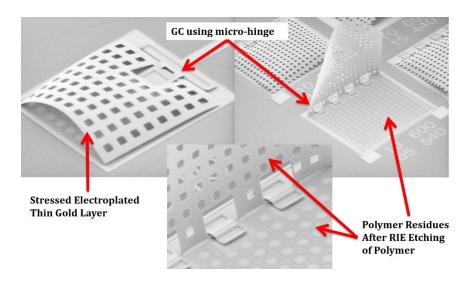

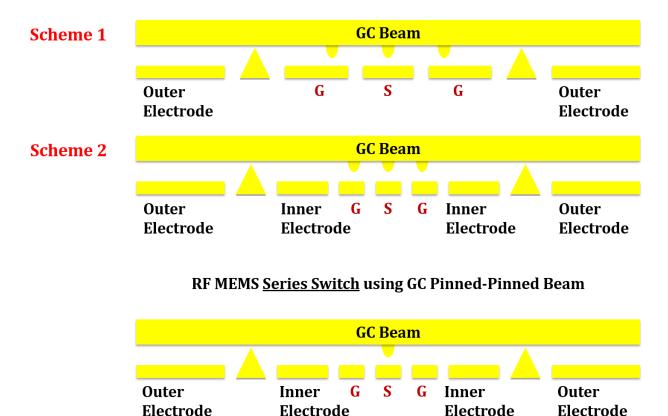

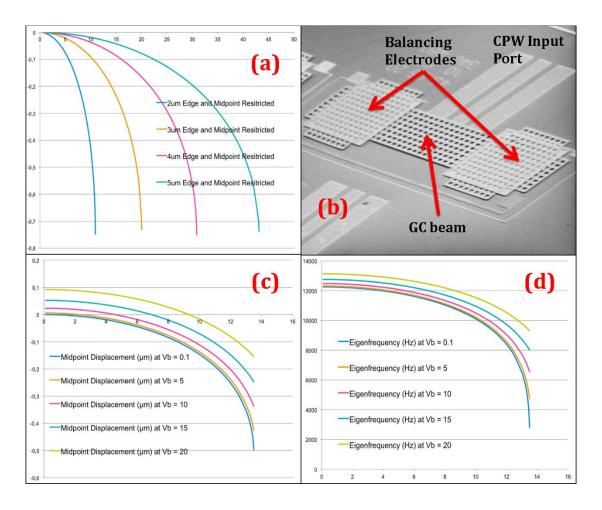

| 5.3 MEMS Switches Using Geometric Confinement of Beams                                                    | 97  |

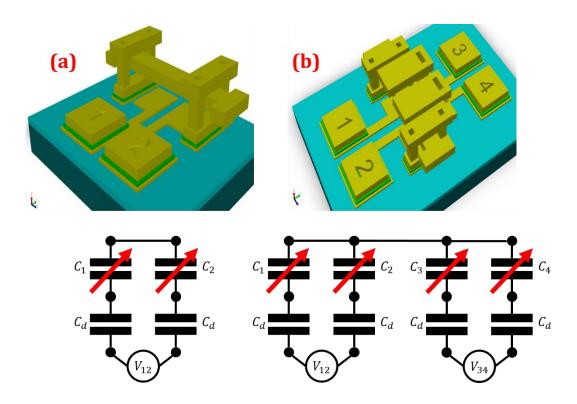

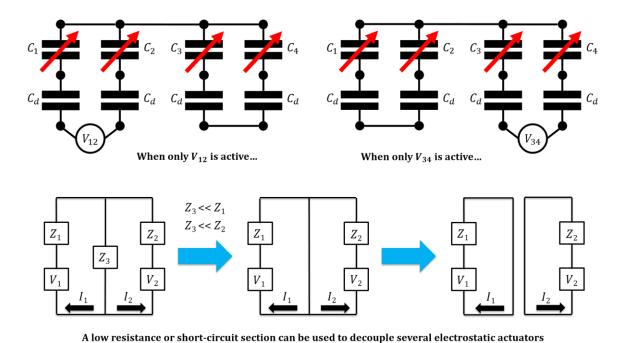

| 5.3.1 Remote Electrostatic Actuation and Decoupled Actuation                                              | 99  |

| 5.4 New Post-Processing of a Modified UWMEMS Process                                                      | 102 |

| 5.4.1 GC Pinned-Pinned Shunt and Series SPST Switches                                                     | 106 |

| 5.4.2 Thermally Restored Switch (TRS)                                                                     | 111 |

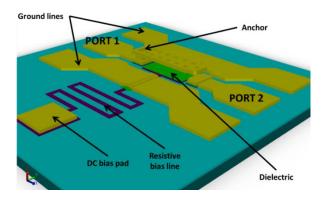

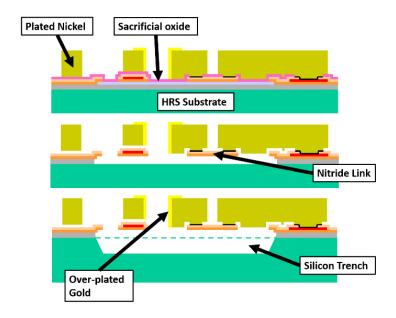

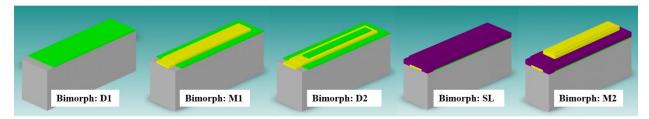

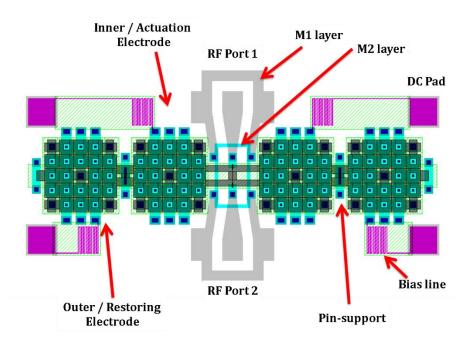

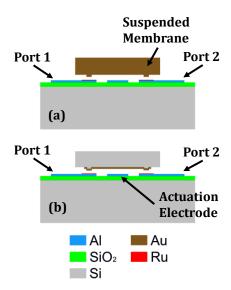

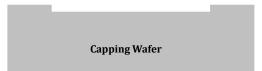

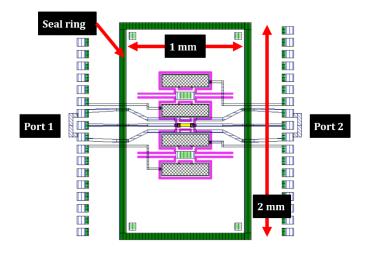

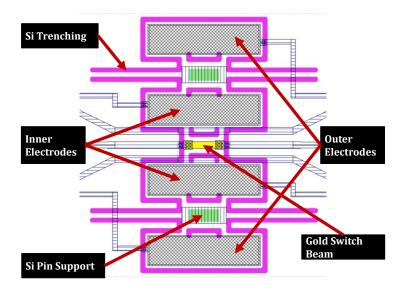

| Chapter 6 : Si-Core RF MEMS Switches with Wafer Level Packaging                                           | 116 |

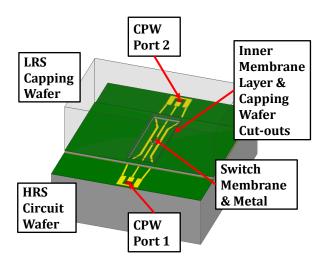

| 6.1 Si-Core MEMS Switches                                                                                 | 116 |

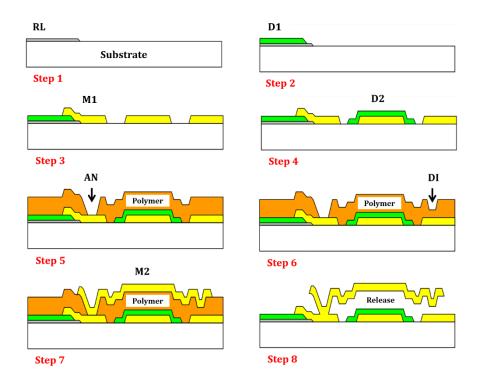

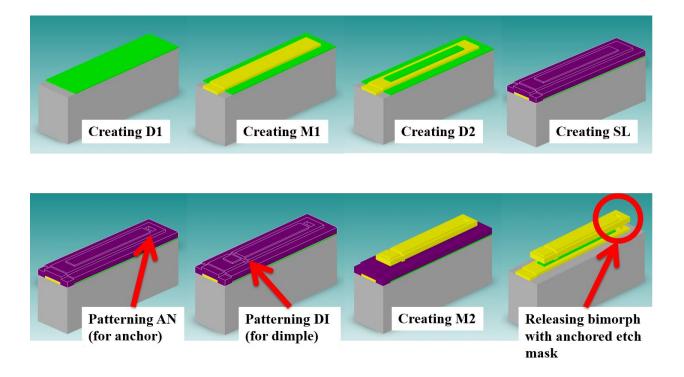

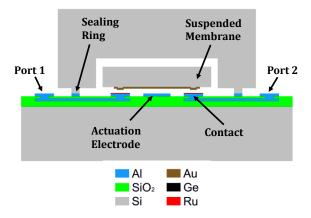

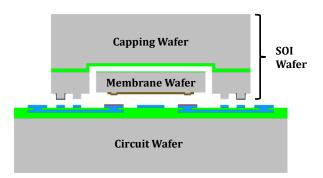

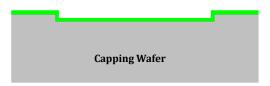

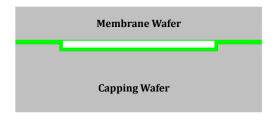

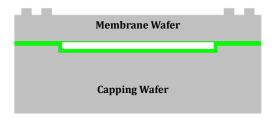

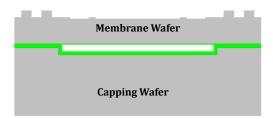

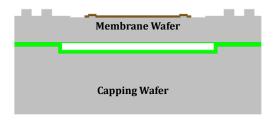

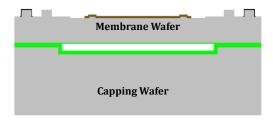

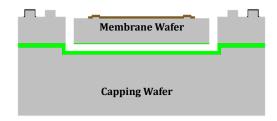

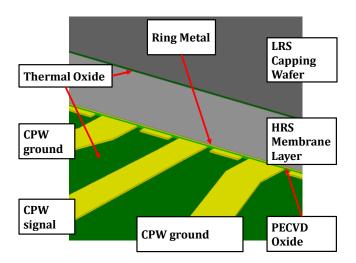

| 6.2 Microfabrication Process Employing WLP                                                                | 118 |

| 6.3 Switch Design                                                                                         | 128 |

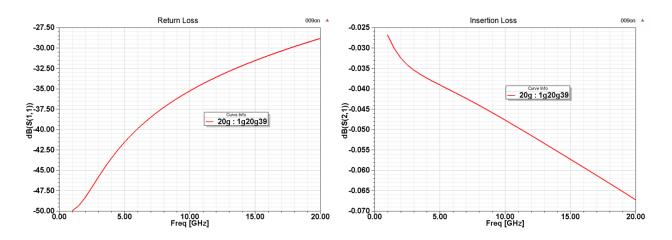

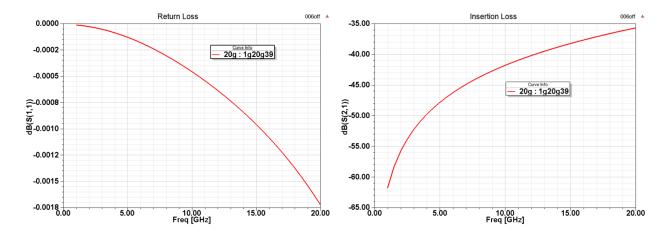

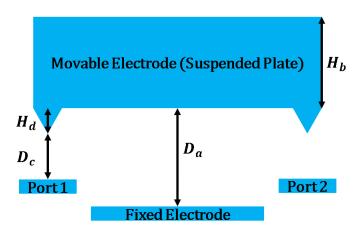

| 6.3.1 Important Considerations for the RF Design                                                          | 128 |

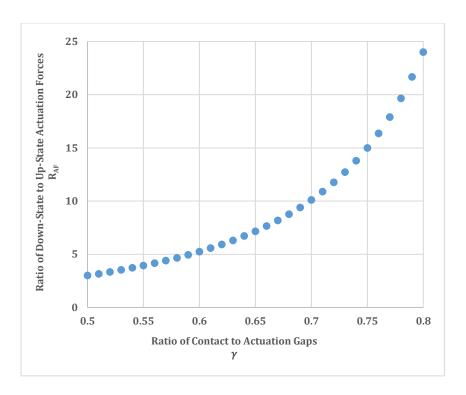

| 6.3.2 Important Considerations for the Electromechanical Design | 130 |

|-----------------------------------------------------------------|-----|

| 6.4 First Generation of Si-Core RF MEMS Switches                | 140 |

| 6.4.1 Clamped-Clamped SPST Switch Designs                       | 143 |

| 6.4.2 Seesaw Push-Pull SPST Switch Design                       | 148 |

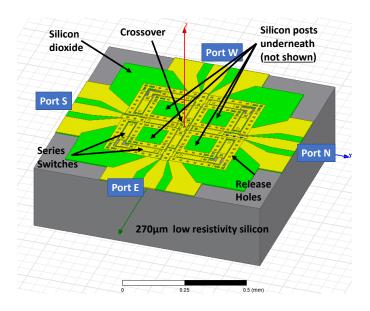

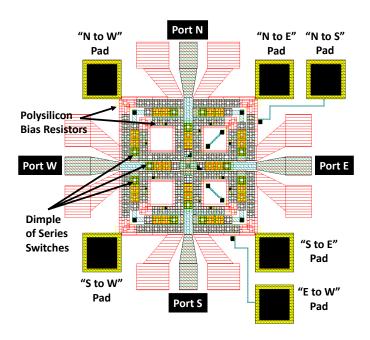

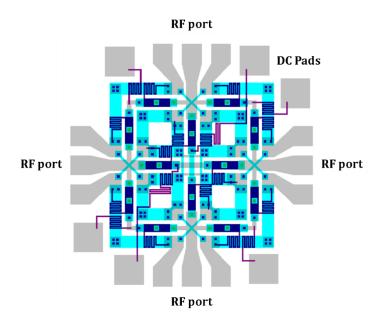

| 6.4.3 Compact T-Switch Crossover Design                         | 150 |

| 6.4.4 Compact C-Switch Design                                   | 153 |

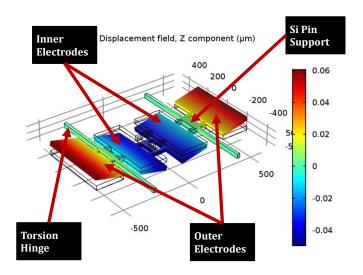

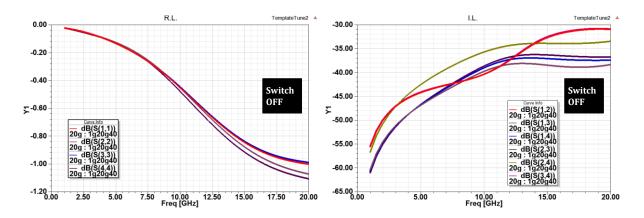

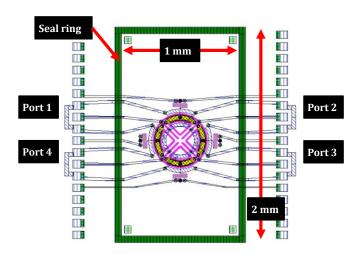

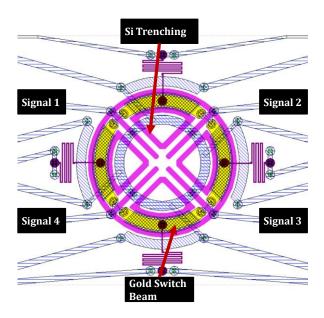

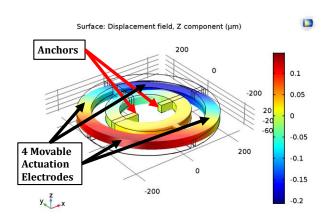

| 6.4.5 Gimbal-Switch Design (G-switch)                           | 155 |

| Chapter 7 : Conclusions & Future Work                           | 157 |

| 7.1 Conclusions                                                 | 157 |

| 7.2 Future Work                                                 | 158 |

| References                                                      | 160 |

# **List of Figures**

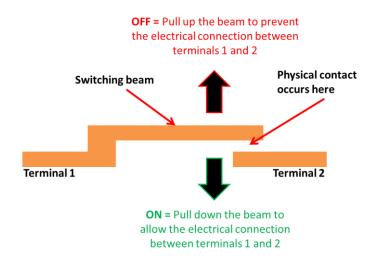

| Fig 2.1: The basic architecture of a mechanical switch                                                                |

|-----------------------------------------------------------------------------------------------------------------------|

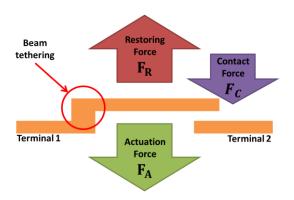

| Fig 2.2: Main components of the operation of a mechanical switch                                                      |

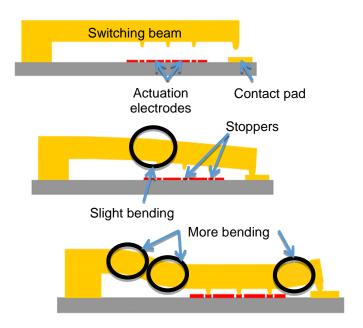

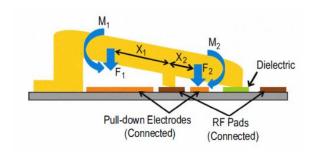

| Fig 2.3: Mechanical solution towards increased contact force; adapted from [2]                                        |

| Fig 2.4: Two-position contact-type switch; reproduced from [16]                                                       |

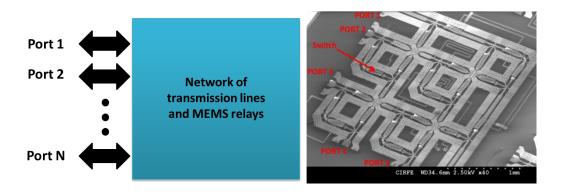

| $Fig\ 2.5: (Left)\ Block\ diagram\ for\ RF\ switching\ network; (right)\ CPW-based\ previously\ fabricated\ switched$ |

| network at CIRFE                                                                                                      |

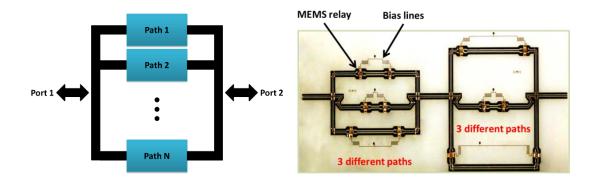

| Fig 2.6: (Left) Block diagram for reconfigurable phase shifters; (right) CPW-based phase shifter previously           |

| fabricated at CIRFE                                                                                                   |

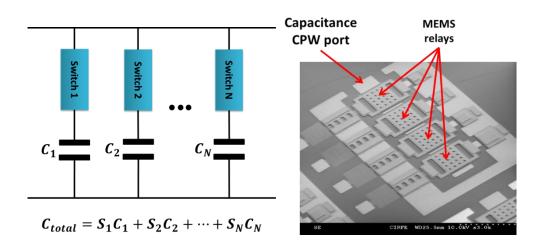

| Fig 2.7: (Left) Block diagram for the tunable capacitance; (right) CPW-based capacitance bank previously              |

| fabricated at CIRFE                                                                                                   |

| Fig 2.8: Conventional series RF MEMS switch                                                                           |

| Fig 2.9: Conventional shunt RF MEMS switch                                                                            |

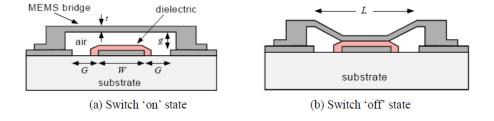

| Fig 2.10: The operation of capacitive shunt RF MEMS switch                                                            |

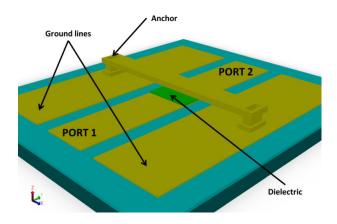

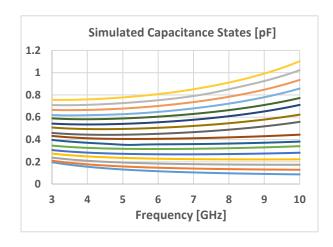

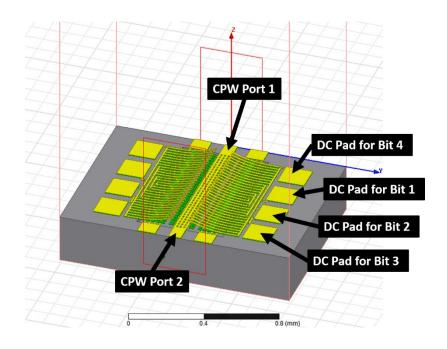

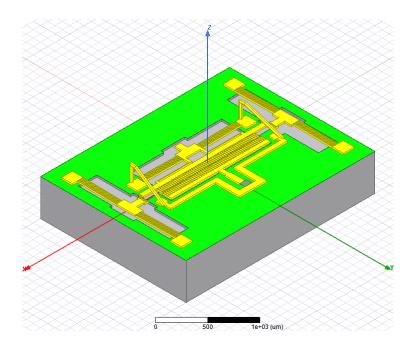

| Fig 3.1: 3D structure of the proposed compact 4-bit CMOS capacitor bank designed and simulated24                      |

| Fig 3.2: Simulated capacitance values for the first state (all beams up) and last state (all beams down)24            |

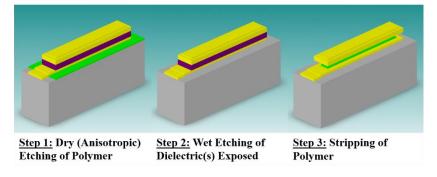

| Fig 3.3: The employed fabrication procedure based on the mask-less post-processing of standard CMOS                   |

| $0.35\mu m$ chips                                                                                                     |

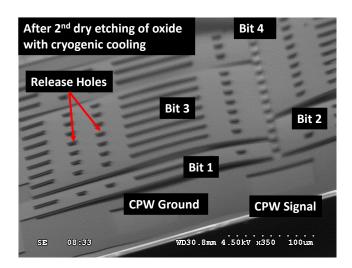

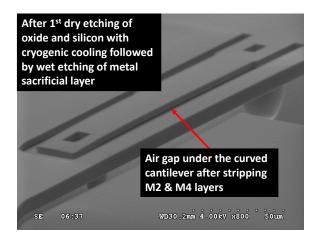

| Fig 3.4: A scanning electron microscope (SEM) image of a released device using the post-processing step               |

| and cryogenic cooling of the chips (keeping them at $\sim 10$ °C) during all the high-plasma-power dry etching        |

| steps                                                                                                                 |

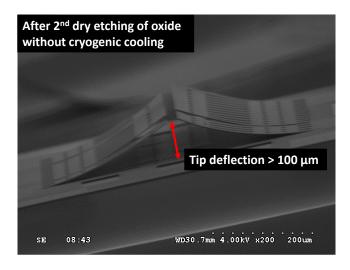

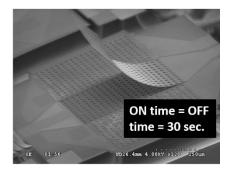

| Fig 3.5: A scanning electron microscope (SEM) image of a released device using the post-processing step               |

| without using cryogenic cooling for the second dry etching step where the acquired stress is controlled via           |

| the duty cycle of the plasma generation in addition to the power level of the plasma27                                |

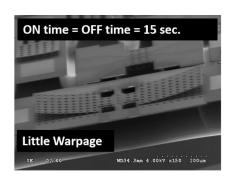

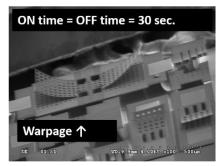

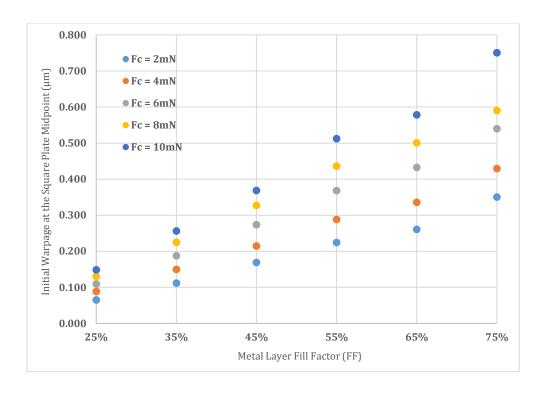

| Fig 3.6: Impact of the post-processing timing on the warpage profile of the suspended structures in the               |

| absence of the cryogenic cooling. The power is 2.5 KW for the three cases                                             |

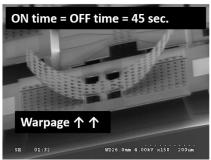

| Fig 3.7: Measured capacitance values of the 16 different states of the proposed 4-bit capacitor bank 28               |

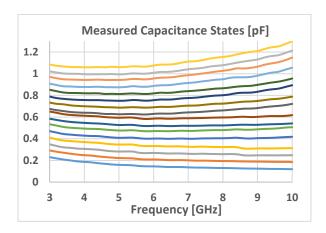

| Fig 3.8: Measured return loss at the maximum capacitance (state "1111"), S11, versus the extracted return             |

| loss after de-embedding the probing pads, S33                                                                         |

| Fig~3.9:~3D~structure~of~the~proposed~compact~4-bit~CMOS-MEMS~phase~shifter~/~delay~line~30                           |

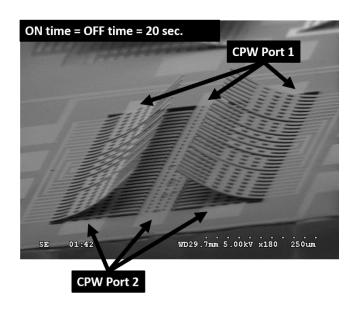

| Fig 3.10: SEM of the fabricated compact 4-bit CMOS-MEMS phase shifter / delay line30                                  |

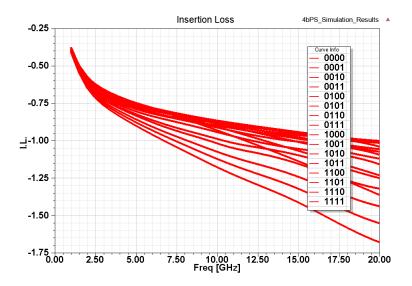

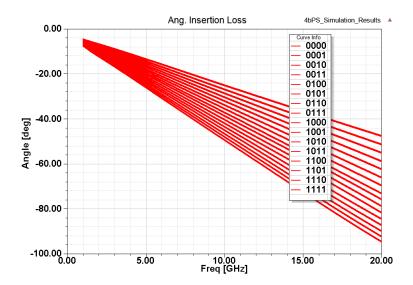

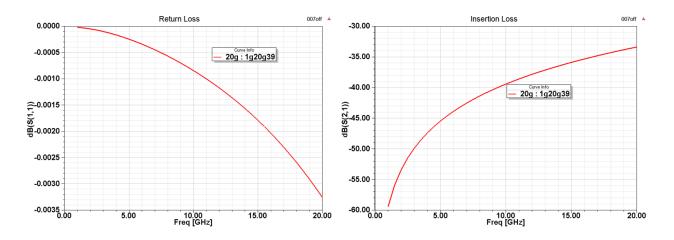

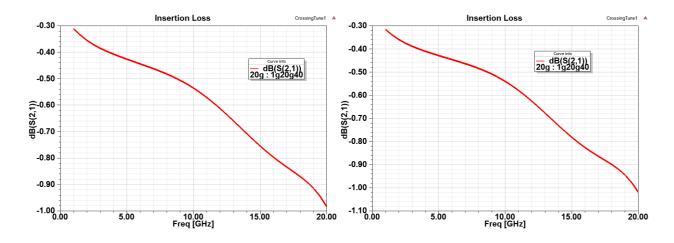

| Fig 3.11: HFSS electromagnetic simulation results of the insertion loss for all the 16 states of the proposed  |

|----------------------------------------------------------------------------------------------------------------|

| phase shifter. The results show good RF performance in terms of the insertion loss and insertion loss          |

| variation                                                                                                      |

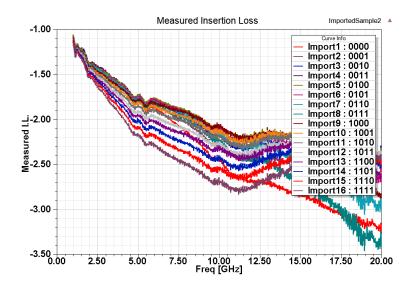

| Fig 3.12: The measured insertion loss for all the 16 states of the proposed phase shifter31                    |

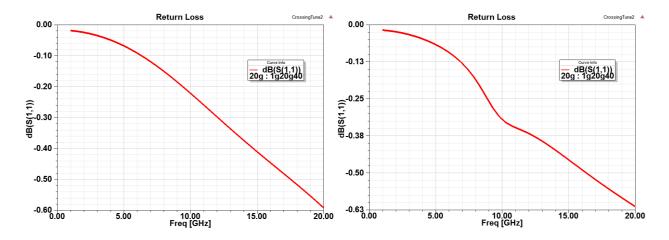

| Fig 3.13: HFSS electromagnetic simulation results of the phase variation for all the 16 states of the proposed |

| phase shifter                                                                                                  |

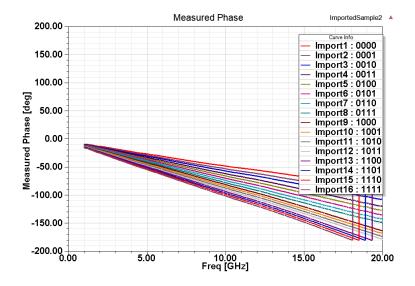

| Fig 3.14: Measured results of the phase variation for the 16 different states of the proposed compact phase    |

| shifter                                                                                                        |

| Fig 3.15: An exact layout of the proposed W-band CMOS-MEMS switch design                                       |

| Fig 3.16: SEM pictures of the fabricated W-band switches using different non-cryogenic post-processing         |

| conditions for the sake of controlling the warpage at the expense of the increase in actuation voltage34       |

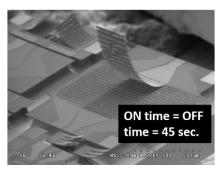

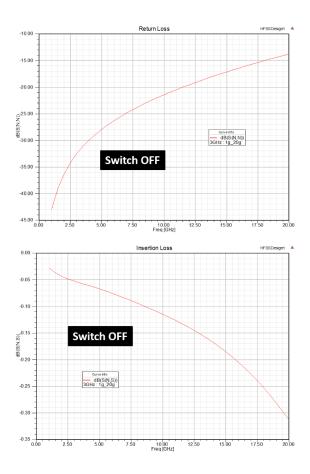

| Fig 3.17: HFSS electromagnetic simulation results of the return loss and insertion loss of the proposed W-     |

| band switch in the OFF state                                                                                   |

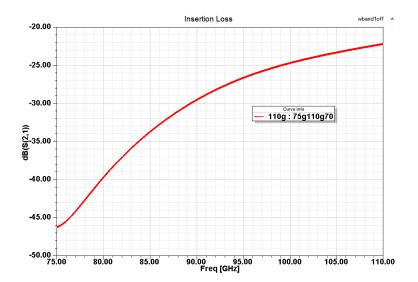

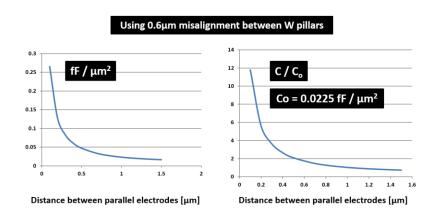

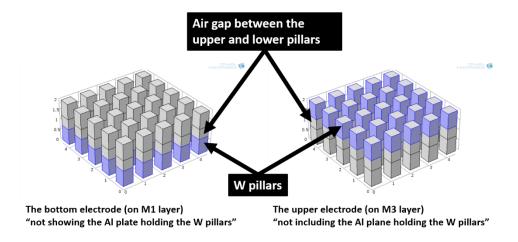

| Fig 3.18: : COMSOL 3D illustration of the interleaving of the upper and lower W pillars for the sake of        |

| increasing the maximum attainable capacitance density published [63, 64]35                                     |

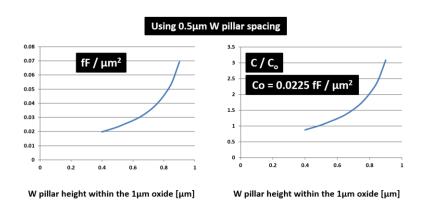

| Fig 3.19: Simulation results of the interleaving of the upper and lower W pillars for the sake of increasing   |

| the maximum attainable capacitance density published [63, 64]                                                  |

| Fig 3.20: COMSOL 3D illustration of the alignment of the upper and lower W pillars for the sake of             |

| increasing the maximum attainable capacitance density published [63, 64]                                       |

| Fig 3.21: Simulation results of the alignment of the upper and lower W pillars for the sake of increasing the  |

| maximum attainable capacitance density published [63, 64]                                                      |

| Fig 3.22: An improved design of the capacitive SPST switch in [64] where the capacitance density is            |

| increased using the first approach, i.e. interleaving the W pillars                                            |

| Fig 3.23: An alternative design to the capacitive SPST switch in [64] where the capacitance density is         |

| increased using the second approach, i.e. alignment of W pillars                                               |

| Fig 3.24: SEM of the fabricated devices following the alternative design to the capacitive SPST switch in      |

| [64] where the capacitance density is increased using the second approach, i.e. alignment of W pillars.        |

| Three levels of warpage are shown where the up-state capacitance is further suppressed in order to increase    |

| the capacitance ratio                                                                                          |

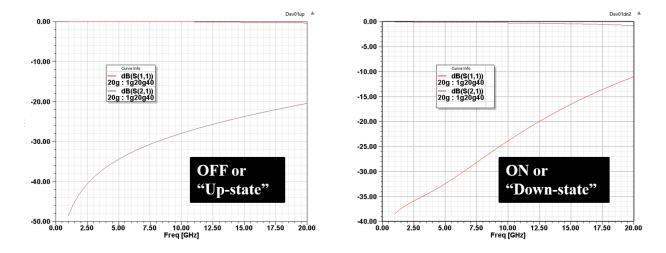

| Fig 3.25: HFSS simulated results of the alternative design to the capacitive SPST switch in [64] for the OFF   |

| state                                                                                                          |

| Fig 3.26: HFSS simulated results of the alternative design to the capacitive SPST switch in [64] for the ON    |

| state 39                                                                                                       |

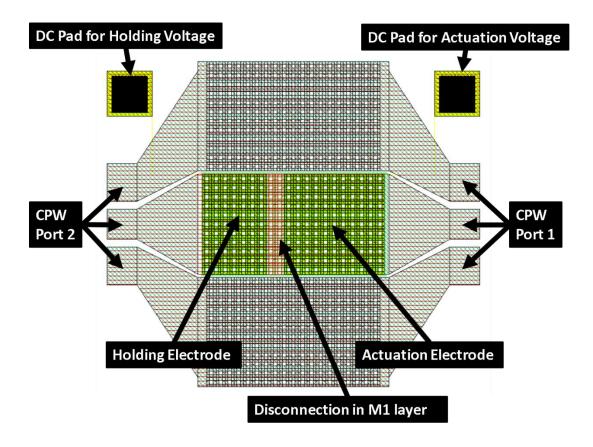

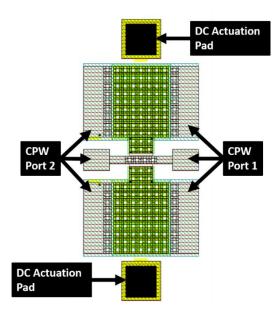

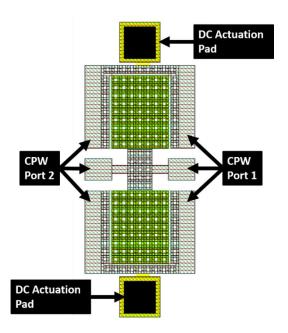

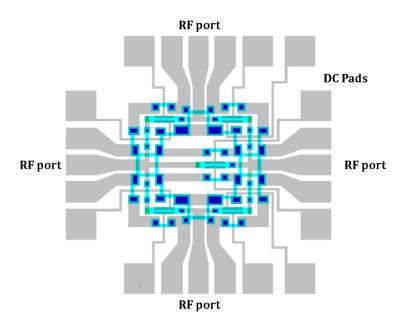

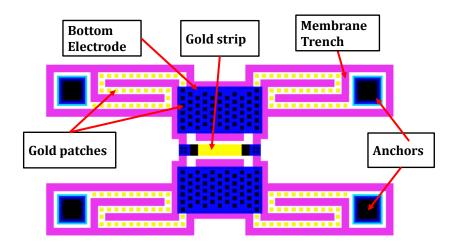

| Fig 3.27: HFSS 3D view of the proposed RF MEMS compact T-type switch using a mask-less post-                      |

|-------------------------------------------------------------------------------------------------------------------|

| processing of standard CMOS 0.35µm chips. The DC actuation pads and biasing resistors are not shown.              |

| The core size of the circuit is ~ 0.5 mm                                                                          |

| Fig 3.28: Top view of the T-type switch design from its layout showing the 150µm actuation pads for the           |

| six different signal routing paths. The layers for via12, via23 and M4 hard mask are not shown41                  |

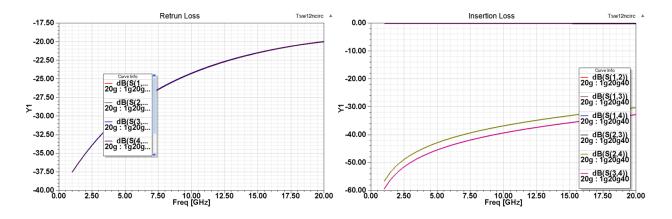

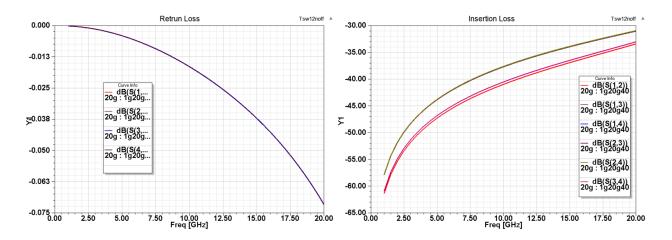

| Fig 3.29: HFSS simulation results for 180° signal paths (i.e. when the signal crossover is needed); (a) return    |

| loss in dB; (b) insertion loss in dB; (c) isolation in dB; the simulated results are for a 60µm deep silicon      |

| trench                                                                                                            |

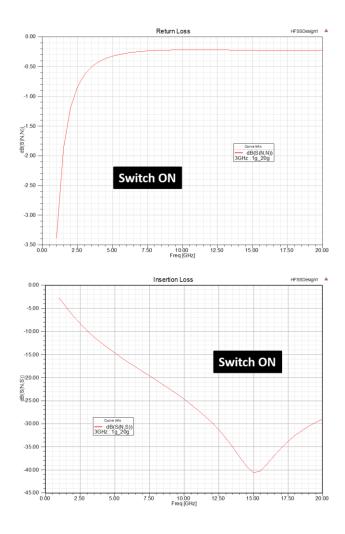

| Fig 3.30: HFSS simulation results for the 90° paths (i.e. C-type operation); (a) return loss in dB; (b) insertion |

| loss in dB; the simulated results are for a 60µm deep silicon trench                                              |

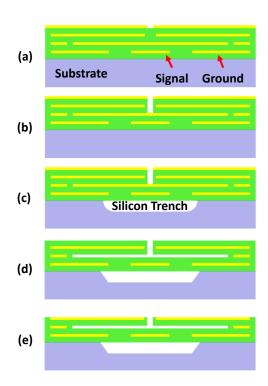

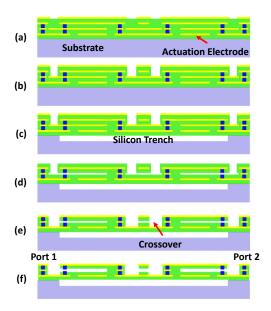

| Fig 3.31: The CMOS mask-less post-processing procedure using the relative alignment of metal layers in            |

| the standard CMOS 0.35 µm BEOL; (a) As-received chip; (b) after dry etching of oxide; (c) after dry etching       |

| of low resistivity silicon or trench creation; (d) after wet etching of the sacrificial M2 and M4 layers as well  |

| as the adhesion layer; (e) after the dry etching of oxide on top of M3 / M1 probing areas and released            |

| switches; (f) after thinning the oxide layer around the tungsten pillars or contact dimples. For the sake of      |

| simplicity, the details of release holes are not shown                                                            |

| Fig 3.32: SEM picture demonstrates an identical test switching element (for DC contact resistance                 |

| characterization) after the first dry etching steps with the cryogenic cooling, wet release of switch and         |

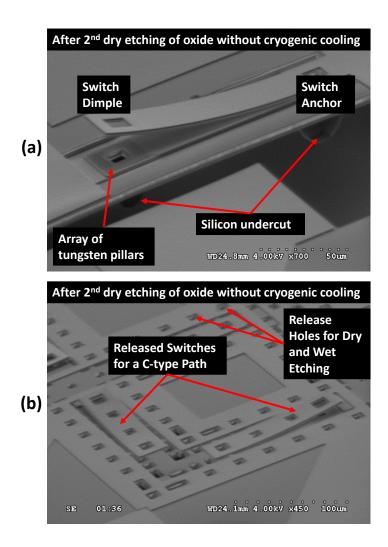

| drying using CPD46                                                                                                |

| Fig 3.33: SEM picture of different switching elements after the second dry etching of oxide without the           |

| cryogenic cooling; (a) DC contact resistance test switch with a relatively long plasma bombardment                |

| duration, and (b) C-type path switches of the T-switch cell with a moderate duration for plasma                   |

| bombardment, which results in less membrane warping and lower actuation voltage47                                 |

| Fig 4.1: Cross-sections of the MetalMUMPs process by MEMSCAP Inc. [70]                                            |

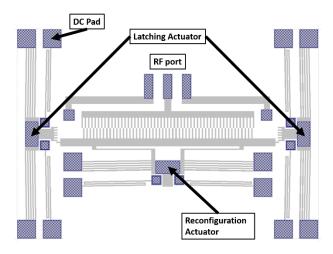

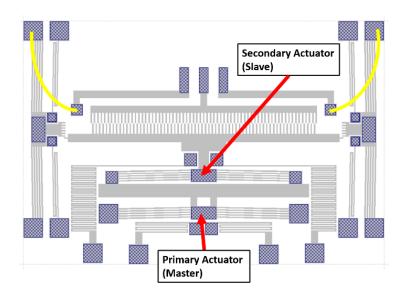

| Fig 4.2: Layout of the MetalMUMPs compact capacitor bank of the second generation50                               |

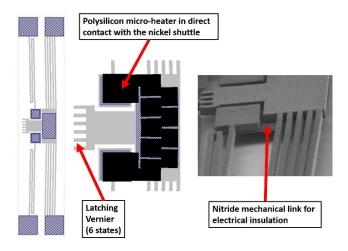

| Fig 4.3: Layout of the latching electrothermal actuator showing the polysilicon micro-heater50                    |

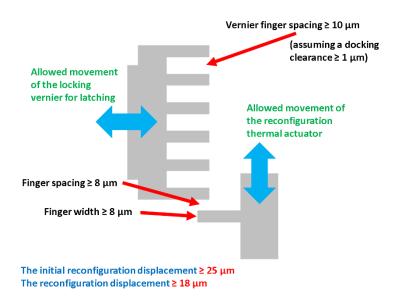

| Fig 4.4: The latching or docking mechanism and typical geometrical dimensions imposed by the intra-layer          |

| design rules for the metal layer in the MetalMUMPs process                                                        |

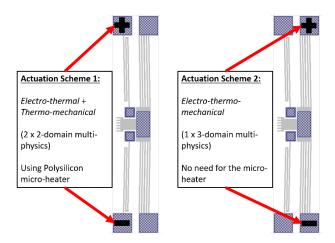

| Fig 4.5: Two different actuation schemes are possible for the electrothermal actuators                            |

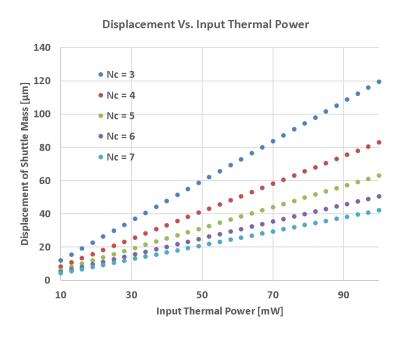

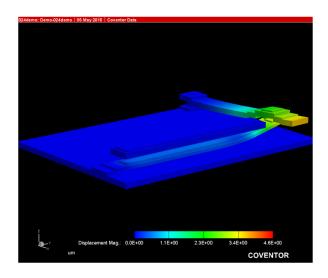

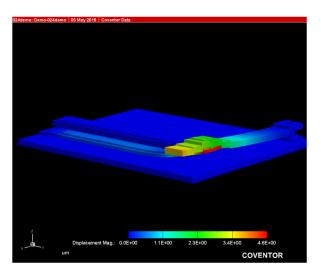

| Fig 4.6: COMSOL thermomechanical simulation results of the thermal actuator showing the displacement              |

| versus the thermal input power to the shuttle mass (provided by the Joule Heating mechanism taking place          |

| in the micro-heater)                                                                                              |

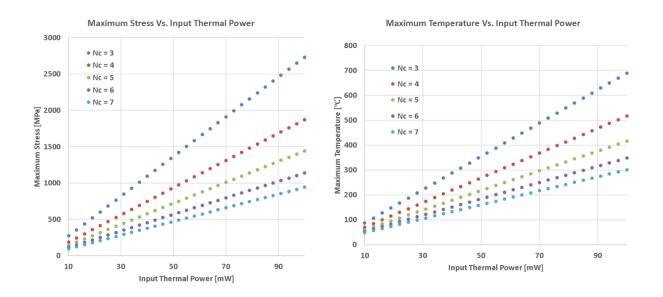

| Fig 4.7: COMSOL thermomechanical simulation results of the thermal actuator showing the maximum               |

|---------------------------------------------------------------------------------------------------------------|

| stress and maximum temperature versus the thermal input power to the shuttle mass (provided by the Joule      |

| Heating mechanism taking place in the micro-heater)                                                           |

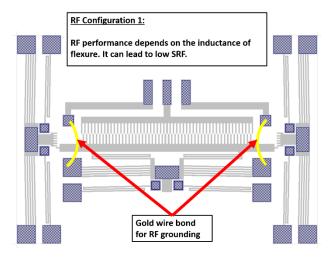

| Fig 4.8: First RF configuration of the capacitor's circuit with the RF grounding through the equivalent       |

| lumped elements of the actuator flexures in addition to the equivalent lumped elements of the chevron         |

| beams                                                                                                         |

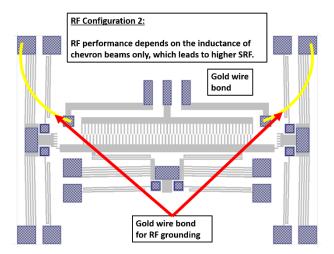

| Fig 4.9: Second RF configuration of the capacitor's circuit with the RF grounding through only the            |

| equivalent lumped elements of the chevron beams, independent of the flexure design in the actuator $\dots 55$ |

| Fig 4.10: HFSS simulated structure following scheme 1 and taking into consideration the required 200 $\mu$ m- |

| high and $40\mu m$ -thick gold wire bonding in addition to the $25\mu m$ trench in the HRS substrate56        |

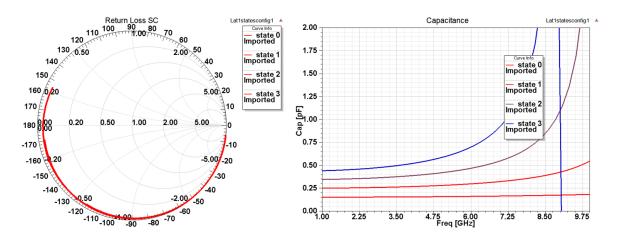

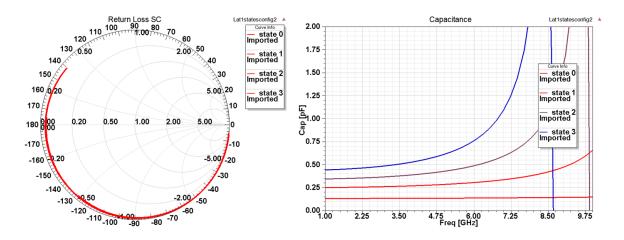

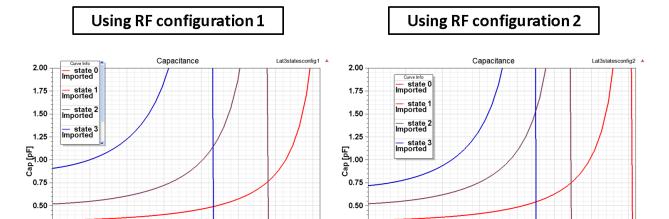

| Fig 4.11: HFSS electromagnetic simulation of the first four states of the compact discrete capacitor in Fig   |

| 4.10 following the first RF configuration                                                                     |

| Fig 4.12: HFSS electromagnetic simulation of the first four states of the compact discrete capacitor in Fig   |

| 4.10 following the second RF configuration                                                                    |

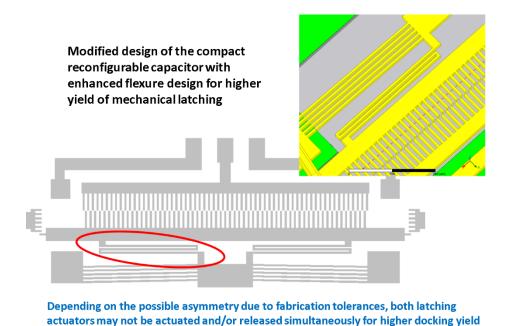

| Fig 4.13: An exact layout and 3D structure of a compact reconfigurable capacitor with an improved             |

| mechanical design of the flexure leading to higher yield in mechanical latching                               |

| Fig 4.14: HFSS electromagnetic simulation results for the extracted capacitance of the compact design in      |

| Fig 4.13. The results of using the first and second RF configurations are compared                            |

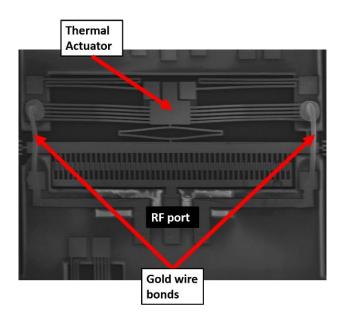

| Fig 4.15: SEM of a fabricated five-state compact discrete capacitor of the first generation. The smallest     |

| gold wire bonds were 200 $\mu$ m-high on average with the wire diameter of $40\mu$ m                          |

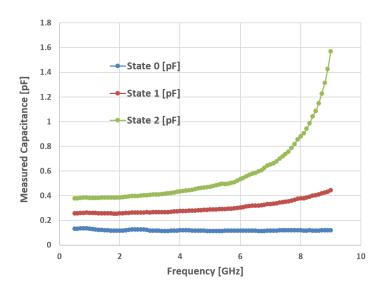

| Fig 4.16: Measurement results of a compact capacitor bank of the first generation                             |

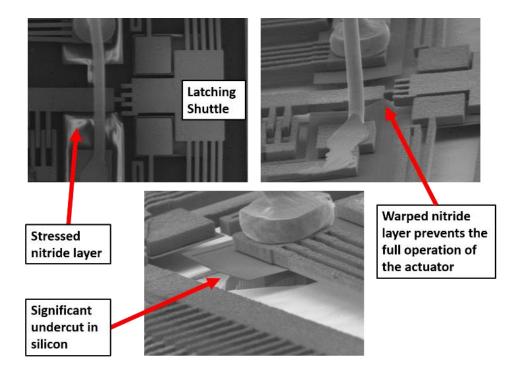

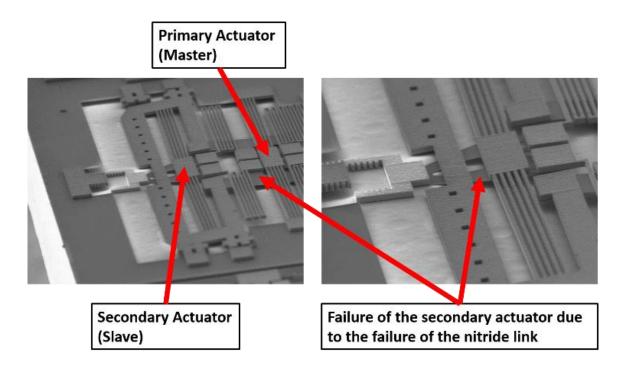

| Fig 4.17: SEM pictures showing some of the main issues with the first generation of fabricated compact        |

| capacitor banks                                                                                               |

| Fig 4.18: Second RF configuration of the capacitor's circuit using a thermal actuator design with enhanced    |

| stroke                                                                                                        |

| Fig 4.19: SEM pictures of the first generation thermal actuators with enhanced stroke revealing the failure   |

| due to the flexible nitride mechanical link                                                                   |

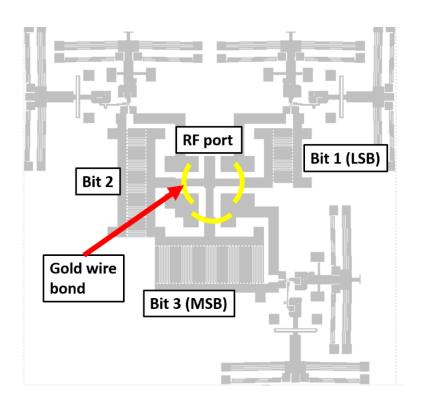

| Fig 4.20: An exact layout of the proposed 3-bit capacitor bank for low frequency and high power RF            |

| applications                                                                                                  |

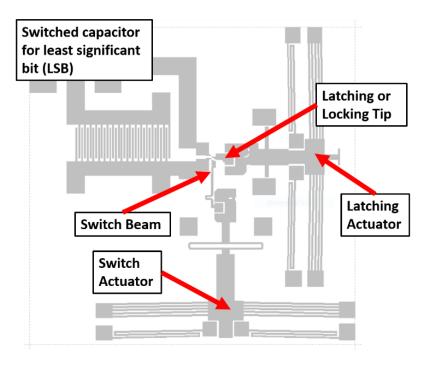

| Fig 4.21: An exact layout of a single bit demonstrating the mechanical latching mechanism employed and        |

| the structure of the individual bit                                                                           |

| Fig 4.22: SEM pictures of the fabricated thermal actuators showing the mechanical latching mechanism          |

| employed [74]                                                                                                 |

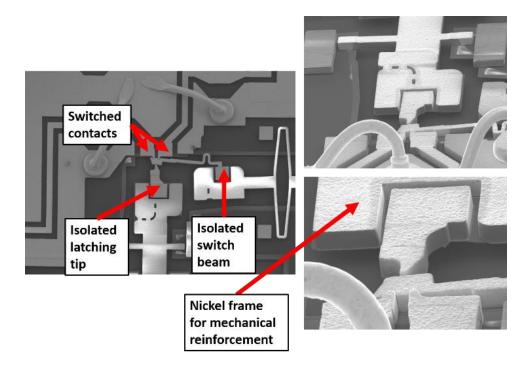

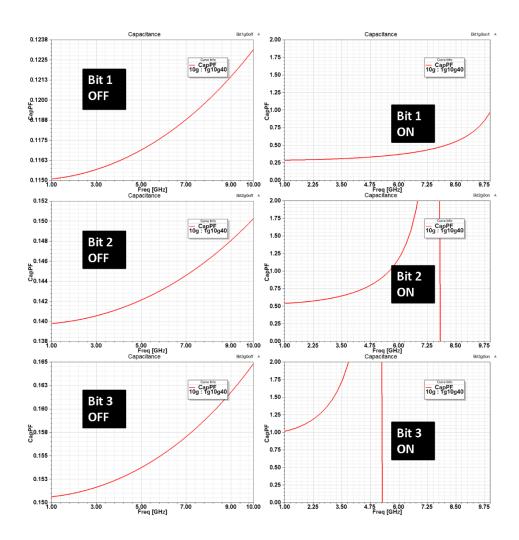

| Fig 4.23: HFSS electromagnetic simulation results for the extracted capacitance of the three individual bits       |

|--------------------------------------------------------------------------------------------------------------------|

| that make the capacitor bank                                                                                       |

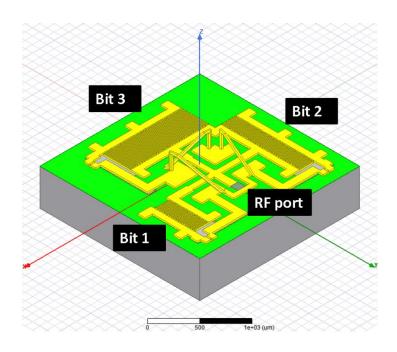

| Fig 4.24: The structure of the 3-bit high-power capacitor bank simulated and analyzed in HFSS. The                 |

| analysis takes into consideration the required $200\mu m$ -high and $40\mu m$ -thick gold wire bonding in addition |

| to the 25µm trench in the HRS substrate                                                                            |

| Fig 4.25: HFSS electromagnetic simulation results for the extracted capacitance of the three individual bits       |

| that make the capacitor bank                                                                                       |

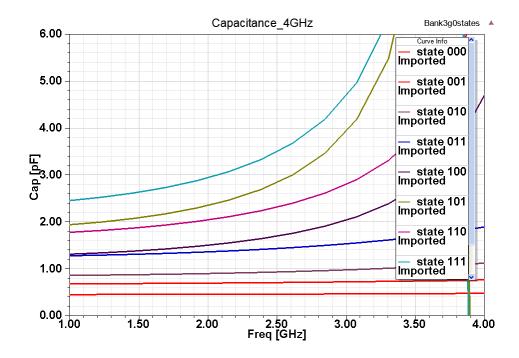

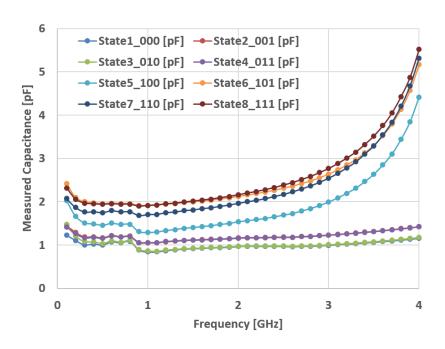

| Fig 4.26: Measurement results of the eight different states of the 3-bit capacitor bank                            |

| Fig 4.27: Capacitance extracted results of the eight different states of the 3-bit capacitor bank based on the     |

| measurement in order to correct for a malfunctioning bit                                                           |

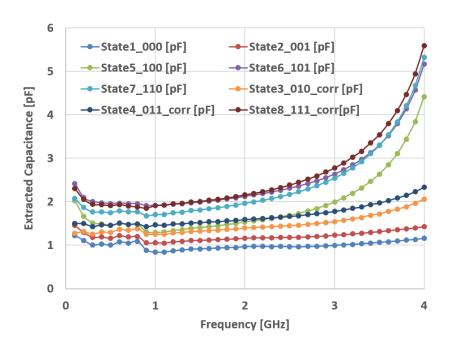

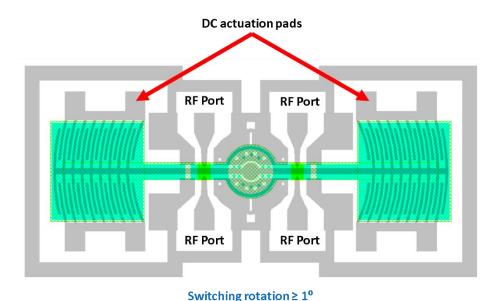

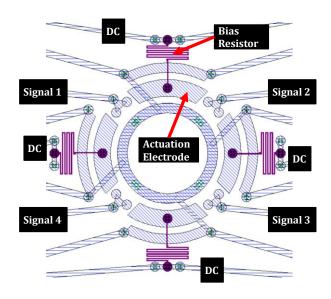

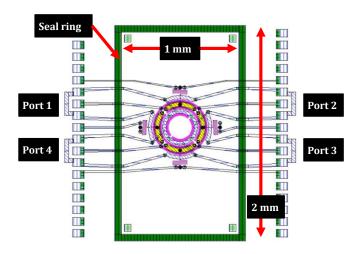

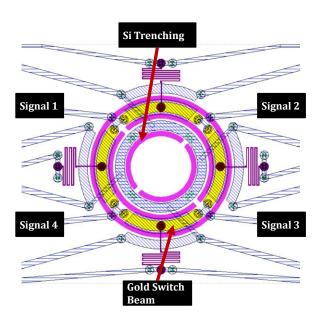

| Fig 4.28: An exact layout of the first generation design of the rotor-based switch implemented in the              |

| MetalMUMPs process. The nickel beam is supported by two narrow nitride beams in the locations shown.               |

| Applying the potential difference diagonally would result in the rotation of the nickel beam such that two         |

| ports at a time are diagonally connected                                                                           |

| Fig 4.29: The 3D structure of the first generation of the proposed rotor-based switch for low-frequency and        |

| high-power RF applications. The pairs of electrostatic actuation electrodes must be assigned diagonally as         |

| shown in order to rotate the switch beam. The patches at the RF ports are the lumped ports used for the            |

| simulation of the switch                                                                                           |

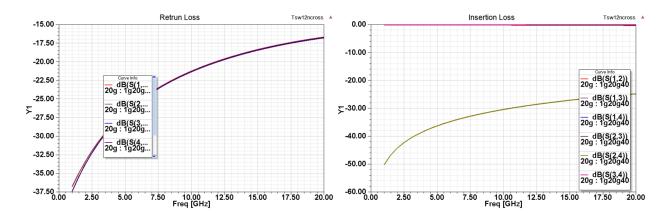

| Fig 4.30: The HFSS electromagnetic simulation results of the proposed rotor-based RF MEMS switch                   |

| revealing its acceptable performance up to 5GHz                                                                    |

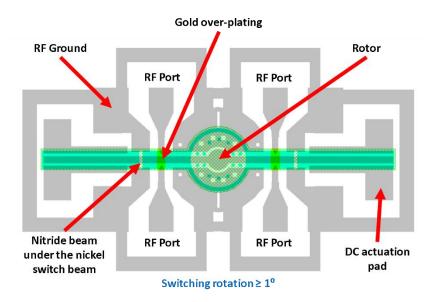

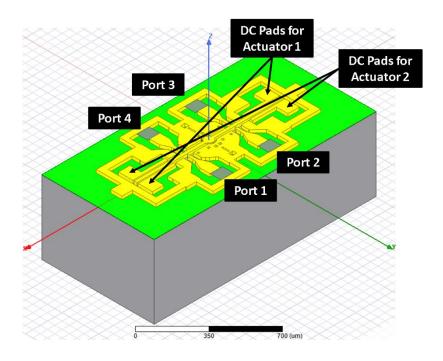

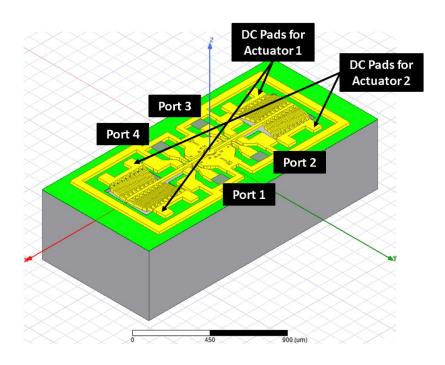

| Fig 4.31: An exact layout of the enhanced design of the rotor-based switch where larger rotation angles are        |

| possible and higher actuation capacitance is achieved, thus lowering the switching voltage71                       |

| Fig 4.32: The 3D structure of the improved design of the proposed rotor-based RF MEMS switch for low-              |

| frequency and high-power applications. The patches at the RF ports are the lumped ports used for the               |

| simulation of the switch                                                                                           |

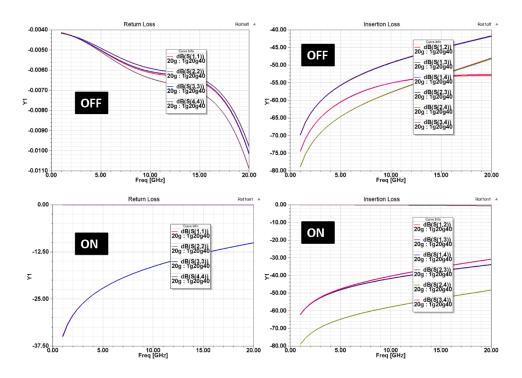

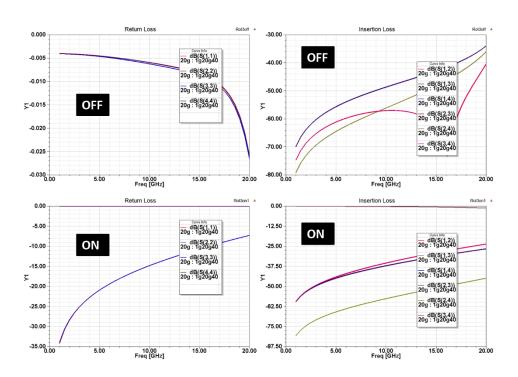

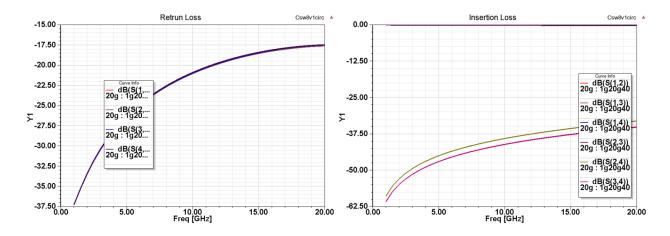

| Fig 4.33: The HFSS electromagnetic simulation results of the second generation of the proposed rotor-              |

| based RF MEMS switch revealing its acceptable performance up to 5GHz                                               |

| Fig 5.1: Cross-sectional view of the main UWMEMS process steps [77]                                                |

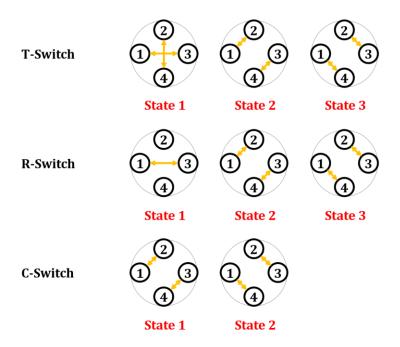

| Fig 5.2: Diagram illustrating the distinct states of the T-switch, R-switch and C-switch designs75                 |

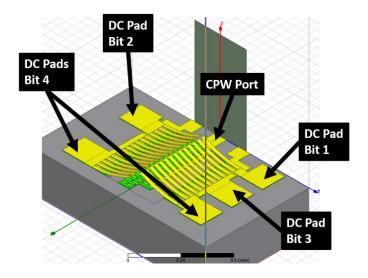

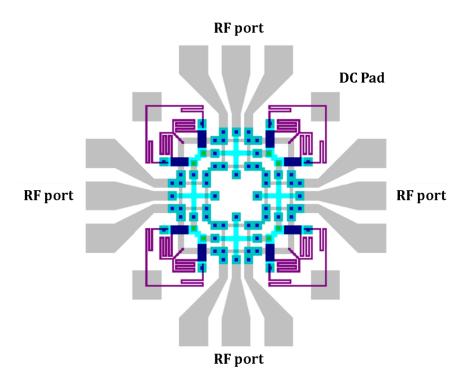

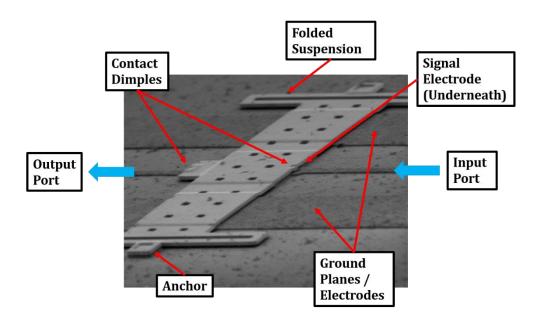

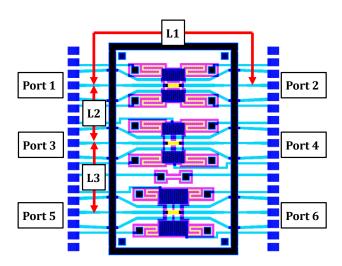

| Fig 5.3: Design of T-switch cell in standard UWMEMS process. Other more compact designs have been                  |

| also developed using a single series switch element per signal path. DC pads are $100\mu m$ each                   |

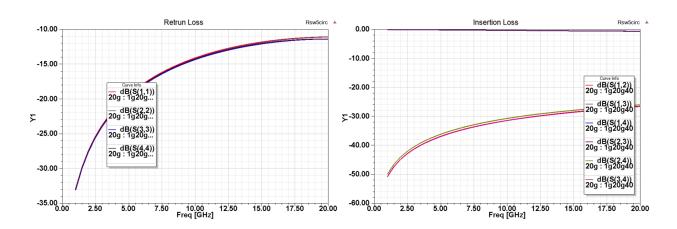

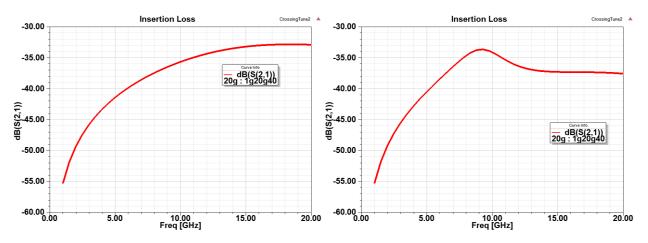

| Fig 5.4: HFSS 3D electromagnetic simulation results of the T-switch cell in the ON state with the cross-           |

| over or 180° state enabled                                                                                         |

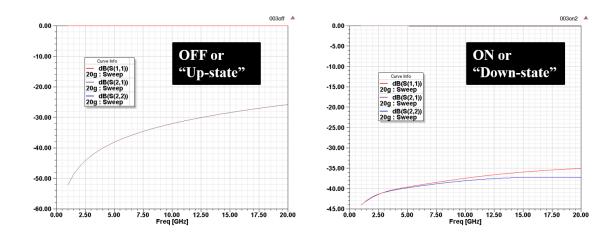

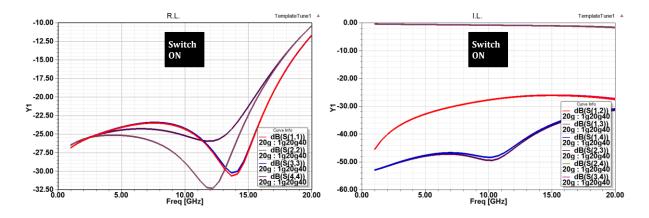

| Fig 5.5: HFSS 3D electromagnetic simulation results of the T-switch cell in the ON state with the periphera                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| or 90° state enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Fig 5.6: HFSS 3D electromagnetic simulation results of the T-switch cell high isolation in the OFF states.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Fig~5.7: Design~of~R-switch~cell~in~standard~UWMEMS~process~.~Other~designs~have~been~also~developed and the standard of the   |

| based on having two series switch elements per signal paths for the sake of better RF matching. DC pad                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| are 100µm each                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Fig~5.8:~HFSS~3D~electromagnetic~simulation~results~of~the~R-switch~cell~in~the~ON~state~with~the~180°~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~state~sta   |

| enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| $Fig \ 5.9: HFSS \ 3D \ electromagnetic \ simulation \ results \ of \ the \ R-switch \ cell \ in \ the \ ON \ state \ with \ the \ peripherature \ and \ an \ an \ an \ an \ an \ an \ a$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| or 90° state enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

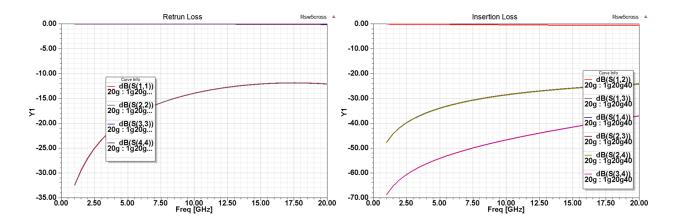

| Fig 5.10: HFSS 3D electromagnetic simulation results of the R-switch cell in the OFF state7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

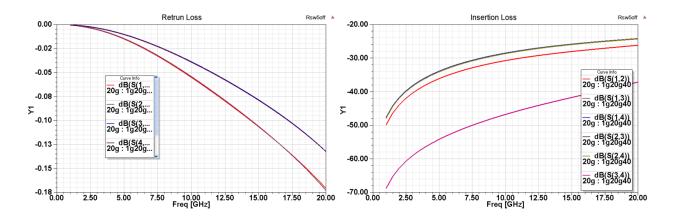

| $Fig \ 5.11: Design \ of \ C-switch \ cell \ in \ standard \ UWMEMS \ process \ . \ Other \ designs \ have \ been \ also \ developed \ and \ an$ |

| based on having two series switch elements per signal paths. DC pads are $100\mu m$ each                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

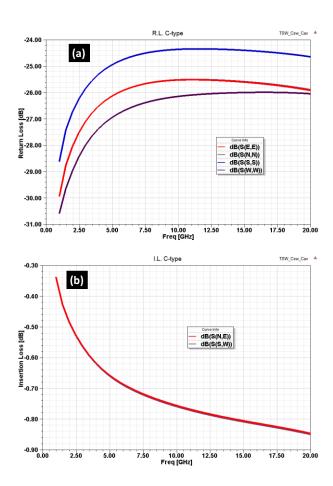

| Fig 5.12: HFSS 3D electromagnetic simulation results of the C-switch cell in the ON state                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Fig 5.13: HFSS 3D electromagnetic simulation results of the C-switch cell in the OFF state                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

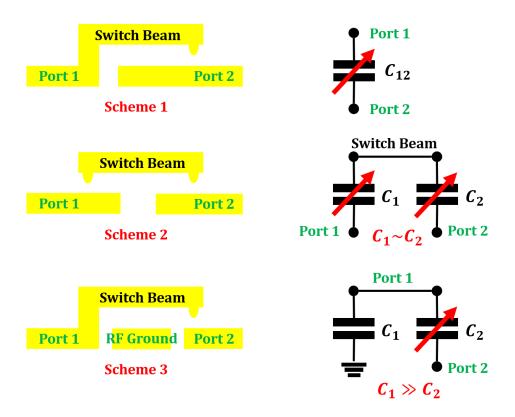

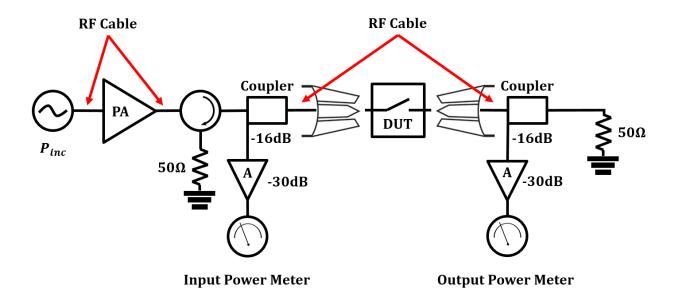

| Fig 5.14: Diagram illustrating the different options for the operation of an electrostatic self-actuation switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

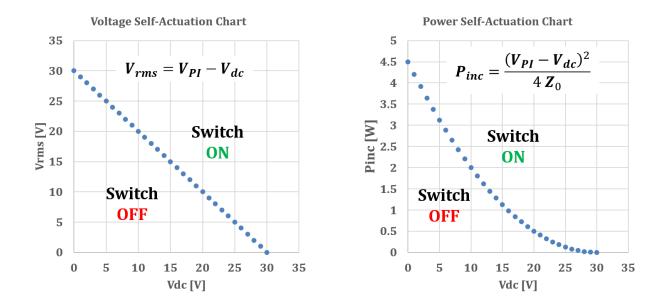

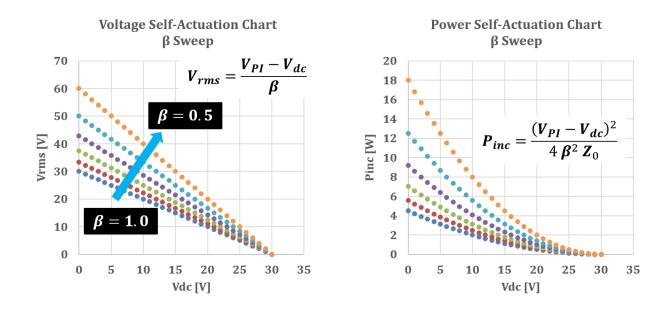

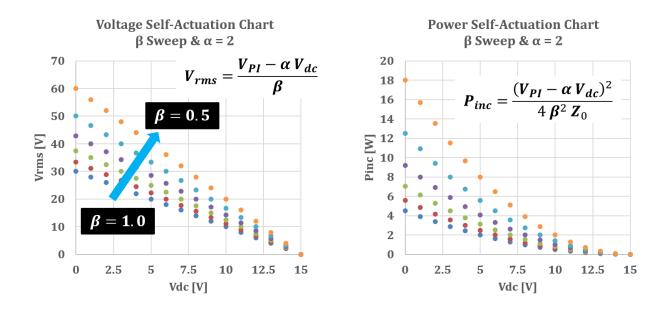

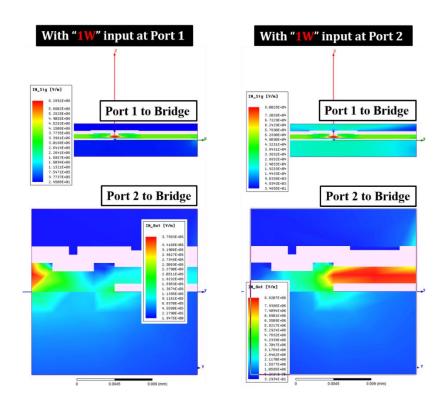

| Fig 5.15: An example of the self-actuation charts as a result of scheme 3 using the RMS value and the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| incident power level of the input RF signal at different DC voltage values. The electromechanical example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| assumes 30V pull-in onset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

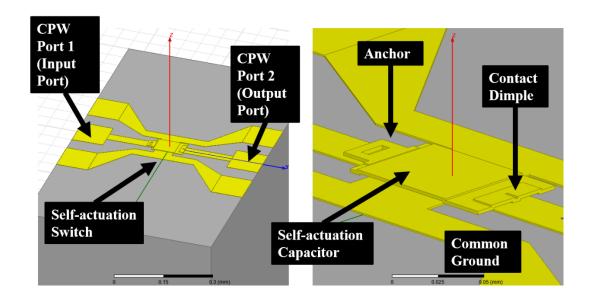

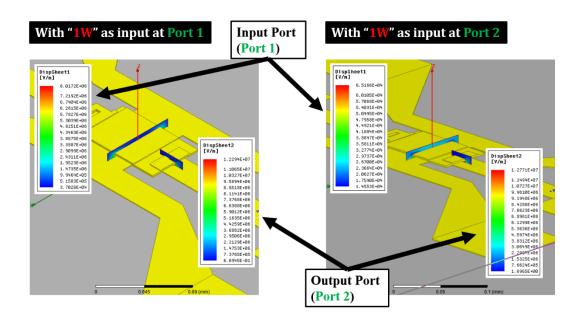

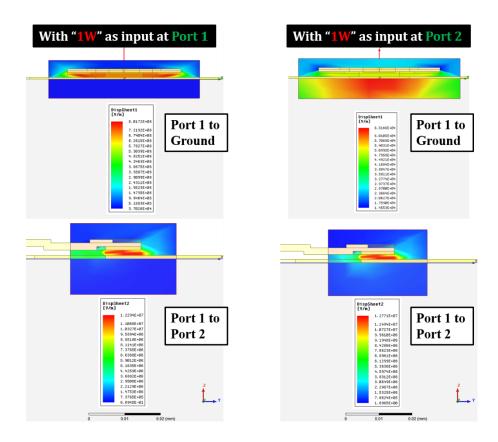

| Fig 5.16: 3D of the single-capacitor HSAS design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

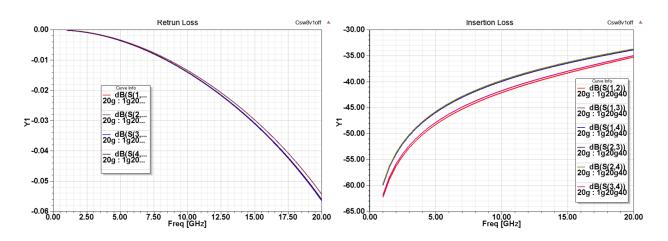

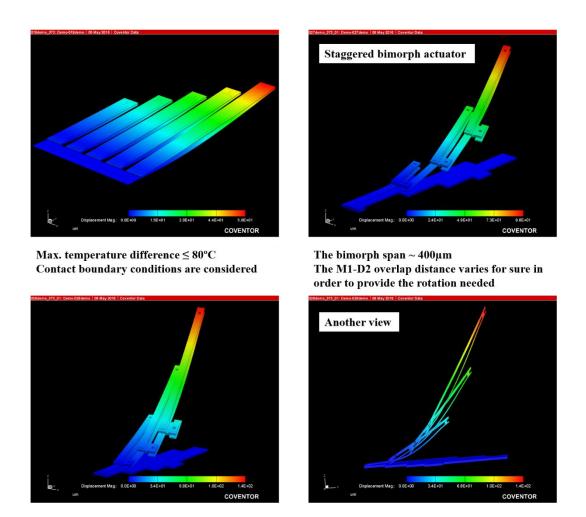

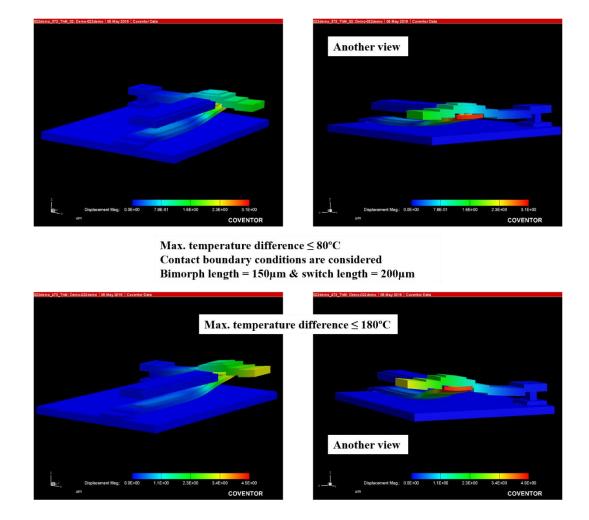

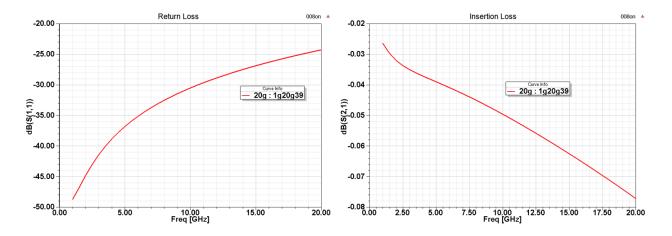

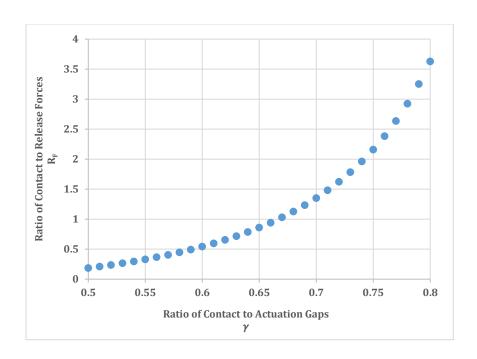

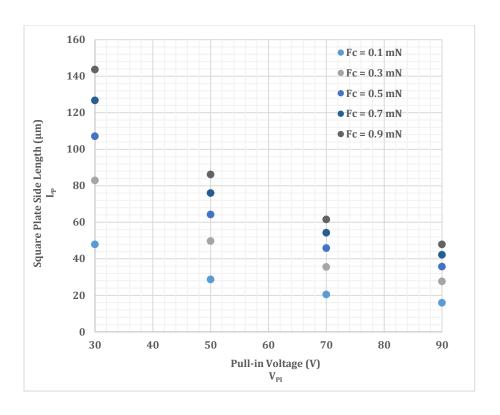

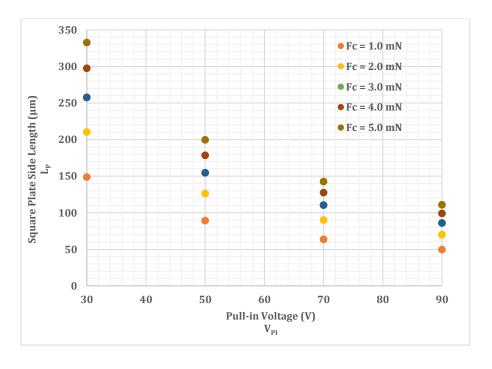

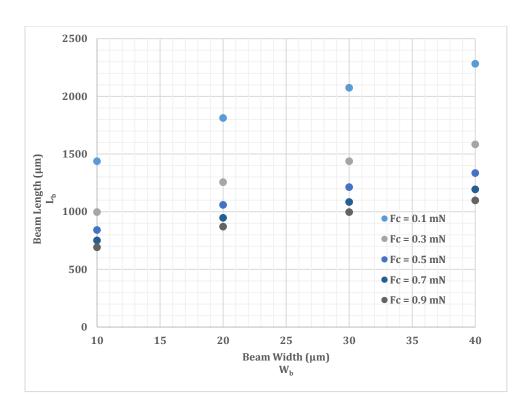

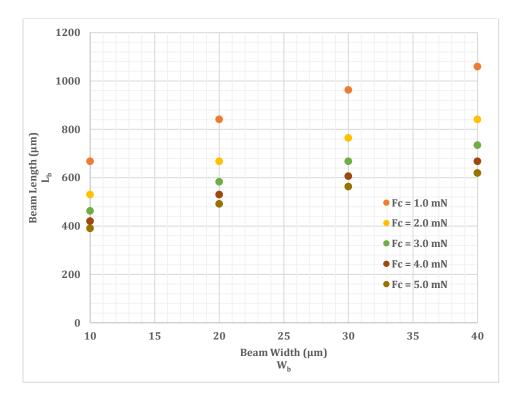

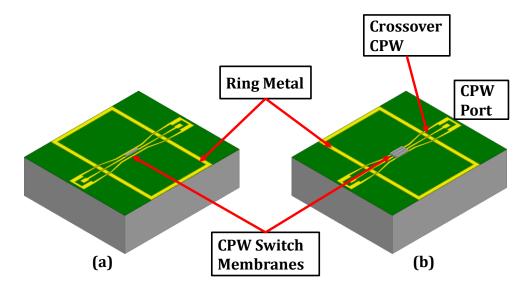

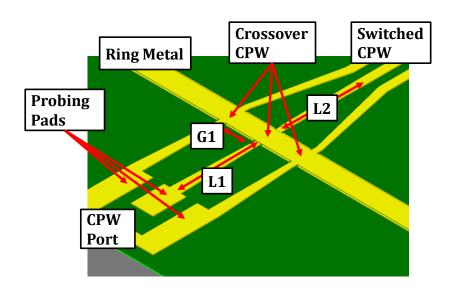

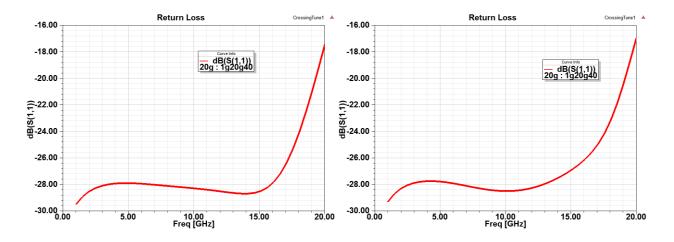

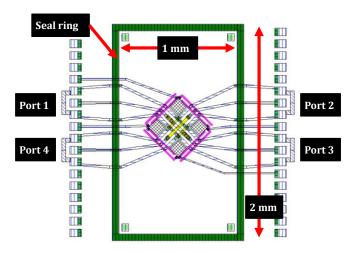

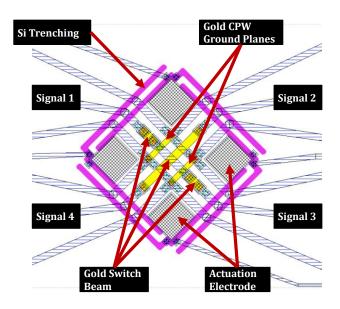

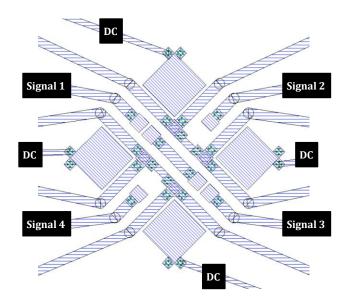

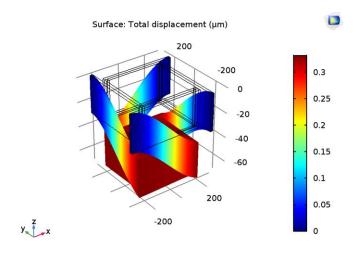

| Fig 5.17: HFSS electromagnetic simulation results for the single-capacitor HSAS design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |