# Assessment of Germanane Field-Effect Transistors for CMOS Technology

Yiju Zhao, AbdulAziz AlMutairi, and Youngki Yoon, Member, IEEE

Abstract-Using self-consistent atomistic quantum transport simulations, the device characteristics of n-type and p-type germanane (GeH) field-effect transistors (FETs) are evaluated. While both devices exhibit near-identical off-state characteristics, n-type GeH FET shows ~40% larger on current than the p-type counterpart, resulting in faster switching speed and lower power-delay product. Our benchmark of GeH FETs against similar devices based on 2D materials reveals that GeH outperforms MoS2 and black phosphorus in terms of energy-delay product (EDP). In addition, the performance of GeH-based CMOS circuit is analyzed using an inverter chain. By engineering power supply voltage and threshold voltage simultaneously, we find the optimal operating condition of GeH FETs, minimizing EDP in the CMOS circuit. Our comprehensive study including material parameterization, device simulation, and circuit analyses demonstrates significant potential of GeH FETs for 2D-material CMOS circuit applications.

Index Terms—Germanane, Field-Effect Transistor, Quantum Transport, Device Simulation, CMOS Circuit

## I. INTRODUCTION

wo-dimensional (2D) semiconductors such as transition metal dichalcogenides and black phosphorus have been in the spotlight for electronic device components of next-generation complementary metal-oxide-semiconductor (CMOS) technology due to their intriguing electrical and mechanical properties [1], [2]. For instance, a microprocessor based on molybdenum disulfide (MoS<sub>2</sub>) has significant potential of 2D demonstrated, exhibiting semiconductors for integrated circuits [3]. Recently, a new family of 2D materials based on group-IV such as germanane (GeH) and silicene has emerged [4]-[6]. GeH is a light-effective-mass material  $(m_e^* < 0.1m_0)$ , and an exceptionally high carrier mobility (>18,000 cm<sup>2</sup>/V·s) is theoretically predicted [4], while measured mobility of GeH field-effect transistor (FET) is still limited to much lower values (30 cm<sup>2</sup>/V·s) [7]. With regard to device performance, promising characteristics of GeH FETs have been predicted for high-performance applications [8]-[10]. Although n-type GeH

The first two authors contributed equally to this work. This work was supported in part by NSERC Discovery Grant (RGPIN-05920-2014) and in part by NSERC Strategic Project Grant (STPGP 478974-15). Computing resources were provided by Calcul Quebec through Compute Canada. AbdulAziz AlMutairi acknowledges the financial support by WIN Nanofellowship.

The authors are with Department of Electrical and Computer Engineering & Waterloo Institute for Nanotechnology (WIN) at the University of Waterloo, Waterloo, ON, Canada N2L 3G1 (Email: youngki.yoon@uwaterloo.ca).

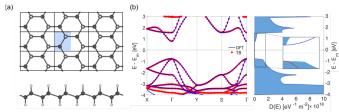

Fig. 1 (a) Top view (top panel) and side view (bottom panel) of GeH supercells chosen for NEGF simulation. Each supercell (black solid box) consists of two unit cells (blue shaded box). (b) (Left panel) Electronic band structure of the GeH supercell from DFT calculation (blue lines). Tight-binding (TB) bands are also shown (red dots), exhibiting excellent matching with the DFT bands. (Right panel) Density of states (DOS) of GeH, showing the significant difference of DOS in the conduction band  $(E_c)$  and the valence band  $(E_v)$ . (Inset) A zoom-in plot of DOS near the band edges, where the velocity of electrons (blue line) and holes (red line) as a function of energy is also provided, showing significantly higher electron velocity.

FETs have been carefully investigated based on atomistic quantum transport simulations [8], in-depth understanding of p-type GeH device is currently absent from the field. Notably, GeH has heavy holes and light holes, which cannot be captured with semi-classical models [10]. Moreover, to assess the GeH-based CMOS circuit performance, the characteristics of both n-type and p-type transistors should be accurately evaluated using rigorous atomistic quantum transport simulations.

The overall goal and the key contribution of this study is to assess GeH-based CMOS technology through rigorous quantum transport simulations of both n-type GeH FET (NMOS) and p-type counterpart (PMOS). For this, first n-type and p-type GeH FETs are investigated individually using self-consistent atomistic quantum transport simulation with tight-binding (TB) parameters extracted from density functional theory (DFT) bands. Second, intrinsic device performance metrics such as intrinsic delay and power-delay product are evaluated and compared against other similar 2D material devices. Finally, circuit-level analyses are conducted to optimize the operating condition of GeH FETs by engineering power supply voltage ( $V_{DD}$ ) and threshold voltage.

# II. SIMULATION METHODS

Electronic properties of GeH are described by TB parameters, which have been achieved through numerical fitting of the DFT band structure [8]. Transport properties are simulated based on the non-equilibrium Green's function (NEGF) method within a TB approximation, while self-consistent electrostatic potential is achieved by solving the Poisson's equation alongside the transport equation [11]. The following parameters are chosen for a nominal device: Monolayer GeH is used for the active material of the device. Channel length  $(L_{ch})$  is 15 nm and source/drain extensions are

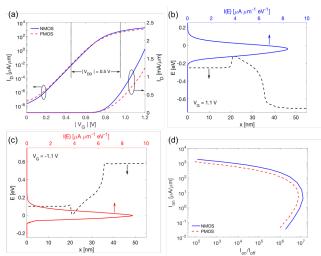

Fig. 2 Transfer characteristics of n-type and p-type monolayer GeH FETs. (a)  $I_D - |V_G|$  curves at  $|V_D| = 0.5$  V.  $V_G$  and  $V_D$  are positive (negative) for the n-type (p-type) transistor. (b) and (c) are energy-resolved current spectrum of the n-type (blue solid line; top axis) and the p-type (red solid line; top axis) GeH FET, respectively, at  $|V_G| = 1.1$  V and  $|V_D| = 0.5$  V.  $E_c$  and  $E_v$  are also shown in (b) and (c), respectively, along the device (black dashed line; bottom axis). (d)  $I_{on}$  vs.  $I_{on}/I_{off}$  plotted by shifting the position of the  $V_{DD}$  window shown in (a). On (off) state is defined at the right (left) boundary of the  $V_{DD}$  window.

20 nm. 3.85-nm-thick Al<sub>2</sub>O<sub>3</sub> ( $\kappa = 9$ ) are used with a single-gate geometry. Source/drain doping concentration is 8.25×10<sup>12</sup> cm<sup>-2</sup> for the n-type device, whereas a higher doping concentration of 1.65×10<sup>13</sup> cm<sup>-2</sup> is used for p-type GeH considering its larger density of states (DOS). Ballistic transport is assumed due to the relatively short channel length considered in this study. A supercell, consisting of two unit cells [Fig. 1(a)], is chosen to construct a Hamiltonian matrix (H) for the NEGF simulation. The left panel of Fig. 1(b) presents the band structure of the GeH supercell based on both DFT and TB, exhibiting the accurate description of electronic states with TB parameters, which is inherently impossible in semi-classical models. The right panel of Fig. 1(b) shows the DOS of GeH, which reveals that the DOS near the valance band edge  $(E_v)$  is  $\sim 6 \times$  larger than that near the conduction band edge  $(E_c)$ . In addition, the velocity of carriers is also plotted in the inset of Fig. 1(b), where it can be seen that electrons have significantly higher velocity than holes.

# III. RESULTS

Figure 2(a) shows the transfer characteristics of n-type and p-type GeH FETs in both a logarithmic scale (left axis) and a linear scale (right axis). While both devices exhibit near-ideal switching characteristic (SS ~68 mV/dec), it is observed that NMOS has ~40% larger on current than PMOS. To understand this, energy-resolved current spectrum (solid line; top axis) is plotted for the n-type and p-type GeH FET in Figs. 2(b) and 2(c), respectively, along with potential profile (dashed line; bottom axis) in the on state ( $|V_G| = 1.1 \text{ V}$ ). It is observed that NMOS has a wider current spectrum compared to PMOS due to the lower potential barrier at the same  $|V_G|$ . This is attributed mainly to the smaller DOS of n-type GeH, making the modulation of potential barrier by the gate easier. Although charge density in NMOS is limited by its small DOS, NMOS exhibits larger  $I_{on}$  than PMOS due to fact that the gain in the

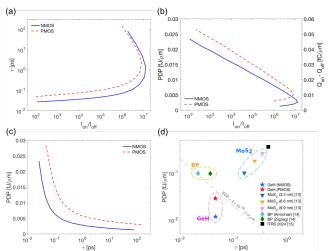

Fig. 3 Intrinsic device performance metrics. (a) Intrinsic delay  $(\tau)$ , (b) power-delay product (PDP; left axis) and  $Q_{on} - Q_{off}$  (right axis) as a function of  $I_{on}/I_{off}$ . (c) PDP- $\tau$  relations. (d) Benchmark of GeH FETs against similar FETs based on MoS<sub>2</sub> and black phosphorus (BP). ITRS 2024 requirement (black square) is also shown. The gray dashed guideline represents EDP =  $2 \times 10^{-30} \, \text{J} \cdot \text{s/um}$ .

carrier velocity overcomes the loss in charge density [8]. Notably, high carrier velocity in NMOS is the result of both large injection velocity (as shown in the inset of Fig. 1(b)) and large energy window for current flow as explained above. To evaluate both on and off states simultaneously, we plot  $I_{on}$  vs.  $I_{on}/I_{off}$  in Fig. 2(d) by shifting the  $V_{DD}$  window [dotted lines in Fig. 2(a)], which exhibits that NMOS outperforms PMOS device. For the same  $I_{on} = 500 \,\mu\text{A}/\mu\text{m}$ , NMOS shows  $I_{on}/I_{off} = 1.2 \times 10^5$ , which is larger than that of PMOS by ~1 order of magnitude.

It will be instructive to investigate the intrinsic performance of the individual GeH FET before circuit-level performance is discussed. Here we evaluate two important device performance metrics: intrinsic delay  $(\tau)$  and power-delay product (PDP), which correspond to the intrinsic limitation of switching speed and the dynamic power dissipation, respectively. Utilizing the simulation results, the intrinsic device characteristics are evaluated as  $\tau = (Q_{on} - Q_{off})/I_{on}$  and PDP =  $(Q_{on} - Q_{off})V_{DD}$ , where  $Q_{on}$  and  $Q_{off}$  are the charges at on and off state, respectively [12]. Figure 3(a) shows  $\tau$  vs.  $I_{on}/I_{off}$  for NMOS and PMOS at a constant  $|V_{DD}| = 0.5 \text{ V}$ . Switching speed, or inverse of the delay, of both devices monotonically increases as the  $V_{DD}$ window shifts from the subthreshold to the super-threshold region. It should be noted that switching speed of NMOS is faster than that of PMOS at high gate voltages, which is mainly due to the larger on current of NMOS as shown in Fig. 2(a). PDP vs.  $I_{on}/I_{off}$  is shown for NMOS and PMOS in Fig. 3(b), where switching energy increases commonly for both NMOS and PMOS as the device switches at higher gate voltages. It was observed that NMOS needs less energy to be switched. It should be noted that the non-monotonic behaviors observed at large delay and small PDP in Figs. 3(a) and 3(b) are attributed to the tunneling component existing at low gate voltages as shown in Fig. 2(a), which is consistent with a previous report [8]. We also plotted PDP-delay trade-off curves in Fig. 3(c), which manifests the inverse relation of switching energy and delay. Energy-delay product (EDP) of transistor is a figure of merit for the intrinsic device performance. The optimal point

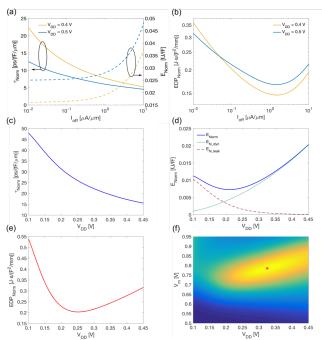

Fig. 4 Optimization of circuit-level figure-of-merits. (a) Normalized propagation delay ( $\tau_{\text{Norm}}$ ) and normalized energy ( $E_{\text{Norm}}$ ), and (b) normalized energy-delay product (EDP<sub>Norm</sub>) as a function of  $I_{off}$  at  $V_{DD}$  = 0.4 V and 0.5 V. (c)  $\tau_{\text{Norm}}$ , (d) normalized total energy (solid line), dynamic energy (dotted line) and leakage energy (dashed line), and (e) EDP<sub>Norm</sub> as a function of  $V_{DD}$  with the mid-point of  $V_{DD}$  window fixed at  $V_m$  = 0.7 V. (f) Color map of 1/EDP<sub>Norm</sub> for various  $V_{DD}$  and  $V_m$ .

can be determined at  $\tau=46.3$  fs and PDP = 11.7 aJ/ $\mu$ m for NMOS and at  $\tau=46.1$  fs and PDP = 28.7 aJ/ $\mu$ m for PMOS, where a product of PDP and  $\tau$  becomes minimum for each device. These optimal points of GeH-based NMOS and PMOS are plotted in Fig. 3(d), in which other similar 2D semiconductor devices, namely MoS<sub>2</sub> FETs [13] and black phosphorus (BP) FETs [14], are also included for comparison along with the ITRS 2024 requirement [15]. In general, 2D-material FETs have fast switching speed and low switching energy as compared to the ITRS 2024 requirement. Among them, GeH FETs exhibit the best performance with the lowest EDP ( $<2\times10^{-30}$  J·s/ $\mu$ m).

Next, we discuss the circuit-level performance of GeH FETs. We use normalized propagation delay  $(\tau_{Norm})$ , normalized energy (  $E_{Norm}$  ) and normalized energy-delay product (EDP<sub>Norm</sub>) for the circuit-level figure-of-merits (FOMs), following the method used for a similar study [16], [17]. Those circuit-level metrics are evaluated by using a simplified CMOS circuit: 15-stage ( $L_d = 15$ ), fan-out one (FO1) inverter chain with an average activity factor ( $\alpha = 0.1$ ) and balanced GeH FETs for NMOS and PMOS. First, we plot the normalized circuit-level FOMs as a function of  $I_{off}$  by changing the position of the  $V_{DD}$  window for a fixed  $V_{DD}$ . While  $\tau_{\text{Norm}}$  can be decreased by increasing  $I_{off}$  (i.e., reducing threshold voltage), it comes with the cost of increasing  $E_{Norm}$  since the normalized leakage energy becomes dominant in the super-threshold region as shown in Fig. 4(a). Therefore, by considering  $\tau_{\text{Norm}}$  and  $E_{\text{Norm}}$  simultaneously, the optimum point can be determined. Figure 4(b) presents the normalized energy-delay product as a function of  $I_{off}$ . For  $V_{DD} = 0.5$  V, the minimum  $EDP_{Norm}$  is 0.17 J·s/(F<sup>2</sup>/mm), which is a 47% improvement as compared to the maximum value observed at  $I_{off} = 10^{-2} \,\mu\text{A/}\mu\text{m}$ . Notably, the minimum EDP<sub>Norm</sub> can be further reduced by engineering power supply voltage. If  $V_{DD} = 0.4 \text{ V}$  is used, EDP<sub>Norm</sub> decreases by 13% compared to that with  $V_{DD} = 0.5 \text{ V}$ . This indicates that smaller  $V_{DD}$  should be taken into account for the global optimization of operating condition of GeH FETs for CMOS circuits. Therefore, next we investigate the effect of  $V_{DD}$ . Figures 4(c)-4(e) show  $\tau_{\text{Norm}}$ ,  $E_{\text{Norm}}$  and EDP<sub>Norm</sub> as a function of  $V_{DD}$ , where the mid-point of  $V_{DD}$  window [ $V_m = (V_{on})$ +  $V_{off}$ ) / 2] is fixed at 0.7 V. We have observed a monotonic decrease of  $\tau_{\text{Norm}}$  with increasing  $V_{DD}$ , which indicates that the increase of  $I_{on}$  is predominant over the increase of  $V_{DD}$ . On the other hand, normalized total energy does not exhibit a monotonic trend with  $V_{DD}$  since  $E_{N_{\underline{}}dyn}$  and  $E_{N_{\underline{}}leak}$  compete with each other as shown in Fig. 4(d). EDP<sub>Norm</sub> vs.  $V_{DD}$  is further plotted in Fig. 4(e), which shows the minimum value of  $0.20 \text{ J} \cdot \text{s/(F}^2/\text{mm})$  at  $V_{DD} = 0.25 \text{ V}$ . Subsequently, we vary both  $V_{DD}$  and  $V_m$  to find the global optimum point for circuit-level performance of the GeH CMOS inverter chain. A color map of the inverse of EDP<sub>Norm</sub> in  $V_{DD}$  and  $V_m$  space is shown in Fig. 4(f). By performing computationally intensive device simulations for different power supply voltages and through careful circuit analyses, the minimum EDP<sub>Norm</sub> of 0.14 J·s/(F<sup>2</sup>/mm) has been achieved at  $V_{DD} = 0.32$  V and  $V_m = 0.78$  V for the GeH-based CMOS inverter chain.

#### IV. CONCLUSION

In this work, monolayer GeH NMOS and PMOS are evaluated for CMOS technology, based on self-consistent atomistic quantum transport simulations. While both NMOS and PMOS have excellent switching characteristics (SS ~68 mV/dec), n-type GeH exhibits ~40% better on-state performance due to its high carrier velocity, compared to the p-type counterpart. We also calculated intrinsic delay and switching energy of GeH FETs and compared with similar 2D material FETs, exhibiting clear benefits of GeH over MoS<sub>2</sub> and BP in terms of energy-delay product. Furthermore, by engineering  $V_{DD}$  and threshold voltage, we identified the optimal operating condition of GeH FETs to minimize energy-delay product in CMOS circuits. Our comprehensive study covering material, device and circuit suggests that germanane can be a significant contender for electronic devices of next-generation CMOS technology.

## REFERENCES

- [1] B. Radisavljevic, A. Radenovic, J. Brivio, V. Giacometti, and A. Kis, "Single-layer MoS<sub>2</sub> transistors," *Nat. Nanotechnol.*, vol. 6, pp. 147–150, Mar. 2011. doi:10.1038/NNANO.2010.279.

- [2] H. Liu, A. T. Neal, Z. Zhu, Z. Luo, X. Xu, D. Tománek, and P. D. Ye, "Phosphorene: An unexplored 2D semiconductor with a high hole mobility," ACS Nano, vol. 8, no. 4, pp. 4033–4041, Mar. 2014. doi:10.1021/nn501226z.

- [3] S. Wachter, D. K. Polyushkin, O. Bethge, and T. Mueller, "A microprocessor based on a two-dimensional semiconductor," *Nat. Commun.*, vol. 8, p. 14948, Apr. 2017. doi:10.1038/ncomms14948.

- [4] E. Bianco, S. Butler, S. Jiang, O. D. Restrepo, W. Windl, and J. E. Goldberger, "Stability and exfoliation of germanane: A germanium graphane analogue," ACS Nano, vol. 7, no. 5, pp.

4

- 4414-4421, May 2013. doi:10.1021/nn4009406.

- [5] P. Vogt, P. Capiod, M. Berthe, A. Resta, P. De Padova, T. Bruhn, G. Le Lay, and B. Grandidier, "Synthesis and electrical conductivity of multilayer silicene," *Appl. Phys. Lett.*, vol. 104, no. 2, p. 21602, Jan. 2014. doi:10.1063/1.4861857.

- [6] A. Molle, J. Goldberger, M. Houssa, Y. Xu, S.-C. Zhang, and D. Akinwande, "Buckled two-dimensional Xene sheets," *Nat Mater*, vol. 16, no. 2, pp. 163–169, Feb. 2017. doi:10.1038/nmat4802.

- [7] B. N. Madhushankar, A. Kaverzin, T. Giousis, G. Potsi, D. Gournis, P. Rudolf, G. R. Blake, C. H. van der Wal, and B. J. van Wees, "Electronic properties of germanane field-effect transistors," 2D Mater., vol. 4, no. 2, p. 21009, 2017. doi:10.1088/2053-1583/aa57fd.

- [8] A. AlMutairi, Y. Zhao, D. Yin, and Y. Yoon, "Performance Limit Projection of Germanane Field-Effect Transistors," *IEEE Electron Device Lett.*, vol. 38, no. 5, pp. 673–676, May 2017. doi:10.1109/LED.2017.2681579.

- [9] R. K. Ghosh, M. Brahma, and S. Mahapatra, "Germanane: A low effective mass and high bandgap 2-D channel material for future FETs," *IEEE Trans. Electron Devices*, vol. 61, no. 7, pp. 2309–2315, Jul. 2014. doi:10.1109/TED.2014.2325136.

- [10] K. L. Low, W. Huang, Y. C. Yeo, and G. Liang, "Ballistic transport performance of silicane and germanane transistors," *IEEE Trans. Electron Devices*, vol. 61, no. 5, pp. 1590–1598, 2014. doi:10.1109/TED.2014.2313065.

- [11] S. Datta, *Quantum Transport: Atom to Transistor*. Cambridge University Press, 2005. doi:10.1017/CBO9781139164313.

- [12] S. O. Koswatta, M. S. Lundstrom, and D. E. Nikonov, "Performance comparison between p-i-n tunneling transistors and conventional MOSFETs," *IEEE Trans. Electron Devices*, vol. 56, no. 3, pp. 456–465, Mar. 2009. doi:10.1109/TED.2008.2011934.

- [13] D. Marian, E. Dib, T. Cusati, A. Fortunelli, G. Iannaccone, and G. Fiori, "Two-dimensional transistors based on MoS<sub>2</sub> lateral heterostructures," in *IEEE International Electron Devices Meeting (IEDM)*, 2016, pp. 352–355. doi:10.1109/IEDM.2016.7838413.

- [14] F. Liu, Y. Wang, X. Liu, J. Wang, and H. Guo, "Ballistic transport in monolayer black phosphorus transistors," *IEEE Trans. Electron Devices*, vol. 61, no. 11, pp. 3871–3876, Nov. 2014. doi:10.1109/TED.2014.2353213.

- [15] "Process Integration, Devices, and Structures." [Online]. Available: http://www.itrs2.net/.

- [16] T. Agarwal, I. Radu, P. Raghavan, G. Fiori, A. Thean, M. Heyns, and W. Dehaene, "Effect of material parameters on two-dimensional materials based TFETs: An energy-delay perspective," in *European Solid-State Device Research Conference (ESSDERC)*, 2016, pp. 47–50. doi:10.1109/ESSCIRC.2016.7598241.

- [17] T. kumar Agarwal, B. Soree, I. Radu, P. Raghavan, G. Iannaccone, G. Fiori, W. Dehaene, and M. Heyns, "Material-Device-Circuit Co-optimization of 2D Material based FETs for Ultra-Scaled Technology Nodes," *Sci. Rep.*, vol. 7, p. 5016, Jul. 2017. doi:10.1038/s41598-017-04055-3.