## SOI RF-MEMS Based Variable Attenuator for Millimeter-Wave Applications

by

Navjot Kaur Khaira

A thesis

presented to the University of Waterloo

in fulfillment of the

thesis requirement for the degree of

Master of Applied Science

in

Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2019

© Navjot Kaur Khaira 2019

### **Declaration**

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### **Abstract**

The most-attractive feature of microelectromechanical systems (MEMS) technology is that it enables the integration of a whole system on a single chip, leading to positive effects on the performance, reliability and cost. MEMS has made it possible to design IC-compatible radio frequency (RF) devices for wireless and satellite communication systems. Recently, with the advent of 5G, there is a huge market pull towards millimeter-wave devices. Variable attenuators are widely employed for adjusting signal levels in high frequency equipments. RF circuits such as automatic gain control amplifiers, broadband vector modulators, full duplex wireless systems, and radar systems are some of the primary applications of variable attenuators.

This thesis describes the development of a millimeter-wave RF MEMS-based variable attenuator implemented by monolithically integrating Coplanar Waveguide (CPW) based hybrid couplers with lateral MEMS varactors on a Silicon–on–Insulator (SOI) substrate. The MEMS varactor features a Chevron type electrothermal actuator that controls the lateral movement of a thick plate, allowing precise change in the capacitive loading on a CPW line leading to a change in isolation between input and output. Electrothermal actuators have been employed in the design instead of electrostatic ones because they can generate relatively larger in-line deflection and force within a small footprint. They also provide the advantage of easy integration with other electrical microsystems on the same chip, since their fabrication process is compatible with general IC fabrication processes. The development of an efficient and reliable actuator has played an important role in the performance of the proposed design of MEMS variable attenuator. A Thermoreflectance (TR) imaging system is used to acquire the surface temperature profiles of the electrothermal actuator employed in the design, so as to study the temperature distribution, displacement and failure analysis of the Chevron actuator.

The  $60\,\mathrm{GHz}$  variable attenuator was developed using a custom fabrication process on an SOI substrate with a device footprint of  $3.8\,\mathrm{mm} \times 3.1\,\mathrm{mm}$ . The fabrication process has a high yield due to the high-aspect-ratio single-crystal-silicon structures, which are free from warping, pre-deformation and sticking during the wet etching process. The SOI wafer used has a high resistivity (HR) silicon (Si) handle layer that provides an excellent substrate material for RF communication devices at microwave and millimeter wave frequencies. This low-cost fabrication process provides the flexibility to extend

this module and implement more complex RF signal conditioning functions. It is thus an appealing candidate for realizing a wide range of reconfigurable RF devices. The measured RF performance of the  $60\,\text{GHz}$  variable attenuator shows that the device exhibits attenuation levels ( $|S_{21}|$ ) ranging from  $10\,\text{dB}$  to  $25\,\text{dB}$  over a bandwidth of  $4\,\text{GHz}$  and a return loss of better than  $20\,\text{dB}$ .

The thesis also presents the design and implementation of a MEMS-based impedance tuner on a Silicon-On-Insulator (SOI) substrate. The tuner is comprised of four varactors monolithically integrated with CPW lines. Chevron actuators control the lateral motion of capacitive thick plates used as contactless lateral MEMS varactors, achieving a capacitance range of 0.19 pF to 0.8 pF. The improvement of the Smith chart coverage is achieved by proper choice of the electrical lengths of the CPW lines and precise control of the lateral motion of the capacitive plates. The measured results demonstrate good impedance matching coverage, with an insertion loss of 2.9 dB.

The devices presented in this thesis provide repeatable and reliable operation due to their robust, thick-silicon structures. Therefore, they exhibit relatively low residual stress and are free from stiction and micro-welding problems.

### Acknowledgements

I would like to extend my deepest gratitude to my supervisor Dr. Raafat R. Mansour. He is an excellent example of a successful engineer and professor. It has been an honor to be his student. I had very limited knowledge of RF engineering when I joined his group, but he has guided me through the design, simulations, fabrication and measurements in my research making this a huge learning experience for me. I am indebted to him for his generous contributions of time, ideas, resources and encouragement to make my research experience productive and stimulating. The enthusiasm he has for research is contagious and kept me motivated. Apart from research, I have learnt a lot of life skills from him, especially the value of patience.

I have no words to express my thanks to my best friend, my colleague, my husband Tejinder Singh for his unconditional love, support and unflinching care throughout my journey. He is a passionate engineer and never fails to fascinate me with his engineering and computer skills. He has taught me to embrace being a lifelong learner, and is always the first one to praise, console or protect me when needed. I consider myself extremely lucky to have met him. He has stood by my side during all the successes and failures of my life. I wouldn't have reached this far without him.

I would also like to thank Prof. Omar Ramahi and Prof. Eihab Abdel Rahman who taught me such wonderful courses during my graduate studies. I also want to deeply acknowledge the members of the CIRFE group including Frank Jiang, Farzad Yazdani, Ahmed Abdel-Aziz and Desireh Shojaei-Asanjan, who have contributed immensely through the valuable discussions to make this a meaningful experience for me. I would like to thank our previous lab manager, Bill Jolley, whose professional experience has been a great help at several times in our research projects. Finally, I really appreciate all the QNC staff members who trained me on several cleanroom equipment and were always there to help.

Aside from my academic colleagues, I want to address my family for all their love and encouragement: my father who raised me with a love of science and supported me in all my pursuits, and my mother whose spirituality and positive outlook towards life has been the guiding compass for me. Her kind words always put me at ease whenever I am stressed in my life. My sister Harmanjot Kaur has been my best friend all my life and

I love her dearly and thank her for all her emotional support. I will not miss a chance to thank my younger brother Jagteshwar Singh for bringing all the fun and laughter into my life. I am grateful to my mother-in-law and father-in-law for all their love and encouragement.

I would like to thank my Lord Sri Guru Granth Sahib for providing me the wisdom and strength during all the low times of my life and blessing me with such amazing and loving people in my life. He has given me the intelligence and will-power to learn and explore the wonders that He has created, for nothing is possible without His will.

### Dedication

To my loving husband Tejinder Singh and my parents.

## **Table of Contents**

| Li         | st of 1       | Figures  |                                                | Xi  |  |

|------------|---------------|----------|------------------------------------------------|-----|--|

| Li         | ist of Tables |          |                                                |     |  |

| G          | lossary       |          |                                                |     |  |

| <b>A</b> l | bbrev         | iations  | <b>3</b>                                       | xxi |  |

| 1          | Intr          | oductio  | on                                             | 1   |  |

|            | 1.1           | Motiv    | ration                                         | 1   |  |

|            | 1.2           | Object   | tives                                          | 3   |  |

|            | 1.3           | Thesis   | Outline                                        | 4   |  |

| 2          | Lite          | rature l | Review                                         | 6   |  |

|            | 2.1           | Variab   | ole Attenuators Using Solid-State Devices      | 6   |  |

|            |               | 2.1.1    | Single/Double Hybrid Coupler and Varactors     | 7   |  |

|            |               | 2.1.2    | PIN Diodes and 0 dB Coupler                    | 10  |  |

|            |               | 2.1.3    | Millimeter Wave CMOS-Based Variable Attenuator | 12  |  |

|            | 2.2           | Gas D    | Discharge Tube-Based Variable Attenuator       | 14  |  |

|            | 2.3           | Graph    | nene-Based Variable Attenuator                 | 15  |  |

|            |               |          |                                                |     |  |

### Table of Contents

|   | 2.4  | VO <sub>2</sub> Based Variable Attenuator          | 17 |

|---|------|----------------------------------------------------|----|

|   | 2.5  | RF-MEMS Based Millimeter-Wave Variable Attenuators | 18 |

| 3 | Rea  | lization of High Aspect Ratio MEMS Actuators       | 24 |

|   | 3.1  | MEMS Actuators                                     | 24 |

|   |      | 3.1.1 Direction of Motion                          | 24 |

|   |      | 3.1.2 Operating Voltage/Power                      | 26 |

|   |      | 3.1.3 Materials                                    | 26 |

|   | 3.2  | Electrothermal Actuators                           | 27 |

|   | 3.3  | Design of Chevron Actuator                         | 32 |

|   | 3.4  | Simulated Results                                  | 34 |

|   | 3.5  | Fabrication Process                                | 36 |

|   | 3.6  | Deep Reactive Ion Etching (DRIE)                   | 41 |

|   |      | 3.6.1 Mask Selection for DRIE                      | 44 |

| 4 | The  | rmal Analysis of Microactuator                     | 47 |

|   | 4.1  | Introduction                                       | 47 |

|   | 4.2  | Thermoreflectance Imaging                          | 49 |

|   | 4.3  | Design and Fabrication of MEMS Chevron Actuator    | 50 |

|   | 4.4  | Experimental Setup                                 | 52 |

|   | 4.5  | Results and Discussion                             | 54 |

|   | 4.6  | Summary                                            | 58 |

| 5 | Vari | iable Attenuator for Millimeter-Wave Applications  | 60 |

|   | 5.1  | Introduction                                       | 60 |

|   | 5.2  | Design and Operation Principle                     | 62 |

### Table of Contents

|    |              | 5.2.1    | MEMS Varactors-Loaded CPW Line   | 65 |

|----|--------------|----------|----------------------------------|----|

|    |              | 5.2.2    | Hybrid Coupler                   | 67 |

|    | 5.3          | Result   | s and Discussion                 | 71 |

|    | 5.4          | Summ     | nary                             | 74 |

| 6  | Moı          | nolithic | eally Integrated Impedance Tuner | 75 |

|    | 6.1          | Introd   | uction                           | 75 |

|    | 6.2          | Princi   | ple of Operation                 | 77 |

|    | 6.3          | Device   | e Design and Fabrication         | 77 |

|    | 6.4          | Result   | s and Discussion                 | 80 |

|    | 6.5          | Summ     | nary                             | 81 |

| 7  | Con          | clusior  | and Future Work                  | 83 |

|    | 7.1          | Contri   | ibutions                         | 83 |

|    | 7.2          | Future   | e Work                           | 85 |

| Th | esis         | List of  | Publications                     | 86 |

| Re | eferences 87 |          |                                  |    |

# **List of Figures**

| 2.1  | Schematic of a variable attenuator using 3-dB hybrid coupler                                        | 7  |

|------|-----------------------------------------------------------------------------------------------------|----|

| 2.2  | Reflection type variable attenuator with single hybrid coupler and two varactors                    | 8  |

| 2.3  | Variable attenuator using single hybrid coupler                                                     | 8  |

| 2.4  | Variable attenuator using two hybrid couplers                                                       | 9  |

| 2.5  | Variable attenuator fabricated on a PCB using single and double hybrid coupler approach [9]         | 9  |

| 2.6  | High frequency equivalent circuit of PIN diode                                                      | 10 |

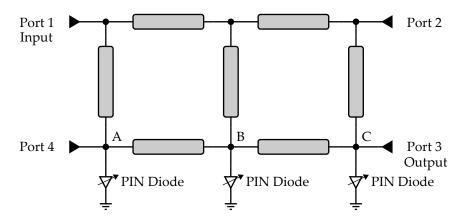

| 2.7  | Schematic diagram of variable attenuator showing the PIN diodes and 0-dB coupler                    | 11 |

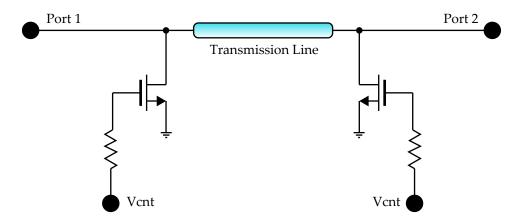

| 2.8  | Variable attenuator $\pi$ -configuration showing a transmission line and two shunt NMOS transistors | 12 |

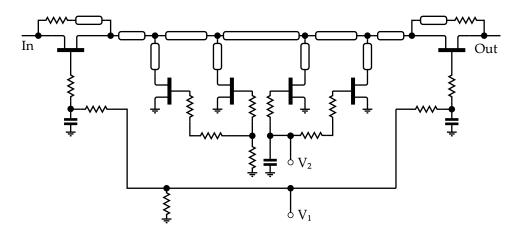

| 2.9  | RF circuit schematic of the DC-50 GHz MMIC attenuator                                               | 13 |

| 2.10 | GDTs with wire leads, no wire lead and surface mount packages. [21]                                 | 14 |

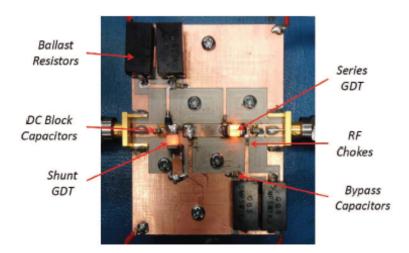

| 2.11 | Fabricated GDT-based variable RF attenuator showing GDTs connected in series-shunt topology [22]    | 15 |

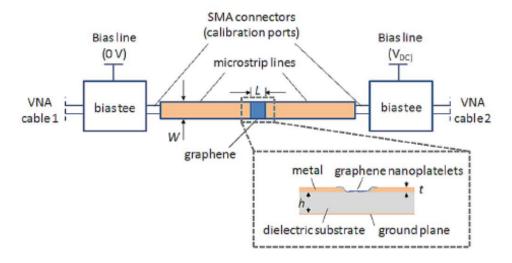

| 2.12 | Measurement setup of the graphene-based microstrip attenuator [23]                                  | 16 |

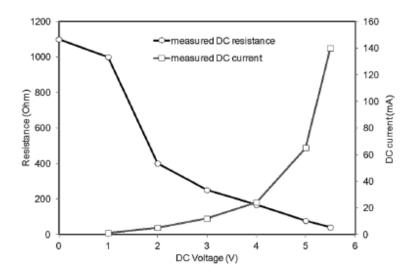

| 2.13 | Measured dc current vs dc resistance of the graphene-based microstrip variable attenuator [23]      | 16 |

### List of Figures

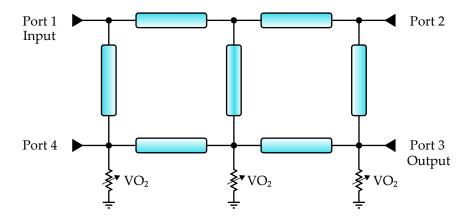

| 2.14 | Schematic of the variable attenuator using VO2 variable resistor and 0-dB hybrid coupler.                                                                                                                                                                    | 17 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

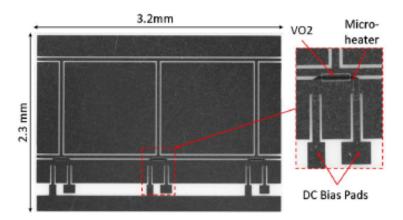

| 2.15 | Optical micrograph of the fabricated variable attenuator showing microheater elements [25]                                                                                                                                                                   | 18 |

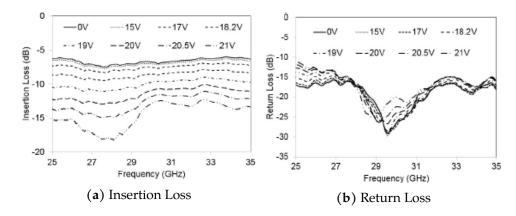

| 2.16 | Measured RF performance of $VO_2$ based variable attenuator [25]                                                                                                                                                                                             | 18 |

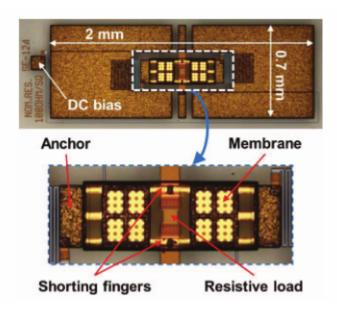

| 2.17 | (Top image) The micrograph of the fabricated variable attenuator showing CPW lines and DC bias pads, (Bottom image) Close-up of the fabricated device showing electrostatically-controlled gold membranes, poly-Si resistive load, and shorting fingers [26] | 19 |

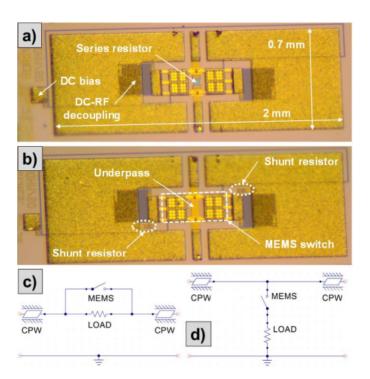

| 2.18 | (a) Micrograph of the series design with an in-line poly-Si resistor; (b) Micrograph of the shunt design with two shunt-to-ground poly-Si resistors; (c) lumped-element model of series design; (d) lumped element model of the shunt attenuator [27]        | 20 |

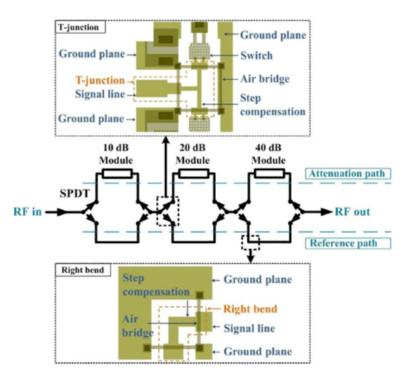

| 2.19 | Overview of the 3-bit reconfigurable attenuator based on RF MEMS SPDT switches. [28]                                                                                                                                                                         | 21 |

| 2.20 | RF performance of each state of the fabricated 3-bit MEMS attenuator [28]                                                                                                                                                                                    | 22 |

| 2.21 | (a) Reconfigurable RF-MEMS attenuator showing the eight cascaded switching units; (b) Equivalent lumped element network of each stage of 8-bit attenuator, including the switches (SW1 to SW8) and the resistive loads (R1 to R8). [29]                      | 22 |

| 3.1  | Bi-morph thermal actuator design for out-of-plane [40]                                                                                                                                                                                                       | 25 |

| 3.2  | Thermal actuator design for in-plane motion                                                                                                                                                                                                                  | 25 |

| 3.3  | Electrostatic actuator configurations, (a) parallel plate actuator, (b) comb drive actuator. X denotes the direction of motion and h gives the capacitive gap between plates                                                                                 | 26 |

| 3.4  | Locking mechanisms in thermal actuators [43]                                                                                                                                                                                                                 | 27 |

| 3.5  | Two-arm electrothermal actuators [47] [48]                                                                                                                                                                                                                   | 28 |

| 3.6  | Three-arm electrothermal actuator                                                                                                                                                                                                                            | 29 |

| 3.7  | Geometrical constraints used to amplify the expansion motion (a) V-shaped beams (b) one-ring spring actuator with insulating beam as a constraint [51]. | 31    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 3.8  | (a) Chevron actuator design (b) lateral displacement observed on application of voltage [52]                                                            | 32    |

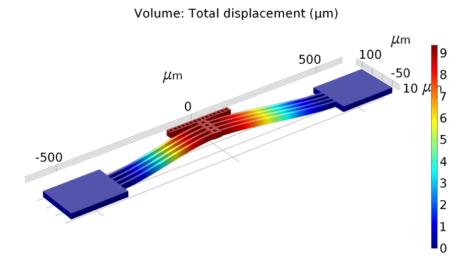

| 3.9  | FEM simulation of Chevron actuator showing lateral displacement with the application of voltage.                                                        | 34    |

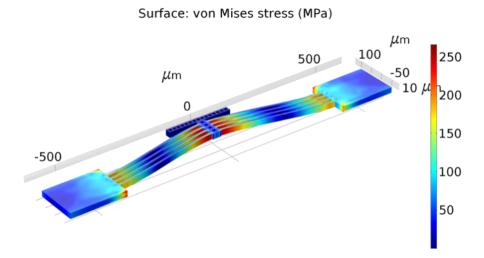

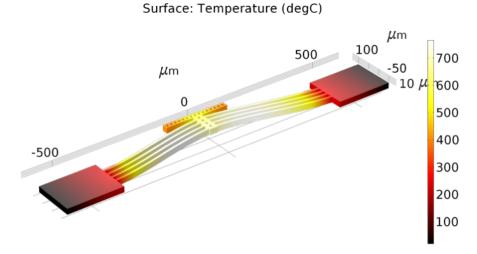

| 3.10 | FEM simulation of heat distribution across the Chevron actuator with applied potential difference across the pads                                       | 35    |

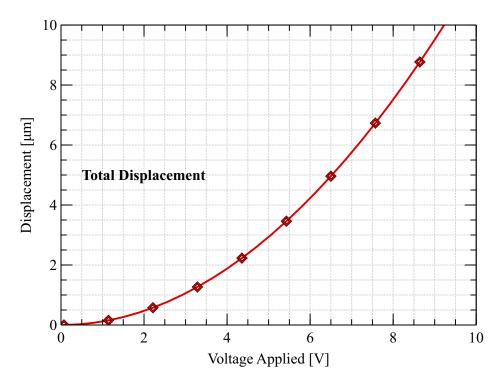

| 3.11 | Simulated results for total displacement of the Chevron actuator versus linear sweep of dc voltage                                                      | 35    |

| 3.12 | RCA cleaned bare SOI wafer showing the device layer, buried oxide and handle layer                                                                      | 36    |

| 3.13 | A 50 nm thick chrome seed layer on SOI wafer                                                                                                            | 37    |

| 3.14 | A 250nm thick gold layer, followed by another 30 nm chrome metal layer forming a stack of metal layers                                                  | 37    |

| 3.15 | An even layer of photoresist spin-coated on the top of metal layer                                                                                      | 37    |

| 3.16 | Patterns of photoresist formed on the top of metal layers after photolithography                                                                        | 38    |

| 3.17 | Etched metal layers after ion milling                                                                                                                   | 38    |

| 3.18 | Exposed metal layers after removing the photoresist mask                                                                                                | 39    |

| 3.19 | The high aspect ratio structures obtained after Si etching of the device layer.                                                                         | 39    |

| 3.20 | The released structures after controlled wet etching of oxide layer. Undercut can be observed under the anchor areas.                                   | 40    |

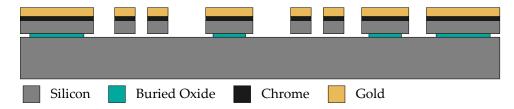

| 3.21 | Wire-bonding on the gold layer of structures                                                                                                            | 40    |

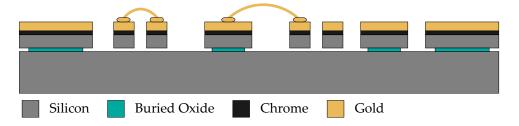

| 3.22 | BOSCH Si DRIE process alternates between etching and passivation steps [56                                                                              | ]. 42 |

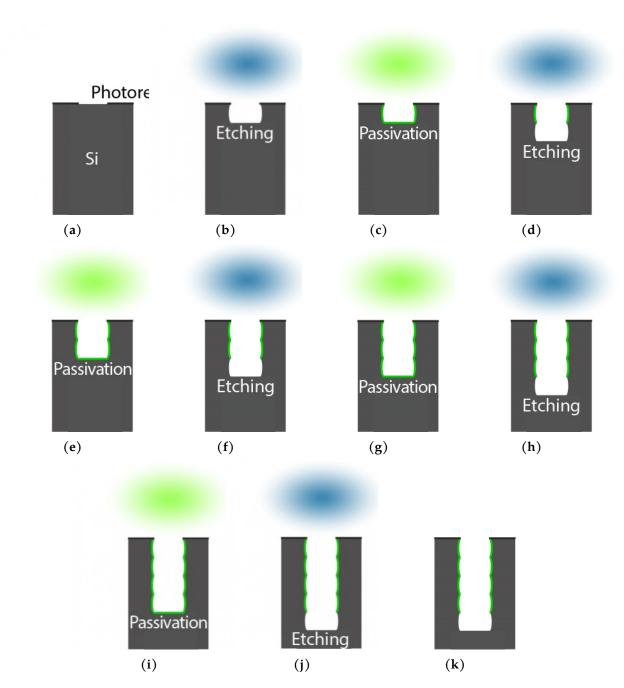

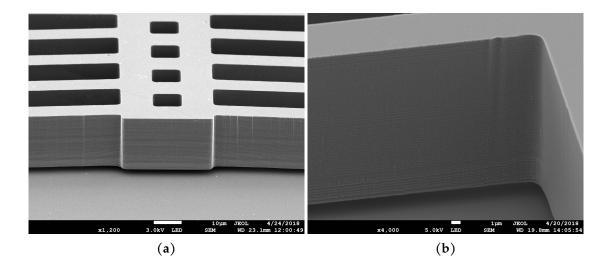

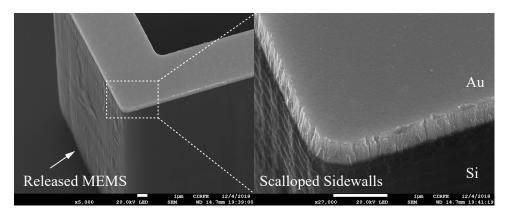

| 3.23 | (a) High aspect ratio structures achieved using Si Deep Reactive Ion Etching; (b) Scalloped walls of the microstructures due to cycles of Bosch etch.   | 44    |

| 3.24 | (a) Smooth sidewalls after Bosch etch; (b) Microstructures etched by Si-DRIE using photoresist mask; (c) Microstructures etched by Si-DRIE using hard mask; and (d) Micro-grass observed in the open areas of wafer |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | due to micromasking                                                                                                                                                                                                 | 45 |

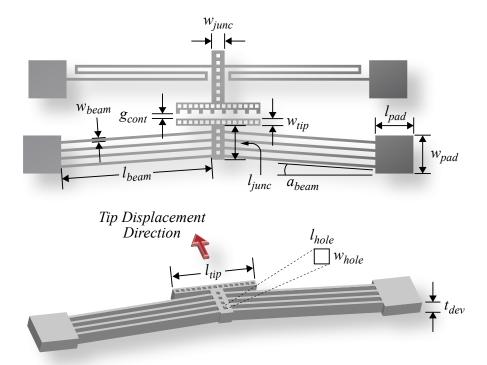

| 4.1  | Design dimensions of Chevron actuator                                                                                                                                                                               | 51 |

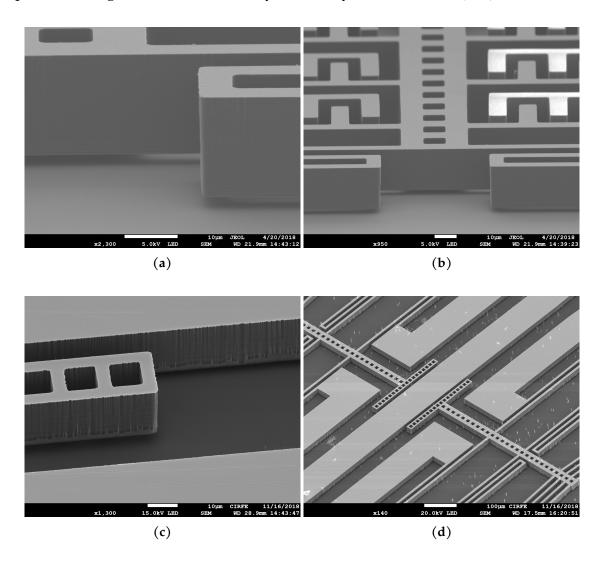

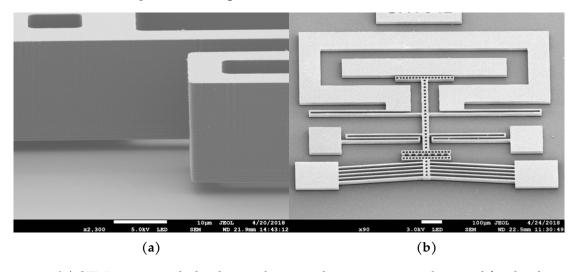

| 4.2  | (a) SEM micrograph the device showing chevron actuator designed for displacement purpose. (b) SEM micrograph of the released free-standing structure                                                                | 51 |

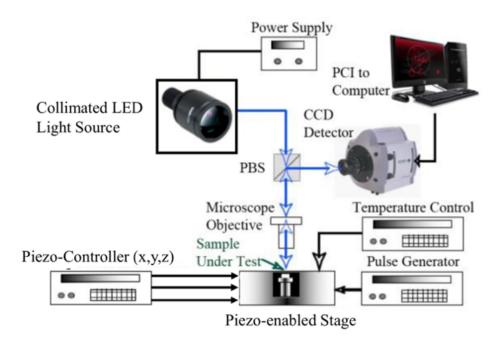

| 4.3  | Illustration of experimental setup used for Thermoreflectance imaging [71].                                                                                                                                         | 52 |

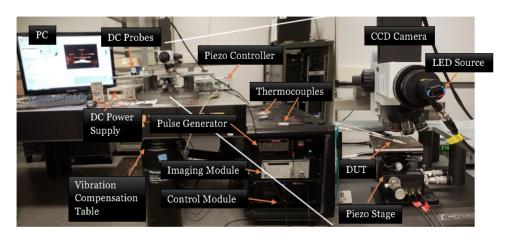

| 4.4  | Experimental setup at University of Waterloo                                                                                                                                                                        | 53 |

| 4.5  | Total tip displacement at 11 V input voltage                                                                                                                                                                        | 54 |

| 4.6  | Stress distribution showing 250 MPa stress                                                                                                                                                                          | 55 |

| 4.7  | Temperature distribution in Chevron actuator. Maximum temperature reaches at 740 degC at 11 V                                                                                                                       | 55 |

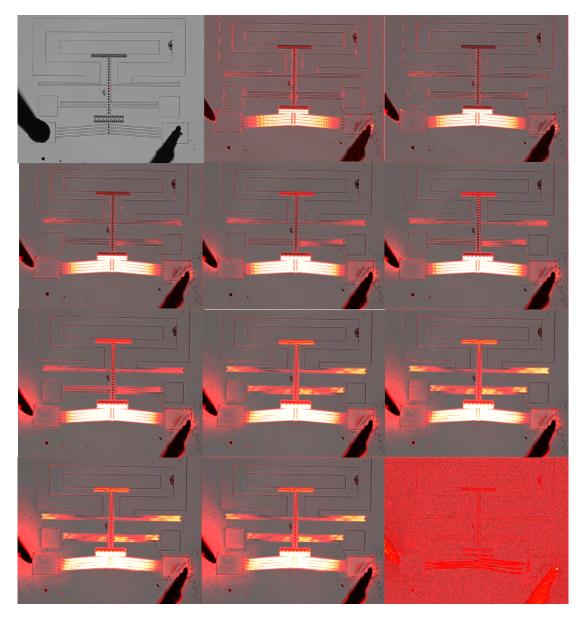

| 4.8  | Thermal imaging microscopy of Chevron actuator. (Top left) CCD image of Chevron actuator, (Top mid to bottom right) Thermal image during voltage application of 5 V to 13 V                                         | 56 |

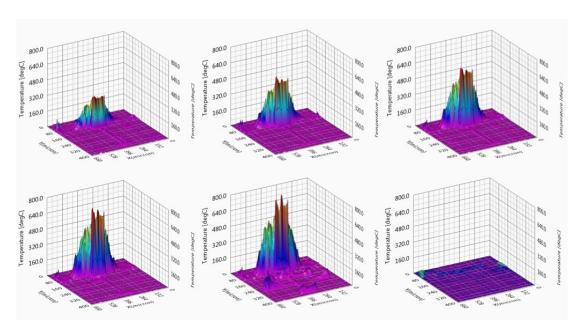

| 4.9  | 3D heat profile of thermally driven Chevron actuator at (from left to right) 5V, 6V, 7V, 9V, 11V and 13 V potential applied across actuator                                                                         | 57 |

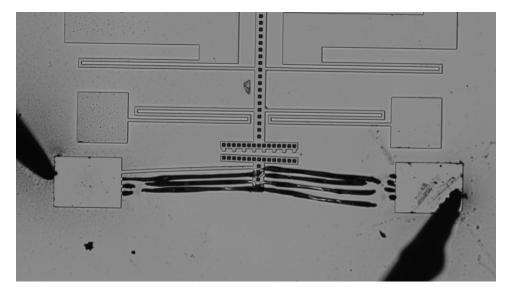

| 4.10 | Optical CCD micrograph of broken Chevron actuator at 13V potential                                                                                                                                                  | 58 |

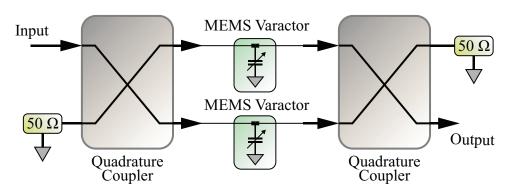

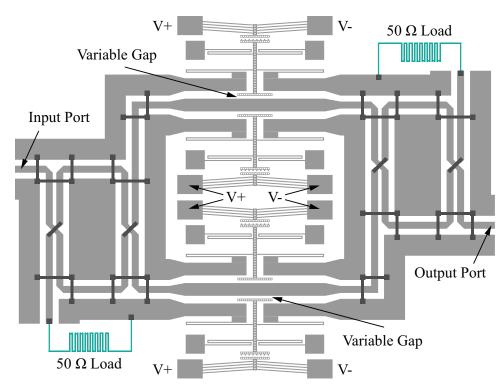

| 5.1  | Schematic of proposed variable attenuator consisting of two 3 dB hybrid couplers and RF MEMS varactors                                                                                                              | 61 |

| 5.2  | Layout of monolithically integrated RF MEMS-based variable attenuator displaying the variable gap between capacitive plates, input and output ports, and $50\Omega$ loads                                           | 62 |

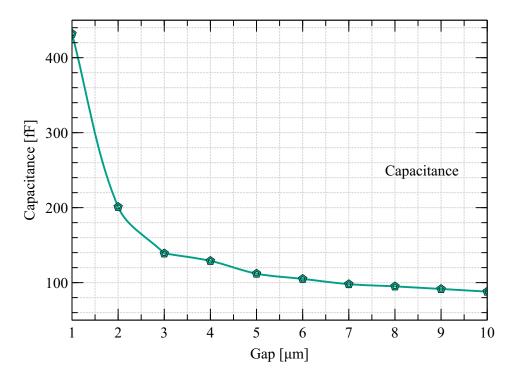

| 5.3  | EM simulation of capacitance with a linear change in variable gap between signal line and actuator plates                                                                                                           | 63 |

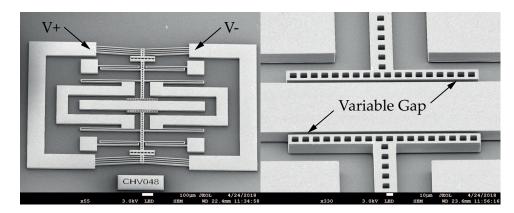

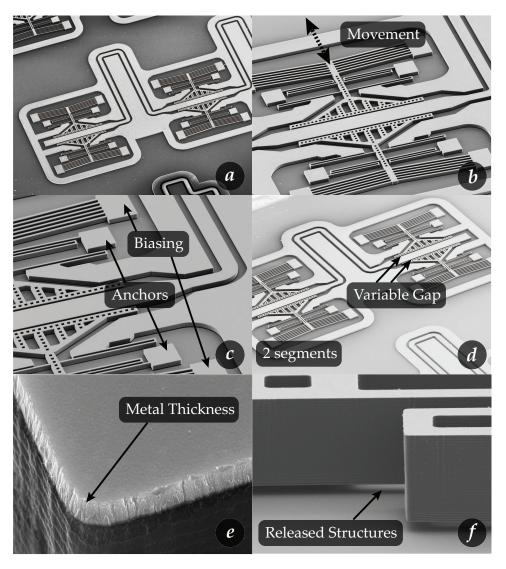

| 5.4  | SEM micrograph of fabricated RF MEMS varactors with the tunable capacitive gap controlled by Chevron actuators and zoomed in view of movable plates on both sides of the signal line                                                                      | 64 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

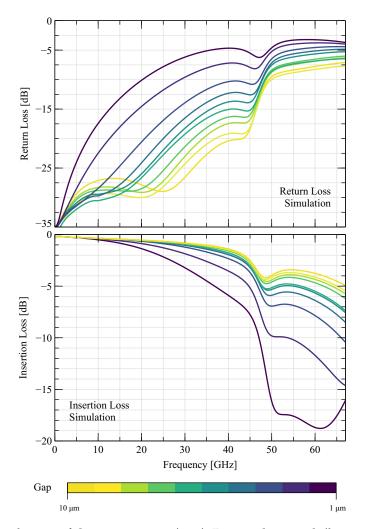

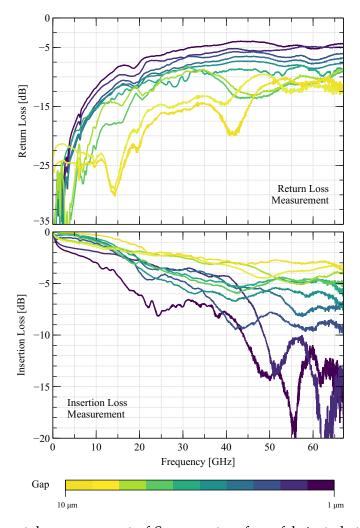

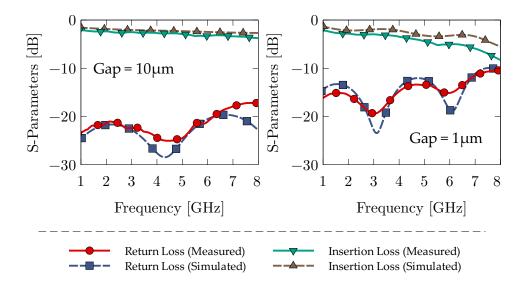

| 5.5  | EM simulation of S-parameters: (top) Return loss and (bottom) Insertion loss of MEMS varactor from DC to 67 GHz with variation in gap from $10\mu m$ to $1\mu m.$                                                                                         | 65 |

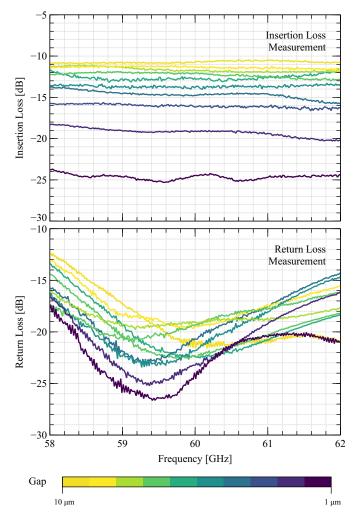

| 5.6  | Experimental measurement of S-parameters from fabricated structure: (top) measured return loss and (bottom) measured insertion loss of the MEMS varactor from DC to 67 GHz with varying gap                                                               | 66 |

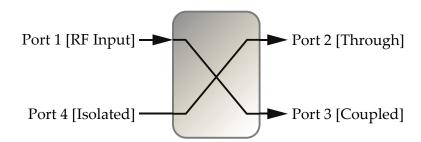

| 5.7  | Schematic representation of quadrature coupler, highlighting RF port numbers                                                                                                                                                                              | 67 |

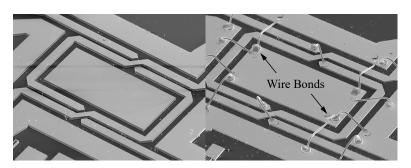

| 5.8  | CPW based quadrature hybrid coupler: (left) before wire bonding (right) after wire bonding the ground planes and the signal lines                                                                                                                         | 68 |

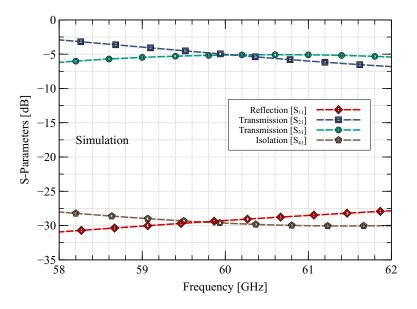

| 5.9  | Simulated S-parameters of hybrid coupler for the range $58\text{GHz}$ to $62\text{GHz}$ showing a $-5\text{dB}$ coupling at $60\text{GHz}$ between $S_{21}$ and $S_{31}$ , and the return loss at the input port $(S_{11})$ and isolation port $(S_{41})$ | 68 |

| 5.10 | Measurement results of the RF performance of fabricated hybrid coupler module displaying $-5.8\mathrm{dB}$ coupling at $60\mathrm{GHz}$ and the return loss at port 1 and port 4 for the $58\mathrm{GHz}$ to $62\mathrm{GHz}$ frequency range             | 69 |

| 5.11 | SEM micrograph of the fabricated structure: (left) sidewalls of the $20\mu m$ thick device layer structures obtained after Si-DRIE, (right) a zoomed in view of the edge displaying the top metal coverage and scallops in the sidewalls                  | 70 |

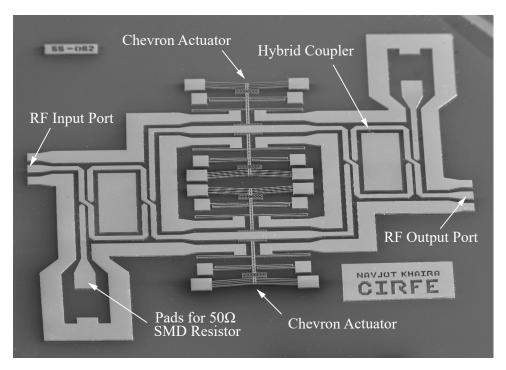

| 5.12 | SEM micrograph of the fabricated variable attenuator module showing the RF input and output ports, hybrid couplers, MEMS varactors controlled by Chevron actuators and the pads where $50\Omega$ resistors are surface mounted                            | 71 |

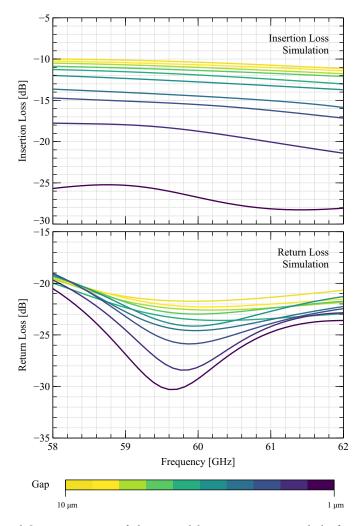

| 5.13 | Simulated S-parameters of the variable attenuator module from 58 GHz to 62 GHz: (top) insertion loss variation with the gap displayed in the colour scale (bottom) return loss for different gap sizes                                                    | 72 |

### List of Figures

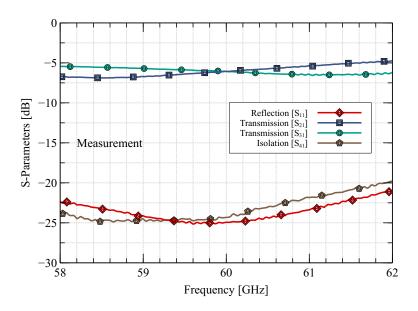

| 5.14 | Measured S-parameters of the variable attenuator module from 58 GHz to 62 GHz: (top) insertion loss variation with the applied bias (bottom) return loss for different gap sizes                                                                                                                              | 73 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

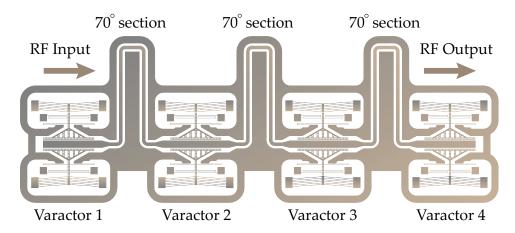

| 6.1  | Layout of MEMS based impedance tuner, highlighting three 40 degree sections and four varactors                                                                                                                                                                                                                | 76 |

| 6.2  | Schematic of impedance tuner using varactors and 40 degree sections                                                                                                                                                                                                                                           | 77 |

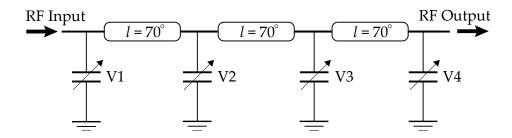

| 6.3  | SEM micrograph of MEMS impedance tuner. a) overhead image of impedance tuner, b) close-up view of varactor unit, c) bias pads and anchors for movable varactors, d) highlighting variable gap of varactors, e). metal coverage on silicon device layer structures and f) close-up view of released structures |    |

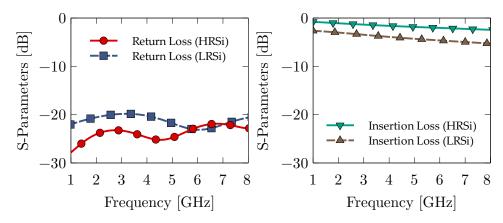

| 6.4  | Simulation and measurement of impedance tuner (left) when all four varactors have minimum capacitance of 0.17 pF with 10 $\mu$ m gap, and (right) when varactors have maximum capacitance of 0.8 pF with 1 $\mu$ m and 12 V DC applied                                                                        | 79 |

| 6.5  | Comparison of simulated S-parameters of device utilizing low resistivity silicon (LRSi) and high resistivity silicon (HRSi) device layer                                                                                                                                                                      | 80 |

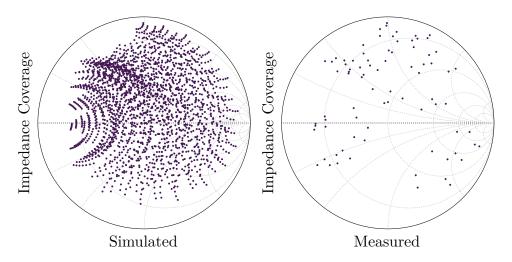

| 6.6  | Simulated and measured impedance coverage at 6 GHz                                                                                                                                                                                                                                                            | 80 |

## **List of Tables**

| 4.1 | Design specifications of MEMS Chevron actuator                       | 50 |

|-----|----------------------------------------------------------------------|----|

| 4.2 | Temperature, resistance and current measured across MEMS Chevron ac- |    |

|     | tuator                                                               | 59 |

## Glossary

- **3G** is the third generation of wireless mobile telecommunications technology. 3G networks support services that provide an information transfer rate of at least 0.2 Mbit/s. Later 3G releases, often denoted 3.5G and 3.75G, also provide mobile broadband access of several Mbit/s to smartphones and mobile modems in laptop computers.

- **4G-LTE** 4G is the fourth generation of broadband cellular network technology, succeeding 3G. 4G-LTE provides peak speed at 100 Mbit/s for high mobility communication and 1 Gbit/s for low mobility communication.

- 5G is the latest generation of cellular mobile communications. 5G performance targets high data rate, reduced latency, energy saving, cost reduction, higher system capacity, and massive device connectivity. As per the ITU specifications, 5G demands speeds of up to 20 Gbit/s, achievable with wide channel bandwidths and massive MIMO (multiple-input and multiple-output) capabilities.

- **cut-off frequency** a boundary in a system's frequency response at which energy flowing through the system begins to be reduced (attenuated or reflected) rather than passing through.

- **DC block** component that prevents the flow of DC signals in to system, while allowing the high frequency RF signals to pass through. It is placed within a system to stop any signal with a frequency of 0 Hz from interfering with sensitive Rf components.

- **latching-switch** a switch that maintains its state after being activated. A push-to-make, push-to-break switch would therefore be a latching switch each time you actuate it, whichever state the switch is left in will persist until the switch is actuated again.

- **micro-fabrication** the process of fabricating miniature structures of micrometre scales and smaller.

- **microstrip** a type of electrical transmission line which can be fabricated using printed circuit board technology, and is used to convey microwave-frequency signals.

- **millimeter-wave** the band of spectrum between 30 GHz and 300 GHz. Researchers are testing 5G wireless broadband technology on millimeter wave spectrum.

- **monolithic integrated circuit** a set of electronic circuits etched or deposited on one small flat piece of semiconductor material that is normally silicon.

- **p-i-n diode** a diode with a wide, undoped intrinsic semiconductor region between a p-type semiconductor and an n-type semiconductor region. The p-type and n-type regions are typically heavily doped because they are used for ohmic contacts.

- **parasitic capacitance** an unavoidable and usually unwanted capacitance that exists between the parts of an electronic component or circuit simply because of their proximity to each other.

- **RF front-end modules** RF front end is a generic term for all the circuitry between a receiver's antenna input up to and including the mixer stage. It consists of all the components in the receiver that process the signal at the original incoming RF, before it is converted to a lower intermediate frequency.

- **Single-Pole Single-Throw** a switch that only has a single input and can connect only to one output. This means it only has one input terminal and only one output terminal and serves in circuits as on-off switches. When the switch is closed, the circuit is on. When the switch is open, the circuit is off.

**Vanadium Oxide** an inorganic compound, has a phase transition very close to room temperature (68 °C). Electrical resistivity and opacity of this material can change up several orders. Due to these properties, it has been widely used in surface coating, sensors, and imaging.

**varactor** a device that acts as a voltage dependent capacitor.

variable attenuators a tunable electronic device that reduces the power of a signal without appreciably distorting its waveform. An attenuator is effectively the opposite of an amplifier, though the two work by different methods. While an amplifier provides gain, an attenuator provides loss, or gain less than 1.

### **Abbreviations**

Ar Argon

Au gold

BHF Buffered hydrofluoric acid

$C_4F_8$  octafluorocyclobutane

**CCD** charge coupled device

**CIRFE** Centre for Integrated RF Engineering

CMOS complementary metal-oxide-semiconductor

CPW co-planar waveguide

**Cr** chromium

**DRIE** deep reactive ion etching

FEM finite element modeling

**FET** field effect transistor

GaAs gallium arsenide

**GHz** gigahertz  $(1 \times 10^9 \text{ Hz})$

**HF** hydrofluoric acid

HfO<sub>2</sub> hafnium dioxide

**HFSS** High Frequency Structural Simulator

**HR** high resistivity

**LED** light emitting diode

LR low resistivity

**MEMS** microelectromechanical systems

MESFET metal semiconductor field effect transistor

MIM metal insulator metal

MMIC monolithic microwave integrated circuit

pHEMT pseudomorphic high electron mobility transistor

**QNC** Quantum Nano Centre

RF Radio frequency

**RF-MEMS** RF microelectromechanical systems

**RIE** reactive ion etching

**SEM** scanning electron microscope

**SF**<sub>6</sub> sulfur hexafluoride

**SiO**<sub>2</sub> silicon dioxide

**SMD** surface mount device

**SOI** silicon on insulator

### Abbreviations

$\textbf{THz} \ \, \text{terahertz} \, \, (1 \times 10^{12} \, \, \text{Hz})$

TR thermoreflectance

$VNA \ \ vector \ network \ analyzer$

$\mathbf{VO}_2$  vanadium oxide

## Chapter 1

### Introduction

### 1.1 Motivation

Canada's wireless communication industry, an area of strategic national interest, is enjoying phenomenal growth with a market that remains fueled by the increased demands for multi-media services. RF devices represent a critical and substantive portion of any communication systems. Whereas third generation (3G) networks brought the internet everywhere and 4G LTE made it faster, 5G will vastly boost both the network capacity and speed by shifting towards the millimeter-wave range (30-80 GHz). Wireless networks operating at millimeter-wave frequencies will be capable of providing incredible data bandwidth and reduced latency between the devices they connect. Thus, 5G will not only allow users to send and receive nearly unfathomable amounts of data but can be employed in other applications like future autonomous vehicles.

The performance of future wireless systems critically depends on hardware capability. For 5G roll-out, affordable radio frequency (RF) devices are necessary to be implemented in RF front-end modules responsible for transmitting and receiving radio signals. Variable attenuators are highly in demand in high frequency equipment for adjusting signal level. They find applications in Radio Frequency (RF) circuits like automatic gain control amplifiers, broadband vector modulators and radar systems.

Currently available standard implementations of power attenuators are either based

Ch. 1 – Introduction 1.1. Motivation

on discrete components mounted on Printed Circuit Board (PCB) or use silicon-based CMOS processes for their implementation. PIN diodes and FETs are commonly used as variable resistors in attenuator circuits. However, the performance of such attenuators is degraded considerably at millimeter-wave frequencies and they exhibit limited power handling (typically up to few watts). Commercially available high-power variable attenuators usually employ mechanically tuning coaxial- or waveguide-based slow and bulky structures. Thus, there is a clear need to develop miniaturized variable attenuator that can deliver cost-effective and superior RF performance for 5G systems. RF-MEMS technology is seen as a potential solution to develop such passive devices and networks that can meet the demanding requirements posed by the upcoming 5G standards. The superior performance of RF-MEMS micro-relays, varactors, resonators and other passive devices in terms of high isolation, low insertion loss, high Q-factor and power handling capability has been widely reported in literature. Exploitation of the mechanical deformability in MEMS has allowed for adding tunability/reconfigurability in RF passive circuits like impedance tuners and variable attenuators. MEMS based microactuators have the potential to precisely control the large out-of-plane or in-plane motion of the attached structures, which can be successfully exploited to achieve controlled and wide tuning range.

In the modern-day smartphones, antenna integration with numerous other components has led to degradation in the quality of voice and data transmission. Currently, the key component that is used to address this problem is the reconfigurable impedance tuner. It can compensate for the input/output impedance variations between the different parts of RF-front-end circuit such as power amplifiers, antennas and low-noise amplifiers, hence allowing multi-band functionality. As we move towards higher frequencies with the increasing day to day consumer demands, there is a need to develop impedance tuners with large tunability, reduced hardware redundancy and power consumption. RF MEMS technology can be used to develop compact reconfigurable impedance tuner with improved tuning range, power handling capability, low insertion loss for high-power applications at microwave frequencies.

Most of the currently available high-aspect ratio lateral MEMS devices like RF single-pole single-throw switches, single-pole multiple-throw switches, varactors, phase shifters are fabricated using MetalMUMPs process, which is a thick nickel micromachining pro-

Ch. 1 – Introduction 1.2. Objectives

cess. There is a need to develop low-cost and simpler fabrication process for such high-aspect ratio structures. Over the past decades, there has been a significant advancement in microfabrication techniques like Si-Deep Reactive Ion Etching (DRIE), which needs to be explored for developing low-cost millimeter wave devices. The monolithic integration of all components on a single chip is an added advantage. Hence, the microdevices developed will serve as building blocks to further expand the structures for a wider range or integration with other modules to provide additional functionality.

### 1.2 Objectives

The purpose of this thesis is to investigate the feasibility of utilizing MEMS technology to implement innovative variable attenuator for millimeter-wave applications. A low-cost in-house fabrication process is adopted for fabricating the proposed design. The stages of this research include:

## Development of a low-cost in-house fabrication process for high-aspect ratio lateral MEMS

A custom fabrication process for high-aspect ratio structures on SOI wafers is developed. It is particularly tuned to develop RF devices based on lateral MEMS. It is a low-cost process that involves single lithography step to co-fabricate the entire microsystem on chip. The sharp vertical structures are achieved using Si-DRIE. It is a high yield process and provides more reliable structures than surface micromachining processes.

#### Implementation of RF MEMS based variable attenuator

A millimeter-wave RF MEMS based variable attenuator is implemented by monolithically integrating CPW based hybrid couplers with lateral MEMS varactors on a SOI substrate. The varactor consists of a movable plate attached to the Chevron actuator. The variation of the gap between the movable plate and the signal line

Ch. 1 – Introduction 1.3. Thesis Outline

with the applied voltage leads to a change in attenuation at the output. It is fabricated using the SOI MEMS fabrication process developed at University of Waterloo, hence it does not suffer from the dielectric charging, micro welding and stiction problems associated with RF MEMS devices realized using surface micromachining processes.

#### Detailed experimental thermal analysis of Chevron actuators

Thermoreflectance (TR) imaging is known for providing high-resolution and accurate thermal images of various (opto) electronic devices at the micro-scale. Thermal imaging microscopy was used for thermal characterisation of chevron actuator. It provided insights into temperature distribution, displacement and failure analysis of chevron actuator fabricated on SOI wafer, which can help in designing the microactuator with high-thermal uniformity and low power consumption.

#### Development, modeling and fabrication of novel RF MEMS impedance tuner

A novel RF-MEMS based impedance tuner is developed with a wide tuning range, good coverage on the Smith chart, compact size and high power handling capability. The tunability was achieved by using monolithically integrated contactless lateral MEMS varactors located strategically along a CPW line. These varactors are realized using laterally moving capacitive thick plates with their motion precisely controlled using Chevron actuators. This device is fabricated in-house using SOI MEMS process. It provides a reliable operation and is useful in high power applications, since it is constructed from lateral thick structures.

### 1.3 Thesis Outline

Following the motivation and objectives given in Chapter 1, Chapter 2 presents an overview of the different technologies available to realize variable attenuators with a focus on those operating at millimeter-wave frequencies. In Chapter 3, different types of MEMS actuators are investigated, particularly lateral electrothermal actuators. Additionally, the

Ch. 1 – Introduction 1.3. Thesis Outline

fabrication process steps are discussed in detail. Chapter 4 investigates the use of thermoreflectance (TR) imaging to study temperature profiles of Chevron actuator. Chapter 5 presents the design and realization of monolithically integrated RF-MEMS based variable attenuator. RF MEMS-based impedance tuner is introduced in Chapter 6. Finally, a brief summary of the contributions of the thesis with an outline of the proposed future research are given in Chapter 7.

## Chapter 2

### Literature Review

Variable attenuators are highly in demand in high frequency equipment for adjusting signal level. They find applications in RF circuits like automatic gain control amplifiers, broadband vector modulators and radar systems. Variable attenuators have been implemented using various technologies; ranging from PIN diodes, FETs, and other CMOS based technologies to advanced materials like Graphene and VO<sub>2</sub> based variable attenuators. Their basic operating principles and performance are discussed in the following sections. RF MEMS-based variable attenuators are recently explored and are described in detail. The important design parameters of attenuator performance are attenuation range, bandwidth, return loss, power handling, flatness of attenuation, and circuit size/cost. Moreover, the linearity is also of utmost importance since the attenuator should not introduce non-linear distortion in the signal path.

### 2.1 Variable Attenuators Using Solid-State Devices

Semiconductor elements like PIN diodes or FETs are popularly used as the control element in variable attenuator circuits because of their speed and ease of design [1–4]. Such variable attenuators utilize the property of the semiconductor element that behaves like resistor at high frequencies. In the simplest form, variable attenuators can be implemented using a series connected or shunt connected p-i-n diode with a transmission line.

The major drawback of such approach is that the circuit's input and output impedance will vary with attenuation. To achieve a constant input and output impedance with the variation in attenuation, several types of variable attenuators circuits using PIN diodes and FETs have been presented:  $\pi$  attenuators, resistive line attenuators, bridged-T attenuators and hybrid coupled attenuators. The single hybrid coupled attenuator is used when reflected power must be minimized. However, double hybrid coupled attenuators are preferred in many applications due to its wider bandwidth, although it requires larger area than a single hybrid coupled attenuator [5, 6].

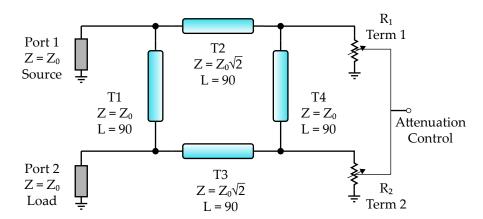

#### 2.1.1 Single/Double Hybrid Coupler and Varactors

A single 3 dB quadrature coupler can be used to implement a variable attenuator by terminating its coupled ports with equal and variable terminations and the isolated port is used as output port as displayed in Fig. 2.1. The idea behind this circuit is that the isolated port of hybrid coupler presents infinite attenuation to the input signal when the coupled ports are terminated with reflection coefficients equal to zero [7]. Zero attenuation to the input signal is achieved when the coupled ports are equally terminated and entirely reflective (with reflection coefficient equal to one). This implies that when the termination resistance at the coupled ports is equal to the reference impedance of the coupler (e.g.  $50\,\Omega$ ), the insertion loss should theoretically, approach infinity. Between

Figure 2.1: Schematic of a variable attenuator using 3-dB hybrid coupler

Figure 2.2: Reflection type variable attenuator with single hybrid coupler and two varactors.

these two extremes, the input port to the isolated port transmission is proportional to the magnitude of the reflection coefficient of the coupled ports.

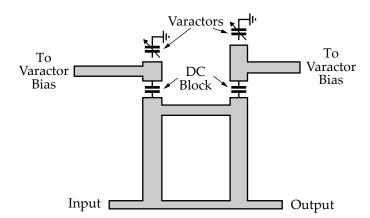

One of the implementations of the above-mentioned idea can be seen in reflection type variable attenuators using a single hybrid coupler with two varactors [8]. As shown in Fig. 2.2, the completed circuit is a low-cost structure comprised of a microstrip quadrature coupler combined with integrated varactors to vary the attenuation from 2.2 dB to 17 dB over a 40% bandwidth for frequencies from 2.8 GHz to 4.2 GHz.

In reflection type variable attenuator, the signal present at the input of hybrid coupler is evenly split between the ports connected to the varactors, with a  $90^{\circ}$  phase difference between them. The signal entering each varactor is fully reflected into the coupler since

**Figure 2.3:** Variable attenuator using single hybrid coupler.

**Figure 2.4:** Variable attenuator using two hybrid couplers.

the varactors present a purely reactive load. The phase difference between the signals that are reflected from each varactor determines the amount of power present at the attenuator output and power reflected to the input. Chip capacitors are used as dc blocks in the circuit. Attenuation occurs because of destructive interference from input signal components that are reflected off each varactor. This implementation of attenuator can be improved by using thin film MIM capacitors instead of chip capacitors to get rid of the parasitics associated with them and replacing the varactor diodes with MEMS-type capacitor banks.

Another MESFET-based attenuator [10] is designed on the same principle with 3 dB quadrature directional coupler and two identical cold MESFETs, which act as voltage-

(b) Double hybrid coupler approach

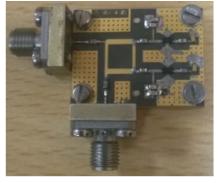

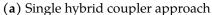

**Figure 2.5:** Variable attenuator fabricated on a PCB using single and double hybrid coupler approach [9].

controlled variable resistance reflection terminations. When zero gate bias voltage is applied, the drain-source channel resistance behaves as a short circuit and the insertion loss is at its minimum level. As the negative gate-bias potential is increased, the channel resistance increases, which results in a decrease in insertion loss.

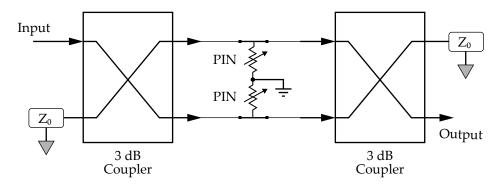

The major advantage of using single hybrid coupler variable attenuator as shown in Fig. 2.3 is the simplified circuitry and good return loss performance. On the other hand, ripples can be seen in the high attenuation states due to directivity of the hybrid coupler. To eliminate this effect, another technique involves using two hybrid couplers as shown in Fig. 2.4 [9].

Fig. 2.5 shows the design implementation of variable attenuators using single vs double hybrid couplers and PIN diodes as the controllable resistances. A comparison of their performance is presented in [9]. The range of the diode resistance defines the dynamic range of the attenuator.

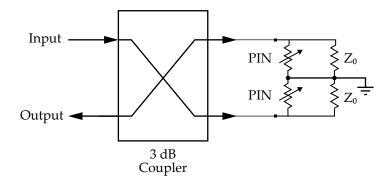

### 2.1.2 PIN Diodes and 0 dB Coupler

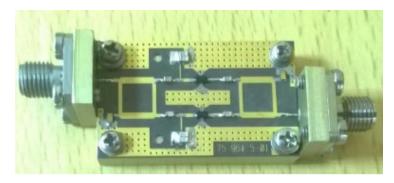

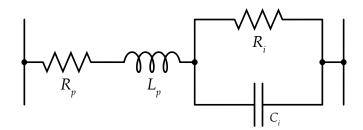

Due to the presence of intrinsic layer between its P-type and N-type layers, a PIN diode behaves as an ordinary PN junction diode at low frequencies and as a resistor at high frequencies whose value can be controlled by current. The high frequency equivalent circuit of PIN diode is shown in Fig. 2.6. At high frequencies, the PIN diode can be considered as a pure resistor.

A variable attenuator has been formed as shown in the schematic diagram in Fig. 2.7 by combining the PIN diode with a  $0\,\mathrm{dB}$  branch line coupler [11]. It utilizes this resistive

**Figure 2.6:** High frequency equivalent circuit of PIN diode.

Figure 2.7: Schematic diagram of variable attenuator showing the PIN diodes and 0-dB coupler.

characteristic of PIN diodes. The 0 dB coupler is formed by  $50\,\Omega$  quarter wavelength microstrip lines. The nodes A, B, and C can be floating or grounded depending on the resistance offered by the PIN diodes, which can be ideally varied from infinity to zero. When the PIN diodes have infinite resistance, the variable attenuator circuit acts as a 0-dB coupler alone, and the power incident at port 1 is transferred without any attenuation or reflection to port 3. Hence the current across the PIN diode acts as the controlling element for the output signal attenuation level. The PIN diodes are mounted through via holes on a thin board with the microstrip and the attenuation monotonically varies from 0.7 dB to 23 dB with the control voltage at the center frequency of 1.9 GHz.

However, the performance of such variable attenuators suffers from non-linearity issues precluding their use in applications where the signal level needs to be controlled without introducing intermodulation components. Moreover, the performance of semi-conductor based attenuators is considerably degraded when operating at millimeter-wave frequencies. Variable attenuators that use diodes as variable resistors require do blocks and bias circuits for operation. At the millimeter wave frequencies, this bias circuit becomes larger than the coupler itself, making it inefficient at higher frequencies.

**Figure 2.8:** Variable attenuator  $\pi$ -configuration showing a transmission line and two shunt NMOS transistors.

#### 2.1.3 Millimeter Wave CMOS-Based Variable Attenuator

Most of the analog type voltage-controlled attenuators use PIN diodes but these have some inherent drawbacks, such as high dc power consumption, narrow bandwidth, and integration limitations.

Conventional attenuator topologies can be categorized into T-,  $\pi$ - [12, 13], or Bridged-T [14–16] networks based on the arrangement of series and shunt branches. These consist of tunable components distributed in series and shunt between the input and output. The series components consist of the signal path and thus control the flow of passing signals, and the shunt tunable components connect the signal path to ground, thus divert the required amount of signal.

Fig. 2.8 shows the  $\pi$ -network used in designing variable attenuators comprising of a series transmission line and two shunt NMOS transistors connected from the signal path to ground. A continuous variable attenuator with wide bandwidth has been developed using 65 nm CMOS process [12]. The variable attenuator is designed using  $\pi$ -configuration with a series transmission line and three shunt FETs on one side of the transmission line. The amount of attenuation is determined by the impedance of the transistors, consisting of channel resistance and parasitic capacitance. Using three transistors in parallel with independent gate bias helps in achieving variable impedance, which expands the attenuation range. Hence, as the voltage bias is varied from 0 V to

**Figure 2.9:** RF circuit schematic of the DC-50 GHz MMIC attenuator.

1.2 V, an attenuation range of more than 16 dB is achieved from DC-110 GHz.

The conventional GaAs MESFETs used as voltage-controlled variable resistors in the variable attenuator T- or  $\pi$ - topology suffer from performance degradation at high frequencies, basically limiting their operation beyond 20 GHz. This parasitic capacitance problem has been overcome by using a MMIC FETs based improved circuit techniques [17]. As shown in Fig. 2.9, this attenuator although being a T-type topology, distributed a shunt FET into four cells interconnected by a length of high impedance transmission lines. This attenuator demonstrated a 30 dB dynamic range of attenuation over a DC–50 GHz frequency band with a minimum insertion loss of 1.8 dB at 26.5 GHz and 2.6 dB at 40 GHz.

Another  $\pi$ -configuration can be seen in [13], where an adaptive bootstrapped body biasing technique is used to effectively reduce variations in transistor impedance resulting from large input signals. This improves the linearity of the attenuator significantly.

A compact DC–40 GHz variable attenuator MMIC has been developed by B. Lefebvre, et al., utilizing a standard T-configuration [18]. This configuration requires two control voltages for the series- and shunt transistors. The use of triple-gate transistors provides the advantage of achieving higher saturation levels in comparison to single gate transistors with minimal layout changes. Apart from FETs, Gallium Arsenide (GaAs) pseudomorphic high-electron mobility transistors (pHEMTs) were also utilized in fully integrated systems, but they face challenges in power handling capability and high-

Figure 2.10: GDTs with wire leads, no wire lead and surface mount packages. [21].

frequency performance [19].

Nevertheless, high-frequency performance is degraded due to resonance and parasitic effects. Recently, D. P. Nguyen, et al., reported a stacked-FET based voltage-controlled attenuator [20]. This topology not only enhances power handling capability, but also allows for wideband performance from 1.5 GHz to 45 GHz, low insertion loss (minimum insertion loss 1.9 dB) and large dynamic range of 26 dB. Moreover, the output power has excellent flatness over the entire frequency band.

### 2.2 Gas Discharge Tube-Based Variable Attenuator

Gas Discharge Tube (GDT)-based approach is particularly useful in emerging applications that involve high temperature and/or pressure and require high power and fast response times, where conventional techniques cannot be used [22]. A travelling electromagnetic (EM) wave exhibits reflection, attenuation and transmission coefficients when incident on a plasma region. These coefficients depend on the values of plasma oscillation and electromagnetic wave frequencies, i.e.  $\omega_p$  and  $\omega$ , respectively. Plasma frequency is decided by the electron number density ( $n_e$ ) in the discharge area. High  $\omega_p/\omega$  ratio leads to high reflection. Since plasma can be turned on and off within a few nanoseconds, a very fast plasma-based RF switches and attenuators can be built on this principle. This work demonstrates the capability of low temperature plasma to be used as a tunable element in variable RF attenuator structures. As shown in Fig. 2.10, GDTs are available in no wire lead, wire lead and surface mount forms with two or three elec-

**Figure 2.11:** Fabricated GDT-based variable RF attenuator showing GDTs connected in series-shunt topology [22].

trodes in an enclosure filled with a non-radioactive rare gas e.g. argon, helium or neon.

Two independently controlled surface mount GDTs in a series-shunt configuration as shown in Fig. 2.11 result in a variable attenuator with maximum attenuation of 20 dB with 2 dB flatness over the 0.5 GHz to 1.2 GHz frequency range.

#### 2.3 Graphene-Based Variable Attenuator

Other types of variable attenuators at microwave and millimeter wave frequencies are based on graphene based resistive elements [23, 24] have also been recently explored. They utilize the property that the graphene film can range from being a discrete conductor to a highly resistive material, depending on the externally applied voltage. A micrometric layer of graphene flakes is implemented in electronically tunable microstrip attenuator. As shown in the measurement setup in Fig. 2.12, the attenuator consists of a microstrip line with a gap that is filled with graphene nanoplatelets with the dimension in the order of  $5\,\mu m$  to  $10\,\mu m$ .

The measurements are performed with different values of dc voltage  $V_{\rm dc}$  applied to the bias tees. Current  $I_{\rm dc}$  increases with increasing  $V_{\rm dc}$ , with suggests decreasing

resistance with applied voltage as shown in Fig. refgraphene-2.

The resistance of graphene changes with applied voltage, and the attenuator exhibits tunability of the insertion loss over the entire frequency range from 1 GHz to 20 GHz. A larger tuning range of 5.5 dB is obtained at lower frequency of 1 GHz and a smaller

Figure 2.12: Measurement setup of the graphene-based microstrip attenuator [23].

**Figure 2.13:** Measured dc current vs dc resistance of the graphene-based microstrip variable attenuator [23].

tuning range of 2.5 dB at 20 GHz.

## 2.4 Metal-Insulator Transition Material (VO<sub>2</sub>) Based Variable Attenuator

Another alternative to PIN diodes has been provided by J. Jiang et al [25]. They have replaced PIN diodes with vanadium dioxide ( $VO_2$ )-based resistive film while using the 0-dB coupler as shown in Fig. 2.14 and 2.15.

Vanadium dioxide is a metal-insulator transition material that has the ability to switch between a metal state and an insulator state with the externally provided heat to the film. It undergoes a change in sheet resistance from  $48\,\Omega/\Box$  to  $47\,k\Omega/\Box$  when voltage is applied to the microheater.

This not only provides excellent performance at millimeter-wave frequencies but also provides monolithic integration of thin-film  $VO_2$  with the 0-dB coupler and the bias heater circuit on a single chip.

The measurement results show that the device provides a continuous attenuation tuning range of 13 dB, and a return loss of 15 dB over the bandwidth of 5 GHz at 30 GHz as shown in Fig. 2.16.

**Figure 2.14:** Schematic of the variable attenuator using VO2 variable resistor and 0-dB hybrid coupler.

**Figure 2.15:** Optical micrograph of the fabricated variable attenuator showing micro-heater elements [25].

**Figure 2.16:** Measured RF performance of VO<sub>2</sub> based variable attenuator [25].

## 2.5 RF-MEMS Based Millimeter-Wave Variable Attenuators

The upcoming field of 5G demands RF devices that operate at high frequencies especially in millimeter wave range. RF-MEMS technology is capable of providing RF devices like impedance tuners and variable attenuators with boosted characteristics in terms of losses and flatness of attenuation. The flexibility to merge more signal conditioning functions on the same RF-MEMS device makes them even more appealing to 5G applications. For

**Figure 2.17:** (Top image) The micrograph of the fabricated variable attenuator showing CPW lines and DC bias pads, (Bottom image) Close-up of the fabricated device showing electrostatically-controlled gold membranes, poly-Si resistive load, and shorting fingers [26].

example, merging the attenuation and phase shifting.

The first published attempt using this technology was by J. Iannacci et.al., who developed RF-MEMS based basic 2-state attenuator module [26, 27]. The device is fabricated using surface micromachining and consists of a series poly-Si Boron doped buried resistive load inserted on the RF line, which can be shorted by electrostatically actuating the suspended thin gold membranes above the resistor as shown in Fig. 2.17.

However, it has only two levels of attenuation. When the load is inserted, and gold membranes are in suspended rest position (no DC bias applied), a flat attenuation level  $(S_{21})$  is observed over the whole range. When the gold membranes are pulled down by electrostatic actuation (DC bias greater than the pull-in voltage), the load is shorted as the RF signal finds a low-impedance path through the gold membrane and the module exhibits an insertion loss  $(S_{21})$  better than 1.4 dB up to 50 GHz.

Another design variation has been proposed by J. Iannacci et. al. with the resistive load connected in series or shunt configuration on the RF line and the attenuation is ON/OFF switched by electrostatically driven MEMS micro-relays [27]. Hence, it oper-

**Figure 2.18:** (a) Micrograph of the series design with an in-line poly-Si resistor; (b) Micrograph of the shunt design with two shunt-to-ground poly-Si resistors; (c) lumped-element model of series design; (d) lumped element model of the shunt attenuator [27].

ates on a similar principle as the one previously mentioned and provides a flat two step variable attenuation up to 110 GHz. As shown in the micrographs and lumped-element models in Fig. 2.18, in the series attenuator when the MEMS switch is actuated, it shorts the in-line resistive load. While in shunt configuration, when the MEMS switch is actuated, it inserts a shunt-to-ground resistive path.

X. Guo et. al. demonstrated a compact  $(2.45\,\mathrm{mm} \times 4.34\,\mathrm{mm} \times 0.5\,\mathrm{mm})$  3-bit microwave attenuator based on RF-MEMS single-pole double-throw (SPDT) switches and a resistive attenuation module [28]. As shown in Fig. 2.19, it is constructed by cascading three 1-bit attenuator units designed for 10-, 20- and 40 dB attenuation. The SPDT switches are used to toggle between each attenuation module path and a reference path to realize the target signal attenuation. The reference path is a fundamental CPW transmission line with a power consumption as low as possible. The attenuation path was

**Figure 2.19:** Overview of the 3-bit reconfigurable attenuator based on RF MEMS SPDT switches. [28]

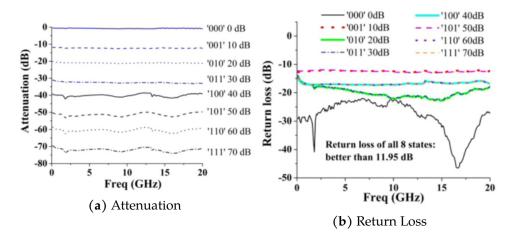

the function module and absorbed signal power depending on the resistive network. By routing the signal through the selected transmission path using SPDT switches, attenuation performance of  $10\,\mathrm{dB}$  to  $70\,\mathrm{dB}$  in the frequency range  $1\,\mathrm{GHz}$  to  $20\,\mathrm{GHz}$  with an accuracy better than  $\pm 1.88\,\mathrm{dB}$  at  $60\,\mathrm{dB}$  and error less than  $2.22\,\mathrm{dB}$  at  $10\,\mathrm{dB}$  is achieved as shown in Fig. 4.2.

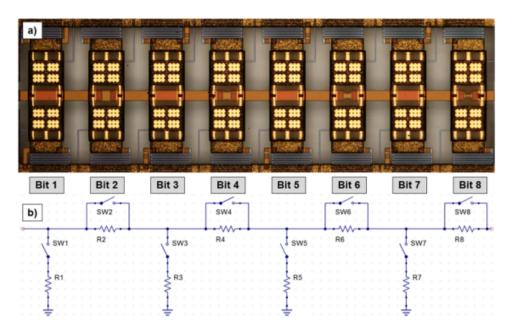

Recently, 8-bit reconfigurable power attenuator up to  $110\,\mathrm{GHz}$  has been developed using RF-MEMS technology available at CMM-FBK, in Italy [29]. The device (with a footprint of  $3\,\mathrm{mm} \times 1.95\,\mathrm{mm}$ ) is based on CPW configuration and comprises eight cascaded stages (8-bit), thus implementing 256 different network configurations. As shown in Fig. 2.21(a), each of these stages has electrostatically actuated MEMS ohmic switches, independently controllable by applying DC bias to the pads. Depending on whether the micro-relay is in the rest position (OFF) or pulled-in (ON), the switches select or deselect a series of low-resistivity (LR) poly-Si resistors as shown in the equivalent network

Figure 2.20: RF performance of each state of the fabricated 3-bit MEMS attenuator [28]

**Figure 2.21:** (a) Reconfigurable RF-MEMS attenuator showing the eight cascaded switching units; (b) Equivalent lumped element network of each stage of 8-bit attenuator, including the switches (SW1 to SW8) and the resistive loads (R1 to R8). [29]

in Fig. 2.21(b).

This device exhibits attenuation levels distributed in the range from 10 dB down to

$60 \, dB$ , in the whole analysed frequency range i.e., from  $10 \, MHz$  to  $110 \, GHz$ . The flatness ranges from  $3 \, dB$  to  $5 \, dB$  at the low frequencies to around  $15 \, dB$  over a  $50 \, GHz$  span, but above  $50 \, GHz$  the  $S_{21}$  traces show several ripples and markedly non-linear behavior.

Since all the above-mentioned approaches of MEMS based variable attenuators involve a CPW line and vertically moving thin membranes, they are still prone to the conventional MEMS reliability problems like stiction, micro-welding, and need high actuation voltages.

## Chapter 3

# Realization of High Aspect Ratio MEMS Actuators

#### 3.1 MEMS Actuators

Over the last two decades, different microelectromechanical systems (MEMS) actuators such as magnetic [30, 31], electrostatic [32–34], piezoelectric [35, 36] and electrothermal actuators [37, 38] have been well documented. However, the most popular ones are electrostatic and electrothermal because of the larger displacements and forces generated by them. Microactuators with different driving mechanisms can be classified and studied based on the following categories:

#### 3.1.1 Direction of Motion

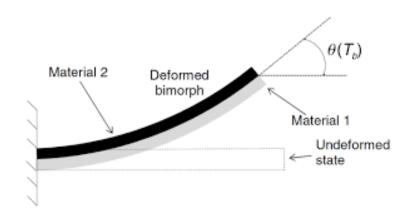

Electrothermal actuation is a widely used driving mechanism and MEMS electrothermal actuators can be categorized into in-plane and out-of-plane based on their direction of motion. Most of the multi-morph designs provide out-of-plane motion since they rely on bending of the layer due to thermal mismatch as shown in Fig. 3.1 [39]. For in-plane

**Figure 3.1:** Bi-morph thermal actuator design for out-of-plane [40].

motion, uniform structural material with different widths of sections is utilized as shown in Fig. 3.2 [37, 38].

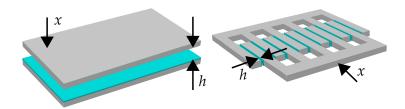

Since electrostatic actuators rely on the forces generated between two conducting electrodes when a voltage is applied, the most popular designs of electrostatic microactuators are parallel plate and comb drive structures. Parallel plate electrostatic actuators are usually used for out-of-plane motion [32, 33] and the comb-drive designs are popular for lateral (in-plane) motion (Fig. 3.3) [34].

Figure 3.2: Thermal actuator design for in-plane motion.

**Figure 3.3:** Electrostatic actuator configurations, (a) parallel plate actuator, (b) comb drive actuator. X denotes the direction of motion and h gives the capacitive gap between plates.

#### 3.1.2 Operating Voltage/Power

Electrostatic actuators consume essentially zero dc power, but they require high operating voltages (usually  $>30\,\mathrm{V}$ ), which makes them incompatible with microelectronic power supplies and integrated circuits. The reasons for this incompatibility are the dielectric oxide and junction breakdown at high voltages and the increased chip area required for larger depletion widths associated with elevated voltages. Moreover, such high electric fields on the surface of device increases the risk of arcing and make the device sensitive to ambient pressure and humidity, which is highly undesirable.

On the other hand, peak displacements of 1  $\mu$ m to 15  $\mu$ m can be achieved in the case of electrothermal actuators by using drive voltage of <15 V, enabling the use of electronic interfaces. The power consumed can be further reduced by implementing a locking mechanism as shown in Fig. 3.4 [41–43]. They provide the advantage of holding the mechanical position of the structure with no further electrical energy supplied unless a change in operation state is needed.

#### 3.1.3 Materials

The transduction mechanisms utilized in the actuators include the use of magnetic materials, shape memory alloys, piezoelectric materials, or encapsulated fluids, but the use of such materials is prevented due to process constraints and difficulty in integration

**Figure 3.4:** Locking mechanisms in thermal actuators [43].

with RF devices. Therefore, electrostatic or electrothermal transduction techniques are considered the best options for RF applications.

Undoubtedly, electrostatic actuators offer several advantages such as low temperature coefficient and zero dc power consumption, but they require high actuation voltages as discussed previously. Depending upon the choice of expansion materials, a wide range of displacements and forces can be achieved by using thermal expansion actuators. Electrothermal actuators can be designed with multi-morph or single-layer structures, where the latter design is more popular since they are more reliable and can provide rectilinear motion compared to the bending motion in the multi-morph designs. The most commonly used structural materials for electrothermal actuators are polysilicon, electroplated Ni, and silicon. Metal-based thermal actuators provide larger displacement at a much lower temperature than that of Si-based actuators [44, 45]. This is because the metals have higher thermal expansion coefficients than Si.

#### 3.2 Electrothermal Actuators

Significant displacements and large forces can be generated by electrothermal actuators, which make them attractive for many space and radio frequency (RF) systems, especially in the tunable capacitors. Electrothermal actuation is generally based on heating two ad-

jacent materials with different expansion coefficients and creating a bending moment. This bimorph deflection is usually out-of-plane and is not rectilinear [39]. Another option is laying the bimorph materials side-by-side to achieve in-plane displacement, but this generally complicates the fabrication process and does not generate significant rectilinear displacement [46].

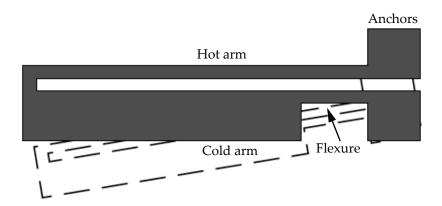

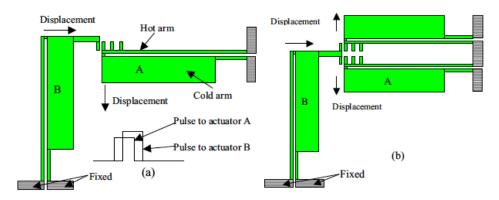

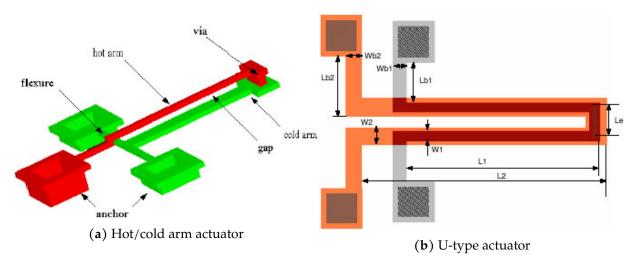

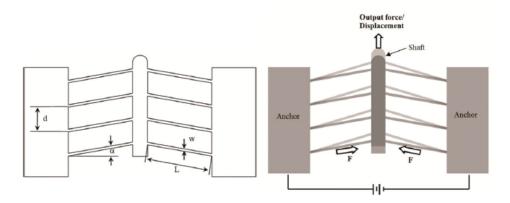

A popular technique to evade the use of dissimilar materials is the use of pseudo bimorph structures. This approach uses a single structural material with a uniform thermal expansion coefficient, but different parts experience different temperature changes because of the difference in width of arms of structure [37, 38]. The hot and cold arms structure can be used to achieve lateral or perpendicular motion to the substrate. In the thermal actuator shown in Fig. 3.5a, the hot arm is above the cold arm and is separated by an air gap [47]. The hot arm is thinner than the cold arm and are connected together with a via on one end. When the current is passes through the arms, the hot arm expands, and it drives the tip of the vertical actuator downward. However, the major limitation of this design is the power dissipated in the cold arm since it has no contribution towards the final motion of the actuator.

**Figure 3.5:** Two-arm electrothermal actuators [47] [48]

**Figure 3.6:** Three-arm electrothermal actuator

More electrically efficient designs are shown in Fig. 3.5b and in Fig. 3.6 where all electrical energy consumed contributes to the final deflection of actuator and no power is wasted in the cold arm. Electrothermal actuator shown in Fig. 3.5b uses two U-shaped beams in the top and bottom layer with a gap between them. The two beams are connected with a via at one end and are anchored separately on the substrate at the other end [48]. The actuator can bend upward or downward depending on which pair of anchors has been applied the voltage.

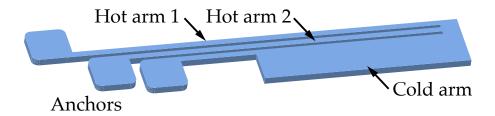

The two hot arm actuator design shown in Fig. 3.6 operates on the same principle as one hot arm actuator but in this case, the electrical current passes only through the outer and inner hot arms making it electrically more efficient than one-hot arm design.

The most popular structural materials for pseudo bimorphs are polysilicon and electroplated metals, however, the use of shape memory alloys has always been debated as they can provide significant linear displacement and forces, but it is challenging for process integration [49]. The thermal expansion coefficient of electroplated Ni is about four times that of Si. Although, this is highly desirable since it means larger displacement, but it also has some down sides. Since there is an expansion mismatch between the structural material Ni and the substrate material Si, the position of the apex may change with the ambient temperature. Moreover, there is a huge difference between the heat tolerance of these materials. While polysilicon structures can operate up to about 600 °C without any permanent deformation of the structures and Si structures can tolerate even higher temperatures [50], Ni structures have a maximum limit of 350 °C. Above this tempera-

ture, an irreversible darkening of the structures can be observed due to oxidation and it causes degradation of the actuation stroke.

To summarize, electrothermal actuators have the advantage of providing higher forces with low driving voltages, which allows the use of standard electronics interface, but they consume more power than electrostatic ones. The thermal time constant of these actuators is larger than the electrical and mechanical time constants of microstructures, making them slower than electrostatic actuators.

There are three important considerations in designing the thermal actuators:

- Thermal expansion of materials upon heating

- Mechanically amplifying the motion achieved by thermal expansion

- Deciding the direction of in-plane motion

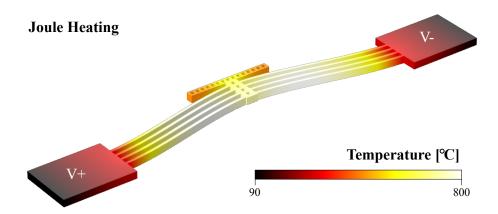

It is well known that most materials undergo an increase in size when heated and decrease in size with decreasing temperature. The basic relation between structural elongation and thermal expansion coefficient  $\alpha$  is given by:

$$\Delta L = \alpha L_0 \Delta T \tag{3.1}$$

where,  $L_0$  is the initial length of object,  $\Delta L$  is the change in the length,  $\alpha$  is the coefficient of linear expansion in  $K^{-1}$  and  $\Delta T$  is the change in temperature in K.

When voltage is applied to the electrical pads, current in the range of milliamps passes through the thin beams. This causes resistive heating and a temperature rise of several hundred degrees. The areas with maximum resistive heating undergo maximum expansion.

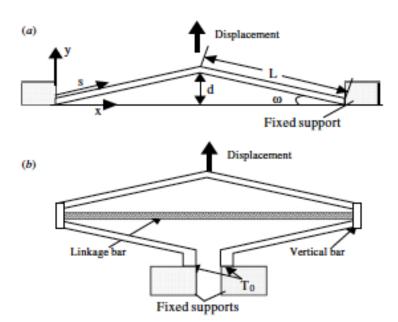

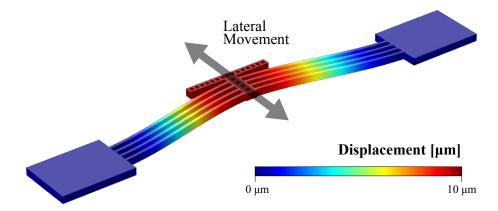

The amount of elongation possible from thermal expansion is limited by the linear thermal expansion coefficient and the melting point of the material. This thermal expansion achieved is small when compared to the overall dimensions of the device and is not sufficient for effective actuation. Hence for larger deflections, it is necessary to amplify this motion by using geometrically constrained design. One of the techniques is to use dissimilarly shaped beams in parallel also called as bi-morphs. Another option is to use two beams bent at a slight angle to each other called as Chevron or V-shaped actuators as shown in Fig. 3.7. This can mechanically amplify the slight motion achieved from thermal expansion [51].

Various deflection modes are possible in thermal microactuators based on the geometry. In this case, the thickness of the structures is defined by the device layer thickness of the SOI wafers which is selected to be 20  $\mu m$ . The width of all the thin beams is designed to be less than thickness to ensure that they deflect in-plane. To control the direction of in-plane motion, the thin beams are fabricated at a small angle with the central beam.

**Figure 3.7:** Geometrical constraints used to amplify the expansion motion (a) V-shaped beams (b) one-ring spring actuator with insulating beam as a constraint [51].

#### 3.3 Design of Chevron Actuator

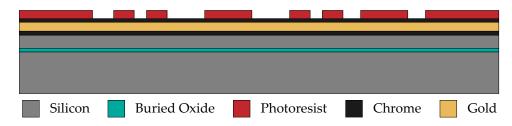

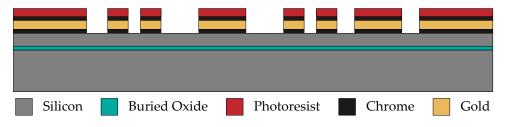

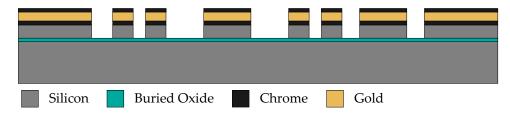

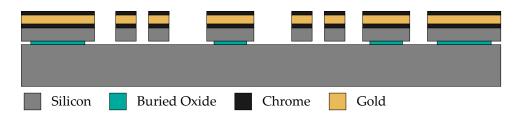

The traditional electro-thermal actuators are fabricated with different widths of hot and cold arms to provide high and low electrical resistance. Hence, when electrical current is applied to these arms, different magnitudes of thermal expansions are observed in hot and cold arms. This forces the tip of the device to bend.