## STT-MRAM Characterization and its Test Implications

by

Govindakrishnan Radhakrishnan

A thesis presented to the University of Waterloo in fulfillment of the thesis requirement for the degree of Doctor of Philosophy in Electrical & Computer Engineering

Waterloo, Ontario, Canada, 2020

© Govindakrishnan Radhakrishnan 2020

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### Abstract

Spin torque transfer (STT)-magnetoresistive random-access memory (MRAM) has come a long way in research to meet the speed and power consumption requirements for future memory applications. The state-of-the-art STT-MRAM bit-cells employ magnetic tunnel junction (MTJ) with perpendicular magnetic anisotropy (PMA). The process repeatability and yield stability for wafer fabrication are some of the critical issues encountered in STT-MRAM mass production. Some of the yield improvement techniques to combat the effect of process variations have been previously explored. However, little research has been done on defect oriented testing of STT-MRAM arrays. In this thesis, the author investigates the parameter deviation and non-idealities encountered during the development of a novel MTJ stack configuration. The characterization result provides motivation for the development of the design for testability (DFT) scheme that can help test and characterize STT-MRAM bit-cells and the CMOS peripheral circuitry efficiently.

The primary factors for wafer yield degradation are the device parameter variation and its non-uniformity across the wafer due to the fabrication process non-idealities. Therefore, effective in-process testing strategies for exploring and verifying the impact of the parameter variation on the wafer yield will be needed to achieve fabrication process optimization. While yield depends on the CMOS process variability, quality of the deposited MTJ film, and other process non-idealities, test platform can enable parametric optimization and verification using the CMOS-based DFT circuits. In this work, we develop a DFT algorithm and implement a DFT circuit for parametric testing and prequalification of the critical circuits in the CMOS wafer. The DFT circuit successfully replicates the electrical characteristics of MTJ devices and captures their spatial variation across the wafer with an error of less than 4%. We estimate the yield of the read sensing path by implementing the DFT circuit, which can replicate the resistance-area product variation up to 50%from its nominal value. The yield data from the read sensing path at different wafer locations are analyzed, and a usable wafer radius has been estimated. Our DFT scheme can provide quantitative feedback based on in-die measurement, enabling fabrication process optimization through iterative estimation and verification of the calibrated parameters.

Another concern that prevents mass production of STT-MRAM arrays is the defect formation in MTJ devices due to aging. Identifying manufacturing defects in the magnetic tunnel junction (MTJ) device is crucial for the yield and reliability of spin-torque-transfer (STT) magnetic random-access memory (MRAM) arrays. Several of the MTJ defects result in parametric deviations of the device that deteriorate over time. We extend our work on the DFT scheme by monitoring the electrical parameter deviations occurring due to the defect formation over time. A programmable DFT scheme was implemented for a sub-array in 65 nm CMOS technology to evaluate the feasibility of the test scheme. The scheme utilizes the read sense path to compare the bit-cell electrical parameters against known DFT cells characteristics. Built-in-self-test (BIST) methodology is utilized to trigger the onset of the fault once the device parameter crosses a threshold value. We demonstrate the operation and evaluate the accuracy of detection with the proposed scheme. The DFT scheme can be exploited for monitoring aging defects, modeling their behavior and optimization of the fabrication process.

DFT scheme could potentially find numerous applications for parametric characterization and fault monitoring of STT-MRAM bit-cell arrays during mass production. Some of the applications include a) Fabrication process feedback to improve wafer turnaround time, b) STT-MRAM bit-cell health monitoring, c) Decoupled characterization of the CMOS peripheral circuitry such as read-sensing path and sense amplifier characterization within the STT-MRAM array. Additionally, the DFT scheme has potential applications for detection of fault formation that could be utilized for deploying redundancy schemes, providing a graceful degradation in MTJ-based bit-cell array due to aging of the device, and also providing feedback to improve the fabrication process and yield learning.

#### Acknowledgement

I would like to express my sincere gratitude and thanks to my supervisor Professor Manoj Sachdev, University of Waterloo, for believing in my thesis while I was lost. Without his guidance and patience, the work would not have been possible. I would also like to thank my co-supervisor, prof Youngki Yoon who has taught me how to research in this field. I would also like to thank my examination committee members, Dr. Guoxing Miao, Dr. David Nairn, Dr. Mustafa Yavuz, and Dr. Nicola Nicolici. I understand the effort put by all of you to be part of my Ph.D. examination committee and I am thankful for it.

I would also like to thank my colleagues for helping me and being part of many interesting conversations. It was great to have worked with you. My sincere thanks go to Adam, Sakib, Assem, Dhruv, Anthony, Kai, Qing, Sunil, Mahdi, Morteza, Hugo, Yugal, Ata, and Matthew.

Lastly, I would like to thank the memory devices group in Imec, Belgium for allowing me to work with real MTJ devices, CMC Microsystems for fabricating the test chips, and the University of Waterloo for funding and supporting my research.

## **Table of Contents**

| Li | List of Tables x |                                              |      |  |  |  |

|----|------------------|----------------------------------------------|------|--|--|--|

| Li | st of            | Figures                                      | xi   |  |  |  |

| Li | st of            | abbreviations                                | xvii |  |  |  |

| 1  | Intr             | oduction                                     | 1    |  |  |  |

|    | 1.1              | Motivation                                   | 1    |  |  |  |

|    | 1.2              | Evolution of MRAM and Future                 | 3    |  |  |  |

|    | 1.3              | MTJ Device Physics                           | 4    |  |  |  |

|    | 1.4              | MTJ Fabrication and Implementation           | 8    |  |  |  |

|    | 1.5              | Test and Characterization of STT-MRAMs       | 12   |  |  |  |

|    | 1.6              | Challenges in State-of-the-art STT-MRAM      | 13   |  |  |  |

|    | 1.7              | Research Goal                                | 14   |  |  |  |

|    | 1.8              | Outline                                      | 14   |  |  |  |

| 2  | STI              | <b>F-MRAM Design Considerations</b>          | 15   |  |  |  |

|    | 2.1              | Bit-Cell Operation                           | 15   |  |  |  |

|    | 2.2              | Write Operation                              | 18   |  |  |  |

|    | 2.3              | Read Operation                               | 18   |  |  |  |

|    |                  | 2.3.1 Reference Signal Generation Techniques | 20   |  |  |  |

|   |                                                                             | 2.3.2                                                                                | Sensing Topologies                                                                                                                                    | 2                                           |

|---|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

|   | 2.4                                                                         | MTJ I                                                                                | Physics & Modelling                                                                                                                                   | 7                                           |

|   |                                                                             | 2.4.1                                                                                | Compact Modelling                                                                                                                                     | 8                                           |

|   |                                                                             | 2.4.2                                                                                | Nanoscale Device Modelling based on NEGF                                                                                                              | 9                                           |

|   |                                                                             | 2.4.3                                                                                | Micro-magnetic Modelling                                                                                                                              | 0                                           |

|   |                                                                             | 2.4.4                                                                                | Model Used for Bit-cell Analysis                                                                                                                      | 1                                           |

|   | 2.5                                                                         | Prelim                                                                               | inary Comparative Analysis of 1T-1MTJ STT-RAM Cells 3                                                                                                 | 3                                           |

|   |                                                                             | 2.5.1                                                                                | Simulation Methodology                                                                                                                                | 3                                           |

|   | 2.6                                                                         | Result                                                                               | s3                                                                                                                                                    | 5                                           |

|   |                                                                             | 2.6.1                                                                                | Read Performance                                                                                                                                      | 6                                           |

|   |                                                                             | 2.6.2                                                                                | Write Performance                                                                                                                                     | 9                                           |

|   | 2.7                                                                         | Summ                                                                                 | ary                                                                                                                                                   | 1                                           |

|   |                                                                             |                                                                                      |                                                                                                                                                       |                                             |

| 3 | MT                                                                          | J Dev                                                                                | ce Characterization 4                                                                                                                                 | 2                                           |

| 3 | <b>MT</b><br>3.1                                                            |                                                                                      | ace Characterization       4         uction       4                                                                                                   |                                             |

| 3 |                                                                             | Introd                                                                               |                                                                                                                                                       | 2                                           |

| 3 | 3.1                                                                         | Introd                                                                               | uction $\ldots \ldots 4$                                          | $\frac{2}{3}$                               |

| 3 | 3.1                                                                         | Introd<br>Film-I                                                                     | uction4Level Characterization4                                                                                                                        | 2<br>3<br>3                                 |

| 3 | 3.1                                                                         | Introd<br>Film-I<br>3.2.1                                                            | uction4Level Characterization4RA Product and TMR Evaluation4                                                                                          | 2<br>3<br>3<br>3                            |

| 3 | 3.1                                                                         | Introd<br>Film-I<br>3.2.1<br>3.2.2<br>3.2.3                                          | uction4Level Characterization4RA Product and TMR Evaluation4Damping Factor4                                                                           | 2<br>3<br>3<br>3<br>4                       |

| 3 | 3.1<br>3.2                                                                  | Introd<br>Film-I<br>3.2.1<br>3.2.2<br>3.2.3<br>Device                                | uction4Level Characterization4RA Product and TMR Evaluation4Damping Factor4Perpendicular Magnetic Anisotropy (PMA)4                                   | $2 \\ 3 \\ 3 \\ 3 \\ 4 \\ 4$                |

| 3 | <ul><li>3.1</li><li>3.2</li><li>3.3</li></ul>                               | Introd<br>Film-I<br>3.2.1<br>3.2.2<br>3.2.3<br>Device<br>Object                      | uction4Level Characterization4RA Product and TMR Evaluation4Damping Factor4Perpendicular Magnetic Anisotropy (PMA)4e-Level Characterization4          | 2<br>3<br>3<br>4<br>4<br>8                  |

| 3 | <ul><li>3.1</li><li>3.2</li><li>3.3</li><li>3.4</li></ul>                   | Introd<br>Film-I<br>3.2.1<br>3.2.2<br>3.2.3<br>Device<br>Object<br>Test S            | uction4Level Characterization4RA Product and TMR Evaluation4Damping Factor4Perpendicular Magnetic Anisotropy (PMA)4Level Characterization4Cive4       | 2<br>3<br>3<br>4<br>4<br>8<br>9             |

| 3 | <ul> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>3.5</li> </ul> | Introd<br>Film-I<br>3.2.1<br>3.2.2<br>3.2.3<br>Device<br>Objec<br>Test S<br>$R_P$ An | uction4Level Characterization4RA Product and TMR Evaluation4Damping Factor4Perpendicular Magnetic Anisotropy (PMA)4Level Characterization4Cive4Letup4 | $2 \\ 3 \\ 3 \\ 3 \\ 4 \\ 4 \\ 8 \\ 9 \\ 0$ |

| 4 | A F          | Parame  | etric DFT Scheme                                                    | 55  |  |  |  |  |

|---|--------------|---------|---------------------------------------------------------------------|-----|--|--|--|--|

|   | 4.1 Overview |         |                                                                     |     |  |  |  |  |

|   | 4.2          | Appro   | bach for the DFT Scheme                                             | 55  |  |  |  |  |

|   |              | 4.2.1   | Parameter Generation Framework                                      | 58  |  |  |  |  |

|   |              | 4.2.2   | DFT-Cell Operation                                                  | 61  |  |  |  |  |

|   |              | 4.2.3   | Replication of MTJ Characteristics Based on the DFT Circuit         | 63  |  |  |  |  |

|   | 4.3          | Comp    | ensating CMOS-Based Non-Idealities in the DFT Circuit               | 64  |  |  |  |  |

|   |              | 4.3.1   | Local Variation                                                     | 65  |  |  |  |  |

|   |              | 4.3.2   | Global Process Corner and Temperature                               | 67  |  |  |  |  |

|   | 4.4          | Test C  | Chip Implementation and Results                                     | 68  |  |  |  |  |

|   |              | 4.4.1   | DC Resistance Voltage Behavior                                      | 69  |  |  |  |  |

|   |              | 4.4.2   | Switching Characteristics                                           | 70  |  |  |  |  |

|   |              | 4.4.3   | Retention Characteristics                                           | 72  |  |  |  |  |

|   |              | 4.4.4   | Transistor Area Overhead                                            | 75  |  |  |  |  |

|   | 4.5          | Appli   | ication: Yield Characterization and process optimization $\ldots$ . | 76  |  |  |  |  |

|   | 4.6          | Sumr    | mary                                                                | 80  |  |  |  |  |

| 5 | DF'          | Γ for I | Long-Term Reliability                                               | 81  |  |  |  |  |

|   | 5.1          | Introd  | luction                                                             | 81  |  |  |  |  |

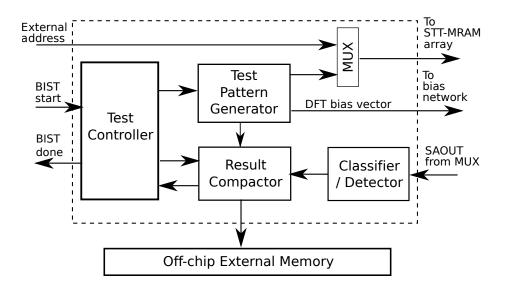

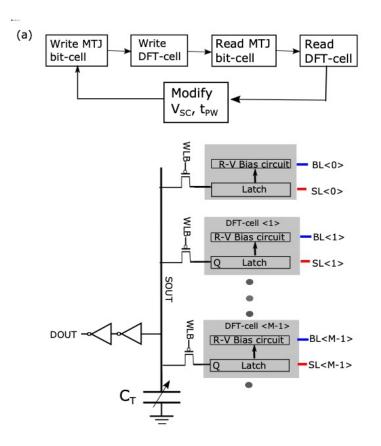

|   | 5.2          | Propo   | sed BIST Scheme and Test Methodolgy                                 | 83  |  |  |  |  |

|   |              | 5.2.1   | DFT Circuit                                                         | 83  |  |  |  |  |

|   |              | 5.2.2   | BIST Structure                                                      | 85  |  |  |  |  |

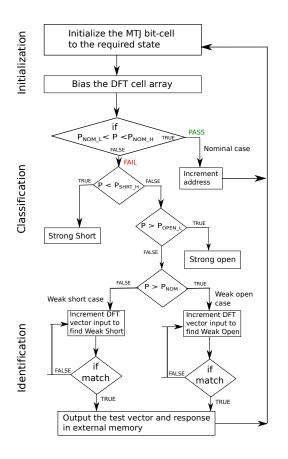

|   |              | 5.2.3   | DFT Fault Classification and Identification                         | 87  |  |  |  |  |

|   |              | 5.2.4   | Fault Analysis, Scheduling and Complexity                           | 89  |  |  |  |  |

|   |              | 5.2.5   | Read-Sensing Path Characterization                                  | 95  |  |  |  |  |

|   | 5.3          | Case S  | Study and Simulation                                                | 99  |  |  |  |  |

|   |              | 5.3.1   | Read-Sensing Circuitry Simulations                                  | 99  |  |  |  |  |

|   | 5.4          | Result  | ts                                                                  | 104 |  |  |  |  |

|   | 5.5          | Summ    | nary                                                                | 110 |  |  |  |  |

|   |              |         |                                                                     |     |  |  |  |  |

| 6          | 6 Conclusion                    |        |                                                                               |     |  |  |

|------------|---------------------------------|--------|-------------------------------------------------------------------------------|-----|--|--|

|            | 6.1                             | Resear | cch Contribution                                                              | 111 |  |  |

|            |                                 | 6.1.1  | In-Die Parametric Characterization                                            | 111 |  |  |

|            |                                 | 6.1.2  | Faster Wafer Screening and MTJ stack development                              | 111 |  |  |

|            |                                 | 6.1.3  | Bit-Cell Health Monitoring                                                    | 112 |  |  |

|            |                                 | 6.1.4  | 65nm Test-Chip Design and Implementation $\ldots \ldots \ldots \ldots \ldots$ | 112 |  |  |

|            |                                 | 6.1.5  | STT-MRAM Characterization                                                     | 112 |  |  |

|            |                                 | 6.1.6  | Future Work                                                                   | 113 |  |  |

| R          | efere                           | nces   |                                                                               | 114 |  |  |

| A Appendix |                                 |        |                                                                               | 125 |  |  |

|            | A.1 Publications From This Work |        |                                                                               |     |  |  |

# List of Tables

| 1.1 | Summary of the state of the art PMA-based STT-MRAM array implemen-<br>tations over the past years | 11  |

|-----|---------------------------------------------------------------------------------------------------|-----|

| 2.1 | MTJ thermal stability needed for different memory capacity and FIT rates,<br>Adapted from [1]     | 18  |

| 2.2 | MTJ device parameters                                                                             | 32  |

| 2.3 | MTJ structure dimension.                                                                          | 33  |

| 5.1 | Parameter tuning range for the DFT cell                                                           | 85  |

| 5.2 | Area estimate with respect to the total area of the STT-MRAM array                                | 106 |

# List of Figures

| 1.1 | STT-RAM performance comparison with other memory technologies [2].                                                                                            | 2  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

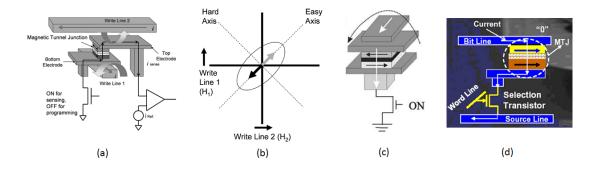

| 1.2 | (a) Field induced MRAM, (b) Toggle MRAM, (c) TAS MRAM, and (d) STT-RAM.                                                                                       | 3  |

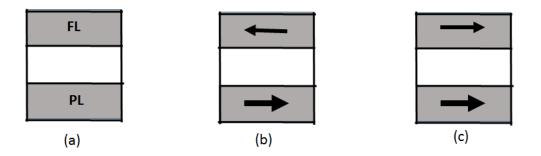

| 1.3 | Operating states of a magnetic tunnel junction (a) the MTJ symbol showing the free layer (FL) and pinning layer (PL) (b) AP state (c) P state                 | 5  |

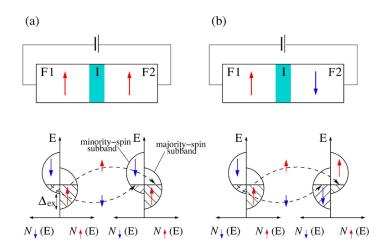

| 1.4 | (a) MTJ in parallel state, (b) in Anti parallel state. Adapted from [3]                                                                                       | 6  |

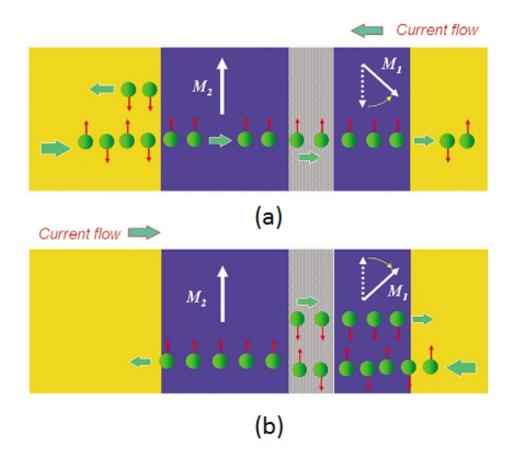

| 1.5 | Spin Torque Transfer (STT) mechanism,(a) $AP \rightarrow P$ ,(b) $P \rightarrow AP$ . Adapted from [4].                                                       | 7  |

| 1.6 | PMA-MTJ stack in a bit-cell. (a) MTJ stack layers, (b) MTJ states and switching, (c) STT-MRAM bit-cell.                                                       | 8  |

| 1.7 | Experimentally achieved TMR results reported till 2006. Adapted from [4].                                                                                     | 9  |

| 1.8 | TEM image of the 50nm MTJ stack [5]                                                                                                                           | 10 |

| 2.1 | Operating modes of 1T-1MTJ cell.                                                                                                                              | 16 |

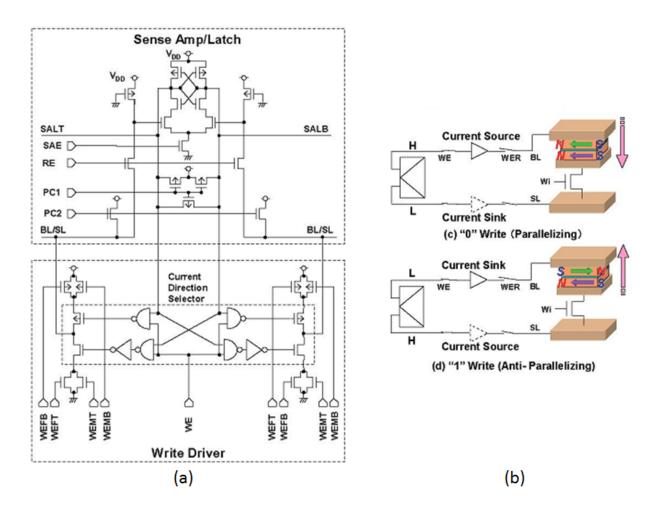

| 2.2 | (a) Sense amplifer latch with bidirectional write driver, (b) illustration of bidirectional write operation. Adapted from [6]                                 | 19 |

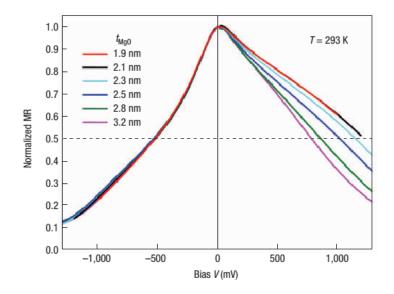

| 2.3 | TMR variation vs. bias voltage applied across the MTJ for various MgO dielectric thickness, Adapted from [7]                                                  | 20 |

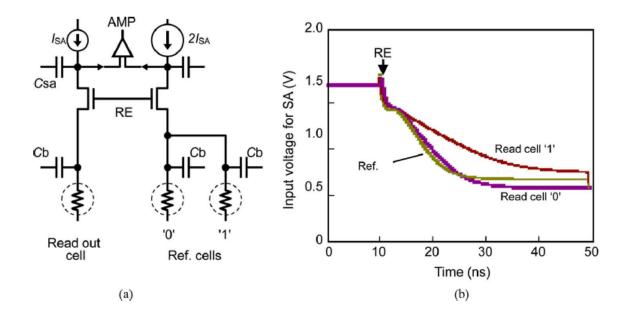

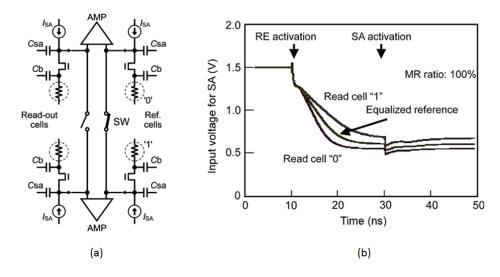

| 2.4 | (a) Schematic of a conventional reference cell read scheme, (b) shows voltage created at the input of the sense amplifier , Adapted from [6]                  | 22 |

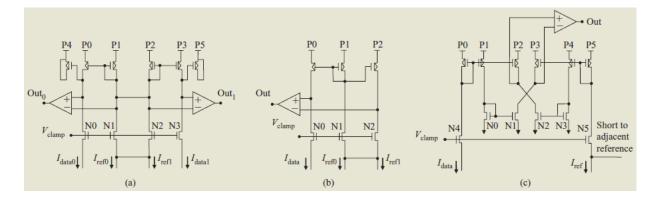

| 2.5 | (a) Differential read scheme, (b) conventional read scheme with 2 reference cells, (c) Cross coupled current mirror amplifier based scheme, adapted from [8]. | 23 |

|     |                                                                                                                                                               |    |

| 2.6  | (a) Dual array equalized reference scheme, (b) Simulation waveform. Adapted from [6]                                                                                                                                                                                                           |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

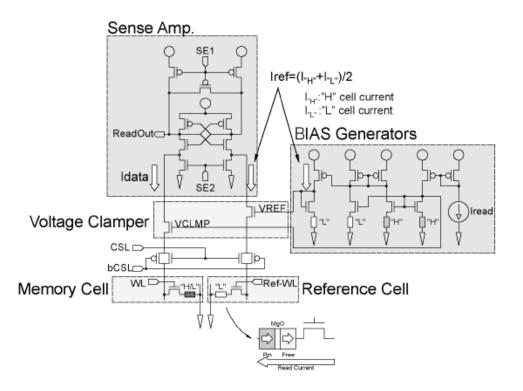

| 2.7  | Current sense amplifier design using a single reference cell and a clamped reference, adapted from [9]                                                                                                                                                                                         |

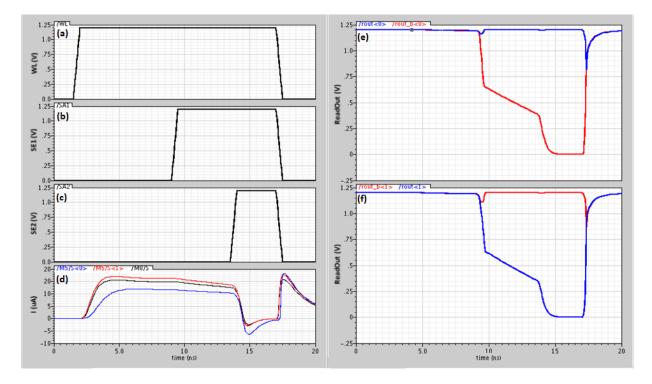

| 2.8  | Simulation waveforms for the sense amplifier (a) $V_{WL}$ , (b) $SE1$ , (c) $SE2$ (d) shows reference current (black), read '0' current (red) and read '1' current (e) Sense amplifier output for reading '0', (f) Sense amplifier output for a read '1'                                       |

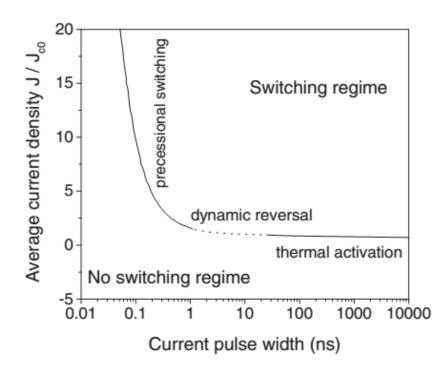

| 2.9  | MTJ switching regimes vs. write pulse duration, adapted from [?] 27                                                                                                                                                                                                                            |

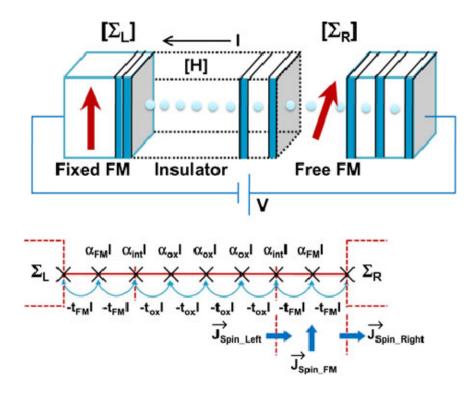

| 2.10 | (a) Shows the MTJ split into individual 2D layer unit cells (b) shows the NEGF representation of MTJ in form of 1D model. Adapted from [10] 29                                                                                                                                                 |

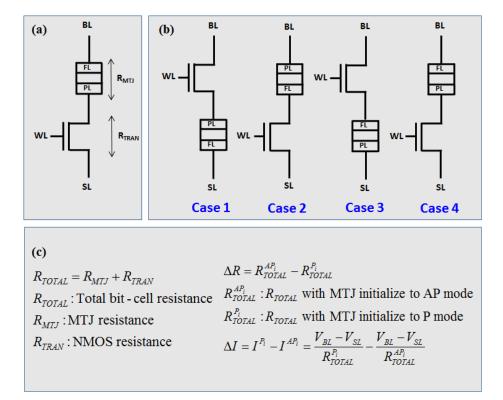

| 2.11 | (a) 1T-1MTJ STT-RAM cell. (b) Four different configurations of bit cell.<br>(c) Details of the extracted simulation parameters. The superscript of $P_i$ or $AP_i$ indicates the initial state of MTJ being P or AP mode                                                                       |

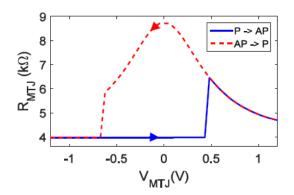

| 2.12 | MTJ hysteresis of 40-nm PMA-MTJ model. $V_{MTJ}$ is defined on the PL with respect to the FL                                                                                                                                                                                                   |

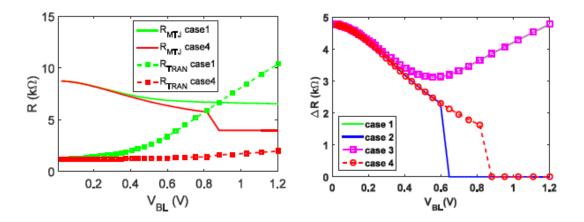

| 2.13 | (a) $R_{MTJ}$ and $R_{TRAN}$ vs. $V_{BL}$ for 1T-1MTJ cell with MTJ initialized in AP mode for case 1 and 4 ( $V_{WL} = 1.2$ V; $W_{NORM} = 1$ ). (b) $R$ vs. $V_{BL}$ ( $V_{WL} = 1.2$ V; $W_{NORM} = 1$ ) for all bit cell cases (the curves for cases 1 and 3 are overlapped)               |

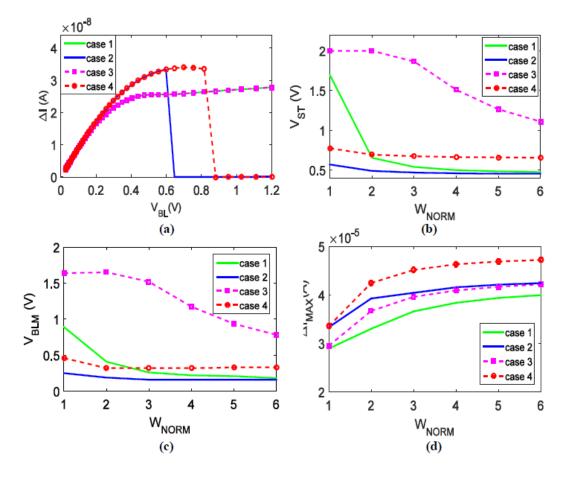

| 2.14 | (a) $\Delta I$ vs. $V_{BL}$ ( $W_{NORM} = 1$ ), (b) $V_{ST}$ , (c) $V_{BLM}$ , and (d) $\Delta I_{MAX}$ variation<br>as a function of $W_{NORM}$ . $V_{WL}$ is 1.2 V in (a)(b)(c)(d). $\ldots \ldots \ldots \ldots 37$                                                                         |

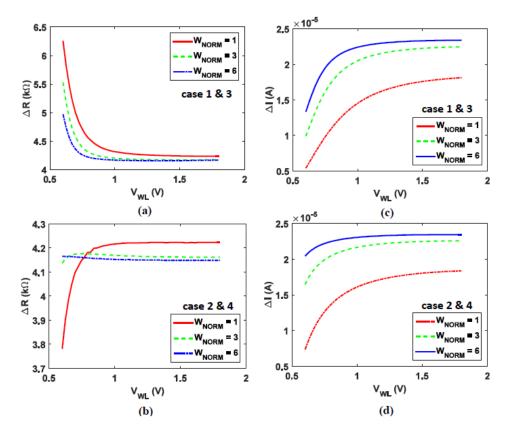

| 2.15 | $\Delta R$ vs. $V_{WL}$ for (a) cases 1 and 3 (source follower) and (b) cases 2 and 4.<br>$V_{BL} = 0.2$ V is used. $\Delta I$ vs. $V_{WL}$ for (c) cases 1 and 3 (source follower) and<br>(d) cases 2 and 4. $V_{BL} = 0.2$ V is used                                                         |

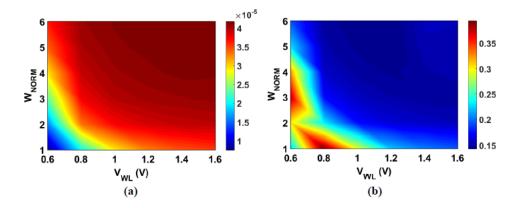

| 2.16 | 2D surface plots of (a) $\Delta I_{MAX}$ , (b) $V_{BLM}$ , as a function of $V_{WL}$ and $W_{NORM}$<br>for case 2                                                                                                                                                                              |

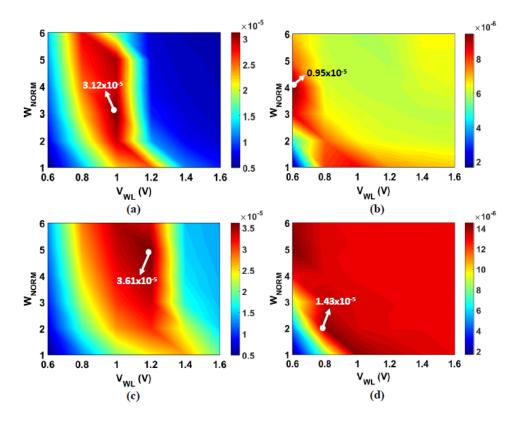

| 2.17 | 2D surface plots of $\Delta I_{MAX} - V_{BLM}$ product as a function of $V_{WL}$ and $W_{NORM}$ for (a) case 1, (b) case 2, (c) case 3 and (d) case 4                                                                                                                                          |

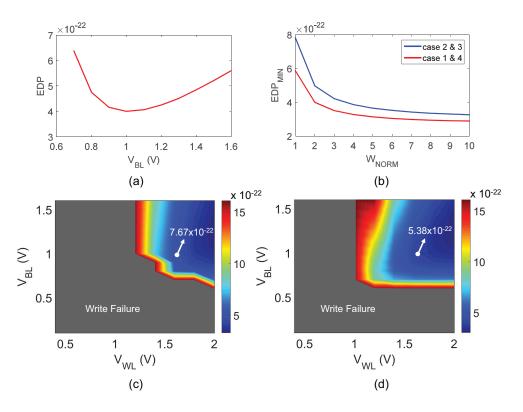

| 2.18 | (a) EDP vs. $V_{BL}$ for case 4 (at $V_{WL} = 1.6$ V, $W_{NORM} = 2$ ). (b) The $EDP_{MIN}$ vs. $W_{NORM}$ (at $V_{WL} = 1.6$ V). 2D surface plots of the $EDP_{MIN}$ as a function of $V_{WL}$ and $V_{BL}$ for a fixed width ( $W_{NORM} = 2$ ) for (c) cases 2 and 3, and (d) cases 1 and 4 |

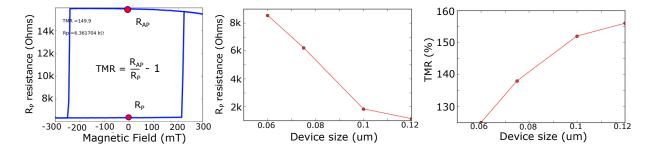

| 3.1  | Electrical characteristics of the MTJ device. (a) Shows the MTJ resistance<br>vs. applied magnetic field for an R-H loop. (b) shows the $R_P$ resistance vs.<br>device dimension. (c) TMR of the MTJ device vs. device size                                                                                                         | 44 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2  | Computed electrical diameter of the MTJ device vs. device size                                                                                                                                                                                                                                                                      | 45 |

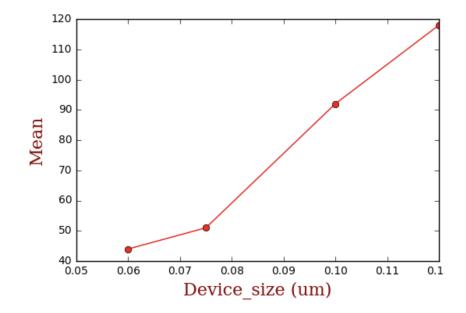

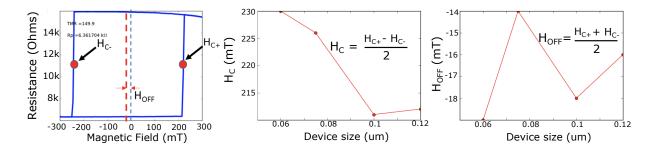

| 3.3  | Magnetic characteristics of the MTJ device (a) shows the R-H loop showing<br>the $H_C$ and $H_{off}$ . (b) $H_C$ vs device size (c) $H_{off}$ vs. device size                                                                                                                                                                       | 46 |

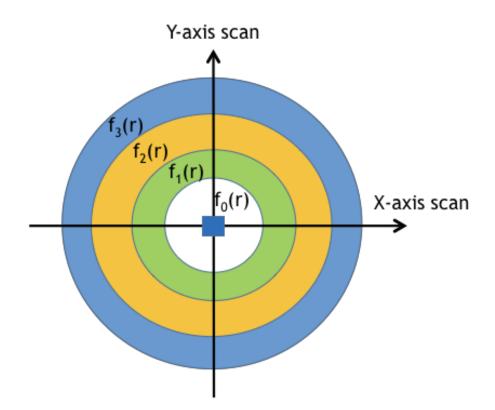

| 3.4  | Generalization of parameter spatial variation across the wafer                                                                                                                                                                                                                                                                      | 47 |

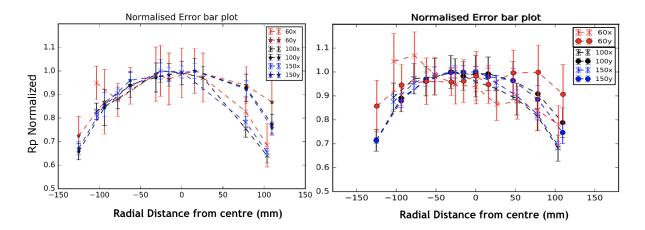

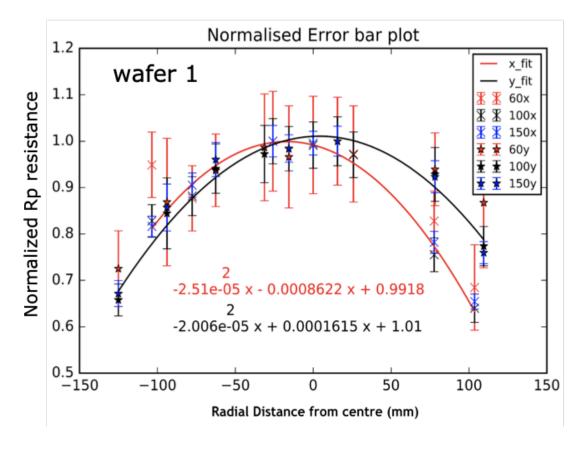

| 3.5  | $R_P$ resistance plots for MTJ stack of 60, 100 and 150 nm sizes. (a) Spatial distribution of Normalized $R_P$ resistance across wafer 1. (b) spatial distribution of $R_P$ resistance on wafer 2 (CMOS substrate)                                                                                                                  | 48 |

| 3.6  | Parabolic fitting for the $R_P$ spatial variation along the x and y axis of the wafer.                                                                                                                                                                                                                                              | 49 |

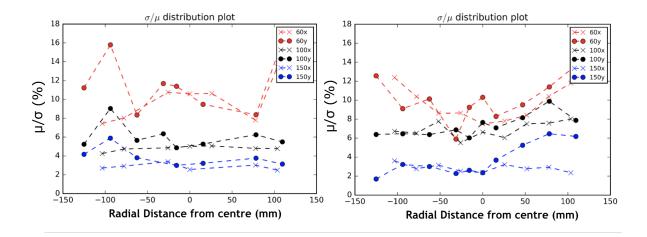

| 3.7  | Mean to the standard deviation ratio for $R_P$ resistance. (a) shows the spatial distribution for wafer 1 (b) spatial distribution for wafer 2 (CMOS substrate).                                                                                                                                                                    | 50 |

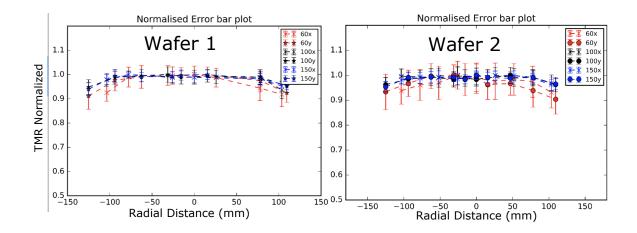

| 3.8  | Normalized TMR median value for MTJ devices for 60, 100 and 150nm devices. (a) spatial variation on wafer 1. (b) spatial variation on wafer 2 (CMOS substrate).                                                                                                                                                                     | 51 |

| 3.9  | Mean to standard deviation ratio for TMR (a) wafer 1. (b) wafer 2 (CMOS substrate deposition)                                                                                                                                                                                                                                       | 52 |

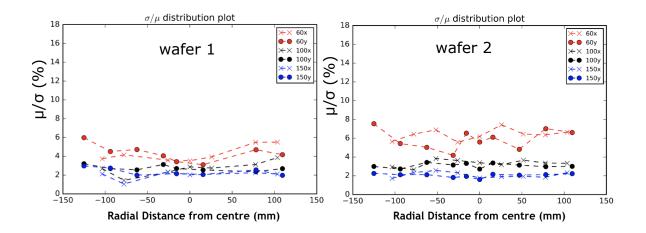

| 3.10 | Application of the spatial variation model on to a generic device model                                                                                                                                                                                                                                                             | 53 |

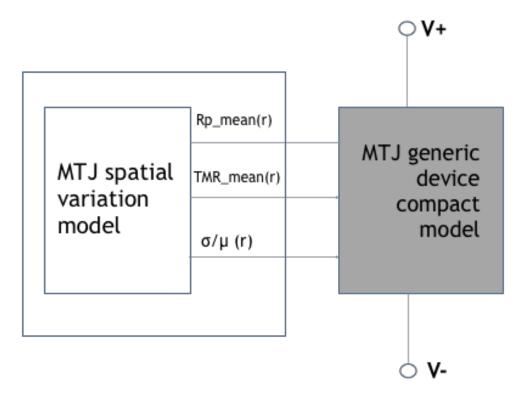

| 4.1  | (Left panel) STT-MRAM fabrication process flow, where the wafer testing<br>and pre-qualification step is included. (Right) The process for testing and<br>qualification adopted is shown in detail. The grey blocked region illustrates<br>the proposed scheme.                                                                     | 56 |

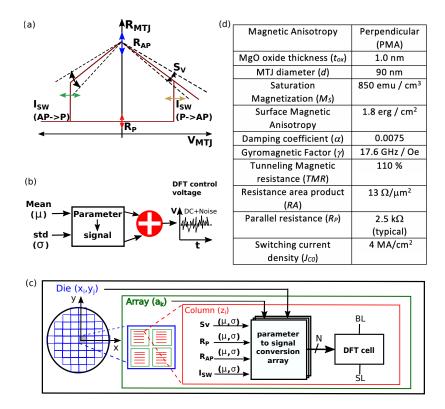

| 4.2  | (a) Generalized MTJ device parameter variations observed during single device level characterization. (b) MTJ device parameter mean and variance translated to control voltage. (c) Top level diagram for the DFT scheme. Here BL and SL are bit-line and source-line of the MTJ column. (d) Typical parameter values used for MTJ. | 57 |

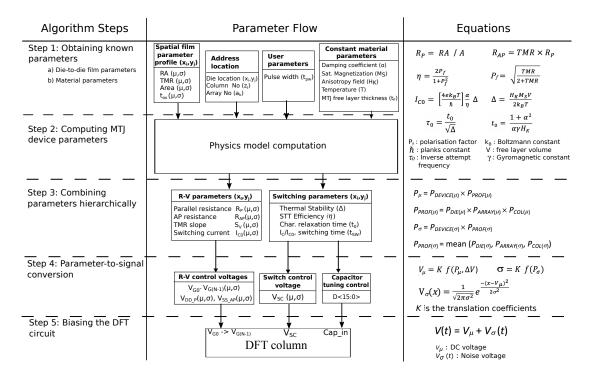

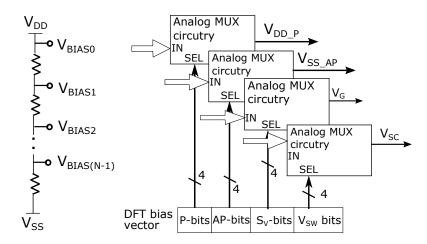

| 4.3  | Parameter generation framework to generate bias voltages for the DFT cir-<br>cuit operation                                                                                                                                                                                                                                         | 59 |

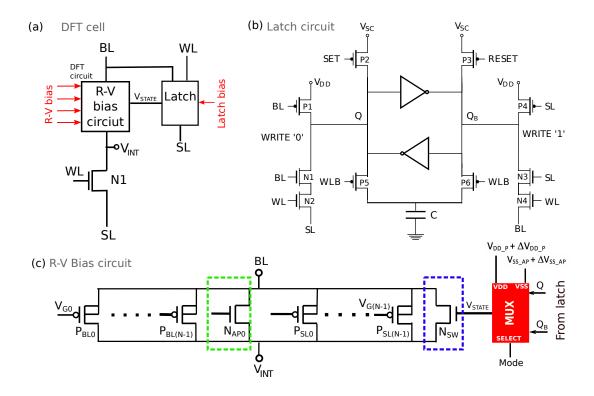

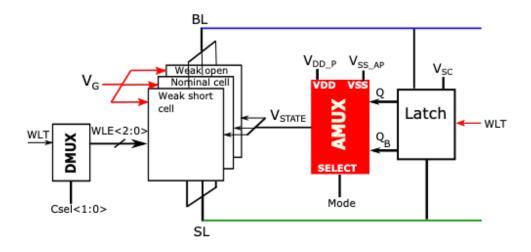

| 4.4  | DFT cell consisting of R-V bias circuit, latch, and the NMOS access transistor. (b) Latch circuit. (c) Generalized R-V bias circuit. BL, SL and WL represent bit-line, source-line and word-line inputs, respectively.                                                                                                                                                                                                                                                        | 62 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

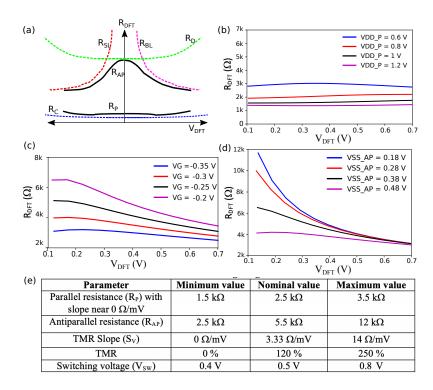

| 4.5  | Selective control of DFT characteristics using individual control voltages.<br>(a) $R_{DS}$ resistances contributed by each transistor group in the DFT circuit.<br>(b) Changing the $R_P$ resistance using $V_{DD_P}$ . (c) Impact of changing $V_G$ on RAP. Here $V_G = V_{G0} = V_{G1} = V_{G2} = V_{G3}$ . (d) Changing the $R_{AP}$ resistance using $V_{SS\_AP}$ . (e) DFT cell parameter tuning range. The results were based on 65–nm process pre–layout simulations. | 64 |

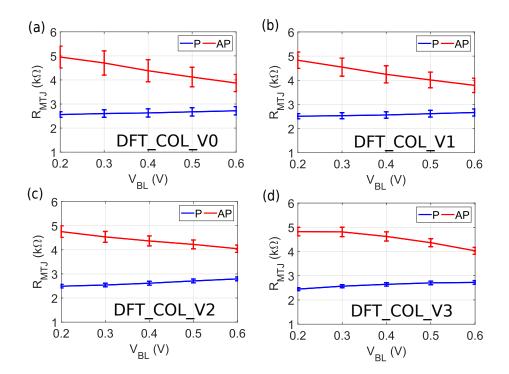

| 4.6  | R-V variation for different columns of the DFT cell arrays based on post<br>layout simulations. (a) DFT_COL_V0 (L = 1X), (b) DFT_COL_V1 (L = 2X), (c) DFT_COL_V2 (L = 3X), and (d) DFT_COL_V3 (L = 4X)                                                                                                                                                                                                                                                                        | 65 |

| 4.7  | (a) Process parameters for the target MTJ characteristics (b) Summary of the resistance variation due to transistor variability for each design.                                                                                                                                                                                                                                                                                                                              | 66 |

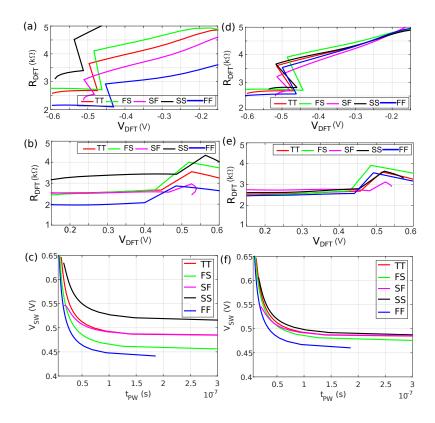

| 4.8  | Impact of global process corner (a)-(c) before correction and (d)-(f) after correction. $R_{DFT}$ vs. $V_{DFT}$ for (a,d) AP state and (b,e) P state. (c,f) $V_{SW}$ vs. $t_{pw}$ for P to AP. TT, FS, SF, SS, FF represent typical-typical, fast-slow, slow-fast, slow-slow, fast-fast, respectively.                                                                                                                                                                        | 67 |

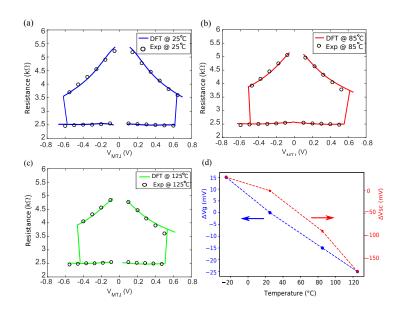

| 4.9  | Temperature dependency behavior of the DFT circuit resistance. The RV loop is shown for (a) 25° C, (b) 85° C, and (c) 125° C (b) RV bias compensation voltage based on post-layout simulation.                                                                                                                                                                                                                                                                                | 69 |

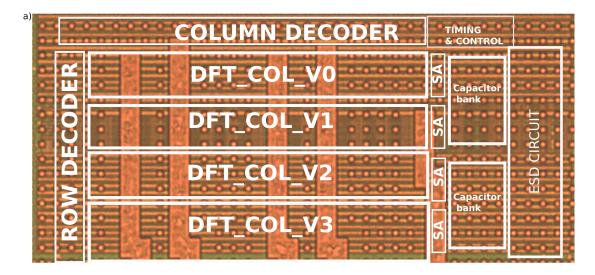

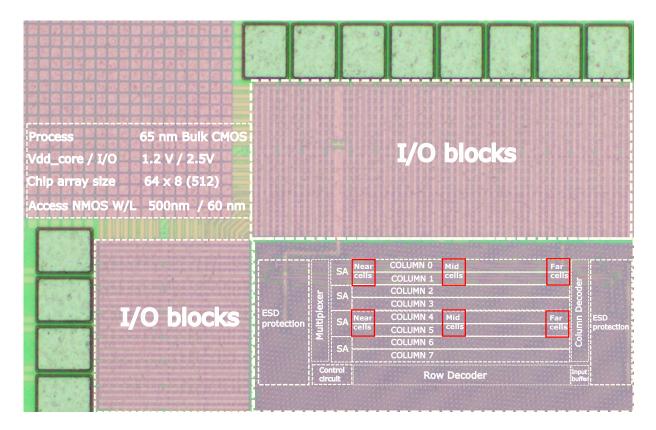

| 4.10 | Die micrograph of the test chip with peripheral circuitry in 65-nm CMOS technology.                                                                                                                                                                                                                                                                                                                                                                                           | 70 |

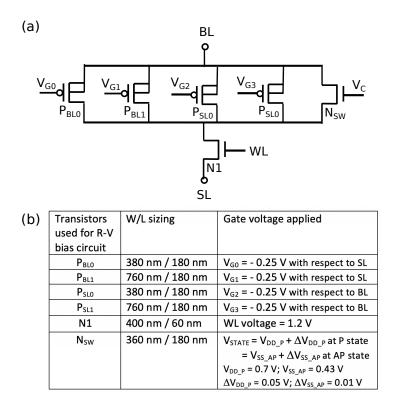

| 4.11 | Schematic design for the R-V bias circuit used for DFT cell. (b) Sizing and voltage for the transistors used in the design.                                                                                                                                                                                                                                                                                                                                                   | 71 |

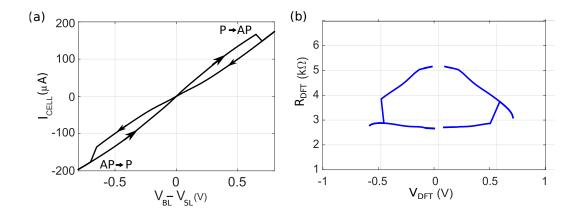

| 4.12 | (a) Bit-cell current $(I_{CELL})$ vs. voltage $(V_{BL}-V_{SL})$ loop from measurement.<br>(b) DFT vs. $V_{DFT}$ characteristics of the DFT circuit from measurement and post-layout simulation.                                                                                                                                                                                                                                                                               | 72 |

| 4.13 | Block diagram of column with the shared tunable capacitor bank circuitry.                                                                                                                                                                                                                                                                                                                                                                                                     | 73 |

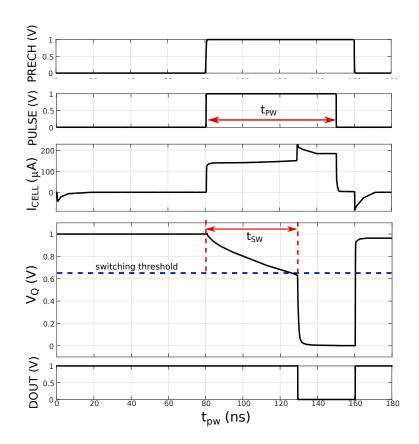

| 4.14 | Post-layout simulation waveforms for the DFT cell switching operation                                                                                                                                                                                                                                                                                                                                                                                                         | 74 |

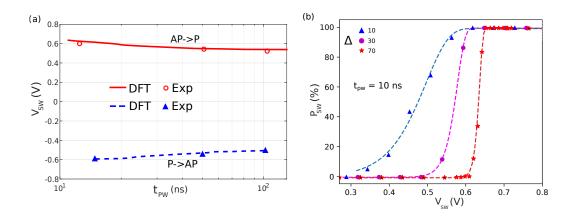

| 4.15 | (a) Switching voltage vs. write pulse width for $AP \rightarrow P$ and $P \rightarrow AP$ switching.<br>(b) DFT cell switching probability measured for different thermal stability factors ( $\Delta$ ). The markers and the lines represent the chip measured data and model simulation results, respectively.                                                                                                                                                              | 75 |

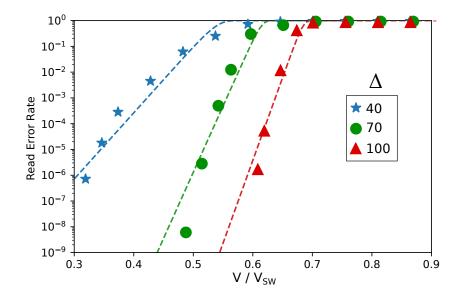

| 4.16 | Read error rate, showing the read-disturb mechanism exhibited by the DFT cell for different thermal stability factors ( $\Delta$ ). The markers and the lines represent the chip measured data and model simulation results, respectively.                                                                                                                       | 76 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.17 | Read access path used for yield characterization simulation of the STT-MRAM column.                                                                                                                                                                                                                                                                              | 77 |

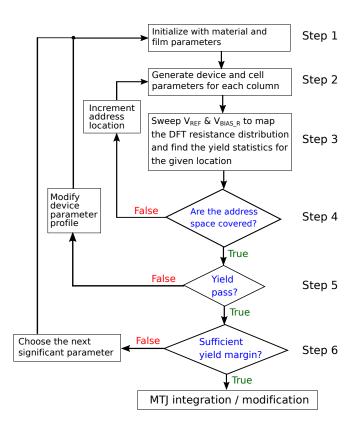

| 4.18 | Yield characterization and optimization process flow chart                                                                                                                                                                                                                                                                                                       | 78 |

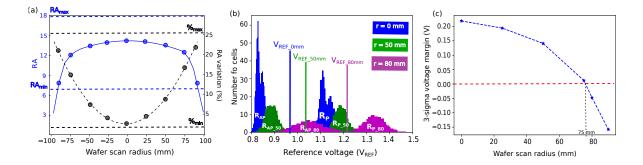

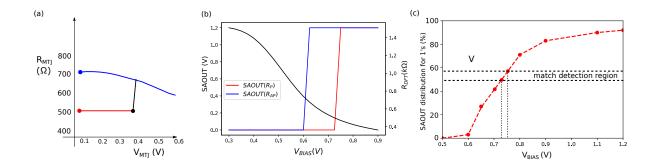

| 4.19 | RA product vs. radial distance from the center of wafer. The markers represent DFT cell output values. (b) Resistance distribution profile for AP and P states at 0 mm, 50 mm and 80 mm radial distance from the center of the wafer based on post layout simulation results. (c) 3-sigma read margin voltage based on sense amplifier outputs across the wafer. | 79 |

| 5.1  | DFT cell used for testing and replication of fault characteristics                                                                                                                                                                                                                                                                                               | 84 |

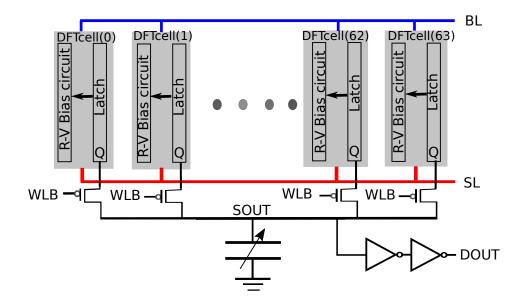

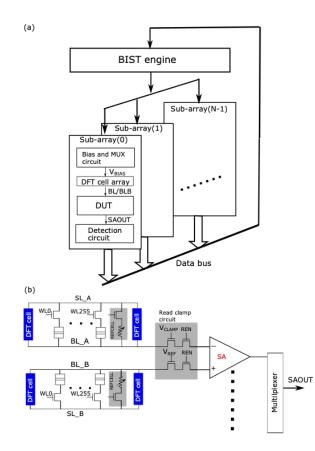

| 5.2  | (a) System level diagram of the BIST scheme. (b) Device under test (DUT), is the conventional STT-MRAM sub-array consisting of bit-cells, read sens-                                                                                                                                                                                                             |    |

|      | ing column and multiplexers                                                                                                                                                                                                                                                                                                                                      | 86 |

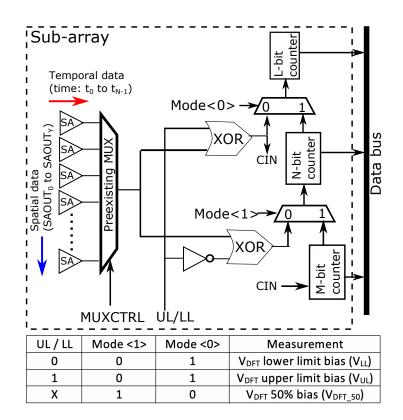

| 5.3  | BIST engine diagram within the sub array                                                                                                                                                                                                                                                                                                                         | 87 |

| 5.4  | Bias voltage generation and analog multiplexer array for selecting DFT con-<br>trol voltages.                                                                                                                                                                                                                                                                    | 88 |

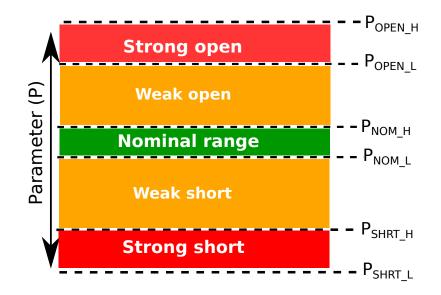

| 5.5  | Generalized parameter range of the MTJ device with defect.                                                                                                                                                                                                                                                                                                       | 89 |

| 5.6  | Flow chart for classification and identification of faults using the DFT scheme.                                                                                                                                                                                                                                                                                 | 90 |

| 5.7  | (a) Switching test cycle. (b) Block diagram of column with the shared tunable capacitor bank circuitry                                                                                                                                                                                                                                                           | 91 |

| 5.8  | (a)Test scheduling based on priority for different tests. (b) Test complexity for each test. Here, N and L correspond to the number of bit-cells in a bit-line column and number of read sense paths accessed simultaneously. M corresponds to the number of bits used to select the bias control voltage.                                                       | 93 |

| 5.9  | Detection circuit within a sub-array. The table shows the different configu-<br>ration modes for the circuit.                                                                                                                                                                                                                                                    | 94 |

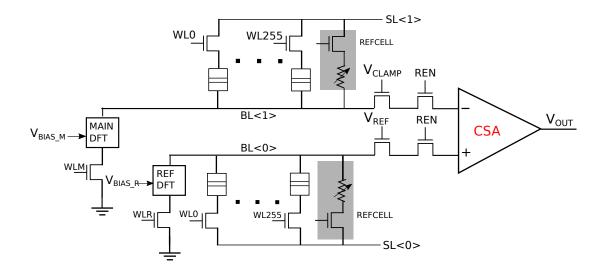

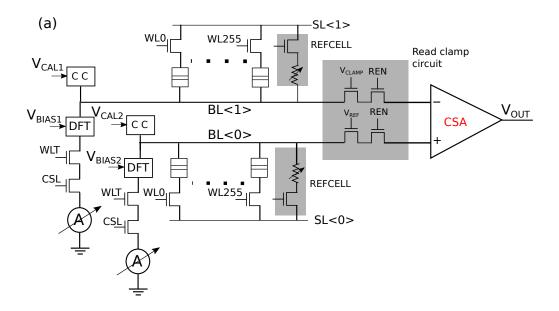

| 5.10 | Schematic for the column read sense path and the current sense amplifier (CSA). CC is the compensation circuit.                                                                                                                                                                                                                                                  | 96 |

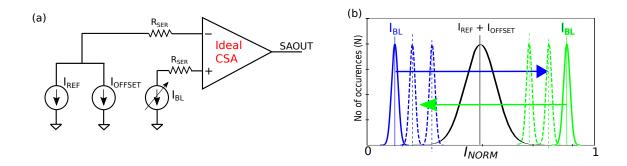

| 5.11 | (a) Simplified equivalent circuit model for offset current calculation. (b)<br>Offset characterization of read sensing circuitry using the DFT cells                                                                                                                                                                                                             | 97 |

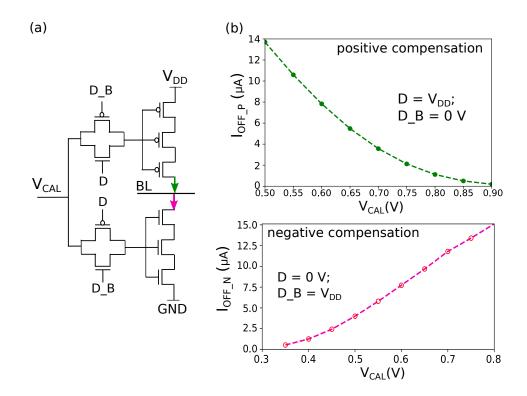

| 5.12 | (a) The read offset compensation circuit. (b) The offset compensation current from PMOS $(I_{OFFP})$ and NMOS $(I_{OFFN})$ chains.                                                                                                                                                                                                                                                                                                                                                     | 98  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

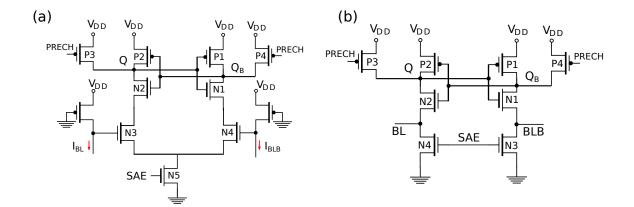

| 5.13 | Sense amplifier circuit design used for characterization. (a) Type I CLSA circuitry. (b) Type II VLSA sense amplifier circuit design.                                                                                                                                                                                                                                                                                                                                                  | 100 |

| 5.14 | Post layout simulation showing the read operation in a CLSA sensing scheme.                                                                                                                                                                                                                                                                                                                                                                                                            | 101 |

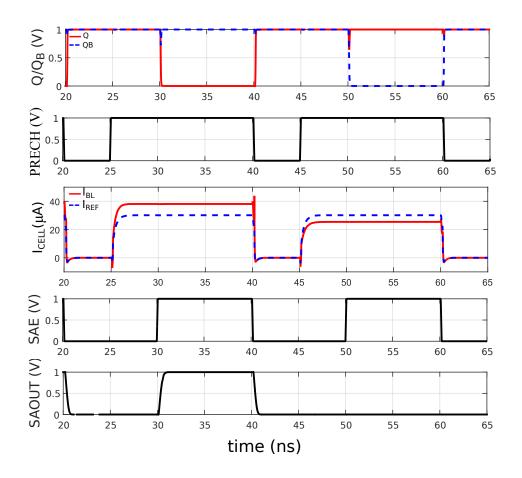

| 5.15 | Statistical yield simulation results for the read sensing yield as a function of the bit–line.                                                                                                                                                                                                                                                                                                                                                                                         | 102 |

| 5.16 | Bias voltage generation and analog multiplexer array for selecting DFT con-<br>trol voltages.                                                                                                                                                                                                                                                                                                                                                                                          | 103 |

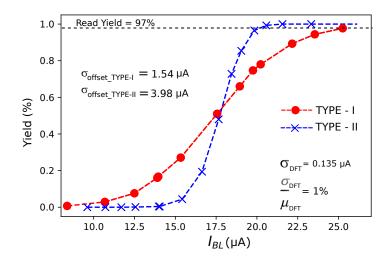

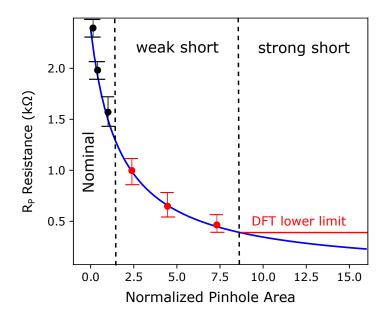

| 5.17 | $R_P$ vs. pin-hole area. The resistance degradation based on MATLAB plot<br>is shown in blue. The black and red corresponds to the measured resistance<br>from the test structure, and the simulation respectively. The dot represents<br>the mean value and the bounds represent the worst case max and min values.                                                                                                                                                                   | 104 |

| 5.18 | Die micrograph of the DFT sub-array implemented in 65 nm bulk CMOS process.                                                                                                                                                                                                                                                                                                                                                                                                            | 105 |

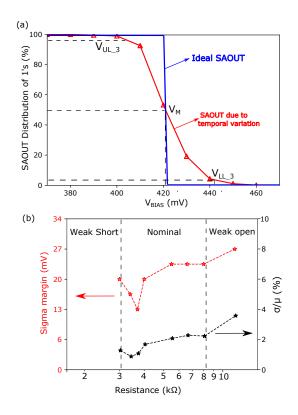

| 5.19 | Impact of temporal variation based on the test chip measured. (a) The SAOUT distribution vs $V_{BIAS}$ for ideal (blue) and temporal variation case (red). (b) Standard deviation of the $V_M$ for different resistance measured.                                                                                                                                                                                                                                                      | 106 |

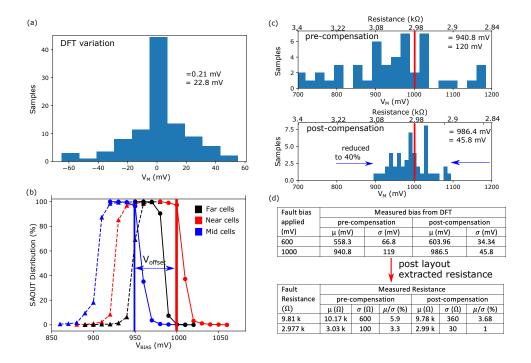

| 5.20 | the bias voltage for SA distribution with $V_M$ is shown on the top right. (b)<br>Distribution from the DFT cells obtained for a given SA location. (c) Re-<br>sistance distribution before (top) and after (bottom) read path circuit offset<br>compensation. The red line indicates the injected fault voltage and the blue<br>line indicates the measured match voltage $(V_M)$ bottom shows the corre-<br>sponding resistance values computed from post layout circuit simulation. |     |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 107 |

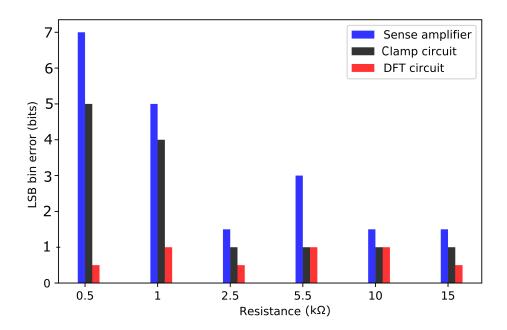

| 5.21 | Worst case LSB bin errors contributed by read sense amplifier, read voltage clamp circuit and the DFT circuit in the proposed scheme.                                                                                                                                                                                                                                                                                                                                                  | 109 |

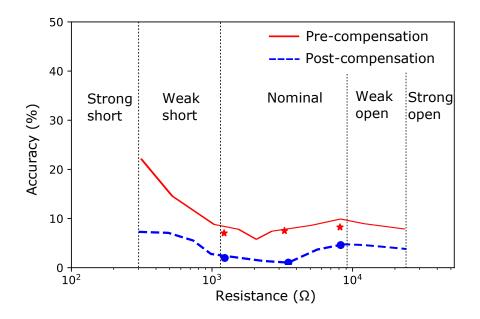

| 5.22 | simulations for the DFT scheme pre-compensation (red solid line) and post-<br>compensation (blue dashed line). The red stars and blue dots represent                                                                                                                                                                                                                                                                                                                                   | 110 |

|      | measured values before and after compensation.                                                                                                                                                                                                                                                                                                                                                                                                                                         | 110 |

## List of abbreviations

1T-1MTJ 1 Transistor 1 MTJ **AP** Anti-Parallel **BEOL** Back-End-of-the-Line **BL** Bit-line bcc Body Centre Cubic **BIST** Built in Self Test **CC** Compensation Circuit **CIPT** Current In-Plane Tunneling CMOS Complementary Metal Oxide Semiconductor **CLSA** Current Latch Sense Amplifier **CSA** Current Sense Amplifier **DFT** Design for Testability **DOS** Density of States **DRAM** Dynamic Random Access Memory **DUT** Device Under Test **EDP** Energy Delay Product fcc Face Centre Cubic FEOL Front-End-of-the-Line FIMS Field Induced Magnetic Storage FeRAM Ferroelectric Random Access Memory

**FM** Ferromagnetic Material **HKMG** High-K Dielectric metal Gate technology **IMA** In-Plane Magnetization Anisotropy imec Interuniversity Microelectronics Centre **IPMA** Interfacial Perpendicular Magnetic Anisotropy **IQR** Inter Quartile Range LSB Least Significant Bit LLG Landeu Lifshitz Gilbert MRAM Magnetic Random Access Memory MTJ Magnetic Tunnel Junction **NEGF** Non-Equilibrium Greens Function **PMA** Perpendicular Magnetic Anisotropy **P** Parallel **PRAM** Phase Change Random Access Memory **PMA** Perpendicular Magnetic Anisotropy **RAM** Random Access Memory **RRAM** Resistive Random Access Memory **RA** Resistance-Area Product **RH** Resistance - Magnetic Field **RSM** Read Sense Margin **RV** Resistance - Voltage bias **SA** Sense Amplifier **STT** Spin Torque Transfer **SRAM** Static Random access memory **TAS** Thermal Assisted Switching **NVM** Non-Volatile Memory **SAF** Synthetic Anti-Ferromagnet

SL Source-line

TAS Thermal Assisted Switching

TEM Transmission Electron Microscopy

TMR Tunnelling Magnetic Resistance

VCMA Voltage Controlled Magnetic Anisotropy

VSM Vibrating Spectral Magnetometry

WL Word-line

### Chapter 1

### Introduction

New technologies are changing the way we see embedded memory architectures. Motivated by the need for lower power and higher densities, new non-volatile memory technologies such as STT-MRAM, Resistive RAM, and PCRAM are likely to become a viable replacement for the DRAM technology in the near future. From the given class of memories, the Spin-Torque-Transfer (STT) Magnetoresistive Random-Access Memory (MRAM) has become a potential candidate for emerging non-volatile memory (NVM) devices [11]. In this chapter, we are introducing the non-volatile memories with emphasis on STT-MRAMs. We explore the motivation for STT-MRAM and the history of MRAM technology. The basic building block of the STT-MRAM is the Magnetic Tunnel Junction (MTJ) used in the bit-cells to store data. Firstly, we describe the functionality of the MTJ device and the physics of operation. Secondly, we look into the fabrication of MTJ devices and challenges faced during the mass production of large-scale STT-MRAMs. The yield and reliability limitations that prevent STT-MRAM from mass production are the main focus driving this research. The chapter concludes with the research goal and the outline.

### 1.1 Motivation

A good candidate for universal memories should have high read and write speeds, unlimited endurance, low power consumption. STT-RAMs have the potential to achieve the speed of SRAM, the density of DRAM with low power consumption, and it is a non-volatile solution, making it an ideal candidate for a universal memory. Figure 1.1 shows the performance comparison of STT-RAM with other memory technologies.

| _                           | SRAM               | DRAM               | Flash<br>(NOR)  | Flash<br>(NAND)  | FeRAM   | MRAM  | PRAM     | STT-RAM |

|-----------------------------|--------------------|--------------------|-----------------|------------------|---------|-------|----------|---------|

| Non-volatile                | No                 | No                 | Yes             | Yes              | Yes     | Yes   | Yes      | Yes     |

| Cell size (F <sup>2</sup> ) | 50-120             | 6–10               | 10              | 5                | 15-34   | 16-40 | 6–12     | 6–20    |

| Read time (ns)              | 1-100              | 30                 | 10              | 50               | 20-80   | 3–20  | 20–50    | 2–20    |

| Write / Erase<br>time (ns)  | 1-100              | 50 / 50            | 1 μs /<br>10 ms | 1 ms /<br>0.1 ms | 50 / 50 | 3–20  | 50 / 120 | 2–20    |

| Endurance                   | 1016               | 1016               | 105             | 105              | 1012    | >1015 | 1010     | >1015   |

| Write power                 | Low                | Low                | Very high       | Very high        | Low     | High  | Low      | Low     |

| Other power consumption     | Current<br>leakage | Refresh<br>current | None            | None             | None    | None  | None     | None    |

| High voltage<br>required    | No                 | 2 V                | 6–8 V           | 16–20 V          | 2–3 V   | 3 V   | 1.5–3 V  | <1.5 V  |

| Existing products Protot    |                    |                    |                 | otype            |         |       |          |         |

Figure 1.1: STT-RAM performance comparison with other memory technologies [2].

Comparing with SRAM cells, STT-RAM is approaching the read and write speed of the SRAM cell designs, and has better performance than other non-volatile memory technologies. Power consumption can be compared by looking at the static leakage and dynamic power consumption during memory access. STT-RAM's have low static power consumption due to its non-volatile nature with very low leakage current compared to SRAM cells. Considering dynamic power, STT-RAM's need higher write power consumption at high speeds compared to SRAM cells. This increase in switching current at high write speeds is due to shifting of the MTJ switching regimes. Several new switching strategies are being explored to reduce switching current. The STT-RAM has been considered actively as a replacement for on-chip SRAM cache memories because of its promising results [12] [13]. STT-RAMs are also compared with DRAM in terms of circuit density and performance. They may not provide the same density advantages as the DRAM cells [14]. Comparison of read and write performance shows that the STT-RAM has the same read performance as DRAM's, but its inferior in terms of write performance.

Research is also done on alternative non-volatile technologies for endurance, but most of them are not meeting the endurance capabilities (E = Number of cycles of successful

operation/life-time) of STT-RAM. Some of the memory technologies and their endurance values are as follows. a) Phase change memory(PRAM) (E = $10^{10}$ ), b) Resistive change memory (RRAM) (E =  $10^{10}$ , c) FeRAM ( $E = 10^{12}$ ), d) Flash Technologies ( $10^5$ ) lack the endurance of existing SRAM, DRAM technologies. Currently used STT-RAM memories have an endurance of  $10^{15}$

#### **1.2** Evolution of MRAM and Future

Figure 1.2: (a) Field induced MRAM, (b) Toggle MRAM, (c) TAS MRAM, and (d) STT-RAM.

MRAM development can be classified based on the development of write mechanisms employed for each generation of MTJ devices. Figure 1.2 shows the evolution of MRAM write technology. The write operation in the MRAM has changed drastically with the change in MTJ technology. The first generation of MRAM, called the field-induced magnetic storage (FIMS)-MRAM [15], relied on passing a current through the write line. Here the write line was placed close to the free layer so that they are magnetically coupled. A high current is then passed through the write line to magnetize the free layer. However, there were limitation to this writing scheme such as half-selection problem of bit cells and scalability issues. The half selection problem occurs in FIMS-MRAM, where all the cells in the column are partially selected when only a single cell in the column is accessed. The half-selection problem was mitigated by the introduction of toggle mode MRAM [16]. The Toggle-RAM shown in Fig. 1.2(b) uses Savtchenko switching to switch the Synthetic Anti-Ferromagnetic (SAF) MTJ structure. Here two perpendicular write lines 1 and 2 are used in a two-step write sequence to program the MTJ.

Another technique adopted was to program the MTJ in a thermally assisted manner. These class of MRAM's were called as TAS MRAM [17]. Initially, a current is passed through the

MTJ junction to heat it above the curie temperature  $(T_C)$  as shown in Fig. 1.2(c). Then a current pulse is passed through the write line to magnetize the free layer. Here the free layer is at a temperature greater than the curie temperature  $(T \ge T_C)$ , hence the MTJ can be switched with a smaller write current. This memory writing technique also poses major drawbacks, such as a longer time to heat the MTJ element and scalability issues.

Figure. 1.2(d) shows the write process in a typical STT-MRAM cell. The theoretical prediction for writing mechanism based on spin torque transfer (STT) technique was proposed by Slonzewski [18]. STT process involves a spin polarised current being passed through the MTJ, where the polarised electrons passing through impart its angular momentum to the free layer, magnetizing the material. Currently different novel switching mechanisms are being investigated to improve the write performance of the MRAM devices. Current focus of research is on the MTJ device physics level to improve the write performance of the MTJ. The breakdown in the dielectric barrier is one of the most prominent failure mechanisms in PMA-MTJ devices that work based on STT write mechanism. Scaling with constant write energy demands decreasing of the RA product which requires decreasing in the MgO barrier thickness. This would lead to reliability issues due to extremely thin layer thickness of the dielectric material. Alternate device-level techniques such as voltagecontrolled magnetic anisotropy (VCMA) [19] or spin-orbital torque (SOT) assisted STT [20] promises a reduction in the switching current without reducing MgO thickness, that could alleviate the stress on the dielectric material. Some of the alternate areas of research are a) Multiferroic [21] b) Spin-Hall effect switching c) Magnetostrictive switching [22].

#### **1.3 MTJ Device Physics**

Magnetic tunnel junction consists of 2 ferromagnetic (FM) materials separated by a dielectric material. The dielectric thickness is set at a few angstroms so that electrons can tunnel through the insulation barrier. Julliere proposed a model for the conduction of electrons through such a structure. Based on his proposal, the electron conduction consists of spin-up and spin-down polarized electrons, and the spins are conserved while tunneling through the dielectric material from one FM layer to another. The conductance across the junction depends on the relative magnetization between the fixed and the free layer of the ferromagnetic material. The state of the MTJ when  $\theta = 0^{\circ}$  is called as the Parallel (P) state. The MTJ has its maximum conductance (minimum resistance  $R_P$ ). The state of the MTJ when  $\theta = 180^{\circ}$ . The MTJ exhibits the least conductance here (maximum resistance  $R_{AP}$ ) is the Anti-Parallel (AP) state. The symbolic representation of AP and P states are as shown in the Fig 1.3.

Figure 1.3: Operating states of a magnetic tunnel junction (a) the MTJ symbol showing the free layer (FL) and pinning layer (PL) (b) AP state (c) P state.

The equation for conductance is described as shown

$$G(\theta) = \frac{G_P - G_{AP}}{2} + \frac{G_P + G_{AP} cos(\theta)}{2}$$

(1.1)

From this the maximum Tunnelling Magnetic Resistance (TMR) ratio can be derived as  $(\theta = 0^{\circ})$

$$G(\theta) = \frac{G_P - G_{AP}}{G_{AP}} \tag{1.2}$$

$$R(\theta) = \frac{R_{AP} - R_P}{R_P} \tag{1.3}$$

where  $G_{AP}$  is the conductance when  $\theta = 180^{\circ}$ , and  $G_P$  is the conductance when  $\theta = 0^{\circ}$ .  $R_{AP}$ and  $R_P$  are corresponding resistances respectively. As per classical band theory, the reason for the TMR effect in such hetero-structures is due to the difference in density of states (DOS) for spin up (N $\uparrow$ ) and spin down (N $\downarrow$ ) electrons at the Fermi level ( $E_F$ ) for each of the sandwiched ferromagnetic material. When the dielectric thickness approach the tunneling barrier thickness, the spin polarised electrons can tunnel through the barrier into their corresponding sub-band without losing its spin momentum as shown in Fig 1.4. Here the MTJ conductance for a given spin is proportional to the product of the DOS( $E_F$ ) at each ferromagnetic material. During parallel state, the sub-bands for one of the spins (either spin up or spin down), have higher DOS product ( $N_{FM1} \uparrow \times N_{FM2} \uparrow$  or  $N_{FM1} \downarrow \times N_{FM2} \downarrow$ ), resulting in higher conductance. However, for AP state, the product of the DOS values from the FM material are minimum, resulting in a lower conductance. In this perspective, the polarisation of electrons in a FM layer can be defined as

Figure 1.4: (a) MTJ in parallel state, (b) in Anti parallel state. Adapted from [3].

$$P = \frac{N \uparrow -N \downarrow}{N \uparrow +N \downarrow} \tag{1.4}$$

Fig. 1.5(a) shows the case for AP  $\rightarrow$  P switching where electrons are passing through the MTJ material from the pinning layer to the free layer. The electrons get spin polarised after passing through the 1st layer of ferromagnetic material (pinning layer). This spin polarised current then tunnels through the thin dielectric material and interacts with the 2nd ferromagnetic layer (free layer), where the interaction leads to the electrons imparting its spin angular momentum to the free layer, resulting in the magnetization switching of the free layer. Figure 1.5(b) shows the case for P  $\rightarrow$  AP switch, where the electrons move from free to pinning layer. Here the tunneling process is similar to the previous case, however, the spin polarised current is reflected into the free layer, toggling its existing magnetization state to AP mode. The P  $\rightarrow$  AP switching is a lower efficiency process compared to the (a), hence the switching threshold current are asymmetrical  $I_C(AP \rightarrow P) \neq I_C(P \rightarrow AP)$ . Initial STT based MTJ structures used In-Plane Magnetization Anisotropy (IMA), where the magnetization plane is parallel to the MTJ plane. Due to MTJ scaling, the read operation of MTJ became more error-prone and the data retention capability was affected. This could mean that the thermal stability for IMA based MTJ structures drop rapidly

with device scaling. Additionally, during the write operation, the energy has to be spent to counteract the unnecessary demagnetization field of the free layer[23], which does not contribute to thermal stability. In order to avoid these effect, the MTJ materials with perpendicular magnetic anisotropy (PMA) was introduced. Here the MTJ is magnetized

Figure 1.5: Spin Torque Transfer (STT) mechanism,(a) AP  $\rightarrow$  P,(b) P  $\rightarrow$  AP. Adapted from [4].

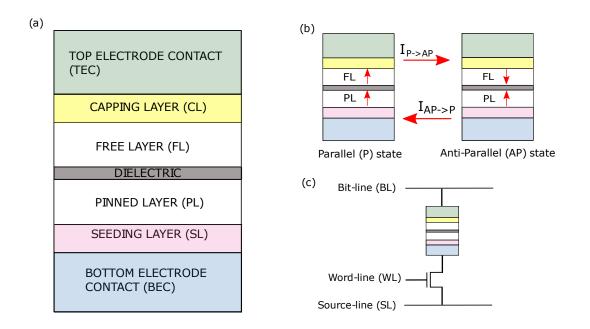

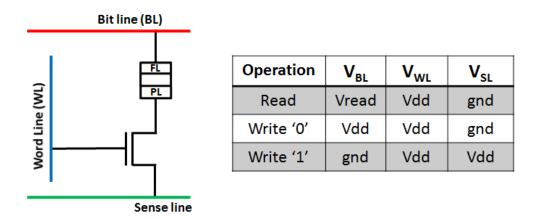

perpendicular to the plane by arranging the crystalline structure of the free layer material perpendicular to the MTJ plane. The technique severely reduced the write current needed without sacrificing on the thermal stability, which allowed for the scaling of the devices to diameters of 40 nm and below. The composition of the modern MTJ stack is shown in Fig. 1.6(a). The pinned layer provides a stable reference magnetic orientation for accessing the data stored in the MTJ stack. Depending on the magnetization of the free layer to its anisotropic easy axis provided by the pinned layer, the MTJ can be defined to be in Anti-Parallel (AP) state or Parallel (P) state as shown in Fig. 1.6(b). MTJ exhibits resistance in both parallel state ( $R_P$ ) and anti-parallel state ( $R_{AP}$ ). Fig. 1.6(c) shows the conventional STT-MRAM bit-cell consisting of the MTJ device and the NMOS access transistor.

Figure 1.6: PMA-MTJ stack in a bit-cell. (a) MTJ stack layers, (b) MTJ states and switching, (c) STT-MRAM bit-cell.

### **1.4 MTJ Fabrication and Implementation**

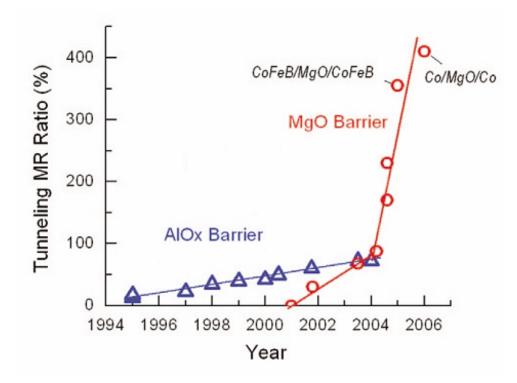

Materials and fabrication techniques can play a crucial role in deciding the quality of the MTJ created. Juliere demonstrated the TMR effect using a Fe/Ge/Co junction which shows a TMR of 14% at a temperature of 4 K [24]. This work was improved to get higher TMR values (15%) at room temperature using  $AlO_X$  as the dielectric material. The material processing techniques were improved further to yield a TMR of up to 70% using junctions such as CoFeB/AlOx/CoFeB. Several theoretical predictions were made for higher TMR using the crystalline structure of MgO dielectric which would make the tunneling process to be more dependent on the spin of electrons. Two major experimental data proved this concept, Yuasa et.al proposed an MTJ structure where the MgO layer was fabricated using molecular beam epitaxy yielding a TMR of 180% [7]. Another structure proposed by Parkin et.al uses a sputtering technique for MgO deposition that showed a TMR of 220% [25]. The Fig. 1.7 shows the rise of TMR over the past years [4].

Current STT-MRAM bit-cells utilize magnetic tunnel junction (MTJ) with perpendicular magnetic anisotropy (PMA) [23]. These MTJ stacks are deposited in a post-CMOS back-

Figure 1.7: Experimentally achieved TMR results reported till 2006. Adapted from [4].

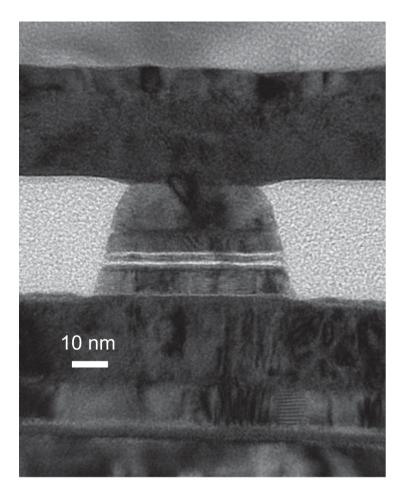

end-of-the-line (BEOL) deposition process [26][27][28] in the regular CMOS fabrication flow. The PMA-MTJ stacks is composed CoFeB ferromagnetic material for the pinned (PL) and the free layer (FL). The MgO dielectric material is used for seperating the ferromagentic materials. The transmission electron microscopy image of the current PMA MTJ stack for a 50 nm MTJ device is as shown in Fig. 1.8. The MTJ integration schemes and the level of metallization schemes are critical in forming uniform deposition over the wafer. Table 1.1 summarizes the features and the challenges addressed during the implementation of PMA-based STT-MRAM array over the years. Asymmetrical write switching current has been an issue during the advent of STT-MRAM bit-cells. This was equalized by reverse connecting the access transistor to the MTJ device and using its source degeneration effect [29]. During the initial years of PMA-based STT-MRAM, the MTJ stack integration has been highly dependent on the CMOS node, and the stack was optimized uniquely for each process. However, this changed when the STT-MRAM integration scheme started following existing fabrication processes such as the high-density DRAM process [30]. Also, the need for standardization of the STT-MRAM integration process motivated the MTJ

Figure 1.8: TEM image of the 50nm MTJ stack [5].

fabrication and deposition to be compatible with bulk, FINFET, and FDSOI CMOS processes. Thus current MTJ stack is implemented at higher metal layers to decouple the stack from underlying front-end-of-line (FEOL) layers. The work by Lee et al. [11] proposed an integration scheme that is compatible with bulk, FDSOI or FinFET processes in the 28-nm node. This implementation methodology provides opportunities for incorporating test structures that connect to lower metal levels for initial characterization and testing of peripheral circuitry in the CMOS process prior to and post MTJ deposition. Additionally with scaling, the interconnect resistance is rapidly increasing, forcing the implementations to adopt 2 metal schemes for bit-line implementation [31]. The CMOS process scaling also results in increased BL and SL parasitic resistance variation impacting the read and write performance of the bit-cells. Modern designs are incorporating low-power read and write

| Publication  | Lin et  | Lu et al.      | Song et   | Rho et    | Shum et   | Shih et  | Wei et   |

|--------------|---------|----------------|-----------|-----------|-----------|----------|----------|

|              | al.     |                | al.       | al.       | al.       | al.      | al       |

| Technology   | TSMC    | 40  nm         | Samsung   | -         | Global    | TSMC     | Intel 22 |

|              | 45  nm  |                | 28  nm    |           | foundries | 40  nm   | nm       |

|              |         |                |           |           | 2x        |          |          |

|              |         |                |           |           | CMOS      |          |          |

| Core Volt-   | 1.1 V   | 1.2 V          | 1.0 V     | 1.8 / 1.2 | -         | 1.1 V    | 1.1 V    |

| age          |         |                |           | V         |           |          |          |

| Metalization | M3      | M4             | -         | -         | M5        | M3       | M2       |

| Features     | (a) Re- | (a) 20         | (a)       | (a)       | (a) High  | (a)      | (a)      |

|              | verse   | ns read        | Novel     | Hierar-   | density   | Read     | Write-   |

|              | con-    | access         | integra-  | chical    | and       | current  | verfiy-  |

|              | nected  | (b)            | tion,     | bit-line  | process   | resolu-  | write    |

|              | for     | Lowest         | pattern-  | (b) self- | compat-   | tion $<$ | scheme   |

|              | write   | write          | ing and   | aligned   | ibility   | +/- μA   | (b) Low  |

|              | current | power          | stack-    | DRAM      | with      | , .      | voltage  |

|              | equal-  | (3.2           | ing. (b)  | process   | HKMG,     |          | read (4  |

|              | ization | $\dot{\mu}W$ / | 10 year   | 1         | Finfet,   |          | ns at    |

|              |         | MBps)          | reten-    |           | FDSOI     |          | 0.9 V)   |

|              |         | ± /            | tion at   |           | (b)       |          | ,        |

|              |         |                | $85 \deg$ |           | Flash     |          |          |

|              |         |                | С         |           | memory    |          |          |

|              |         |                |           |           | replace-  |          |          |

|              |         |                |           |           | ment      |          |          |

Table 1.1: Summary of the state of the art PMA-based STT-MRAM array implementations over the past years.

schemes. The read sense margin is directly impacted by the bit-line parasitic resistance and the accuracy of the reference current generated. Thus, the accurate characterization of parasitic resistance variation across bit-lines is needed to adopt appropriate resistance matching schemes. To mitigate the impact of bit-line resistance and capacitance, hierarchical bit-line schemes [30] are adopted for larger memory sizes.

### 1.5 Test and Characterization of STT-MRAMs

Parametric testing has been widely used for MRAM technology development [32], which complements the simulation process by offering better coverage of testing conditions on the processed wafer. The previous works used analog multiplexer modules for monitoring cell resistance characterization and digital testing [32]. Alternatively, other strategies for memory built-in self-testing are employed to detect stochastic retention failures in STT-MRAM arrays [33]. Although these techniques characterizes specific MTJ cell resistance distribution issues in the lab environment, it provides limited avenues for exploration of parameter sensitivity. The MTJs have limitations in terms of its parameter tunability once deposited. Ideally, fabrication optimization requires the viability of different parameter tuning options. For instance, understanding the contribution of each MTJ device parameter, such as resistance-area (RA) variation or tunnel magnetoresistance (TMR), to the yield could be achieved by implementing MTJ stacks with different parameter combinations on multiple wafers. However, this strategy would be cumbersome due to the numerous process parameter options to be manipulated and would require significant wafer turnaround time and effort.