# Dynamic Laser Fault Injection Aided by Quiescent Photon Emissions in Embedded Microcontrollers: Apparatus, Methodology and Attacks

by

Karim Amin

A thesis presented to the University of Waterloo in fulfillment of the thesis requirement for the degree of Doctor of Philosophy in Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2020

© Karim Amin 2020

## Examining Committee Membership

The following served on the Examining Committee for this thesis. The decision of the Examining Committee is by majority vote.

| External Examiner:        | Domenic Forte<br>Associate Professor, Dept. of ECE, University of Florida         |

|---------------------------|-----------------------------------------------------------------------------------|

| Supervisor:               | Catherine Gebotys<br>Professor, Dept. of ECE, University of Waterloo              |

| Internal Member:          | Manoj Sachdev<br>Professor, Dept. of ECE, University of Waterloo                  |

| Internal Member:          | Gordon Agnew<br>Associate Professor, Dept. of ECE, University of Waterloo         |

| Internal-External Member: | Germán Sciaini<br>Associate Professor, Dept. of Chemistry, University of Waterloo |

#### Author's Declaration

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### Abstract

Internet of Things (IoT) is becoming more integrated in our daily life with the increasing number of embedded electronic devices interacting together. These electronic devices are often controlled by a Micro-Controller Unit (MCU). As an example, it is estimated that today's well-equipped automobile uses more than 50 MCUs. Some MCUs contain cryptographic co-processors to enhance the security of the exchanged and stored data with a common belief that the data is secured and safe. However many MCUs have been shown to be vulnerable to Fault Injection (FI) attacks. These attacks can reveal shared secrets, firmware, and other confidential information. In addition, this extracted information obtained by attacks can lead to identification of new vulnerabilities which may scale to attacks on many devices. In general, FI on MCUs corrupt data or corrupt instructions. Although it is assumed that only authorized personnel with access to cryptographic secrets will gain access to confidential information in MCUs, attackers in specialized labs nowadays may have access to high-tech equipment which could be used to attack these MCUs. Laser Fault Injection (LFI) is gaining more of a reputation for its ability to inject local faults rather than global ones due to its precision, thus providing a greater risk of breaking security in many devices.

Although publications have generally discussed the topic of security of MCUs, attack techniques are diverse and published LFI provides few and superficial details about the used experimental setup and methodology. Furthermore, limited research has examined the combination of both LFI and Photo-Emission Microscopy (PEM), direct modification of instructions using the LFI, control of embedded processor resets using LFI, and countermeasures which simultaneously thwart other aspects including decapsulation and reverse engineering (RE).

This thesis contributes to the study of the MCUs' security by analyzing their susceptibility to LFI attacks and PEM. The proposed research aims to build a LFI bench from scratch allowing maximum control of laser parameters. In addition, a methodology for analysis of the Device Under Attack (DUA) in preparation for LFI is proposed, including frontside/backside decapsulation methods, and visualization of the structure of the DUA. Analysis of attack viability of different targets on the DUA, including One-Time Programmable (OTP) memory, Flash memory and Static Random Access Memory (SRAM) was performed. A realistic attack of a cryptographic algorithm, such as Advanced Encryption Standard (AES) using LFI was conducted. On the other hand, countermeasures to the proposed attack techniques, including decapsulation/RE, LFI and PEM, were discussed. This dissertation provides a summary for the necessary background and experimental setup to study the possibility of LFI and PEM in different DUAs of two different technologies, specifically PIC16F687 and ARM Cortex-M0 LPC1114FN28102. Attacks performed on on-chip peripherals such as Universal Asynchronous Receiver/Transmitter (UART) and debug circuity reveal new vulnerabilities. This research is important for understanding attacks in order to design countermeasures for securing future hardware.

#### Acknowledgements

All my gratitude is due to Allah, first and foremost; and then I would like to express my gratitude to the people who inspired and encouraged me during my PhD research at University of Waterloo. Without their support, this thesis would not have been completed.

I would like to kindly thank the thesis committee Professors Manoj Sachdev, Domenic Forte, Germán Sciaini and Gordon Agnew for peer-reviewing and providing valuable comments on my thesis. Also, I would like to acknowledge Professor Donna Strickland, from the Physics and Astronomy department at the University of Waterloo, for her enormous knowledge and experience related to using lasers, which she shared with us very openly. Her help, support and continuous advice were of crucial importance in operating and upgrading our laser setup. In addition, I'd like to thank KA Imaging Inc. for facilitating X-ray imaging for our research purposes. I'd like to thank all my lab mates and colleagues on their positive impact on getting my PhD degree, namely, Bahar, Brian, Caio, Edgar, Haohao, Mahmoud and Mustafa. Thanks to all my friends near by and far away who kept me believing in myself and in my ability to acquire the PhD degree. I would like to express my deep gratitude and sincere thanks to my supervisor Prof. Catherine Gebotys for her patient guidance and enthusiastic support of this research work. With her insight based on industrial and theoretical background, my research could be guided in the right way. She was always so helpful and inspiring. She always met me with a smile in our regular meetings even through the toughest times and obstacles we faced while conducting the research work. She always tried to make my life easier, provided support whenever needed and gave me confidence in myself. Her sublime attention to detail along with having the bigger picture in mind for our research objectives always inspired me. Without her generous support, this thesis wouldn't have been possible.

Thanks to the University of Waterloo for immersing me in such learning environment through out those many years of my PhD journey. Also, thanks to Professor Serag El-Din Habib, Yehea Ismail, Alaa El-Rouby and Amr Wassal who guided me through my BSc and MSc back in Egypt and taught me how to keep learning, be more productive and develop on the personal level. Moreover, joining the squash varsity team enhanced my attention to detail, time management, consistency and research productivity.

Special thanks to my parents and family. All of my accomplishments through my life have been realized by endless love and support of my mother Mona and sister Mariam. My mother showed me her positive attitude towards life specially through difficult times. Also, I'd like thank also my wife Safy for being supportive. Her love and friendship are great gifts in my life. My love towards my kids, Malik and Adam, supported me during hard times in my PhD journey.

#### Dedication

This PhD thesis is dedicated to my mom Mona.

# **Table of Contents**

| Li            | st of | Figure | es                                                                                              | xii  |

|---------------|-------|--------|-------------------------------------------------------------------------------------------------|------|

| $\mathbf{Li}$ | st of | Tables | 5                                                                                               | xix  |

| Li            | st of | Code   | Listings                                                                                        | xx   |

| Li            | st of | Acron  | ıyms                                                                                            | xxi  |

| 1             | Intr  | oducti | on                                                                                              | 1    |

|               | 1.1   | Motiva | ation                                                                                           | . 2  |

|               | 1.2   | Object | tives $\ldots$ | . 3  |

|               | 1.3   | Thesis | Overview                                                                                        | . 4  |

| <b>2</b>      | Bac   | kgrour | nd                                                                                              | 5    |

|               | 2.1   | Types  | of Attacks                                                                                      | . 5  |

|               |       | 2.1.1  | Non-invasive                                                                                    | . 5  |

|               |       | 2.1.2  | Invasive                                                                                        | . 6  |

|               |       | 2.1.3  | Semi-invasive                                                                                   | . 7  |

|               | 2.2   | Laser  | Theory and Operation                                                                            | . 8  |

|               |       | 2.2.1  | Laser beams - Gaussian TEM                                                                      | . 9  |

|               |       | 2.2.2  | Optics and Laser beam spot size                                                                 | . 12 |

|               |       | 2.2.3  | Laser absorption and fault mechanisms                                                           | . 16 |

|   | 2.3  | Photo  | excitation Effect of Laser on Silicon | 21 |

|---|------|--------|---------------------------------------|----|

|   |      | 2.3.1  | Continuous vs pulsed laser            | 22 |

|   | 2.4  | Tunab  | le Parameters in LFI                  | 22 |

|   |      | 2.4.1  | Frontside                             | 23 |

|   |      | 2.4.2  | Backside                              | 23 |

|   | 2.5  | Summ   | ary                                   | 24 |

| 3 | Lite | rature | Review                                | 25 |

|   | 3.1  | Revers | se Engineering                        | 25 |

|   |      | 3.1.1  | Decapsulation                         | 26 |

|   |      | 3.1.2  | Deprocessing                          | 27 |

|   |      | 3.1.3  | Imaging                               | 27 |

|   |      | 3.1.4  | Stitching and Aligning                | 28 |

|   |      | 3.1.5  | Annotation                            | 28 |

|   |      | 3.1.6  | Verification and schematic creation   | 29 |

|   |      | 3.1.7  | Schematic organization and analysis   | 29 |

|   | 3.2  | Microj | probing                               | 29 |

|   | 3.3  | Fault  | Injection and Laser-based Attacks     | 32 |

|   |      | 3.3.1  | General Fault Injection               | 32 |

|   |      | 3.3.2  | Laser-based Techniques                | 33 |

|   |      | 3.3.3  | Laser Fault Injection                 | 35 |

|   | 3.4  | Summ   | ary                                   | 38 |

| 4 | Res  | earch  | Objectives, Methodology and Setup     | 40 |

|   | 4.1  | Object | tives                                 | 40 |

|   | 4.2  | Metho  | odology                               | 41 |

|   |      | 4.2.1  | General Flow                          | 42 |

|   |      | 4.2.2  | Flow for Decapsulation                | 42 |

|   | 4.3 | Exper   | imental setup                                                              | 44 |

|---|-----|---------|----------------------------------------------------------------------------|----|

|   |     | 4.3.1   | LFI setup                                                                  | 45 |

|   |     | 4.3.2   | PEM setup                                                                  | 51 |

|   |     | 4.3.3   | Sample preparation                                                         | 52 |

|   |     | 4.3.4   | Sample orientation                                                         | 54 |

|   | 4.4 | Device  | es under Attack                                                            | 55 |

|   |     | 4.4.1   | PIC16F687                                                                  | 55 |

|   |     | 4.4.2   | ARM Cortex-M0 LPC1114FN28102                                               | 55 |

|   |     | 4.4.3   | RISC-V                                                                     | 56 |

| 5 | Bos | ulta fo | r MicroChip PIC16F687                                                      | 57 |

| 0 |     |         | -                                                                          |    |

|   | 5.1 |         | side and backside decapsulation trials                                     | 58 |

|   |     | 5.1.1   | Frontside proposed procedure                                               | 59 |

|   |     | 5.1.2   | Backside proposed procedure:                                               | 65 |

|   | 5.2 | Laser   | pulse measurements and characterization                                    | 69 |

|   |     | 5.2.1   | Induced and switching currents                                             | 69 |

|   | 5.3 | Introd  | luction to PIC16F687                                                       | 71 |

|   | 5.4 | Attack  | ss on PIC16F687                                                            | 72 |

|   |     | 5.4.1   | Instruction skip attack                                                    | 73 |

|   |     | 5.4.2   | Instruction replacement attack                                             | 74 |

|   |     | 5.4.3   | Configuration bits attack                                                  | 75 |

|   |     | 5.4.4   | AES-128 key retrieval                                                      | 76 |

|   |     | 5.4.5   | Instruction register PEM analysis                                          | 77 |

|   | 5.5 | Count   | ermeasures                                                                 | 80 |

|   |     | 5.5.1   | Configuration bits factory protection                                      | 80 |

|   |     | 5.5.2   | Encrypted instruction set and dummy structures                             | 81 |

|   |     | 5.5.3   | Thicker substrate to obstruct PEM $\ . \ . \ . \ . \ . \ . \ . \ . \ . \ $ | 81 |

|   |     | 5.5.4   | Hardfault                                                                  | 81 |

|   |     |         |                                                                            |    |

|                           |                      | 5.5.5 Latchup                                   | 31         |

|---------------------------|----------------------|-------------------------------------------------|------------|

|                           |                      | 5.5.6 Bulk current sensor and substrate coating | 31         |

|                           | 5.6                  | Summary and comparison with previous research   | 32         |

| 6                         | $\operatorname{Res}$ | ults for ARM Cortex-M0 LPC1114FN28102 8         | <b>34</b>  |

|                           | 6.1                  | Introduction to ARM Cortex-M0                   | 34         |

|                           | 6.2                  | Attacking procedure                             | 37         |

|                           |                      | 6.2.1 LFI firmware                              | 91         |

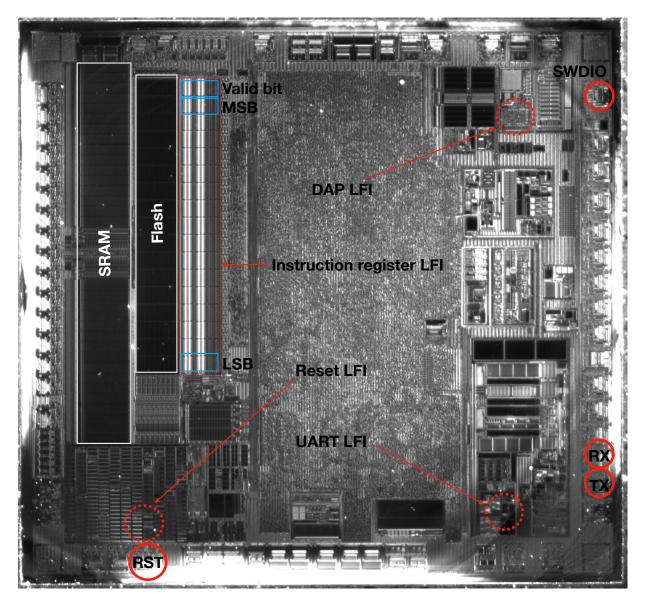

|                           | 6.3                  | Locating Debug Access Port (DAP) circuitry      | 93         |

|                           | 6.4                  | Attacking UART                                  | 99         |

|                           |                      | 6.4.1 Lockup state                              | )1         |

|                           | 6.5                  | Resetting without reset                         | )1         |

|                           | 6.6                  | Instruction manipulation                        | )3         |

|                           | 6.7                  | PEM                                             | )7         |

|                           | 6.8                  | Countermeasures                                 | )8         |

|                           | 6.9                  | Summary and comparison with previous research   | )8         |

| 7                         | Dis                  | ussions, Conclusions and Future Work 11         | .0         |

|                           | 7.1                  | Summary                                         | 0          |

|                           | 7.2                  | Contributions                                   | .1         |

|                           | 7.3                  | Limitations and Future Work                     | 2          |

| Re                        | efere                | nces 11                                         | .5         |

| $\mathbf{A}$              | PPE                  | NDICES 13                                       | 0          |

| $\mathbf{A}_{\mathbf{j}}$ | ppen                 | dix A AlphaNov PDM+ measurements 13             | ; <b>1</b> |

| $\mathbf{A}_{\mathbf{j}}$ | ppen                 | dix B Code snippets 13                          | 4          |

| $\mathbf{A}_{\mathbf{j}}$ | ppen                 | dix C Additional experiments 14                 | .0         |

# List of Figures

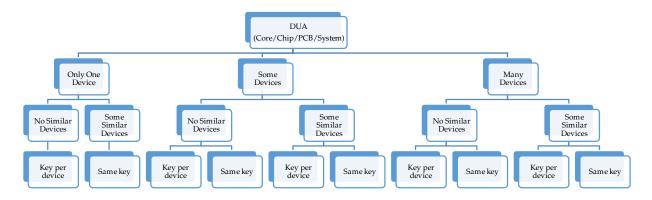

| 1.1 | RE based on chip type                                                                                                                                                                             | 2  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

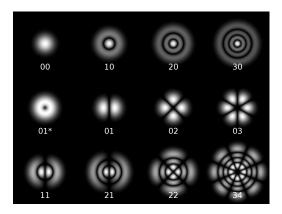

| 2.1 | TEM modes [1]                                                                                                                                                                                     | 9  |

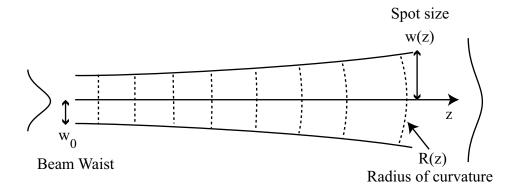

| 2.2 | Illustration of the meaning of $w_o$ , $w(z)$ and $R(z)$ [2]                                                                                                                                      | 10 |

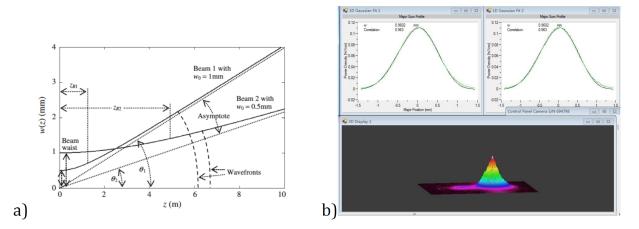

| 2.3 | Half angle divergence and Gaussian beams from [3], notice that values of $w_o$ shown in labels in a) should be reversed and Gaussian beam intensity of laboratory laser in b).                    | 11 |

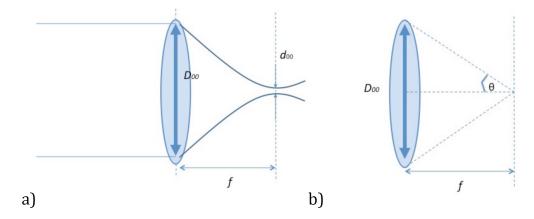

| 2.4 | Focusing with thin lens to small spot size in a) and triangle of thin lens in b).                                                                                                                 | 13 |

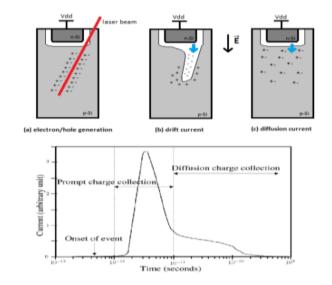

| 2.5 | Laser pulse effect on semiconductor: electron-hole generation a), drift b), diffusion c) and resultant displacement current (below) [4]                                                           | 19 |

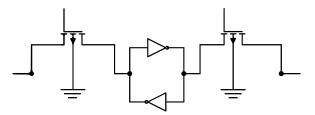

| 2.6 | A typical one-bit SRAM cell.                                                                                                                                                                      | 21 |

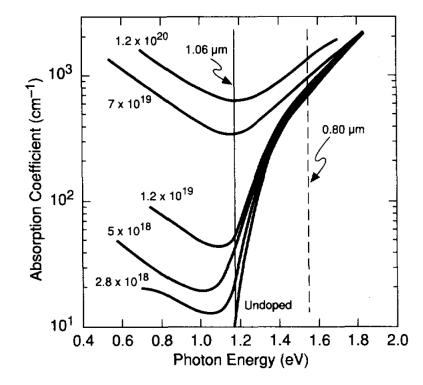

| 2.7 | Absorption coefficient for silicon at various doping levels of a p-type material [5]                                                                                                              | 24 |

| 3.1 | RE flow                                                                                                                                                                                           | 26 |

| 4.1 | Scenarios of DUA (represented by paths through the tree)                                                                                                                                          | 42 |

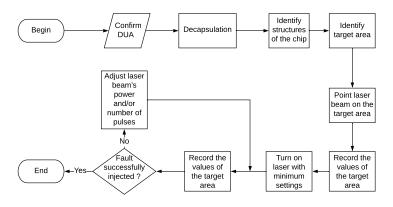

| 4.2 | General flow for LFI                                                                                                                                                                              | 42 |

| 4.3 | Methodology for decapsulation                                                                                                                                                                     | 43 |

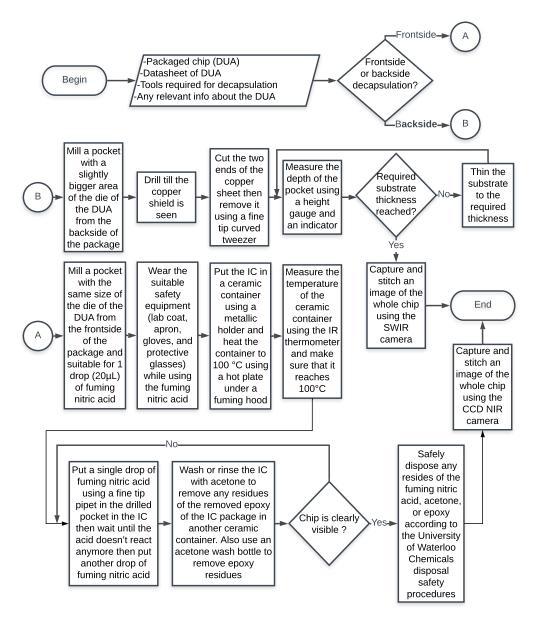

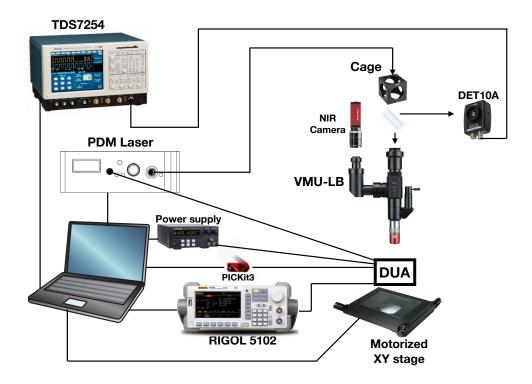

| 4.4 | Experiment setup showing connections between PC and other devices such as XY-stage, RIGOL 5102, power supply, PDM laser, VMU, camera, photo-detector and oscilloscope in order to attack the DUA. | 44 |

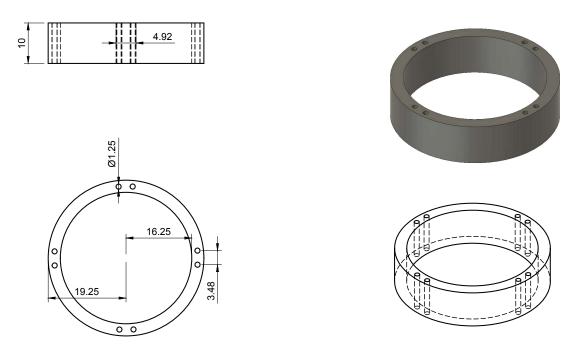

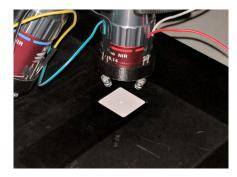

| 4.5 | Infrared (IR) ring mechanical drawing with dimensions in $mm$ . A real picture of the IR ring with the IR light-emitting diodes (LEDs) mounted through it is shown in Figure 5.13.                | 45 |

| 4.6  | Laser spot using the Mitutoyo 5X M Plan Apo NIR objective on a high power IR sensor card                                                                                                                                      |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

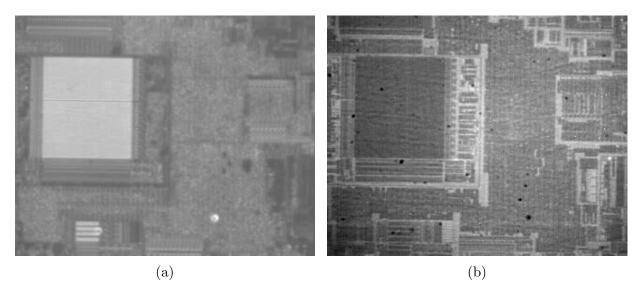

| 4.7  | SWIR image of PIC16F687 under the Mitutoyo setup using a)custom-designed IR Ring and b)MHAB-100W-IR illuminator.                                                                                                              |

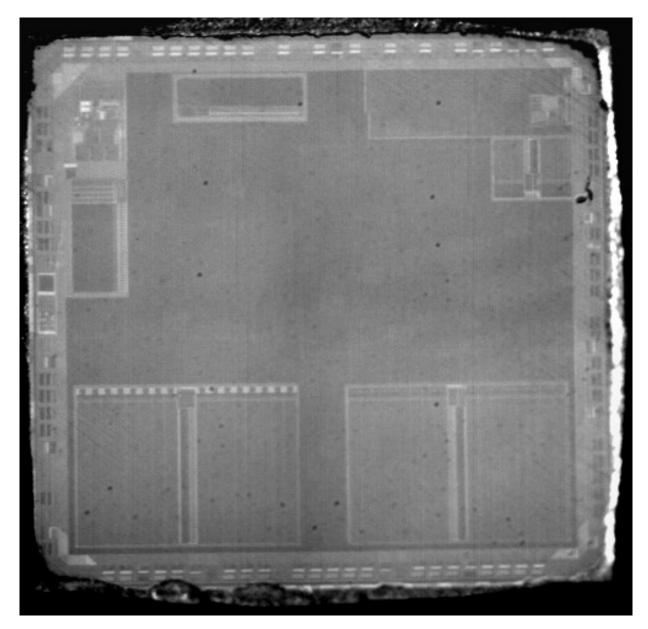

| 4.8  | short-wave Infrared (SWIR) image of the RISC-V backside using the Mito-<br>toyo setup with the MHAB-100W-IR illuminator.                                                                                                      |

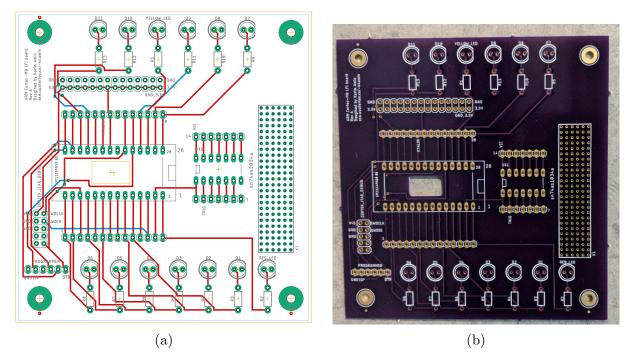

| 4.9  | a) Design of the ARM Cortex-M0 LPC1114FN28102 (ARM Cortex-M0 LPC1114FN28102) Printed circuit board (PCB) layout b) Manufactured PCB                                                                                           |

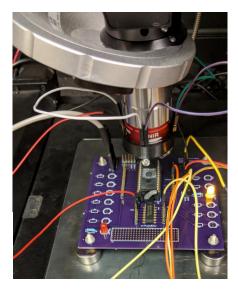

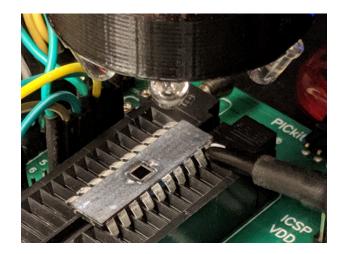

| 4.10 | Soldered PCB with a functional backside decapped ARM LPC1114                                                                                                                                                                  |

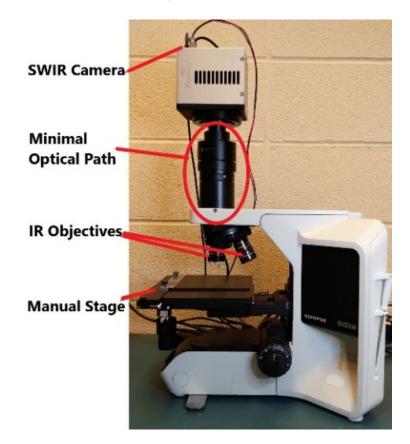

| 4.11 | In house PEM setup [6] consisting of Xenics SWIR camera and Olympus IR optimized microscope and objective lenses.                                                                                                             |

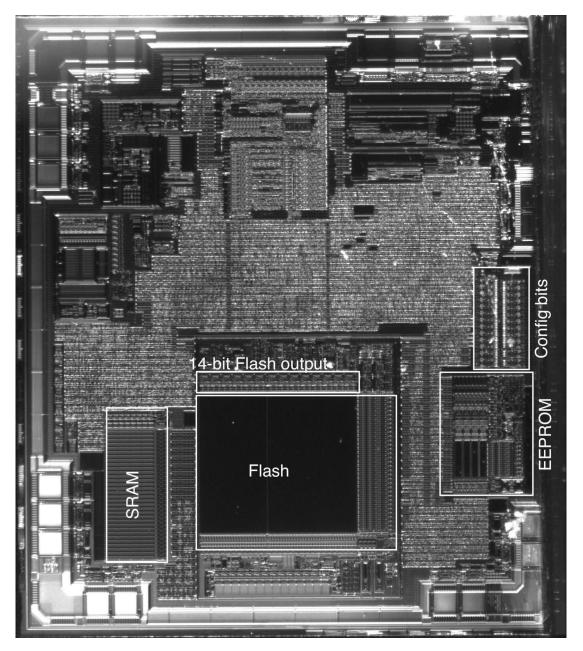

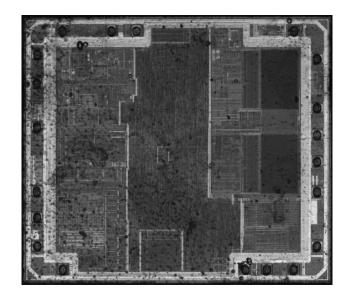

| 4.12 | PIC16F687 backside view captured using the 5X Mitutoyo lens and the NIR camera with different structures identified such as SRAM, Flash, Electrically Erasable Programmable Read-Only Memory (EEPROM) and configuration bits. |

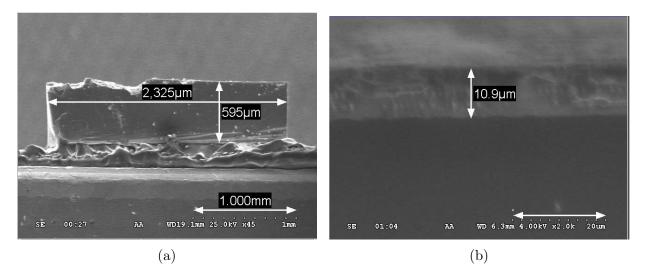

| 4.13 | a) Cross-sectional view of the substrate thickness captured using scanning electron microscope (SEM). b) Active layer thickness is the top part of the die and represents only $\sim 2\%$ of the whole die thickness.         |

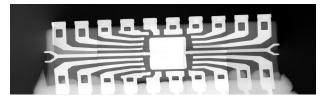

| 4.14 | X-ray stitched image for PIC16F687 Frontside                                                                                                                                                                                  |

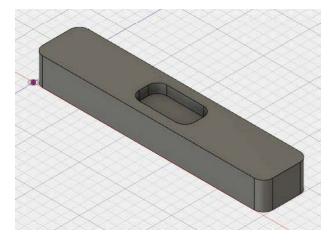

| 5.1  | Chip pocket demonstration.                                                                                                                                                                                                    |

| 5.2  | Pipette used for frontside decap                                                                                                                                                                                              |

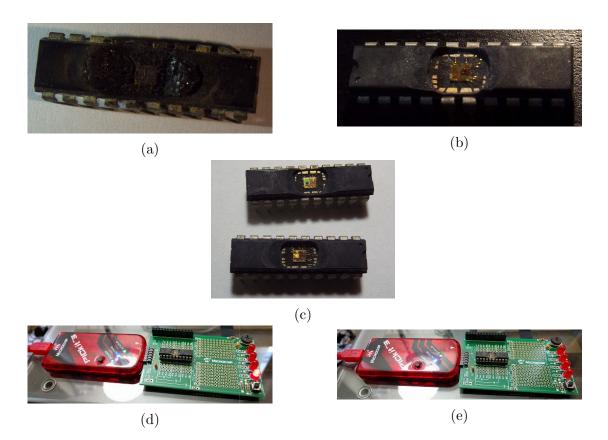

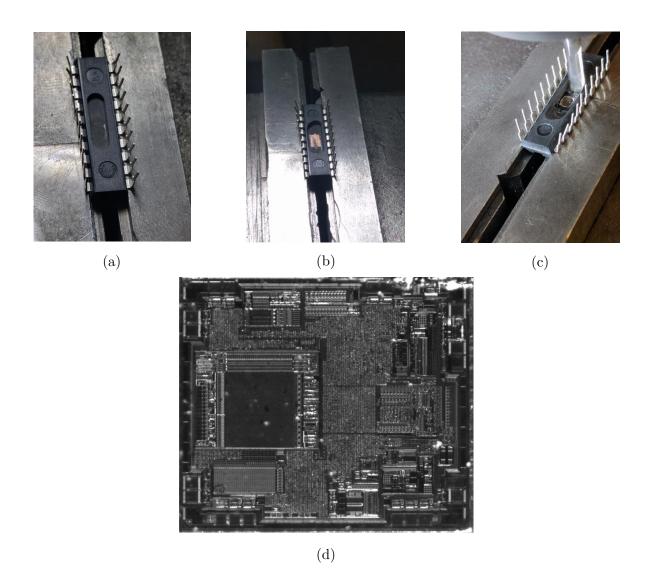

| 5.3  | Unsuccessful frontside decapsulation trial in (a) and successful trials in (b) and (c). One of the samples was programmed and tested as shown in (d) and (e).                                                                 |

| 5.4  |                                                                                                                                                                                                                               |

| 5.5  | Stitched image of the whole frontside decapped PIC16F687 chip                                                                                                                                                                 |

| 5.6  | Frontside decapped PIC16F687 with M Plan APO NIR 5X and 50X objectives.                                                                                                                                                       |

| 5.7  | Clean sample of frontside decapped PIC16F687 with an acetone footprint<br>in the center probably due to high pressure                                                                                                                                                                                                                               |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.8  | Bonding wires of the front side decapsulated PIC16F1827 chip were dissolved during the chemical etching process. Different chemicals may be needed to etch the epoxy without dissolving the bonding wires made of a material other than copper according to [7].                                                                                    |

| 5.9  | Backside decapped chip at different stages (a) before getting to the copper shield, (b) With the copper shield should the attached ends, (c) Without the copper shield and (d) SWIR image of the backside decapped PIC16F687 chip.                                                                                                                  |

| 5.10 | (a) Backside of the decapsulated Spartan-6 Field-Programmable Gate Array (FPGA) and (b) its unaltered frontside.                                                                                                                                                                                                                                    |

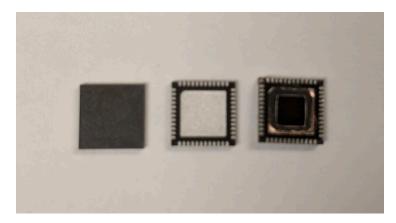

| 5.11 | RISC-V FE310-G002 backside decapsulated chip with both frontside and backside before decapsulation.                                                                                                                                                                                                                                                 |

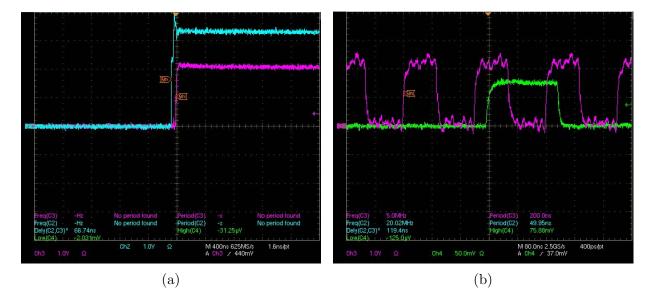

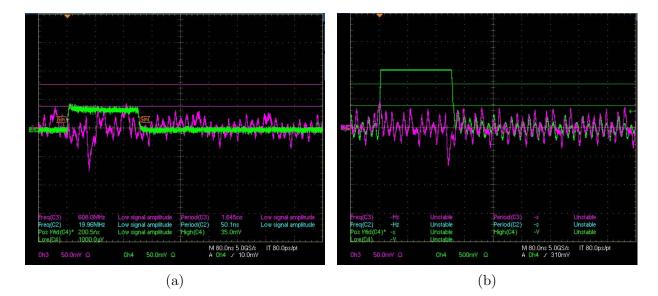

| 5.12 | a) Clock-to-instruction cycle delay and b) Instruction cycle to laser pulse (green) delay with the DUA running @ 20MHz where the instruction frequency is 5MHz $(\frac{f_{osc}}{4})$                                                                                                                                                                |

| 5.13 | Rohde & Schwarz RS H 2.5-2 H-field probe [8] placed on the $V_{DD}$ pin, as shown on the right hand side.                                                                                                                                                                                                                                           |

| 5.14 | a) Induced current (purple) due to laser pulse (green), 200 <i>ns</i> at 50% peak current, where the H-field probe is connected to CH3; and CH4 is connected to avalanche photodiode (APD).b) Switching current (purple) due to triggering of the MCU where the H-field probe is connected to CH3; and CH4 is connected to trigger I/O pin (green). |

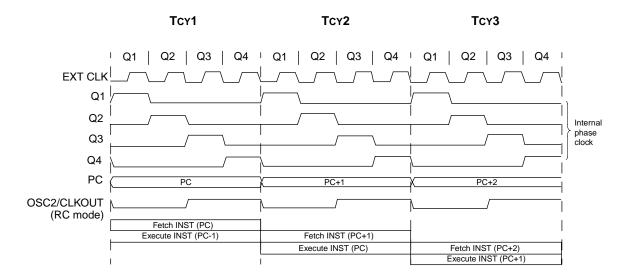

| 5.15 | Fetch and execute timing diagram [9] for the two-stage pipelined DUA where the fetch and execution of instructions overlaps.                                                                                                                                                                                                                        |

| 5.16 | Laser beam spot target location captured using the NIR camera at $1.5\%$ peak current near the instruction register $(I_{reg})$ .                                                                                                                                                                                                                   |

| 5.17 | Laser beam spot target location captured using the NIR camera for a (50ns, $34.625\%$ peak current) near the $I_{reg}$ to alter the immediate value in <i>addlw</i> $0x01.$                                                                                                                                                                         |

| 5.18 | AES-128 internals showing the $1^{st}$ round till the $11^{th}$ round where the $10^{th}$ round check ( <i>decfsz round_counter,f</i> ) is skipped to add an additional $11^{th}$ no-mix-column round.                                                                                                                                              |

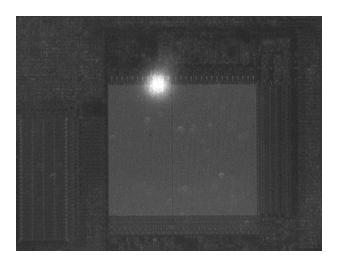

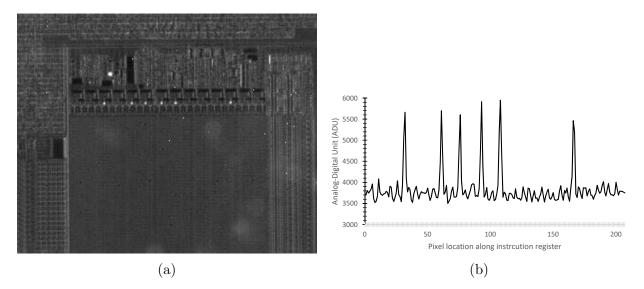

| $(decfsz \ 0x44, f)$ instruction (14-bit instruction word = $0b00101111000100$ )<br>a) $I_{reg}$ emissions and b) ADU graph where the Analog-Digital Unit (ADU)<br>values correspond to the emissions intensity along the $I_{reg}$ .                                                                                                                | 78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $I_{reg}$ emissions for ( <i>incf 0x44,f</i> ) instruction (opcode = 0b00101011000100)<br>at $V_{DD} = 10.5V.$                                                                                                                                                                                                                                       | 79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

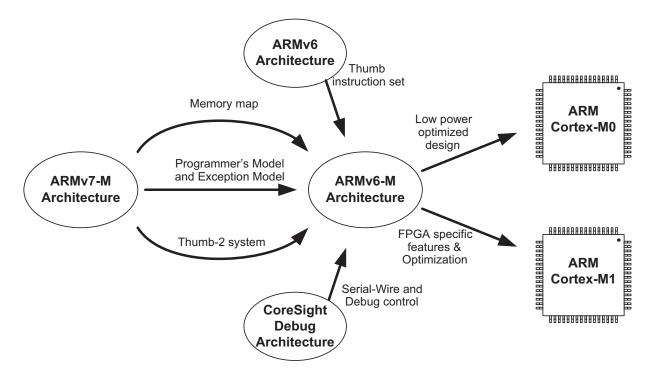

| ARMv6-M inherits attractive features from various ARM architectures [10].                                                                                                                                                                                                                                                                            | 85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

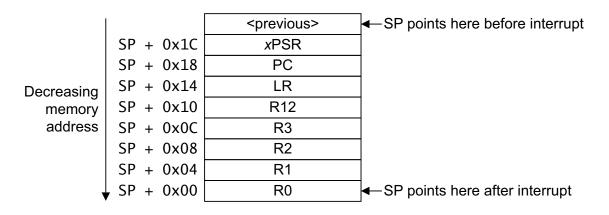

| ARM Cortex-M0 LPC1114 stack frame                                                                                                                                                                                                                                                                                                                    | 86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

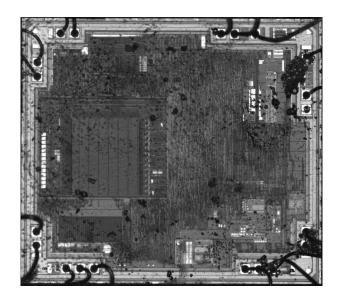

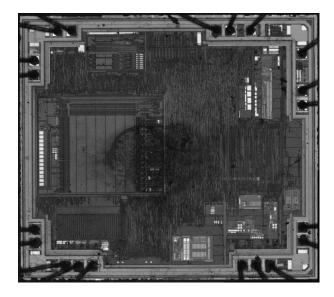

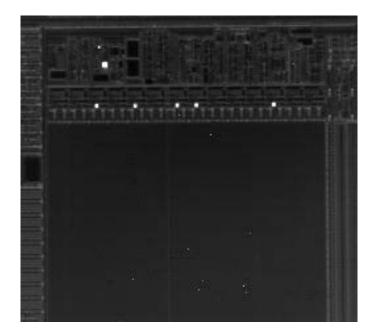

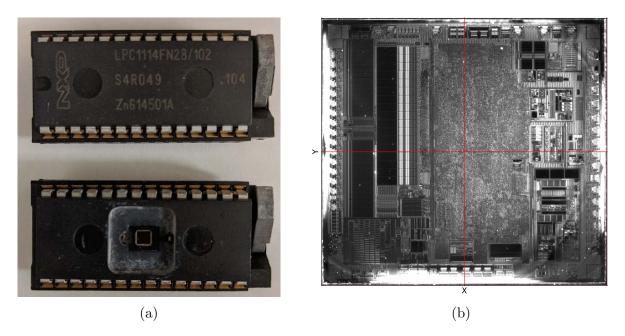

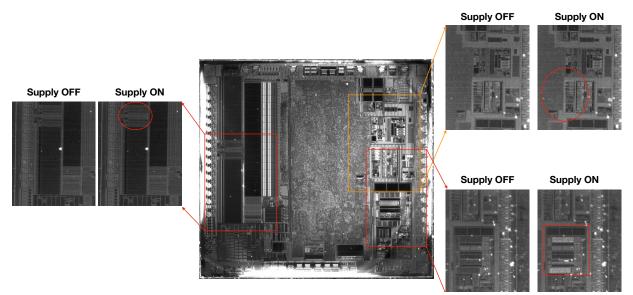

| ARM Cortex-M0 LPC1114FN28 a)backside decapsulated chip and b) backside image using SWIR Olympus.                                                                                                                                                                                                                                                     | 88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

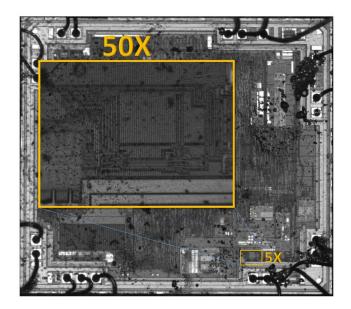

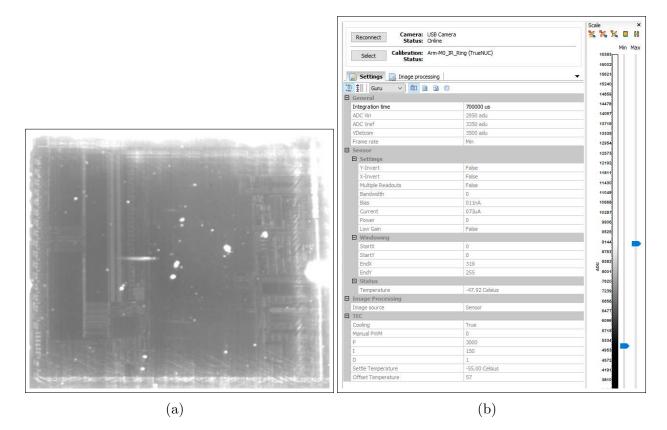

| a) ARM Cortex-M0 LPC1114FN28102 backside image using SWIR camera under Mitutoyo setup and b) Settings for such view                                                                                                                                                                                                                                  | 89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

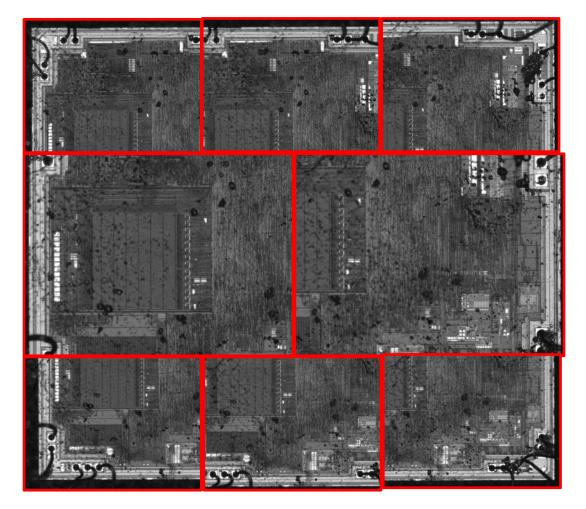

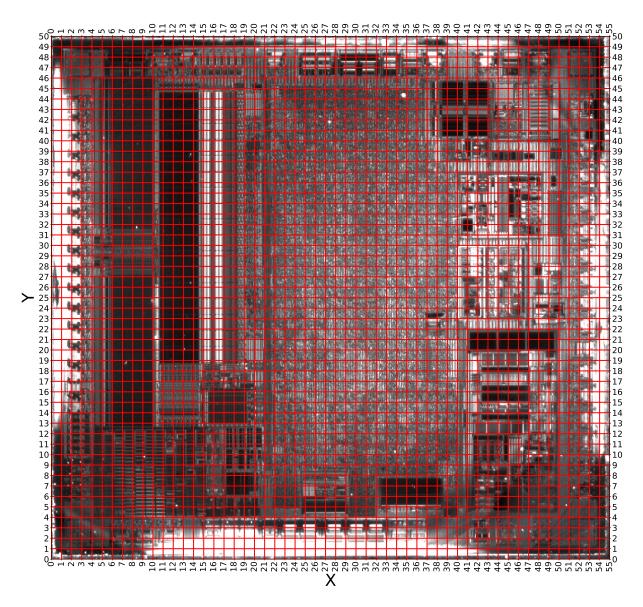

| Superimposed grid on the ARM Cortex-M0 backside captured using SWIR camera under the Olympus setup                                                                                                                                                                                                                                                   | 90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Laser beam spot with 1.75% laser intensity at the bottom left corner of the ARM Cortex-M0 LPC1114FN28102 using a) 5X and b) 50X objectives                                                                                                                                                                                                           | 91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

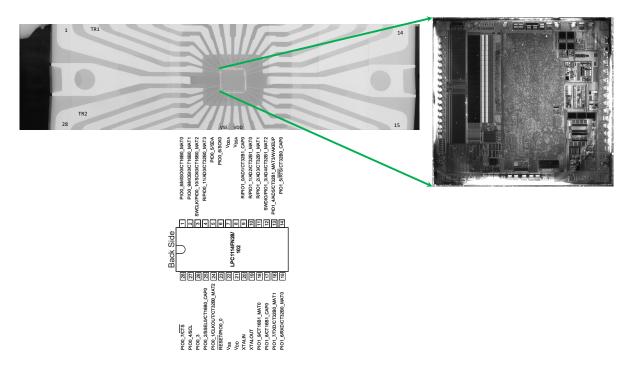

| Pin mapping through X-ray scanning of a backside decapsulated ARM Cortex-M0 LPC1114FN28102 chip. TR1/TR2 are the pins used for trig-<br>gering channels 1/2 of the laser source.                                                                                                                                                                     | 94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

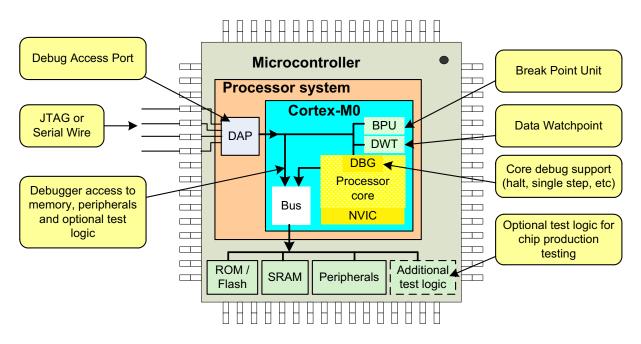

| Debug Access Port (DAP) in ARM Cortex-M0 LPC1114FN28102 [11]                                                                                                                                                                                                                                                                                         | 95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

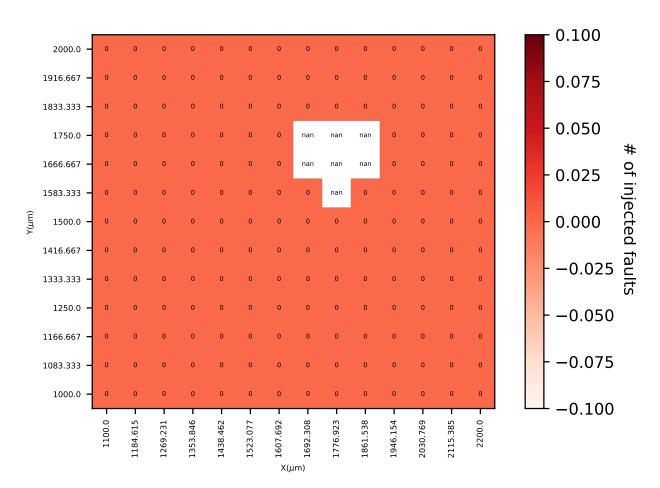

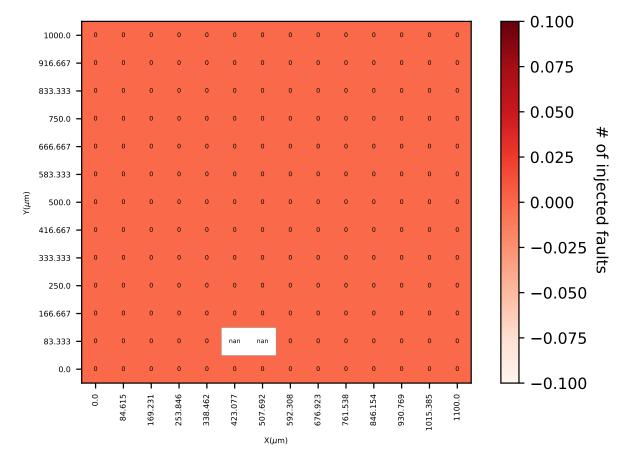

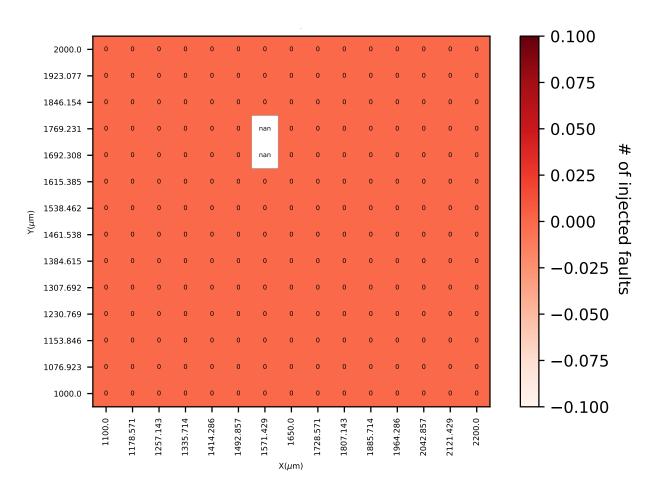

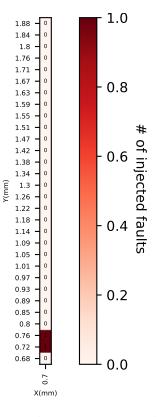

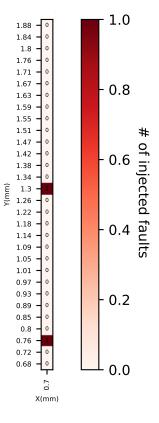

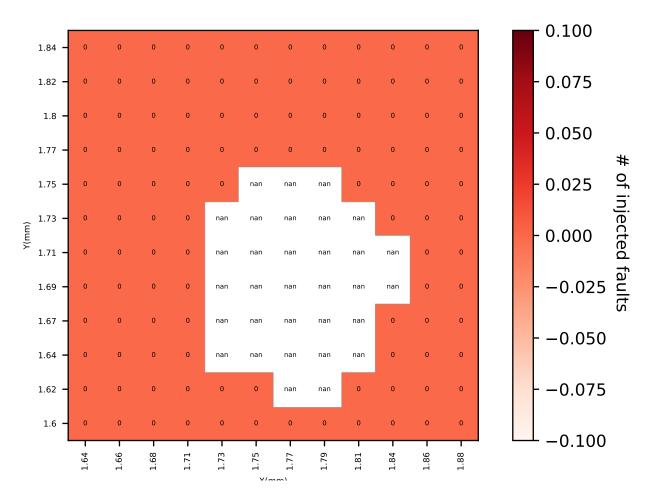

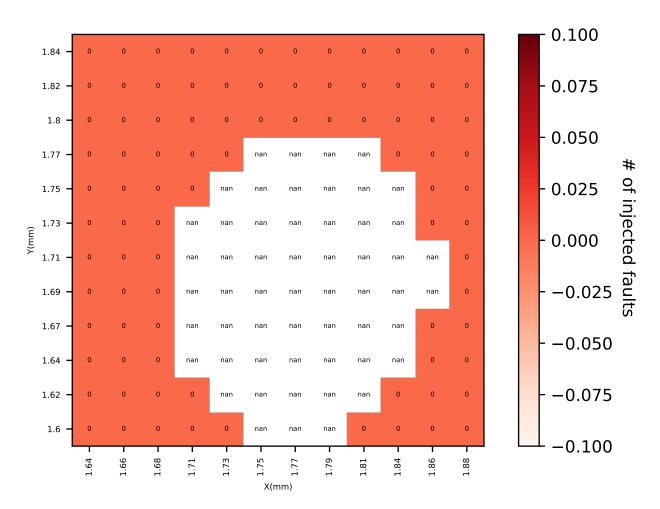

| DAP location in heat map. 5X objective used at 182 locations scanned<br>in the upper right quadrant at 3.3V supply voltage and DUA running at<br>20MHZ and a 200ns laser pulse width at 100.0% of peak current with both<br>PDM CH1 and CH2 enabled. The seven sensitive locations (labelled as<br>Not-A-Number (NaN)) experienced a reset behavior. | 97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Debugger session ended as a result of LFI                                                                                                                                                                                                                                                                                                            | 98                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

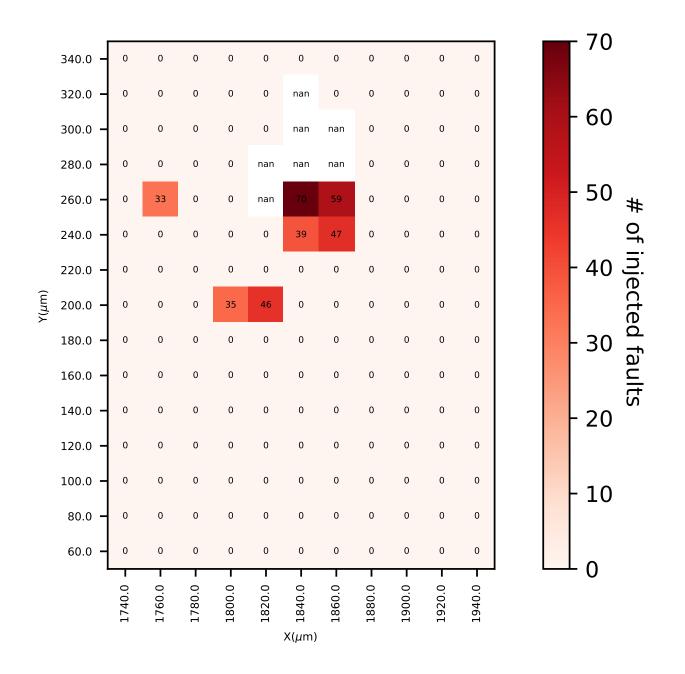

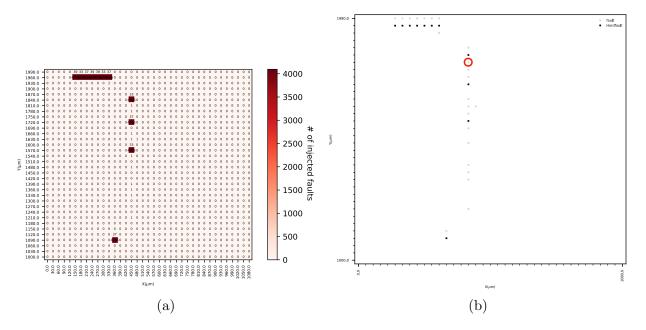

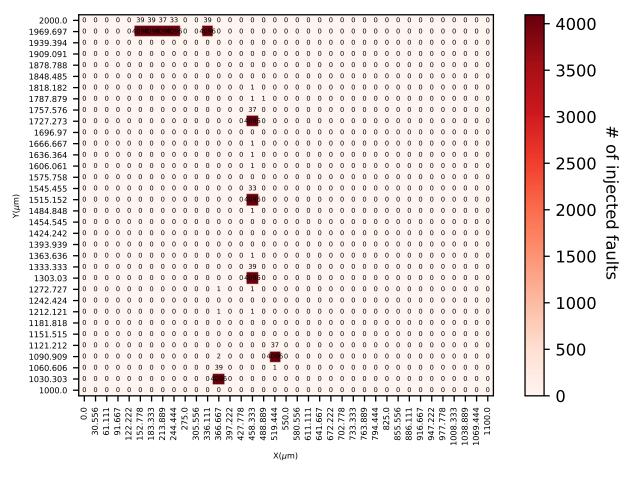

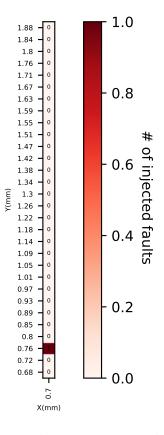

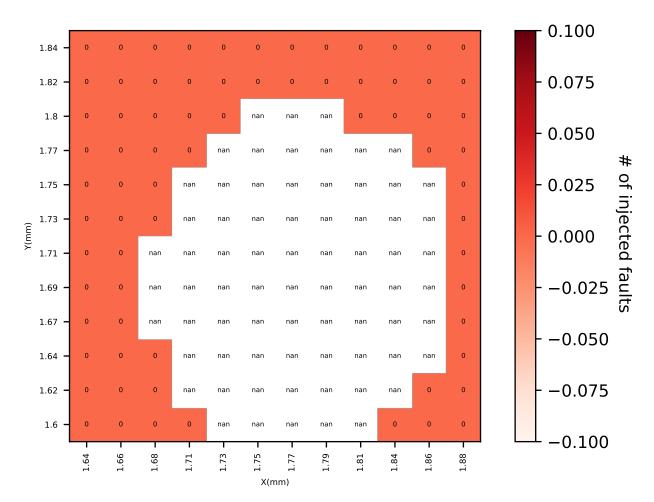

| 5X objective used at 182 locations scanned in a specific area in the bottom right quadrant at 3.3V supply voltage and DUA running at 20MHZ and a 200ns laser pulse width at 100.0% of the peak current with only PDM CH1                                                                                                                             | 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                      | a) $I_{reg}$ emissions and b) ADU graph where the Analog-Digital Unit (ADU) values correspond to the emissions intensity along the $I_{reg}$<br>$I_{reg}$ emissions for ( <i>incf</i> $0x44,f$ ) instruction (opcode = $0b00101011000100$ ) at V <sub>DD</sub> = 10.5V<br>ARMv6-M inherits attractive features from various ARM architectures [10].<br>ARM Cortex-M0 LPC1114 stack frame<br>ARM Cortex-M0 LPC1114FN28 a)backside decapsulated chip and b) back-<br>side image using SWIR Olympus<br>a) ARM Cortex-M0 LPC1114FN28102 backside image using SWIR camera<br>under Mitutoyo setup and b) Settings for such view<br>Superimposed grid on the ARM Cortex-M0 backside captured using SWIR<br>camera under the Olympus setup<br>Laser beam spot with 1.75% laser intensity at the bottom left corner of the<br>ARM Cortex-M0 LPC1114FN28102 using a) 5X and b) 50X objectives<br>Pin mapping through X-ray scanning of a backside decapsulated ARM<br>Cortex-M0 LPC1114FN28102 chip. TR1/TR2 are the pins used for trig-<br>gering channels 1/2 of the laser source<br>Debug Access Port (DAP) in ARM Cortex-M0 LPC1114FN28102 [11]<br>DAP location in heat map. 5X objective used at 182 locations scanned<br>in the upper right quadrant at 3.3V supply voltage and DUA running at<br>20MHZ and a 200ns laser pulse width at 100.0% of peak current with both<br>PDM CH1 and CH2 enabled. The seven sensitive locations (labelled as<br>Not-A-Number (NaN)) experienced a reset behavior<br>5X objective used at 182 locations scanned in a specific area in the bottom<br>right quadrant at 3.3V supply voltage and DUA running at 20MHZ and a 300 specific area in the bottom<br>right quadrant at 3.3V supply voltage and DUA running at 20MHZ and a 300 specific area in the bottom<br>right quadrant at 3.3V supply voltage and DUA running at 20MHZ and a 300 specific area in the bottom<br>right quadrant at 3.3V supply voltage and DUA running at 20MHZ and a 300 specific area in the bottom<br>right quadrant at 3.3V supply voltage and DUA running at 20MHZ and a |

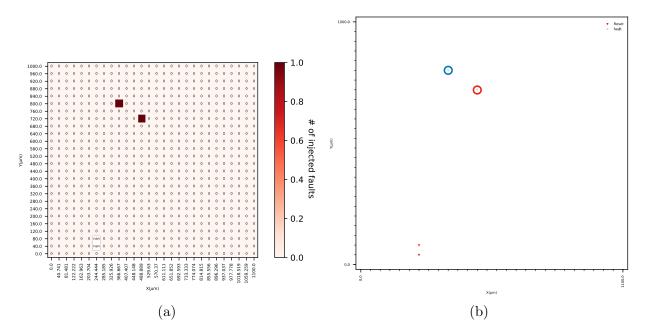

| er<br>ly<br>%<br>vn<br>ng<br>104  |

|-----------------------------------|

| m<br>t-<br>%<br>ur<br>ts<br>. 105 |

| id<br>ne<br>e-<br>ne<br>. 106     |

| of<br>. 107                       |

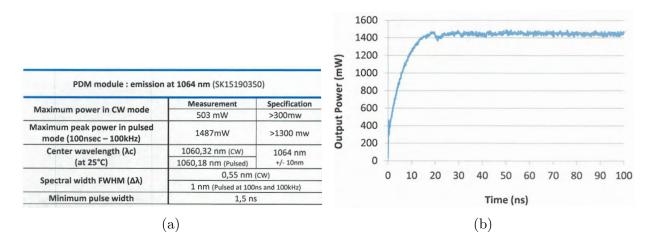

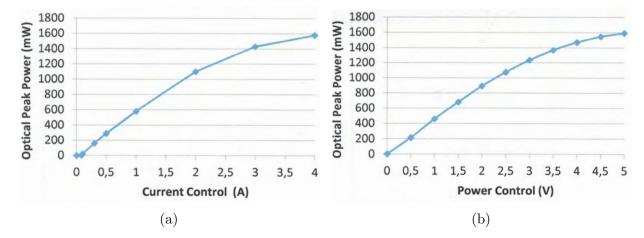

| . 131                             |

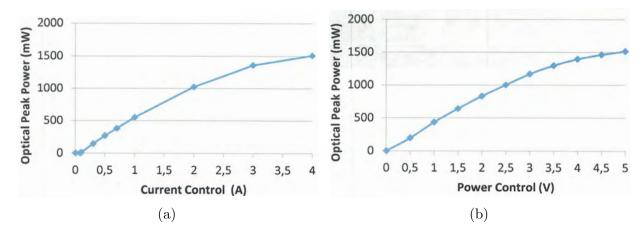

| nt<br>. 132                       |

| . 132                             |

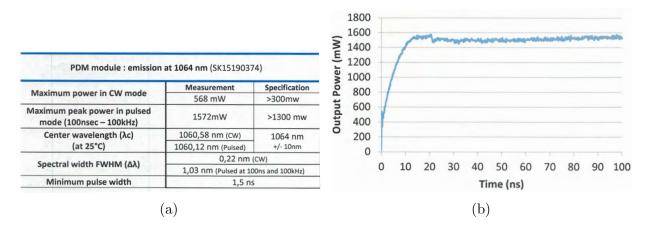

| nt<br>. 133                       |

|                                   |

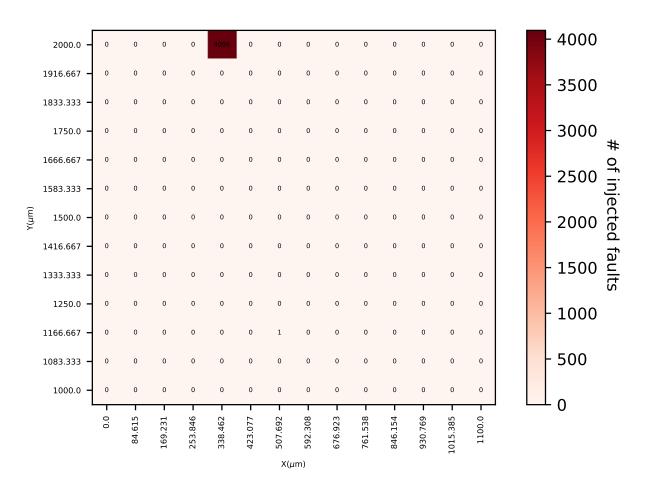

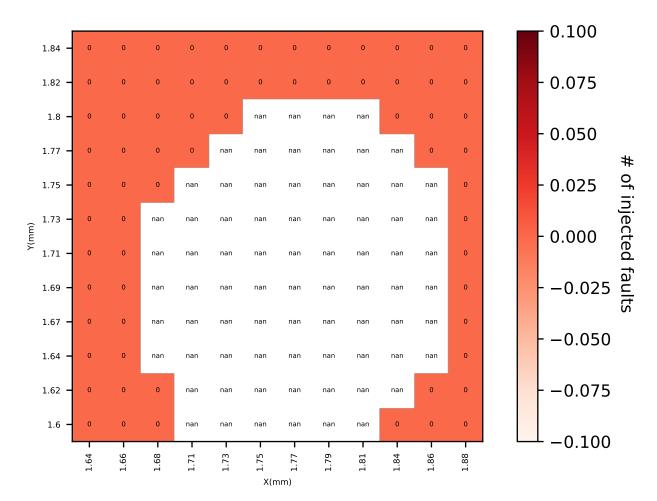

| C.1 | DAP location in heat map. 50X objective used at 210 locations scanned<br>in the upper right quadrant at 3.3V supply voltage and DUA running at<br>20MHZ and a 200ns laser pulse width at 100.0% of peak current with both<br>PDM CH1 and CH2 enabled. Only two sensitive locations (labelled as NaN)<br>experienced a reset behavior. | 141 |

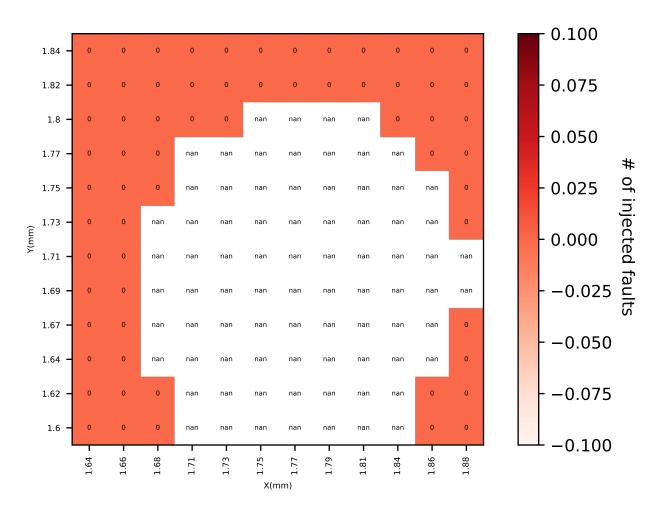

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| C.2 | $50\mathrm{X}$ objective used at 1258 locations scanned in the upper left quadrant at 1.65V supply voltage and DUA running at 20MHZ and a 200ns laser pulse width at 100.0% of peak current with both PDM CH1 and CH2 enabled.                                                                                                        | 142 |

| C.3 | 50X objective used at 182 locations scanned at upper left quadrant at 1.8V supply voltage and DUA running at 20MHZ and a 200ns laser pulse width at 100% of peak current with both PDM CH1 and CH2 enabled. Only a hardfault at the top and a single instruction manipulation fault at the SRAM address 0x10000801.                   | 143 |

| C.4 | 50X objective used at 30 locations scanned at Flash output at 3.3V supply voltage and DUA running at 20MHZ and a 200ns laser pulse width at 100% of peak current with both PDM CH1 and CH2 enabled. Both faults were instruction manipulation faults at the SRAM address 0x10000801                                                   | 144 |

| C.5 | 50X objective used at 30 locations scanned at Flash output at 3.3V supply voltage and DUA running at 20MHZ and a 200ns laser pulse width at 100% of peak current with both PDM CH1 and CH2 enabled. Both faults were instruction manipulation faults at the SRAM address 0x10000801                                                   | 145 |

| C.6 | 50X objective used at 30 locations scanned at Flash output at 3.3V supply voltage and DUA running at 20MHZ and a 200ns laser pulse width at 100% of peak current with both PDM CH1 and CH2 enabled. The fault was an instruction manipulation fault at the SRAM address 0x10000801                                                    | 146 |

| C.7 | 5X objective used at 144 locations scanned in the DAP area at 3.3V supply voltage and DUA running at 20MHZ and a 200ns laser pulse width at 12.5% of peak current with only PDM CH1 enabled.                                                                                                                                          | 147 |

| C.8 | 5X objective used at 144 locations scanned in the DAP area at 3.3V supply voltage and DUA running at 20MHZ and a 200ns laser pulse width at 25% of peak current with only PDM CH1 enabled.                                                                                                                                            | 148 |

| C.9 | 5X objective used at 144 locations scanned in the DAP area at 3.3V supply voltage and DUA running at 20MHZ and a 200ns laser pulse width at 50% of peak current with only PDM CH1 enabled.                                                                                                                                            | 149 |

| C.10 5X objective used at 144 locations scanned in the DAP area at 3.3V supply                                                                        |     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| voltage and DUA running at 20MHZ and a 200ns laser pulse width at $75\%$                                                                              |     |

| of peak current with only PDM CH1 enabled                                                                                                             | 150 |

| C.11 5X objective used at 144 locations scanned in the DAP area at 3.3V supply voltage and DUA running at 20MHZ and a 200ns laser pulse width at 100% |     |

| of peak current with only PDM CH1 enabled                                                                                                             | 151 |

|                                                                                                                                                       |     |

# List of Tables

| 3.1 | Proper etchant for different materials [13]                                                                          | 28 |

|-----|----------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | Some Known Attacks on AES 128 [14]                                                                                   | 33 |

| 3.3 | Frontside and Backside Injection Characteristics according to [14]                                                   | 38 |

| 4.1 | Basic specifications for PIC16F687                                                                                   | 55 |

| 4.2 | Basic specifications for ARM Cortex-M0 LPC1114FN28102                                                                | 56 |

| 4.3 | Basic specifications for RISC-V with probable structures in Figure 4.8. $\ .$ .                                      | 56 |

| 5.1 | PIC pocket dimensions for different DUAs                                                                             | 60 |

| 5.2 | Effect of the laser source peak current on the number of skipped instructions for a 200ns laser pulse width.         | 73 |

| 5.3 | Injecting arbitrary number of clock cycles to reach the end of a certain Q cycle for a desired assembly instruction. | 78 |

# List of Code Listings

| 6.1 | Pseudo-code for ARM Cortex-M0 LPC1114FN28102                   | 92  |

|-----|----------------------------------------------------------------|-----|

| 6.2 | Code for LFI triggering using ARMv6-M instruction set          | 92  |

| B.1 | Different target instructions for ARM Cortex-M0 LPC1114FN28102 | 134 |

| B.2 | Seven consecutive pulses for ARM Cortex-M0 LPC1114FN28102      | 138 |

| B.3 | Stack frame dumping for ARM Cortex-M0 LPC1114FN28102           | 139 |

# List of Acronyms

$I_{reg}$  instruction register

$W_{reg}$  working register

ADU Analog-Digital Unit

**AES** Advanced Encryption Standard

**AHB** Advanced High-Performance Bus

**ALU** Arithmetic Logic Unit

**APD** avalanche photodiode

ASIC Application-Specific Integrated Circuit

BGA Ball Grid Array

CaLIAD calibratable lightweight invasive attack detector

CCD charge-coupled device

**CNC** Computer Numeric Control

**CPA** correlation power analysis

**CPLD** complex programmable logic device

**DAP** Debug Access Port

**DIP** dual in-line package

**DLL** dynamic-link library

DMC Design and manufacturing company

**DND** Department of National Defence

**DOF** Depth of Field

**DUA** Device Under Attack

ECU Electronic Control Unit

**EEPROM** Electrically Erasable Programmable Read-Only Memory

${\bf EM}$  Electro-Magnetic

EMFI electro-magnetic fault injection

**EOFM** electro-optical frequency modulation

**EOP** electro-optical probing

EPROM erasable programmable read only memory

FD-SOI Fully Depleted Silicon on Insulator

**FF** flip-flop

FI Fault Injection

FIB Focused Ion Beam

FinFET fin field-effect transistor

FPGA Field-Programmable Gate Array

${\bf HW}$  hardware

**IC** Integrated Circuit

**IoT** Internet of Things

${\bf IR}~{\rm Infrared}$

IS instruction skip

**ISR** Interrupt Service Routine

JTAG Joint Test Action Group

**KPA** known-plaintext attack

**LAPD** low area probing detector

**LED** light-emitting diode

LFI Laser Fault Injection

LIVA Light Induced Voltage Alteration

LSB Least Significant Bit

${\bf LUT}$  look-up table

**LVP** laser voltage probing

MCU Micro-Controller Unit

**MDK** Microcontroller Development Kit

**MOSFET** Metal-Oxide-Semiconductor Field-Effect Transistor

**MSB** Most Significant Bit

**NA** Numerical Aperture

${\bf NaN}$  Not-A-Number

Nd:YAG Neodymium: Yttrium Aluminum Garnet

Nd:YLF Neodymium: Yttrium Lithium Fluoride

${\bf NIR}\,$  Near Infrared

**NMI** nonmaskable interrupt

$\mathbf{NOP}$  no operation

- $\mathbf{NUV}$  Near Ultraviolet

- **NVIC** Nested Vectored Interrupt Controller

**OBIC** Optical Beam Induced Current

- **OTP** One-Time Programmable

- **PAD** probe attempt detector

PCB Printed circuit board

- **PEA** photon emission analysis

- **PEM** Photo-Emission Microscopy

- **PIN** Personal Identification Number

- PKC public-key cryptography

**PLL** phase-locked loop

- **PUF** physical unclonable function

- QFP Quad Flat Package

- **RE** reverse engineering

- **RISC** reduced instruction set computer

**RO** ring oscillator

- **ROM** read-only memory

- **S-box** substitution box

- ${\bf SCA}\,$  side-channel attack

- SCM scanning capacitance microscope

- **SEE** Single Event Error

- **SEL** Single Event Latch-up

**SEM** scanning electron microscope

**SET** Single Event Transient

**SEU** Single Event Upset

${\bf SOI}$  Silicon on Insulator

**SRAM** Static Random Access Memory

${\bf STI}$  shallow trench isolation

**SWD** Serial Wire Debug

${\bf SWIR}\,$  short-wave Infrared

**TEM** Transverse Electric and Magnetic

**TSOP** Thin Small Outline Package

**UART** Universal Asynchronous Receiver/Transmitter

$\mathbf{UV}$  Ultraviolet

**UV-C** Ultraviolet light in the C spectrum

$\mathbf{VMU}$ Video Microscope Unit

# Chapter 1

## Introduction

The wide integration of embedded devices into almost every aspect in our lives is forcing manufacturers of these devices to design secure products. Contactless credit cards, e-passports, automobiles, etc., are just few examples of the everyday "things" that have embedded electronics built inside. Ensuring the security of such devices is of crucial importance, especially with different types of known popular attacks which can exploit any ignored security gaps to conduct a security breach. For example, various security threats and protection mechanisms in the automotive industry are mentioned in [15]. The implementation of cryptographic algorithms could be attacked on known side channels [16], for example analyzing the device's power which unintentionally leaks secret information during the execution of the security algorithm. Injecting faults in electronic circuits through Electro-Magnetic (EM) waves or laser for example as in [17] and [18] may also leak secret information and thus demands higher levels of physical security. Also, reverse engineering (RE) [19], which is defined as the processes of extracting knowledge or design information from anything man-made and reproducing it or reproducing anything based on the extracted information, is a known methodology in de-assembling electronic circuits. For example, RE may leak details on contents of secure memories or security implementations.

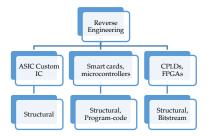

It's worth noting that it's highly likely any embedded system may be reverse engineered with variation in the time consumed, expenses incurred and expertise required to do so. The security measures taken while designing each system determine the costs required for RE that system. Also, advancement in technology leading to reduced size of on-chip transistors and increased device complexity are challenges facing RE. Different classifications have been proposed for the types of the RE processes that can be followed [20]. Some classifications are based on the chip type; for example, as shown in Figure 1.1, Application-Specific Integrated Circuits (ASICs) and custom Integrated Circuits (ICs) require structural RE, smart cards and MCUs need both structural and program-code RE while structural and bit-stream RE are used to deal with complex programmable logic devices (CPLDs) and FPGAs. Structural RE [20] means extracting all the information about the internal structure of a chip such as locations of transistors and interconnections in-between. This process is very tedious, time-consuming and requires a certain level of experience. Program-code RE targets retrieving the memory contents to understand how the device works. Bit-stream RE is based on converting the acquired bit-stream to logic gates and equations that describe the functionality. Companies like *TechInsights* [21] provide structural RE, while *Bottomline* Technologies [22] provides bit-stream RE.

Figure 1.1: RE based on chip type.

RE is becoming a niche area for business since it can be used as a very strong aiding factor to reduce time-to-market because RE basically serves as a method to understand the function of a certain system and provides the ability to replicate a similar or better one.

### 1.1 Motivation