# Broadband Linearity-Enhanced Doherty Power Amplifier Design Techniques for 5G Sub-6 GHz Applications

by

Emile Traore

A thesis

presented to the University of Waterloo

in fulfillment of the

thesis requirement for the degree of

Master of Applied Science

in

Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2021

©Emile Traore 2021

# **AUTHOR'S DECLARATION**

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### **Abstract**

The recently deployed fifth generation (5G) cellular networks represent a significant technological advancement over fourth generation (4G) networks. Specifically, new 5G frequency bands were allocated at sub-6 GHz and instantaneous signal bandwidths were increased to satisfy the rapidly growing need for increased data rates. Furthermore, 5G uses more complex modulation schemes to improve spectrum efficiency. Finally, 5G introduced the massive multiple input multiple output (MIMO) concept, where multiple transceivers are used to direct the signal towards specific users, increasing channel capacity.

Conventional power amplifiers (PAs) are not suitable for 5G applications due to the increased signal and system complexity. For example, while the popular Doherty PA (DPA) technique can efficiently amplify signals with complex modulation schemes, conventional DPAs have narrow bandwidths and poor linearity that preclude their use in 5G systems. This has motivated research into techniques to improve DPA bandwidths and linearity for use in 5G networks.

This work focuses on bandwidth and linearity enhancements for sub-6 GHz DPAs realized using discrete components on a printed circuit board. Bandwidth is improved by using broadband architectures for the DPA output combiner network, the absorption of drain parasitics, and a broadband input matching network design. Linearity is enhanced by a proper drain biasing network design and careful selection of transistor source impedances. A 3.3-5.0 GHz DPA using these techniques is fabricated using Cree gallium nitride high electron mobility transistors on a Rogers RO4003C substrate. Measurements indicate 7.8–9.7 dB gain, 38.0–39.2 dBm output power, and drain efficiencies of 48.4– 67.1% (saturation) and 38.6–45.1% (6 dB output back-off) over the bandwidth, with good agreement between simulation and measurement results. Under wideband modulated signal excitation, the DPA offers very good linearity, ranging from -51 to -54 dBc at 100 MHz bandwidth and -50 to -52 dBc at 200 MHz bandwidth, with an appropriate digital pre-distortion (DPD) algorithm and number of coefficients. A 2×2 DPA array is evaluated in a fully digital MIMO setup using a 2×2 antenna array with variable spacing to test various antenna crosstalk levels. The DPA array achieves excellent linearity characteristics under 100 MHz bandwidth signals and use of dual-input single-output DPD, with an adjacent channel power ratio below -48 dBc for all antenna coupling levels tested. The DPA remains the ideal choice in 5G MIMO systems when compared to a 2×2 class AB PA array since it can maintain a higher average drain efficiency and similar linearity.

# Acknowledgements

I would like to thank my supervisor Professor Slim Boumaiza for his mentorship and support during the past two years. He was instrumental in shaping the direction of my research and led me to gain an entirely new perspective on the design of high-power radio frequency and microwave circuits. He motivated me to surpass myself and accomplish tasks that I never thought I would be capable of and truly made me feel like a valuable member of the EmRG research group.

I would also like to thank all other members of the EmRG research group for technical and moral support during the most trying times of the research process, and for the enlightening and lively discussions we have had during the successful times. In particular, I would like to thank Dr. Jingjing Xia who helped review my designs and provided technical assistance with the equipment, Mohammed Almoneer who assisted me with the modulated signal testbed and digital pre-distortion code, and Hang Yu for being a dependable and cooperative colleague who double-checked all my work inside and outside the lab.

This work would not have been possible without the support from industry and research partners: Keysight for providing the Advanced Design System software and suite of test equipment that were instrumental for accomplishing the work in the EmRG group, Ericsson for contributing financially to the EmRG sub-6 GHz project, and NSERC for funding my research through the CGS M scholarship.

Finally, I would like to extend my thanks to Professors Derek Wright and Peter Levine for reviewing my thesis, and to all the staff at the University of Waterloo who kept the university running and guaranteed students' safety during the COVID-19 pandemic. Without you, this work would not have seen the light of day.

# **Table of Contents**

| AUTHOR'S DECLARATION                                             | ii  |

|------------------------------------------------------------------|-----|

| Abstract                                                         | iii |

| Acknowledgements                                                 | iv  |

| Table of Contents                                                | v   |

| List of Figures                                                  | Vii |

| List of Tables.                                                  | X   |

| Chapter 1 Introduction                                           | 1   |

| 1.1 Motivation                                                   | 1   |

| 1.2 Problem Statement                                            | 2   |

| 1.3 Thesis Organization                                          | 3   |

| Chapter 2 High Power Amplifier Review                            | 5   |

| 2.1 Power Amplifier Basics                                       | 5   |

| 2.1.1 Fundamental Power Amplifier Concepts                       | 5   |

| 2.1.2 Ideal Transistor Model                                     | 7   |

| 2.1.3 Transistor Technologies                                    | 8   |

| 2.2 Power Amplifier Classes                                      | 9   |

| 2.2.1 Class A                                                    | 9   |

| 2.2.2 Reduced Conduction Angle Classes                           | 10  |

| 2.2.3 High Efficiency Classes.                                   | 13  |

| 2.2.4 Broadband Classes                                          | 15  |

| 2.3 Output Back-off Efficiency Enhancement Techniques            | 17  |

| 2.3.1 EER and ET Power Amplifiers                                | 18  |

| 2.3.2 Outphasing Power Amplifiers                                | 19  |

| 2.3.3 Doherty Power Amplifiers                                   | 21  |

| 2.4 Practical DPA Design Challenges                              | 25  |

| 2.4.1 Main and Auxiliary Device Biasing                          | 25  |

| 2.4.2 Device Capacitances and Package Parasitics                 | 26  |

| 2.4.3 Knee Region Effects                                        | 28  |

| 2.5 Literature Review of Sub-6 GHz Broadband High-Frequency DPAs | 29  |

| 2.5.1 Broadband DPAs                                             | 29  |

| 2.5.2 Multi-band DPAs                                            | 34  |

| 2.5.3 DPA-like Architectures                              | 35 |

|-----------------------------------------------------------|----|

| 2.5.4 Literature Review Conclusions                       | 36 |

| Chapter 3 3.3–5.0 GHz Linearity-Enhanced DPA Design       | 37 |

| 3.1 Design Specifications                                 | 37 |

| 3.2 Design Strategy                                       | 38 |

| 3.3 Transistor Characterization                           | 38 |

| 3.3.1 DC Characterization                                 | 38 |

| 3.3.2 Stability Characterization                          | 39 |

| 3.3.3 Load Pull Characterization.                         | 41 |

| 3.4 Biasing Network Design                                | 42 |

| 3.5 Output Combiner Network Design                        | 44 |

| 3.5.1 Output Combiner Network Bandwidth Study             | 44 |

| 3.5.2 Output Combiner Network Realization                 | 47 |

| 3.6 Input Section Design                                  | 49 |

| 3.6.1 Source Impedance Selection                          | 49 |

| 3.6.2 Input Matching Network Realization                  | 52 |

| 3.6.3 Input Power Divider Design.                         | 54 |

| 3.7 Full DPA Simulation Results                           | 56 |

| Chapter 4 3.3–5.0 GHz Linearity-Enhanced DPA Measurements | 65 |

| 4.1 Single DPA Measurements                               | 65 |

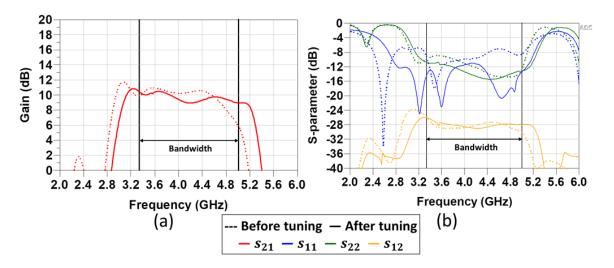

| 4.1.1 S-parameter Measurements                            | 65 |

| 4.1.2 Continuous-Wave Measurements                        | 67 |

| 4.1.3 Modulated Signal Measurements                       | 70 |

| 4.2 2×2 DPA Array Measurements                            | 74 |

| 4.2.1 2×2 Array Test Setup Description                    | 74 |

| 4.2.2 2×2 Array Measurement Results                       | 77 |

| Chapter 5 Conclusions and Future Work                     | 81 |

| 5.1 Conclusions                                           | 81 |

| 5.2 Future Work                                           | 82 |

| Pibliography                                              | 21 |

# **List of Figures**

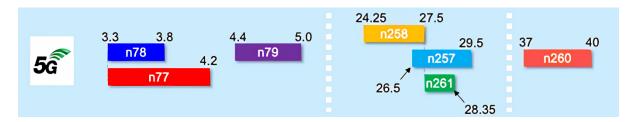

| Figure 1.1 Spectrum of 5G frequency bands at sub-6 GHz and millimeter-wave (above 24 GHz)2                                     |

|--------------------------------------------------------------------------------------------------------------------------------|

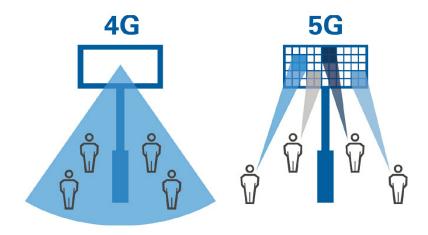

| Figure 1.2 Comparison of 4G (no beamforming) and 5G (MIMO beamforming)2                                                        |

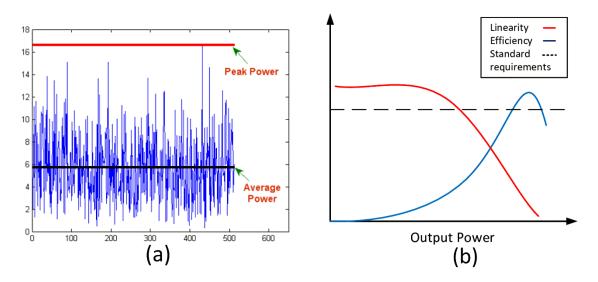

| Figure 1.3 a) Peak and average powers of a signal, b) PA linearity-efficiency trade-off3                                       |

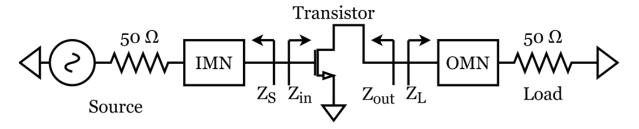

| Figure 2.1 Basic schematic of an RF PA                                                                                         |

| Figure 2.2 Output spectra of a nonlinear PA                                                                                    |

| Figure 2.3 Simplified model of a transistor in the common-source configuration                                                 |

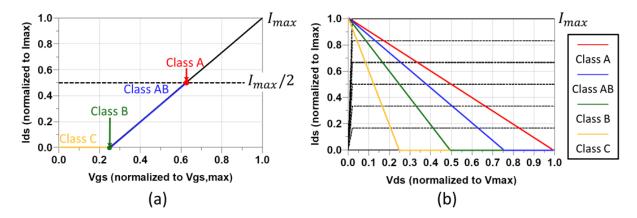

| Figure 2.4 Transistor: a) $V_{gs}$ to $I_{ds}$ transfer characteristic, b) $V_{ds}$ vs. $I_{ds}$ at various $V_{gs}$           |

| Figure 2.5 Optimum transistor technology vs. frequency and output power range9                                                 |

| Figure 2.6 PA class A, AB, B, C: a) Biasing point, b) Load line                                                                |

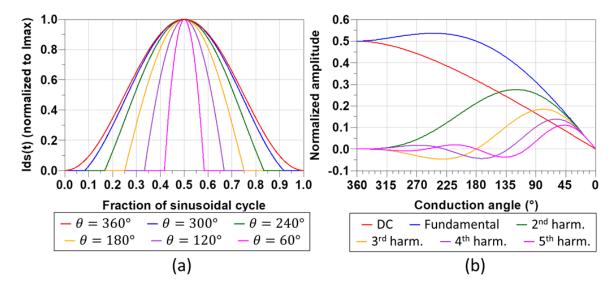

| Figure 2.7 a) $I_{ds}$ waveforms vs. conduction angle, b) $I_{ds}$ harmonic amplitudes vs. conduction angle 12                 |

| Figure 2.8 a) $\eta_D$ vs. $P_{out}$ at various conduction angles, b) $P_{out}$ vs. $P_{in}$ at various conduction angles 13   |

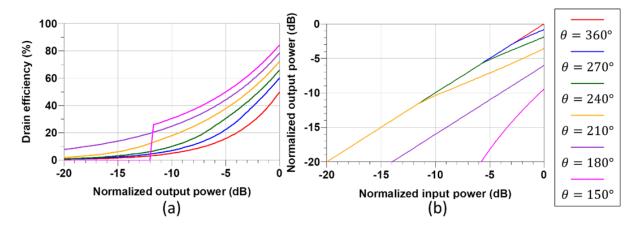

| Figure 2.9 $I_{ds}(t)$ and $V_{ds}(t)$ waveforms vs. number of harmonics for: a) Class F, b) Class F <sup>-1</sup> 15          |

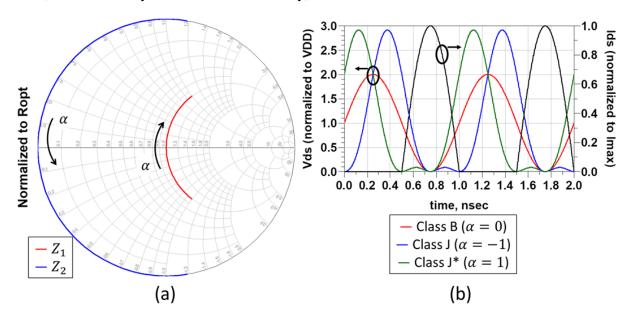

| Figure 2.10 Continuous class B/J/J*: a) $Z_1$ and $Z_2$ vs. frequency, b) $I_{ds}(t)$ and $V_{ds}(t)$ for various $\alpha$ 17  |

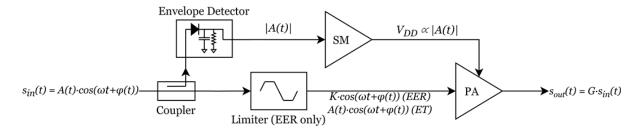

| Figure 2.11 Block diagram of a supply-modulated PA (EER/ET)                                                                    |

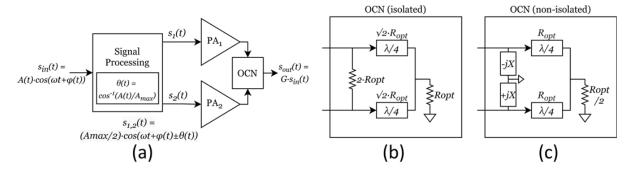

| Figure 2.12 Block diagrams of an: a) Outphasing PA, b) Isolated OCN, c) Non-isolated OCN20                                     |

| Figure 2.13 Chireix outphasing PA load modulation and efficiency profiles at various OBO levels21                              |

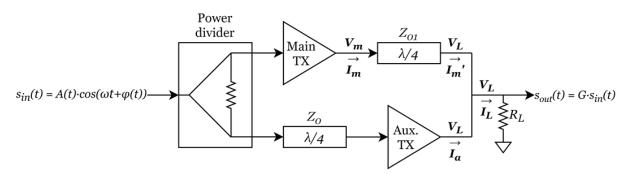

| Figure 2.14 Block diagram of a conventional DPA                                                                                |

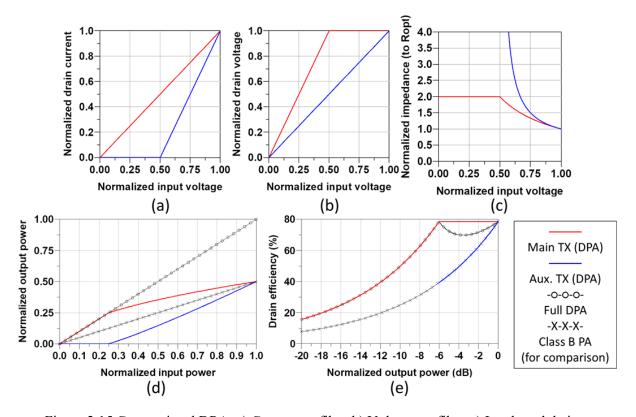

| Figure 2.15 Conventional DPA current/voltage profiles, load modulation, power/efficiency profiles 24                           |

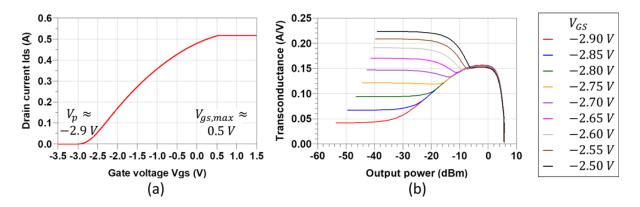

| Figure 2.16 CGHV1F006 transistor: a) $I_{ds}$ vs. $V_{gs}$ transfer characteristic, $g_m$ vs. $P_{out}$ at various $V_{gs}$ 26 |

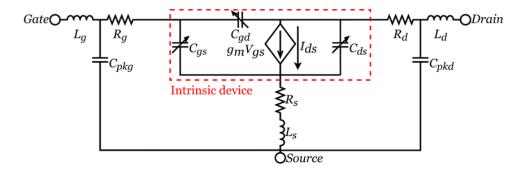

| Figure 2.17 RF transistor equivalent circuit model                                                                             |

| Figure 2.18 CGHV1F006 transistor intrinsic capacitances: a) $C_{gs}$ vs. $V_{gs}$ , b) $C_{ds}$ and $C_{gs}$ vs. $V_{gs}$ 28   |

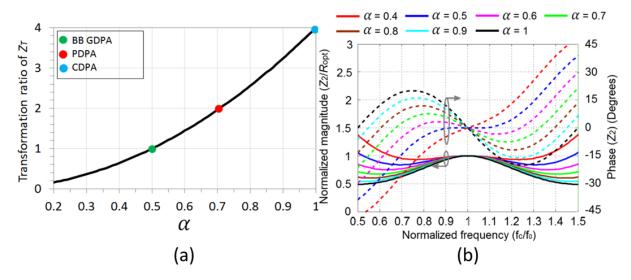

| Figure 2.19 Inverted DPA ITR, $\alpha$ , and bandwidth: a) ITR vs. $\alpha$ , b) Bandwidth vs. $\alpha$ 31                     |

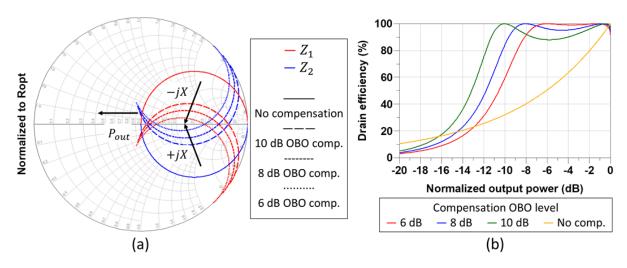

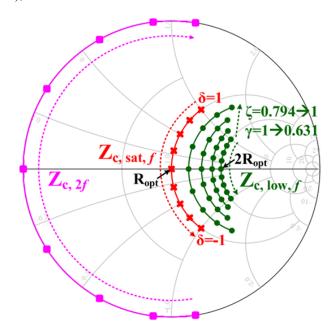

| Figure 2.20 Continuous class J/J* DPA main transistor impedances at OBO and saturation33                                       |

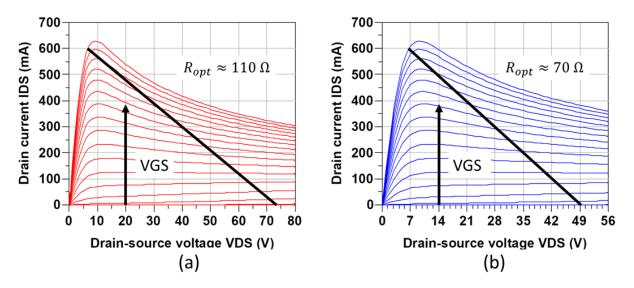

| Figure 3.1 CGHV1F006 transistor load line and $R_{opt}$ for: a) $V_{DD} = 40 V$ , b) $V_{DD} = 28 V$ 39                        |

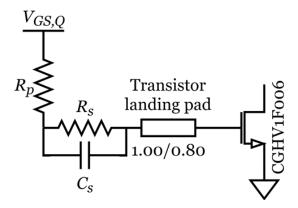

| Figure 3.2 CGHV1F006 transistor stabilization circuit                                                                          |

| Figure 3.3 CGHV1F006 transistor: a) Stability factor/MAG, b) Load and source stability circles40                               |

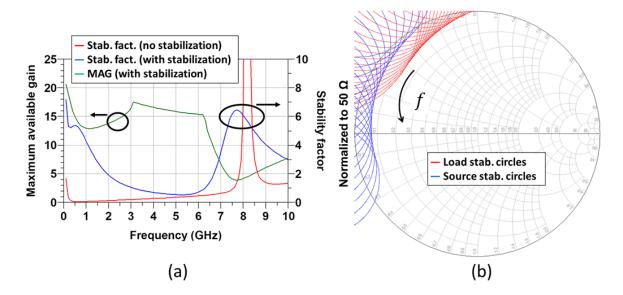

| Figure 3.4 CGHV1F006 transistor drain parasitic network                                                                        |

| Figure 3.5 CGHV1F006 transistor class AB load pull: a) $R_{opt}$ vs. $P_{out}$ , b) $C_{ds}$ vs. $P_{out}$ 42                  |

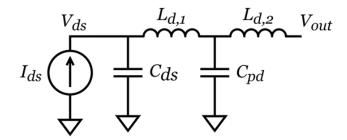

| Figure 3.6 CGHV1F006 transistor: a) Drain BN, b) Gate BN, c) Baseband impedance                                                |

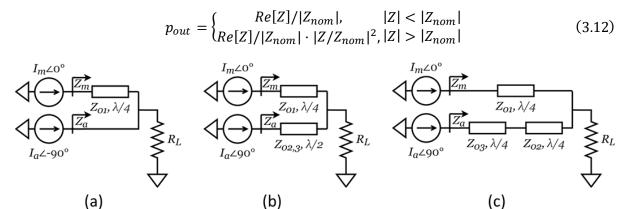

| Figure 3.7 DPA OCN topologies: a) Conventional, b) Inverted ( $\alpha = 1$ ), c) Inverted (arbitrary $\alpha$ ) 45             |

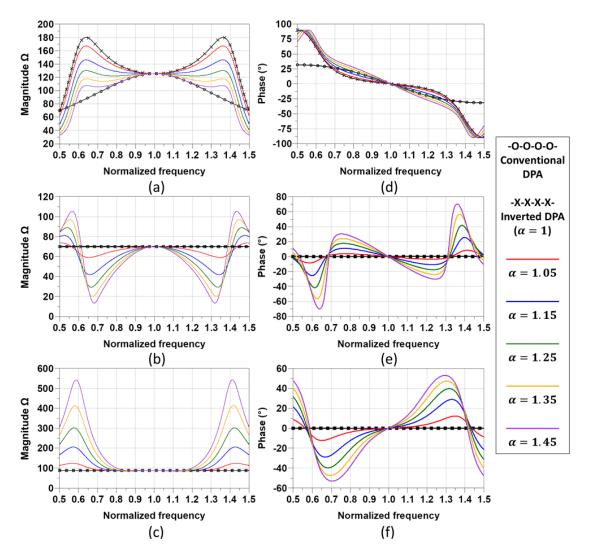

| Figure 3.8 DPA OCN realized impedances vs. normalized frequency                                          | 46   |

|----------------------------------------------------------------------------------------------------------|------|

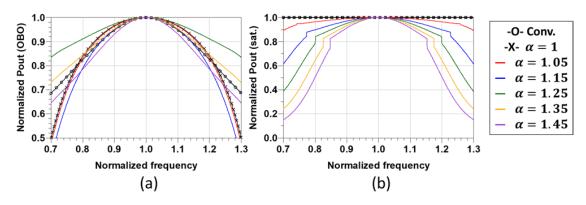

| Figure 3.9 DPA OCN normalized $P_{out}$ vs. normalized frequency at: a) OBO, b) $P_{sat}$                | 46   |

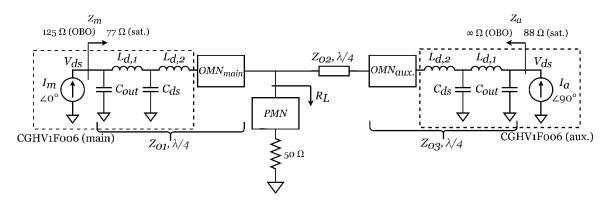

| Figure 3.10 DPA OCN topology                                                                             | 48   |

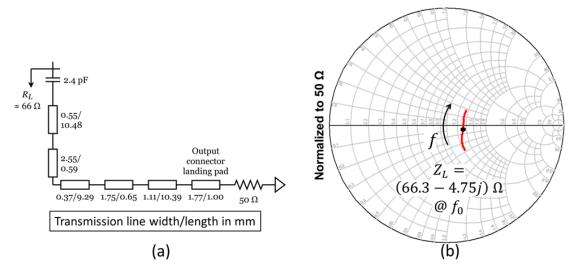

| Figure 3.11 a) PMN schematic, b) Realized PMN load impedance $Z_L$                                       | 48   |

| Figure 3.12 OCN schematic                                                                                | 49   |

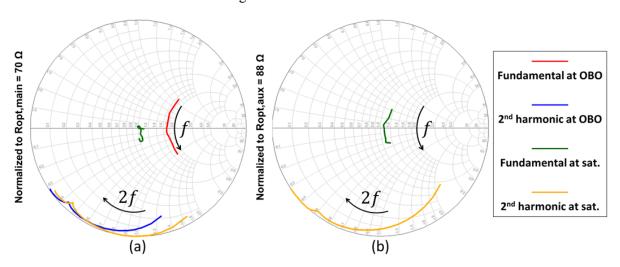

| Figure 3.13 Realized PMN transistor impedances at fundamental and second harmonic                        | 49   |

| Figure 3.14 Schematic used to determine $Z_{s,m}$ and $Z_{s,a}$                                          | 51   |

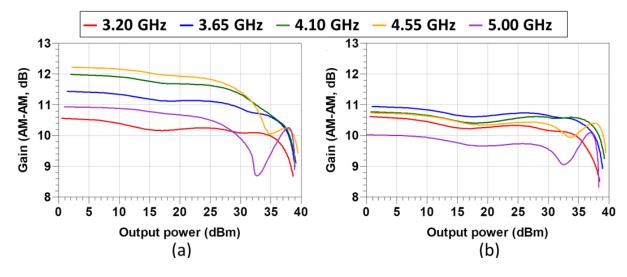

| Figure 3.15 DPA AM-AM: a) With initial $Z_{s,m}/Z_{s,a}$ , b) With optimized $Z_{s,m}/Z_{s,a}$           | 51   |

| Figure 3.16 DPA AM-PM: a) With initial $Z_{s,m}/Z_{s,a}$ , b) With optimized $Z_{s,m}/Z_{s,a}$           | 52   |

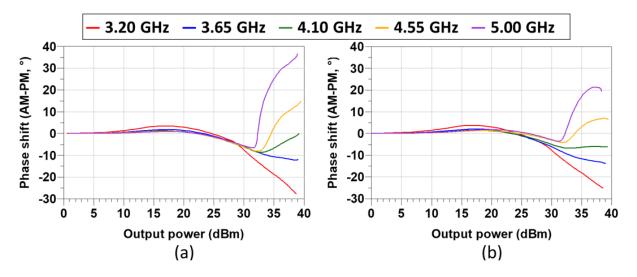

| Figure 3.17 DPA load modulation: a) With initial $Z_{s,m}/Z_{s,a}$ , b) With optimized $Z_{s,m}/Z_{s,a}$ | 52   |

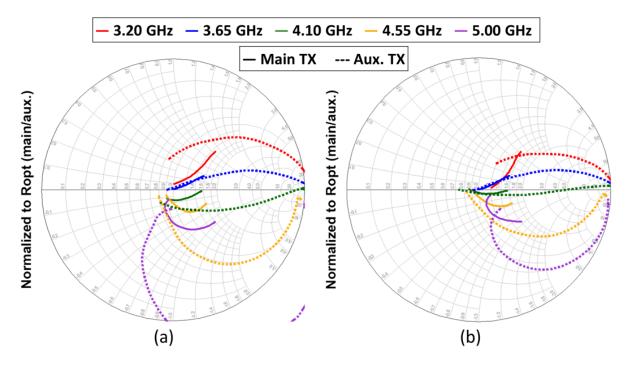

| Figure 3.18 IMN schematic for: a) Main transistor, b) Auxiliary transistor                               | 53   |

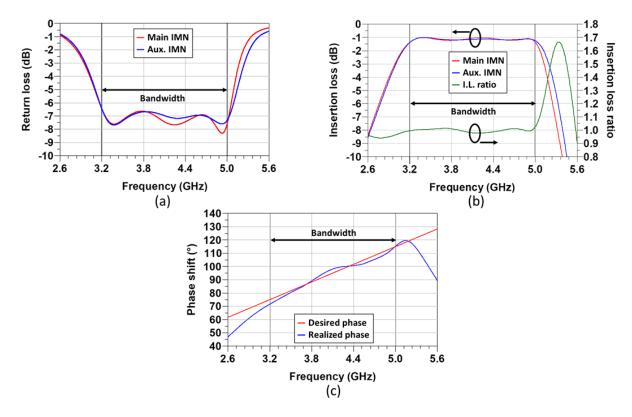

| Figure 3.19 IMN performance: a) Return loss, b) Insertion loss, c) Phase relationship                    | 54   |

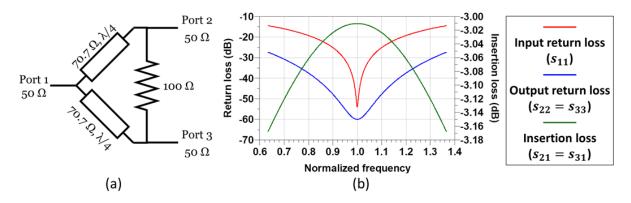

| Figure 3.20 Symmetric Wilkinson power divider: a) Schematic, b) S-parameters                             | 55   |

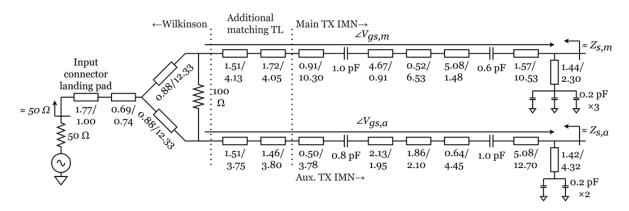

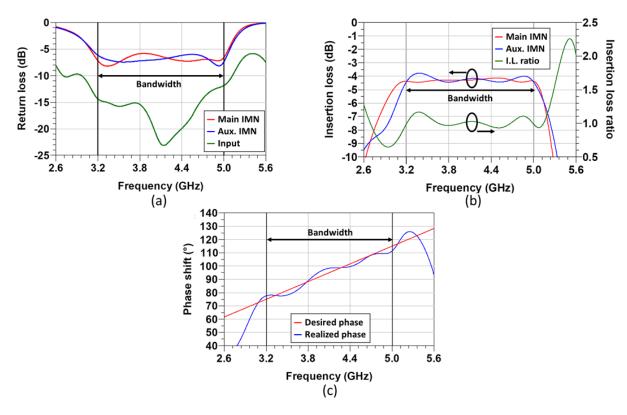

| Figure 3.21 Input section schematic                                                                      | 55   |

| Figure 3.22 Input section performance: a) Return loss, b) Insertion loss, c) Phase relationship          | 56   |

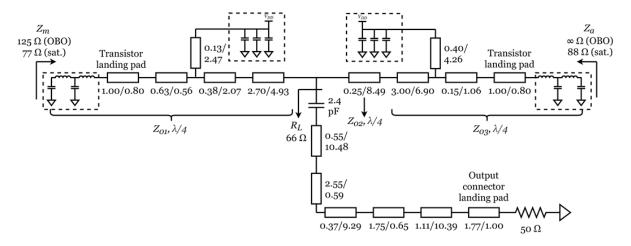

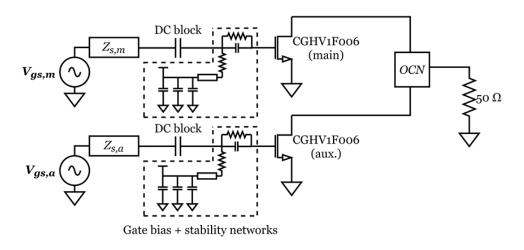

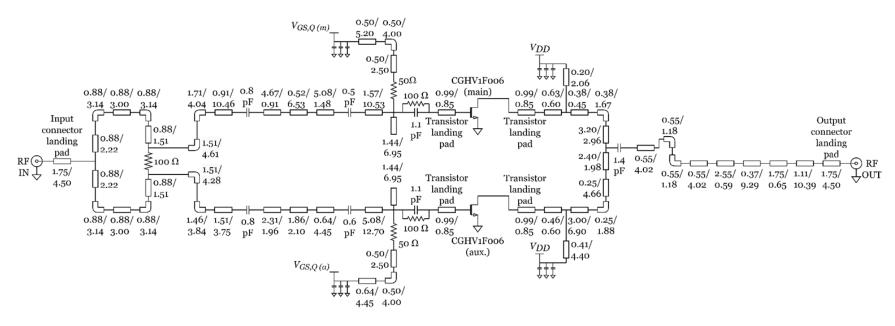

| Figure 3.23 Overall DPA schematic                                                                        | 59   |

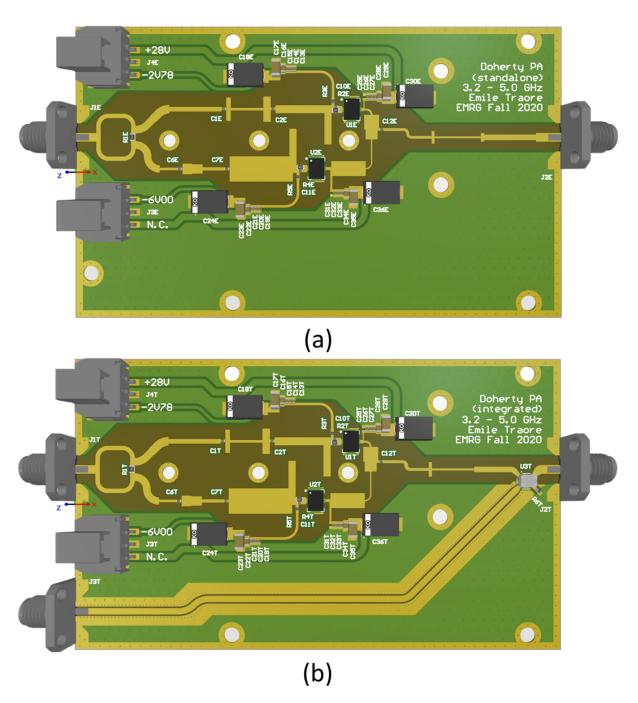

| Figure 3.24 DPA layout on PCB: a) Without coupler (fabricated), b) With coupler (not fabricated          | 1)60 |

| Figure 3.25 Simulated DPA S-parameters: a) $s_{21}$ , b) $s_{11}$ , $s_{22}$ , $s_{12}$                  | 61   |

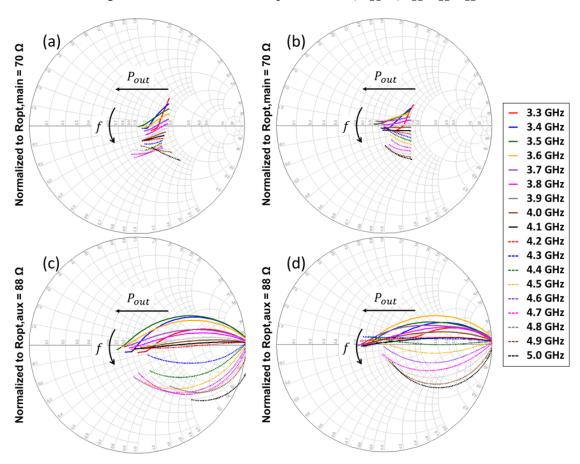

| Figure 3.26 Simulated DPA load modulation trajectories vs. frequency and output power                    | 61   |

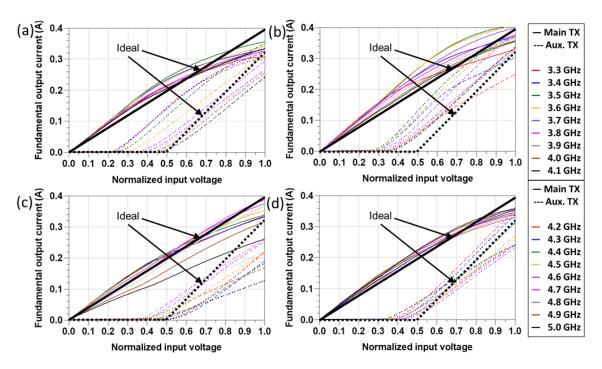

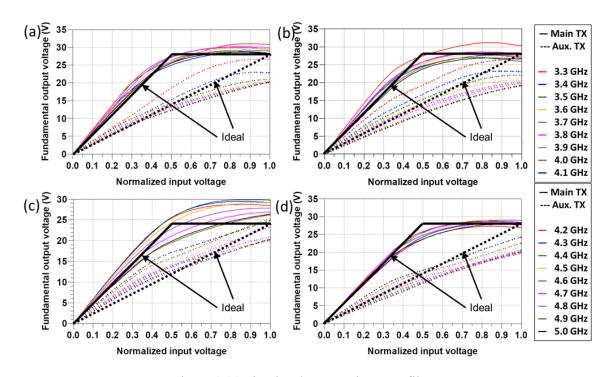

| Figure 3.27 Simulated DPA current profiles                                                               | 62   |

| Figure 3.28 Simulated DPA voltage profiles.                                                              | 62   |

| Figure 3.29 Simulated DPA AM-AM.                                                                         | 63   |

| Figure 3.30 Simulated DPA AM-PM                                                                          | 63   |

| Figure 3.31 Simulated DPA $\eta_D$                                                                       | 64   |

| Figure 3.32 Simulated DPA PAE                                                                            | 64   |

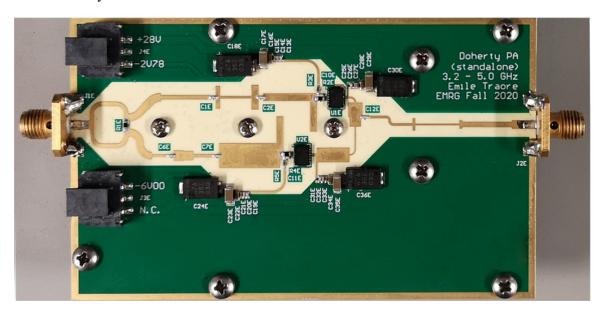

| Figure 4.1 Photograph of the fabricated DPA                                                              | 65   |

| Figure 4.2 Block diagram of the DPA S-parameter measurement setup                                        | 66   |

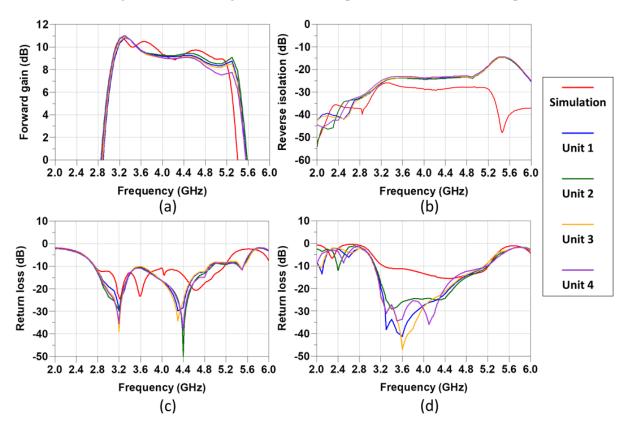

| Figure 4.3 Measured DPA S-parameters: a) $s_{21}$ , b) $s_{12}$ , c) $s_{11}$ , d) $s_{22}$              | 66   |

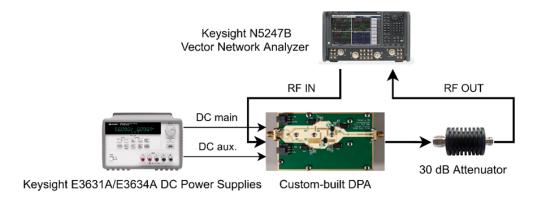

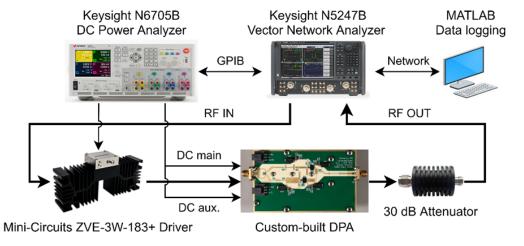

| Figure 4.4 Block diagram of the DPA CW measurement setup                                                 | 67   |

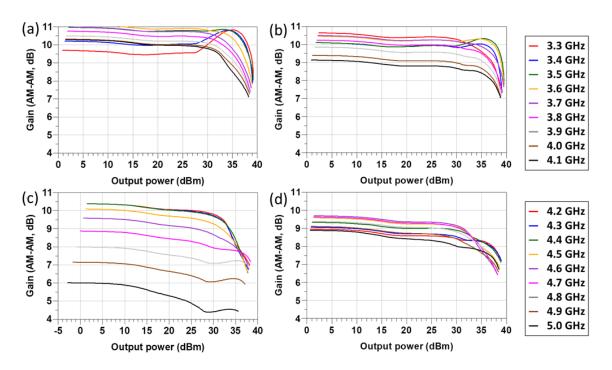

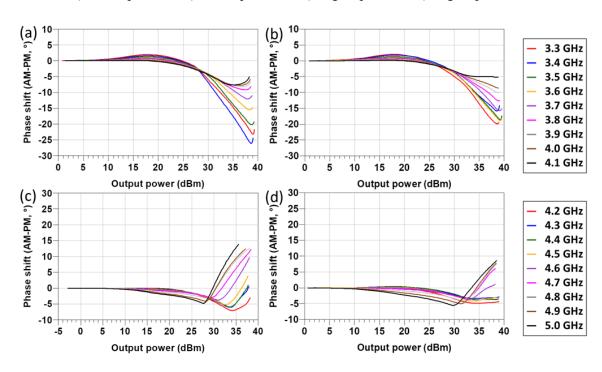

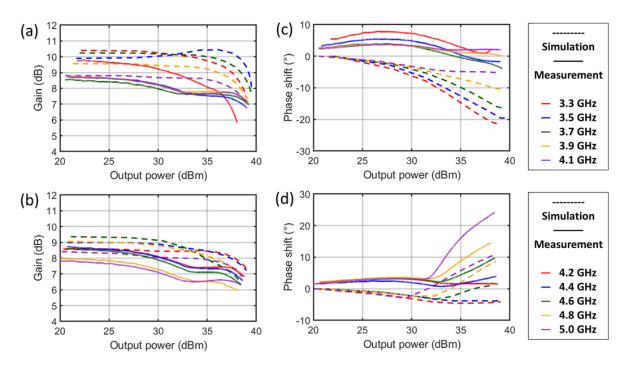

| Figure 4.5 Measured DPA linearity performance vs. <i>Pout</i>                                            | 68   |

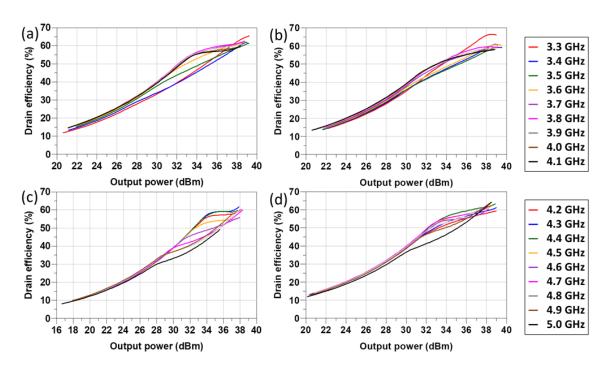

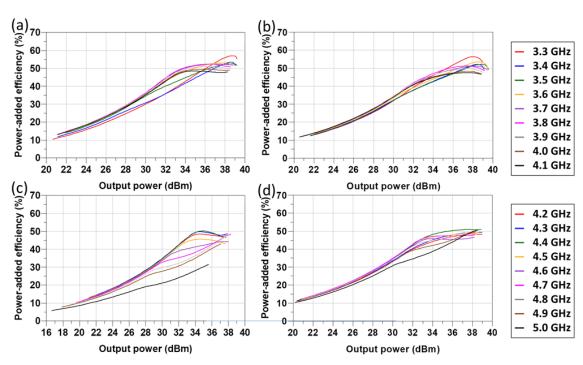

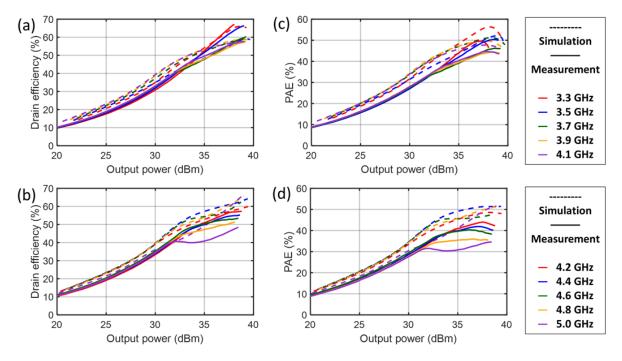

| Figure 4.6 Measured DPA efficiency performance vs. Pout                                                  | 68   |

| Figure 4.7 Measured DPA small-signal gain vs. frequency                                                  | 69   |

| Figure 4.8 Measured DPA <i>P<sub>sat</sub></i> vs. frequency                                  | 69 |

|-----------------------------------------------------------------------------------------------|----|

| Figure 4.9 Measured DPA $\eta_D$ at $P_{sat}$ vs. frequency                                   | 69 |

| Figure 4.10 Measured DPA $\eta_D$ at 6 dB OBO vs. frequency                                   | 69 |

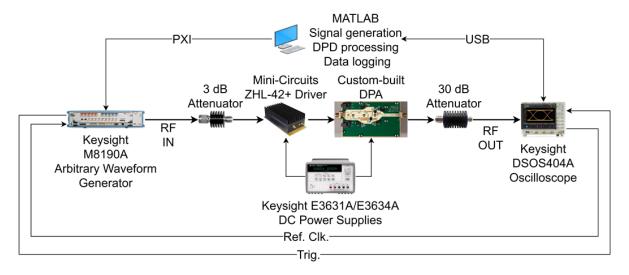

| Figure 4.11 Block diagram of the DPA modulated signal measurement setup                       | 70 |

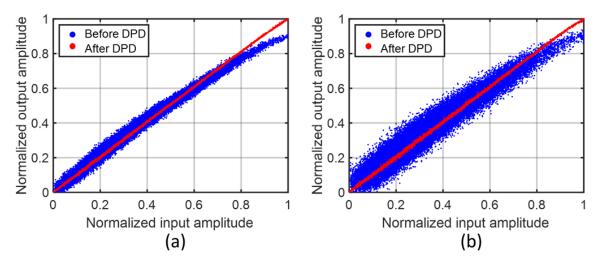

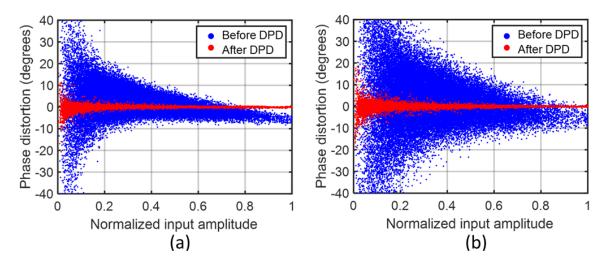

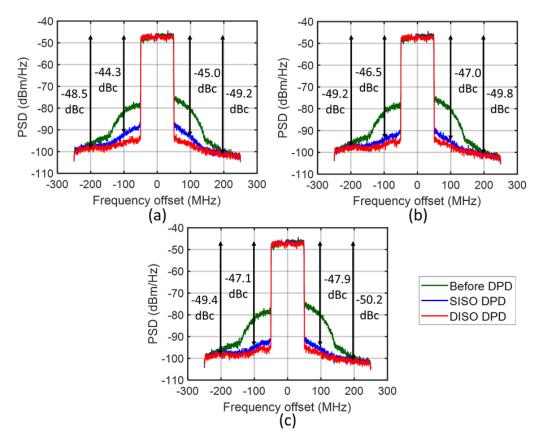

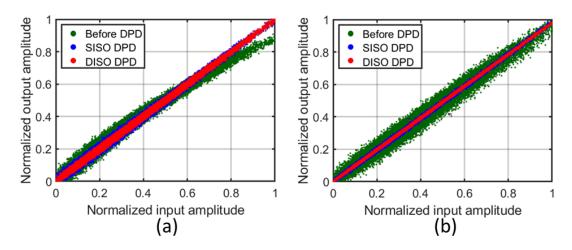

| Figure 4.12 AM-AM distortion before and after DPD for: a) 100 MHz, b) 200 MHz                 | 73 |

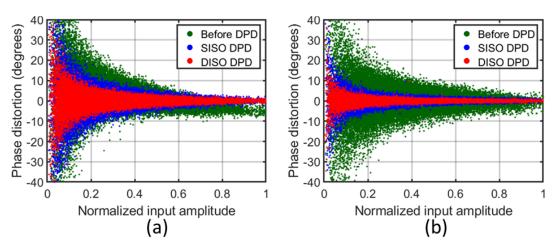

| Figure 4.13 AM-PM distortion before and after DPD for: a) 100 MHz, b) 200 MHz                 | 73 |

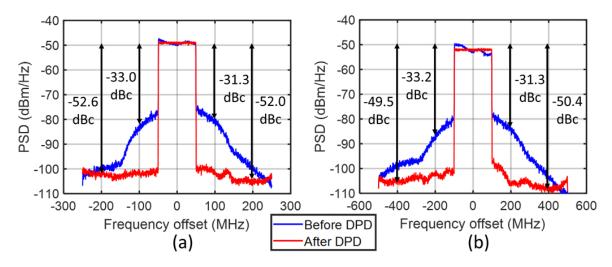

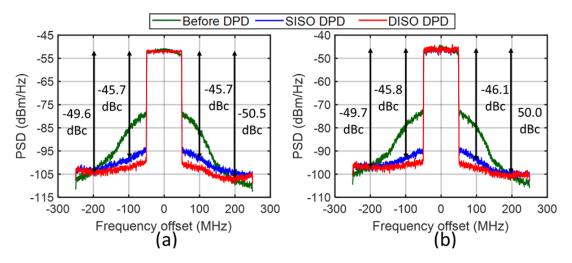

| Figure 4.14 Output spectra before and after DPD for: a) 100 MHz, b) 200 MHz                   | 74 |

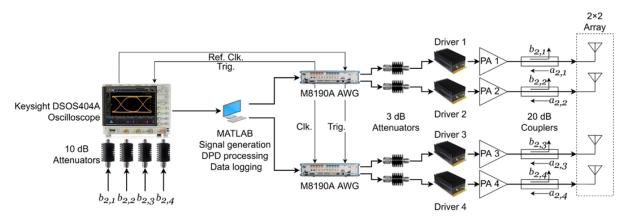

| Figure 4.15 Block diagram of the 2×2 PA array modulated signal measurement setup              | 75 |

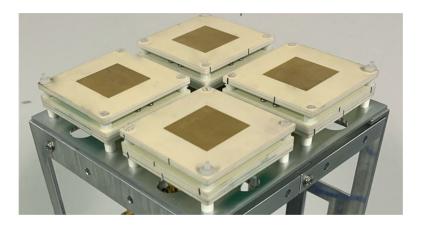

| Figure 4.16 Photograph of the fabricated antenna array                                        | 76 |

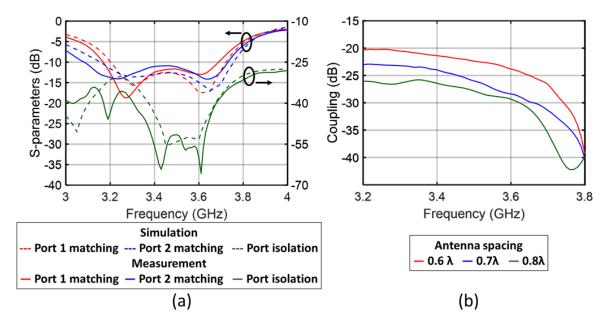

| Figure 4.17 Antenna array: a) Single element S-parameters, b) Worst coupling between elements | 76 |

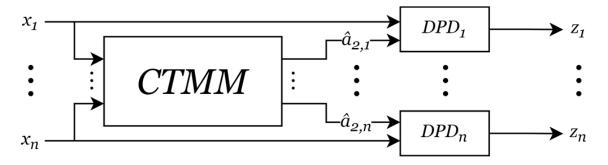

| Figure 4.18 Block diagram of DISO DPD including CTMM block                                    | 76 |

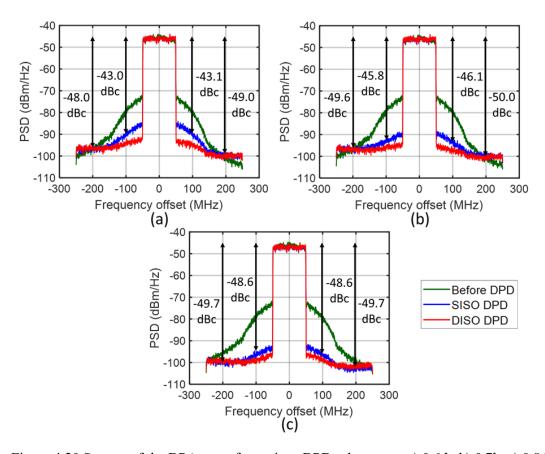

| Figure 4.19 Spectra of the DPA array for various DPD schemes                                  | 78 |

| Figure 4.20 Spectra of the DPA array for various DPD schemes                                  | 79 |

| Figure 4.21 2×2 array AM-AM distortion for: a) Single PA output, b) Combined output signal    | 80 |

| Figure 4.22 2×2 array AM-PM distortion for: a) Single PA output, b) Combined output signal    | 80 |

| Figure 4.23 2×2 array spectra for: a) Single PA output, b) Combined output signal             | 80 |

# **List of Tables**

| Table 2.1 Characteristics of conduction angle-based PA classes                                    | .13 |

|---------------------------------------------------------------------------------------------------|-----|

| Table 2.2 Efficiency of class F PA vs. number of terminated harmonics                             | .15 |

| Table 2.3 Comparison of state-of-the-art broadband DPAs in the literature                         | .34 |

| Table 3.1 Design parameters of the OCN for optimum DPA bandwidth                                  | .48 |

| Table 3.2 Initial and optimized values of $Z_{s,m}$ and $Z_{s,a}$ for optimum DPA load modulation | .51 |

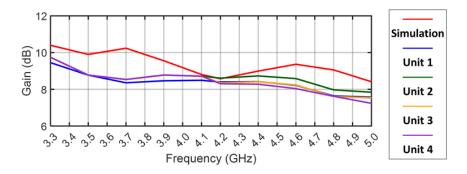

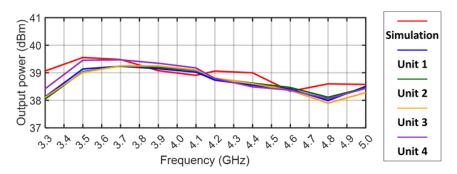

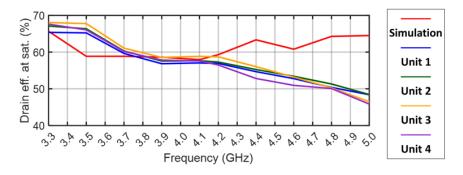

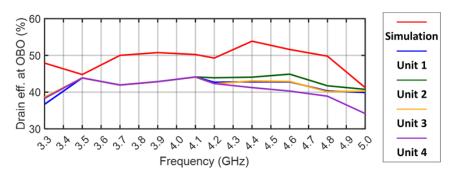

| Table 4.1 Comparison of measured DPA CW performance across units and vs. simulation               | .70 |

| Table 4.2 Comparison of DPA modulated signal performance vs. DPD algorithm                        | .71 |

| Table 4.3 Comparison of DPA modulated signal performance vs. signal frequency                     | .72 |

| Table 4.4 Comparison of DPA modulated signal performance vs. signal bandwidth for all units       | .72 |

| Table 4.5 Performance summary of the 2×2 class AB PA and DPA arrays under modulated signals       | .77 |

## **Chapter 1**

#### Introduction

#### 1.1 Motivation

Modern wireless networks are faced with a perpetual requirement to increase data rates to fulfill the growing demand for high-quality video streaming (for communication and entertainment purposes) and to accommodate the increasing number of Internet-connected devices, including self-driving vehicles and Internet of Things gadgets. Despite the continuous improvements brought by the fourth generation (4G) Long Term Evolution cellular standard, the growing data requirements of the future would not be satisfied, leading to the advent of fifth generation (5G) cellular networks.

To enable increased data rates, 5G networks employ multiple new strategies. First, higher frequency bands have been allocated for 5G use in the sub-6 GHz space, such as 3.3–3.8 GHz, 3.3–4.2 GHz, and 4.4–5.0 GHz [1]–[4] (new millimeter-wave bands have also been allocated above 24 GHz, which are outside the scope of this work). Figure 1.1 shows the distribution of new 5G frequency bands. Furthermore, wider modulation bandwidths and carrier techniques increase the bandwidth of the signal (up to 100 MHz for the sub-6 GHz bands) [1], [3]–[12]. As data rate is proportional to signal bandwidth, these bands provide higher data rates. Channel capacity for a given bandwidth is further enhanced by more sophisticated modulated schemes (both amplitude and phase modulation), which lead to a higher peak to average power ratio (PAPR) for the signal [1]–[6], [8]–[25]. Finally, 5G introduces the massive multiple input multiple output (MIMO) technique, which is shown in Figure 1.2. This allows the use of beamforming, where the signal can be directed towards a particular user, which improves signal quality and channel capacity. Although MIMO was already present in a few 4G systems, it featured only a few transmitters and receivers, whereas massive MIMO will expand this number up to 64 or 128 [26] or more, greatly improving the effectiveness of this technique.

The more stringent 5G system specifications improvements directly translate into more rigorous requirements for power amplifier (PA) design. Indeed, the PA is arguably the most important component in the transceiver [4], [9], [11], [26]–[27]. As it is the largest and most power-consuming component of the transmitter (between 40–60% of the power in base stations), it is the main determining factor for transmitter size and power efficiency [4], [11], [26]–[27]. Thus, improving PA efficiency leads to reduced energy usage in base stations, reducing costs, cooling needs, and environmental

impact. Furthermore, since the PA is the last active component in the signal chain, its linearity has the greatest effect on the transmitter's overall linearity. This explains the need for improvements in PA design techniques for compliance with 5G standards.

Figure 1.1 Spectrum of 5G frequency bands at sub-6 GHz and millimeter-wave (above 24 GHz) [28]

Figure 1.2 Comparison of 4G (no beamforming) and 5G (MIMO beamforming) [29]

#### 1.2 Problem Statement

The advancements in 5G techniques render existing 4G PAs and PA design techniques obsolete. Indeed, 5G places more stringent linearity and efficiency requirements on PAs while requiring the PA to maintain this performance over a wider bandwidth and at higher carrier frequencies. As shown in Figure 1.3 a), the high PAPR of higher-order modulation schemes signifies that the PA must handle signals up to the peak power while meeting the linearity requirements set by the 5G standard [adjacent channel power ratio (ACPR) and normalized mean square error (NMSE)] and remain as efficient as possible at the average power level. However, these specifications are in direct contradiction, as shown in Figure 1.3 b). When a typical PA operates at its peak efficiency, its linearity performance may not meet the defined standard, and when the PA operates at output back-off (OBO) power level and meets the

linearity specifications, its efficiency degrades. Furthermore, in massive MIMO arrays, the PAs will interfere with each other due to crosstalk through the antenna array, introducing a load modulation effect to each of the PA outputs, degrading linearity and efficiency. Digital predistortion (DPD) can alleviate the linearity-efficiency trade-off by enhancing overall system linearity, allowing PAs to operate in a more nonlinear and efficient regime [13], [16].

The quest for an enhanced trade-off between efficiency and linearity has motivated the use of OBO efficiency enhancement techniques for PAs, which increase the power range where a PA operates near its maximum efficiency to handle high PAPR signals with high average efficiency. Of the multiple architectures available, the Doherty PA (DPA) is the most popular due to its inherent simplicity. However, the conventional DPA architecture suffers from significant bandwidth limitations, which are worsened by transistor non-idealities. Furthermore, although the DPA architecture is theoretically perfectly linear, its linearity is significantly compromised by transistor non-idealities in practice. Thus, the improvement of practical DPA bandwidth and linearity is a very active topic for researchers and is the main focus of this work.

Figure 1.3 a) Peak and average powers of a signal [30], b) PA linearity-efficiency trade-off [31]

#### 1.3 Thesis Organization

This thesis is organized as follows. Chapter 2 begins with a theoretical review of PA-related concepts. It then provides an overview of the different PA classes of operation (basic, high-efficiency, broadband), as well as PA OBO efficiency enhancement techniques including the DPA technique. Finally, the chapter concludes with a literature review of state-of-the-art broadband sub-6 GHz DPAs.

Chapter 3 describes a design methodology for a broadband, linearity-enhanced sub-6 GHz DPA based on discrete components and transmission lines (TLs) on a printed circuit board (PCB). Several bandwidth and linearity enhancement techniques are discussed and applied to a 3.3–5.0 GHz DPA design. Simulation results for the DPA after full electromagnetic (EM) simulation are presented.

Chapter 4 presents measurement results for four different fabricated DPA units and compares them to simulation results. Modulated signal measurements for the individual DPA units and a 2×2 MIMO DPA array are presented, with the devices attached to an antenna array and driven with 5G-candidate orthogonal frequency division multiplexing (OFDM) modulated signals.

Finally, Chapter 5 summarizes the main findings of this work and concludes with a section on potential future work.

# **Chapter 2**

### **High Power Amplifier Review**

#### 2.1 Power Amplifier Basics

#### 2.1.1 Fundamental Power Amplifier Concepts

Radio frequency (RF) PAs amplify signals generated by the RF transmitter to a higher power level, to improve the range of wireless transmission by the antenna. Ideally, the output signal faithfully reproduces the smaller input signal; however, at high power levels, the output signal is affected by PA nonlinear distortion, which is paramount to the study of PAs.

Fundamentally, the PA is an RF amplifier consisting of a transistor with input and output matching networks (IMN and OMN). The IMN and OMN transform the source and load impedances, set to the system characteristic impedance ( $Z_0 = 50 \Omega$ ), into the impedances seen at the transistor reference planes ( $Z_S$  and  $Z_L$ ) as shown in Figure 2.1. The judicious choice of  $Z_S$  and  $Z_L$  based on the PA input and output impedances ( $Z_{in}$  and  $Z_{out}$ ) in the nonlinear region is the main aspect of PA design.

Figure 2.1 Basic schematic of an RF PA

At low input power  $(P_{in})$ , the PA output power  $(P_{out})$  is proportional to  $P_{in}$ , as the PA operates in linear mode. The small-signal power gain G is thus defined as the ratio of  $P_{out}$  to  $P_{in}$  for small  $P_{in}$ :

$$G = \frac{P_{out}}{P_{in}} \Big|_{P_{in} \approx 0} \tag{2.1}$$

To amplify RF signals, the PA must consume a certain amount of direct current (DC) power, acting as a DC to RF converter. The efficiency with which the PA accomplishes this conversion is known as drain efficiency ( $\eta_D$ ) and is given by:

$$\eta_D = \frac{P_{out}}{P_{DC}} \tag{2.2}$$

Drain efficiency is an accurate metric for assessing PA performance when the gain is high. However, high power RF PAs often have low gain and must be driven with a high  $P_{in}$ . When  $P_{in}$  cannot be neglected, power-added efficiency (PAE) is a more accurate efficiency metric:

$$PAE = \frac{P_{out} - P_{in}}{P_{DC}} = \eta_D \cdot \left(1 - \frac{1}{G}\right) \tag{2.3}$$

Note that as G becomes large, the value of PAE tends towards  $\eta_D$ .

As  $P_{in}$  increases, nonlinear distortion starts to occur. The ratio between  $P_{out}$  and  $P_{in}$  deviates from its small-signal value G. Since the output amplitude is distorted by the input amplitude, this type of distortion is known as amplitude to amplitude (AM-AM). A key PA performance metric is the 1 dB compression point  $(OP_{1dB})$ , or the  $P_{out}$  level where gain drops by 1 dB:

$$OP_{1dB} = P_{out}|_{P_{out}/P_{in} = G-1}$$

(2.4)

The phase of the output signal may also change relative to its small-signal value if the PA exhibits memory effects, a type of distortion known as amplitude to phase (AM-PM). These nonlinearities cause degradation of the signal quality and must be minimized.

Furthermore, as the PA is driven into a nonlinear regime, it emits harmonics, or frequency content at multiples of the signal frequency  $f_0$ . The nonlinear PA output signal y(t) can be expressed as a power series of the input signal x(t):

$$y(t) = a_0 + a_1 x(t) + a_2 x^2(t) + a_3 x^3(t) + \cdots$$

(2.5)

If x(t) is a sinusoidal signal of the form  $A \cdot \cos(2\pi f_0 t) = A \cdot \cos(\omega_0 t)$ , y(t) can be expressed as:

$$y(t) = \left(a_0 + \frac{a_2 A^2}{2}\right) + \left(A + \frac{3a_3 A^3}{4}\right)\cos(\omega_0 t) + \frac{a_2 A^2}{2}\cos(2\omega_0 t) + \frac{a_3 A^3}{4}\cos(3\omega_0 t) + \cdots$$

(2.6)

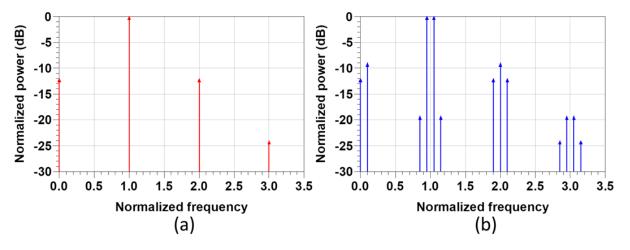

The appearance of harmonics at multiples of the center frequency  $(f_0)$  is evident, as shown in Figure 2.2 a). However, these terms do not pose a problem because they are far from the desired frequency range and can be filtered out.

However, when the input signal consists of multiple frequencies, equation (2.6) leads to intermodulation distortion (IMD). The output spectrum will then contain terms at frequencies that are the sums and differences of the harmonics as shown in Figure 2.2 b). If the input contains frequencies  $f_1$  and  $f_2$ , the second-order IMD terms are  $f_1 \pm f_2$  and the third-order IMD terms are  $2f_1 \pm f_2$  and  $2f_2 \pm f_1$ . The  $2f_1 - f_2$  and  $2f_2 - f_1$  terms are problematic because they fall near  $f_1$ ,  $f_2$

and cannot easily be filtered out. These terms will cause out-of-band emissions interfering with neighboring communication channels, so it is critical to diminish IMD.

Figure 2.2 Output spectra of a nonlinear PA for: a) Single-tone at  $f_0$ , b) Two-tone at  $0.95f_0$ ,  $1.05f_0$

#### 2.1.2 Ideal Transistor Model

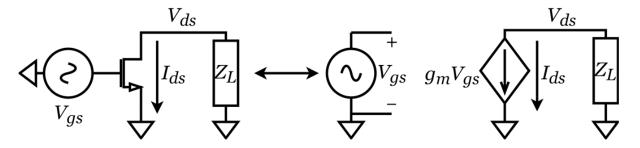

The majority of RF PAs are based on a transistor operating as a current source. The transistor has three terminals: gate, drain, and source. In the common source configuration, the input is applied at the gate, the output collected at the drain, and the source is grounded. As shown in Figure 2.3, the simplified model of a field-effect transistor (FET) is a voltage-controlled current source. The gate-source voltage  $V_{gs}$  is sampled and converted to a drain-source current  $I_{ds}$  based on the transconductance  $(g_m)$ , and  $I_{ds}$  is converted to a drain-source voltage  $V_{ds}$  based on the load impedance  $Z_L$ . Figure 2.4 a) shows the  $V_{gs}$  to  $I_{ds}$  transfer characteristic, demonstrating the three regions of operation: pinch-off  $(V_{gs}$  below pinch-off voltage  $V_p$ ), linear, and saturation  $(V_{gs}$  above  $V_{gs,max}$ ,  $I = I_{max}$ ). In amplifier design, the FET is operated in the linear region to ensure  $g_m$  remains constant. Figure 2.4 b) shows the relationship between  $V_{ds}$  and  $I_{ds}$  at various  $V_{gs}$ .  $V_{ds}$  must not fall below the knee voltage  $V_k$  to ensure linear operation and must not exceed the drain-source breakdown voltage  $V_{max}$ . For the subsequent theoretical derivations, the knee voltage will be considered small  $(V_k \approx 0)$  for simplicity. In real transistors,  $V_k$  can be a significant fraction of  $V_{max}$ , which varies based on the instantaneous value of  $V_{gs}$ , so the analysis is significantly more complex.

Figure 2.3 Simplified model of a transistor in the common-source configuration

Figure 2.4 Transistor: a)  $V_{gs}$  to  $I_{ds}$  transfer characteristic, b)  $V_{ds}$  vs.  $I_{ds}$  at various  $V_{gs}$

#### 2.1.3 Transistor Technologies

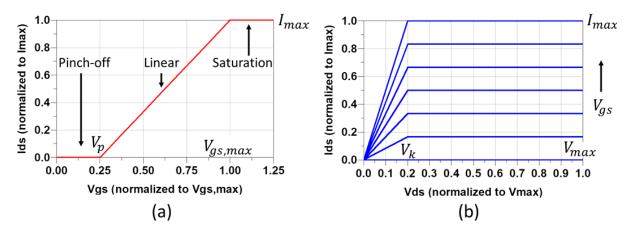

According to [32], different RF and microwave applications require different ranges of power and frequency, each satisfied by a different transistor technology. Silicon-based technologies include complementary metal-oxide semiconductor (CMOS), silicon germanium (SiGe), and laterally diffused metal oxide semiconductor (LDMOS). III-V technologies are based on compound semiconductors composed of Group III and Group V elements from the periodic table. The most common ones are gallium arsenide (GaAs) and gallium nitride (GaN).

As shown in Figure 2.5 [32], SiGe and GaAs are mostly used for low-power, high-frequency devices. Although GaAs reaches higher power and frequency than SiGe, silicon-based technologies can integrate the PA with the rest of the transceiver on a single chip [33]–[34]. For high-power applications, the two dominant technologies are LDMOS and GaN, which can sustain much higher operating voltages than other technologies [32], [35]. While LDMOS is limited to lower frequencies, GaN quickly outperforms it as frequencies rise towards the GHz range, due to its significantly higher electron velocities [35]. GaN is also able to sustain higher breakdown voltages and temperatures, enabling

improve power density and smaller devices [35]. Thus, for sub-6 GHz 5G applications, which mainly consist of discrete devices on PCBs, GaN is the optimal technology [32], [35].

Figure 2.5 Optimum transistor technology vs. frequency and output power range [32]

#### 2.2 Power Amplifier Classes

The different PA classes of operation are distinguished by the biasing point of the transistor and the load network at the transistor drain. The transistor is biased at a quiescent gate voltage  $V_{GS,Q}$  and drain voltage  $V_{DD}$ , with a corresponding quiescent drain current  $I_{DS,Q}$ . The various classes offer trade-offs between linearity and efficiency, which are detailed in [36] and will be summarized in this section.

#### 2.2.1 Class A

In class A,  $V_{GS,Q}$  is set to the midpoint between  $V_p$  and  $V_{GS,max}$  ( $I_{DS,Q}$  is half of  $I_{max}$ ), and  $V_{DD}$  is set to the midpoint between  $V_{max}$  and  $V_k$ . Assuming  $V_k \ll V_{max}$ , the biasing point is given as follows [36]:

$$(V_{DD}, I_{DS,Q}) = \left(\frac{V_{max}}{2}, \frac{I_{max}}{2}\right) \tag{2.7}$$

This bias point allows the voltage and current to swing from 0 V to  $V_{max}$  and 0 A to  $I_{max}$ , with amplitudes of  $V_{max}/2$  and  $I_{max}/2$ , respectively. To ensure both  $V_{ds}$  and  $I_{ds}$  reach their maximum swing simultaneously, the transistor must be terminated with its optimum load resistance  $(R_{opt})$  [36]:

$$R_{opt} = \frac{V_{max}/2}{I_{max}/2} = \frac{V_{max}}{I_{max}}$$

(2.8)

In class A, the PA maximum (saturated) output power ( $P_{sat}$ ), DC power consumption ( $P_{DC}$ ), and drain efficiency are the following [36]:

$$P_{sat,class\,A} = \frac{1}{2} \cdot \frac{V_{max}}{2} \cdot \frac{I_{max}}{2} = \frac{V_{max} \cdot I_{max}}{8}$$

(2.9)

$$P_{DC,class\,A} = V_{DS,Q} \cdot I_{DS,Q} = \frac{V_{max}}{2} \cdot \frac{I_{max}}{2} = \frac{V_{max} \cdot I_{max}}{4}$$

(2.10)

$$\eta_{D,class\,A} = \frac{P_{sat}}{P_{DC}} = \left(\frac{V_{max} \cdot I_{max}}{8}\right) / \left(\frac{V_{max} \cdot I_{max}}{4}\right) = 0.5 = 50\%$$

(2.11)

Class A PA efficiency is theoretically limited to 50%. Furthermore, since  $P_{DC}$  is constant and independent of  $P_{out}$ ,  $\eta_D$  drops proportionally to  $P_{out}$ , which is unsuitable for handling high PAPR signals. However, class A PA linearity is very good because the  $I_{ds}$  and  $V_{ds}$  are both sinusoidal, and gain is high because the PA is conducting for the entire range of the input signal. Therefore, class A PAs are mostly used for instrumentation applications, and rarely in cellular applications.

#### 2.2.2 Reduced Conduction Angle Classes

The main disadvantage of the class A PA is its low efficiency, especially at OBO. Different classes of operation can be obtained by setting  $V_{GS,Q}$  such that  $I_{DS,Q}$  is below  $I_{max}/2$ . For example, class B operates the transistor at  $V_{GS,Q} = V_p$  and  $I_{DS,Q} = 0$ . In class B, the transistor conducts for only half of the input signal waveform and operates in cutoff for the other half. In other words, the conduction angle of the class B PA is  $\theta = 180^{\circ}$ , whereas it is  $\theta = 360^{\circ}$  for the class A PA.

Besides classes A and B, there exists a continuum of PA biasing conditions. Class AB PAs are biased such that  $0 < I_{DS,Q} < I_{max}/2$  such that  $180^{\circ} < \theta < 360^{\circ}$ . Class C PAs are biased at  $V_{GS,Q} < V_p$  such that  $\theta < 180^{\circ}$ . In all these cases, the drain is biased at  $V_{DD} = V_{max}/2$ . Figure 2.6 a) shows the relationship between  $V_{GS,Q}$  and  $I_{DS,Q}$  for the different classes, and Figure 2.6 b) shows the load lines, which relate the instantaneous voltage and current,  $V_{ds}(t)$  and  $I_{ds}(t)$ , for each class. As the conduction angle decreases, the transistor spends more and more of the cycle at zero current, reducing  $P_{DC}$ . The reduced PA classes have different linearity-efficiency trade-offs, which can be directly computed from the conduction angle.

Figure 2.6 PA class A, AB, B, C: a) Biasing point, b) Load line

Figure 2.7 a) shows the time-domain waveforms of  $I_{ds}(t)$  for the various classes of operation. The corresponding equation is the following, where  $\omega t$  represents the phase of the input signal [36]:

$$I_{ds}(t) = \begin{cases} 0, & -\pi < \omega t < -\theta/2 \\ \frac{I_{max}}{1 - \cos(\theta/2)} \left[ \cos(\omega t) - \cos\left(\frac{\theta}{2}\right) \right], & -\frac{\theta}{2} < \omega t < \frac{\theta}{2} \\ 0, & \theta/2 < \omega t < \pi \end{cases}$$

(2.12)

By applying Fourier analysis, the drain current can be written as follows [36]:

$$I_{ds}(t) = I_0 + I_1 \cos(\omega t) + I_2 \cos(2\omega t) + I_3 \cos(3\omega t) + \cdots$$

(2.13)

$$I_0 = \frac{I_{max}}{2\pi} \cdot \frac{2 \cdot \sin(\theta/2) - \theta \cdot \cos(\theta/2)}{1 - \cos(\theta/2)}$$

(2.14)

$$I_1 = \frac{I_{max}}{2\pi} \cdot \frac{\theta - \sin(\theta)}{1 - \cos(\theta/2)}$$

(2.15)

$$I_n = \frac{1}{\pi} \int_{-\theta/2}^{\theta/2} \frac{I_{max}}{1 - \cos(\theta/2)} [\cos(\omega t) - \cos(\theta/2)] \cdot \cos(n\omega t) \cdot d(\omega t)$$

(2.16)

When  $\theta$  is reduced, harmonics appear in  $I_{ds}(t)$ . Figure 2.7 b) plots the amplitudes of the first five harmonics against  $\theta$ , showing that as  $\theta$  decreases, harmonic distortion increases. To avoid power dissipation at the harmonics, which is undesired because they do not contribute to the useful signal, the load network must feature short-circuits at the harmonic frequencies to force the voltage at the harmonics to zero. Thus, only the DC current  $I_0$  and fundamental current  $I_1$  influence  $\eta_D$ . Interestingly,  $I_1$  is higher for class AB than class A or class B, leading to a higher  $P_{sat}$ .

Figure 2.7 a)  $I_{ds}$  waveforms vs. conduction angle, b)  $I_{ds}$  harmonic amplitudes vs. conduction angle

Based on these parameters,  $R_{opt}$ ,  $P_{sat}$ ,  $P_{DC}$ , and  $\eta_D$  can be calculated for a general value of  $\theta$ .  $R_{opt}$  is set to simultaneously maximize voltage amplitude ( $V_{max}/2$ ) and current amplitude ( $I_1$ ).  $P_{sat}$  is calculated based on the fundamental voltage and current amplitudes, and  $P_{DC}$ , based on the DC voltage and current. This results in the following equations [36]:

$$R_{opt} = \frac{V_{max}/2}{I_1} \tag{2.17}$$

$$P_{sat} = \frac{V_{max}/2 \cdot I_1}{2} = \frac{V_{max} \cdot I_1}{4}$$

(2.18)

$$P_{DC} = \frac{V_{max} \cdot I_0}{2} \tag{2.19}$$

$$\eta_D = \frac{P_{sat}}{P_{DC}} = \frac{I_1}{2 \cdot I_0} \tag{2.20}$$

Note that  $\theta = 2\pi$  is consistent with the parameters for class A derived previously  $(I_0 = I_1 = I_{max}/2)$ . Furthermore, for the special case of the class B PA  $(\theta = \pi)$ ,  $I_0 = I_{max}/\pi$  and  $I_1 = I_{max}/2$  are obtained. Thus, class B has the same  $R_{opt}$  and  $P_{sat}$  as class A, but with a significantly lower  $P_{DC}$  and higher  $\eta_D$  as shown in equation (2.21). Figure 2.8 a) plots  $\eta_D$  against  $P_{out}$  for different biasing points, showing that for smaller values of  $\theta$ , efficiency is higher at  $P_{sat}$  and drops off slower at OBO. In summary, reduced conduction angles classes improve  $\eta_D$  compared to class A [36].

$$\eta_{D,class\,B} = \frac{I_{max}/2}{2 \cdot I_{max}/\pi} = \frac{\pi}{4} \approx 78.5\%$$

(2.21)

Figure 2.8 b) plots  $P_{out}$  against  $P_{in}$  for various biasing points to assess gain and linearity. The gain follows the opposite trend of  $\eta_D$ : it decreases monotonically as  $\theta$  decreases since the PA conducts for a smaller portion of the input signal. In terms of linearity, for classes A and B,  $P_{out}$  is always proportional to  $P_{in}$  because  $\theta$  is constant ( $\theta = 360^{\circ}$  for class A,  $\theta = 180^{\circ}$  for class B). Thus, class A and B are perfectly linear in theory, although class B has a 6 dB lower gain because half of the input signal is not utilized. For classes AB and C,  $\theta$  changes as the input signal magnitude changes, so they are nonlinear (weakly for class AB, strongly for class C). The characteristics of the different classes of operation of the PA based on conduction angle are summarized in Table 2.1.

Figure 2.8 a)  $\eta_D$  vs.  $P_{out}$  at various conduction angles, b)  $P_{out}$  vs.  $P_{in}$  at various conduction angles

| Class of operation | Conduction angle      | Efficiency   |      | Gain | Linearity (theory) | Output<br>power |

|--------------------|-----------------------|--------------|------|------|--------------------|-----------------|

| A                  | $\theta = 2\pi$       | 50%          | Poor | Best | Ideal              | Good            |

| AB                 | $\pi < \theta < 2\pi$ | 50%-78.5%    | Fair | Good | Good               | Best            |

| В                  | $\theta = \pi$        | 78.5%        | Good | Fair | Ideal              | Good            |

| C                  | $0 < \theta < \pi$    | 78 50% 1000% | Post | Door | Door               | Door            |

Table 2.1 Characteristics of conduction angle-based PA classes

#### 2.2.3 High Efficiency Classes

The reduced conduction angle class PAs presented in the previous section offer trade-offs between linearity and efficiency. However, as  $\eta_D$  tends towards 100% in class C, gain and  $P_{out}$  both quickly drop to zero. Therefore, other high efficiency classes were developed, such as classes F and F<sup>-1</sup> [36].

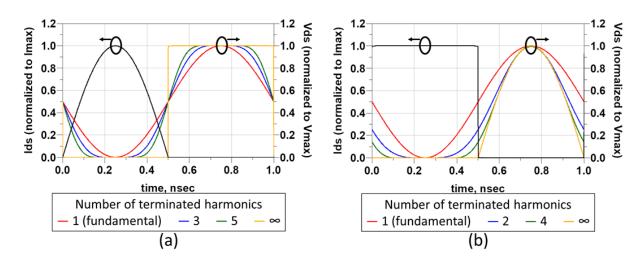

As described in [27], [36]–[37], class F operation aims to achieve a square wave  $V_{ds}(t)$  and a half-sine wave  $I_{ds}(t)$ , and class F<sup>-1</sup> is its dual, with a half-sine wave  $V_{ds}(t)$  and square wave  $I_{ds}(t)$ . As shown in Figure 2.9 a) and b), the overlap between the  $V_{ds}$  and  $I_{ds}$  waveforms of class F and F<sup>-1</sup> PAs decreases as more and more harmonics are terminated and disappears if all harmonics are terminated.

Class F PAs are biased in class B, to obtain a half-sine  $I_{ds}$ , and class F-1 PAs are biased in class A and overdriven to approximate a square wave  $I_{ds}$ .  $V_{ds}$  waveforms are engineered by setting the harmonic impedances appropriately. In class F, the odd harmonics are open-circuited and even harmonics are short-circuited to obtain a square wave. In class F-1, the even harmonics are open-circuited and odd harmonics are short-circuited to obtain a half-sine wave. The current and voltage waveforms can be written as follows [36]–[37]:

$$I_{ds,class\,F}(t) = I_0 + I_1 \cos(\omega t) + I_2 \cos(2\omega t) + \dots = \frac{I_{max}}{\pi} + \frac{I_{max}}{2} \cos(\omega t) + \dots$$

(2.22)

$$V_{ds,class\,F}(t) = V_0 + V_1 \cos(\omega t) + V_3 \cos(3\omega t) + \dots = \frac{V_{max}}{2} - \frac{2V_{max}}{\pi} \cos(\omega t) + \dots$$

(2.23)

$$I_{ds,class F^{-1}}(t) = I_0 + I_1 \cos(\omega t) + I_3 \cos(3\omega t) + \dots = \frac{I_{max}}{2} + \frac{2I_{max}}{\pi} \cos(\omega t) + \dots$$

(2.24)

$$V_{ds,class \, F^{-1}}(t) = V_0 + V_1 \cos(\omega t) + V_2 \cos(2\omega t) + \dots = \frac{V_{max}}{\pi} - \frac{V_{max}}{2} \cos(\omega t) + \dots$$

(2.25)

$R_{opt}$ ,  $P_{sat}$ ,  $P_{DC}$ , and  $\eta_D$  are the following [36]:

$$R_{opt,class\,F} = \left| \frac{V_1}{I_1} \right| = \frac{2V_{max}/\pi}{I_{max}/2} = \frac{4}{\pi} \cdot \frac{V_{max}}{I_{max}} = \frac{4}{\pi} \cdot R_{opt,class\,B} \tag{2.26}$$

$$R_{opt,class\,F^{-1}} = \left| \frac{V_1}{I_1} \right| = \frac{V_{max}/2}{2I_{max}/\pi} = \frac{\pi}{4} \cdot \frac{V_{max}}{I_{max}} = \frac{\pi}{4} \cdot R_{opt,class\,B}$$

(2.27)

$$P_{sat} = \left| \frac{V_1 \cdot I_1}{2} \right| = \frac{V_{max} \cdot I_{max}}{2\pi} \tag{2.28}$$

$$P_{DC} = V_0 \cdot I_0 = \frac{V_{max} \cdot I_{max}}{2\pi}$$

(2.29)

$$\eta_D = \frac{P_{out}}{P_{DC}} = 1 = 100\% \tag{2.30}$$

From equations (2.28) – (2.30), both class F and F<sup>-1</sup> provide  $\eta_D = 100\%$  and increased  $P_{sat}$  from the transistor. However, class F is preferred in wireless applications because it provides increased  $R_{opt}$

compared to class B (easier to match to  $Z_0 = 50 \Omega$ ) and does not require overdriving the transistor like class F-1 [37].

In practice, ideal class F and F<sup>-1</sup> terminations cannot be achieved because of the infinite number of terminated harmonics. Practically, up to three harmonics can be terminated with a single stub matching network and  $\lambda/4$  biasing TL [27]. The relationship between the number of terminated harmonics and  $\eta_D$  for class F PAs is given in Table 2.2, showing a 10 percentage point improvement from class B by terminating the third harmonic [36].

Voltage harmonics 1 1, 3 1, 3, 5 3, 5... ∞ 0.500 0.563 0.586 1 0.637 Current 1, 2 0.667 0.750 0.781 0.849 harmonics 1, 2, 4 0.905 0.711 0.8000.833 2, 4...<u>∞</u> 0.785 0.8840.920 1.000

Table 2.2 Efficiency of class F PA vs. number of terminated harmonics

Figure 2.9  $I_{ds}(t)$  and  $V_{ds}(t)$  waveforms vs. number of harmonics for: a) Class F, b) Class F<sup>-1</sup>

#### 2.2.4 Broadband Classes

The reduced conduction angles and high efficiency PAs require open-circuit or short-circuit harmonic terminations, which cannot be maintained over wide bandwidths, so these PAs are narrowband by nature. Indeed, PAs and other RF circuits can be characterized by their fractional bandwidth (FBW), which is the ratio of bandwidth to center frequency, an important figure of merit to determine if a circuit is broadband or narrowband. For example, conventional class F PAs have less than 10% FBW [7]. A

broadband alternative is the class J/J\* PA, which maintains the performance of class B without the strict requirement of shorted harmonics [36], [38]–[39], and can achieve above 120% FBW [27].

Class J/J\* is based on the class B biasing point, so the drain current waveform equation is obtained from equations (2.13)–(2.16) with the conduction angle set to  $\theta = \pi$  [36], [38]–[39]:

$$I_{ds}(t) = I_0 + I_1 \cos(\omega t) + I_2 \cos(2\omega t) + \dots = \frac{I_{max}}{\pi} + \frac{I_{max}}{2} \cos(\omega t) + \frac{2}{3\pi} \cos(2\omega t) + \dots$$

(2.31)

However, as shown in [27], [36], [38]–[40], class J/J\* allows the fundamental load impedance to deviate from  $R_{opt}$  and the second harmonic impedance to take reactive values instead of a strict short-circuit. The other harmonics are still assumed to be short-circuited. The fundamental and second harmonic impedances  $(Z_1, Z_2)$  are chosen based on equations (2.32) and (2.33), where  $-1 < \alpha < 1$ .  $\alpha = 0$  corresponds to class B, whereas class J and J\* operation refer to the regions where  $-1 \le \alpha < 0$  and  $0 < \alpha \le 1$ , respectively.

$$Z_1 = R_{opt} \cdot (1 + j\alpha) \tag{2.32}$$

$$Z_2 = -j\frac{3\pi}{8}\alpha \cdot R_{opt} \tag{2.33}$$

Figure 2.10 a) shows the impedances  $Z_1$  and  $Z_2$  on a Smith chart normalized to  $R_{opt}$ .  $Z_1$  has a constant resistive component  $R_{opt}$  with a reactive impedance component, and  $Z_2$  has only a reactive component with opposite sign to  $Z_1$ . These conditions can be achieved over a broad bandwidth: in fact, the matching network can be designed such that as frequency varies,  $Z_1$  and  $Z_2$  vary along the class J/J\* curves. This is known as continuous class B/J/J\* design [38]–[39].

The class J/J\* load network produces a drain voltage given by equation (2.34) where  $V_{DD}$  represents the supply voltage [36], [38]–[39]:

$$V_{ds}(t) = V_{DD} \left[ 1 - \cos(\omega t) + \alpha \cdot \sin(\omega t) - \frac{\alpha}{2} \sin(2\omega t) \right]$$

(2.34)

As shown in [36], [38]–[40], this shape of  $V_{ds}(t)$ , together with  $I_{ds}(t)$  given in equation (2.31), results in  $P_{out}$ , linearity, and efficiency identical to a class B PA. Indeed, the first two terms,  $V_{DD}$  (DC voltage) and  $-V_{DD} \cdot \cos(\omega t)$  (real part of the fundamental voltage), are the same as for class B. Thus,  $P_{out}$  and efficiency are identical to class B. The third and fourth terms are purely imaginary and dissipate no power, but shape the drain voltage waveform to avoid intrusion into the knee region to maintain the same linearity as class B. However, class J PAs have limitations. The peak value of  $V_{ds}(t)$

is significantly higher than in class B for the same  $V_{DD}$ , as shown in Figure 2.10 b), so a continuous class B/J/J\* PA design must use transistors with higher  $V_{max}$  or decrease  $V_{DD}$  which lowers  $P_{sat}$ . Furthermore, the maximum theoretical bandwidth is one octave, since the fundamental and second harmonic frequency ranges overlap beyond that point, while they require different termination styles. Also, class J PAs only achieve class B efficiency, not 100% like the class F/F-1 PAs.

Figure 2.10 Continuous class B/J/J\*: a)  $Z_1$  and  $Z_2$  vs. frequency, b)  $I_{ds}(t)$  and  $V_{ds}(t)$  for various  $\alpha$

Continuous class B/J/J\* principle can be applied to class F/F<sup>-1</sup> PAs, leading to broadband and highly efficient continuous class F/F<sup>-1</sup> PAs (equivalent efficiency to conventional class F/F<sup>-1</sup> without strict harmonic open and short circuits). The PA can also be designed to transfer between continuous class F and F<sup>-1</sup> over its bandwidth. Formulations that allow resistive components for the harmonic terminations [7], [27], [40] also exist, allowing bandwidths exceeding one octave. The detailed theory of continuous class F/F<sup>-1</sup> PAs is outside of the scope of this work.

#### 2.3 Output Back-off Efficiency Enhancement Techniques

The PA classes presented so far are all targeted maximum  $\eta_D$  at  $P_{sat}$ . However, modern communication signals have high PAPR, so the PA spends most of the time at OBO, leading to a rapid drop-off in  $\eta_D$  as  $P_{out}$  decreases. This led to the development of techniques that allow the PA to maintain peak  $\eta_D$  at OBO. These techniques are either based on supply modulation, such as envelope elimination and

restoration (EER) or envelope tracking (ET) or based on load modulation, such as the outphasing PA and DPA.

#### 2.3.1 EER and ET Power Amplifiers

EER and ET PAs are described in [36]. Both techniques are based on supply modulation. A diagram of a supply modulated PA is shown in Figure 2.11. The PA  $V_{DD}$  is dynamically adjusted based on the envelope of the input signal using a supply modulator (SM). Thus, as signal level decreases from peak power,  $V_{DD}$  decreases proportionally, such that the PA always outputs the highest fundamental voltage  $V_1$  allowed by  $V_{DD}$  and maintains its peak efficiency across a wide range of power levels.

Figure 2.11 Block diagram of a supply-modulated PA (EER/ET)

The main distinction between EER and ET is the input signal to the PA. In EER, the envelope is eliminated through a limiter: the input signal to the PA has constant amplitude and contains only phase information. Since  $P_{in}$  is constant, a nonlinear and thus very efficient PA can be used. However, the SM must track the envelope perfectly, which is very difficult to accomplish and is a major limitation of EER. The time alignment of the SM and PA paths must be near-ideal, otherwise the incorrect amplitude will be restored to the PA output signal, causing distortion (third-order IMD approximately -30 dBc for a delay mismatch of 10% of the RF bandwidth) [41]. Thus, EER is limited to signal bandwidths much lower than the hundreds of MHz required by 5G. Furthermore, to maintain the output signal linearity, the supply modulation must be maintained down to 0 V, which requires a very high dynamic range SM.

In contrast, ET does not eliminate the amplitude information from the PA input signal and requires a linear PA, such as class B, which is typically less efficient than nonlinear classes. However, the requirements on the supply tracking are relaxed: the time alignment requirement is not as stringent and the SM can operate at a lower dynamic range, not necessarily down to 0 V. Unfortunately, EER still has practical implementation problems. Accurate delay alignment between SM and PA still plays a

role: if  $V_{DD}$  is too low, or too high for the signal, linearity or efficiency will suffer, respectively. Furthermore, a broadband SM is required: the signal envelope is a vector sum of the in-phase and quadrature baseband components, so its bandwidth is theoretically infinite [6], [42]. In practice, the SM bandwidth must be four to eight times the signal bandwidth [6]. Broadband SMs are power-inefficient, so even if the PA is highly efficient, the overall efficiency of the ET system will be degraded due to the low SM efficiency, as shown in equation (2.35) [15]. Thus, ET is also not viable for signal bandwidths in the hundreds of MHz required by 5G.

$$\eta_{total} = \eta_{PA} \cdot \eta_{SM} \tag{2.35}$$

Improvements to the ET PA have been proposed in the literature. In [6], the authors propose to track the envelope squared or to the fourth power, which eliminates the square root function: the required bandwidth of the SM is only two or four times the baseband signal's bandwidth. This improves  $\eta_{SM}$  significantly, at a small linearity penalty. The design in [15] features a soft-switching buck converter that eliminates overlap in the SM drain current and voltage waveforms, improving  $\eta_{SM}$ . However, in general, ET is not a popular OBO efficiency-enhancement technique in state-of-the-art publications in the literature.

#### 2.3.2 Outphasing Power Amplifiers

The outphasing technique is described in [16], [18]. A signal processor decomposes an amplitude- and phase-modulated signal  $s_{in}(t)$  into two phase-modulated, constant-amplitude signals  $s_1(t)$  and  $s_2(t)$  as shown in equations (2.36)–(2.38).  $s_{1,2}(t)$  are then amplified using two PAs and combined at the output to form an amplified version of  $s_{in}(t)$ . Since both PAs always operate at a constant  $P_{in}$ , they can be nonlinear and highly efficient topologies. The outphasing output combiner network (OCN) can be either isolated or non-isolated. Figure 2.12 a) shows a block diagram of an outphasing PA.

$$s_{in}(t) = A(t)\cos(\omega t + \phi(t)) = s_1(t) + s_2(t)$$

(2.36)

$$s_{1,2}(t) = \frac{A_{max}}{2} \cdot \cos\left[\omega t + \phi(t) \pm \cos^{-1}\left(\frac{A(t)}{A_{max}}\right)\right] = \frac{A_{max}}{2} \cdot \cos[\omega t + \phi(t) \pm \theta(t)] \qquad (2.37)$$

$$\theta(t) = \cos^{-1}\left(\frac{A(t)}{A_{max}}\right) \tag{2.38}$$

Figure 2.12 Block diagrams of an: a) Outphasing PA, b) Isolated OCN, c) Non-isolated OCN

With an isolated OCN, shown in Figure 2.12 b), each PA sees a load of  $R_{opt}$  regardless of the other PA's output signal, so both PAs always operate at peak  $\eta_D$ . However, while the PAs always operate at  $P_{sat}$ ,  $P_{out}$  is proportional to  $A^2(t)$ . The excess power must be dissipated in the OCN, which is lossy. Thus, no OBO efficiency enhancement results: the only benefit is linearity.

Chireix [43] proposed a non-isolated OCN, shown in Figure 2.12 c). The output impedance of each PA is modulated by the output of the other PA. The impedances seen by each PA are given in equation (2.39) [36], [41], [43]:

$$Z_{1,2} = \frac{R_L}{2} \cdot [1 \mp j \cdot \tan(\theta)] = R_{opt} \cdot [1 \mp j \cdot \tan(\theta(t))]$$

(2.39)

As  $P_{out}$  decreases,  $\theta(t)$  increases and  $Z_{1.2}$  both increase, reducing the power output by each PA. Thus, the sum of the PA output powers equals  $P_{out}$  and the OCN is lossless. However, the load modulation also produces an imaginary impedance component, which degrades PA efficiency and linearity. Therefore, the Chireix OCN also includes compensating reactances  $\pm jX$  to restore the impedances  $Z_1$  and  $Z_2$  to a real value for a specific OBO level. Figure 2.13 a) shows  $Z_1$  and  $Z_2$  for both PAs with various levels of Chireix compensation. The resulting outphasing efficiency profiles, with peaks at the chosen OBO level and at  $P_{sat}$ , are shown in Figure 2.13 b).

The Chireix outphasing PA offers good OBO efficiency enhancement when handling high PAPR communication signals [1], [6], [8], [11], [15]–[16], [18], [22], [44]. However, the signal separation is very computationally intensive and requires a separate computer [16] or field-programmable gate array [18]. The baseband processor's power consumption is not accounted for in reported efficiency figures [16], [18], which is not a realistic representation of the outphasing system performance. Furthermore,  $\theta(t)$  is a nonlinear function of the baseband signal, so the signal processor's bandwidth requirement is broader than the signal bandwidth, increasing complexity and power consumption [16].

Figure 2.13 Chireix outphasing PA at various OBO levels: a) Load modulation, b) Efficiency profiles

Improvements to the outphasing PA have been proposed in the literature. The outphasing PA in [18] uses broadband continuous class F PAs for improving the overall system bandwidth, and the authors in [16] propose a multi-mode outphasing PA with multiple branches in the Chireix OCN that can be switched on and off, providing OBO efficiency enhancement at various levels. However, the bandwidth limitations and high baseband system complexity per signal chain make the outphasing PA impractical for broadband 5G signals and MIMO applications.

#### 2.3.3 Doherty Power Amplifiers

The DPA is an OBO efficiency enhancement technique based on load modulation occurring entirely in the RF domain without any signal processing. The basic DPA architecture uses two transistors, the main (or carrier), and the auxiliary (or peaking), connected as shown in Figure 2.14 [37].

Figure 2.14 Block diagram of a conventional DPA

The basic DPA operation is derived in [37] and presented in this section. The main transistor is designed to reach peak efficiency at a certain OBO level  $P_{OBO}$ , while the auxiliary transistor is off. Then, for  $P_{OBO} \le P_{out} \le P_{sat}$ , the auxiliary transistor begins to turn on, modulating the load impedance seen by the main transistor to maintain its peak efficiency until  $P_{sat}$ , where both transistors reach peak efficiency. Thus, the overall DPA has efficiency peaks at  $P_{OBO}$  and  $P_{sat}$ .

Proper DPA operation requires the main and auxiliary transistor currents  $I_m$  and  $I_a$  to follow the profiles in equations (2.40) and (2.41), respectively.  $I_m$  is proportional to the normalized input voltage  $v_{in}$  and reaches its peak value  $I_{m,sat}$  when  $v_{in} = 1$ .  $I_a$  remains 0 (off) until  $v_{in} = 1/\beta$ , where  $\beta$  represents the OBO level, then linearly rises towards its peak value  $I_{a,sat}$  at  $v_{in} = 1$ .

$$I_m = I_{m,sat} \cdot v_{in}, \qquad 0 \le v_{in} < 1$$

(2.40)

$$I_{a} = \begin{cases} 0, & 0 \le v_{in} \le 1/\beta \\ \frac{I_{a,sat}}{1 - 1/\beta} \cdot (v_{in} - 1/\beta), & \frac{1}{\beta} \le v_{in} \le 1 \end{cases}$$

(2.41)

To ensure the DPA reaches peak efficiency at  $P_{OBO}$  ( $v_{in}=1/\beta$ ) and  $P_{sat}$  ( $v_{in}=1$ ), the fundamental voltage amplitude of the main transistor ( $V_m$ ) must be maximized at  $P_{OBO}$  and  $P_{sat}$ , and that of the auxiliary transistor ( $V_L$ ), at  $P_{sat}$ . Let  $R_{opt}$  be the optimum load resistance of the main transistor at  $P_{sat}$ . Then, the optimum load resistance of the main transistor at  $P_{OBO}$  and aux. transistor at  $P_{sat}$  are given by  $R_{opt,OBO}$  and  $R_{opt,aux}$ , respectively.

Since  $I_{m,OBO}$  is  $\beta$  times lower than  $I_{m,sat}$ , the following equation for  $R_{opt,OBO}$  is obtained:

$$R_{ont,OBO} = \beta \cdot R_{ont} \tag{2.42}$$

Since  $I_{m,sat}$  and  $I_{a,sat}$  may not be equal, the values of  $R_{opt,aux}$  and  $R_{opt}$  are related as follows:

$$R_{opt,aux} = R_{opt} \frac{I_{m,sat}}{I_{a,sat}}$$

(2.43)

It can be shown that the circuit in Figure 2.14 can be designed to present the optimum load impedances to the transistors. Consider the ABCD matrix of the  $\lambda/4 = 90^{\circ}$  TL with  $Z_0 = Z_{01}$ :

$$\begin{bmatrix} A & B \\ C & D \end{bmatrix} = \begin{bmatrix} \cos\theta & j \cdot Z_{01} \cdot \sin\theta \\ j/Z_{01} \cdot \sin\theta & \cos\theta \end{bmatrix} = \begin{bmatrix} 0 & j \cdot Z_{01} \\ j/Z_{01} & 0 \end{bmatrix}$$

(2.44)

Thus, the voltage and current relationships of the DPA can be written as follows, where bolded symbols represent voltage and current phasors:

$$\begin{bmatrix} V_m \\ V_L \end{bmatrix} = \begin{bmatrix} jZ_{01} \cdot I_m' \\ -jZ_{01} \cdot I_m \end{bmatrix}$$

(2.45)

The appropriate phases of  $I'_m$  and  $V_L$  are set using the  $\lambda/4$  TLs at the main transistor output and auxiliary transistor input. Thus, the analysis can be performed using only magnitudes. Equation (2.45) becomes the following:

$$\begin{bmatrix} V_m \\ V_L \end{bmatrix} = \begin{bmatrix} Z_{01} \cdot I'_m \\ Z_{01} \cdot I_m \end{bmatrix} \tag{2.46}$$

Applying Kirchhoff's current law and Ohm's law at node  $V_L$  results in the following relationship:

$$I'_{m} = I_{L} - I_{a} = \frac{V_{L}}{R_{L}} - I_{a} \tag{2.47}$$

The impedance seen by each transistor is the ratio of its drain voltage to drain current. Using equations (2.46) and (2.47), the impedances  $Z_m$  and  $Z_a$  can be written as:

$$Z_{m} = \frac{V_{m}}{I_{m}} = \frac{Z_{01}(V_{L}/R_{L} - I_{a})}{I_{m}} = \frac{Z_{01}(Z_{01}I_{m}/R_{L} - I_{a})}{I_{m}} = \frac{Z_{01}^{2}}{R_{L}} - Z_{01}\frac{I_{a}}{I_{m}}$$

(2.48)

$$Z_a = \frac{V_L}{I_a} = Z_{01} \frac{I_m}{I_a} \tag{2.49}$$

Setting  $Z_m$ ,  $Z_a$  to their optimum values from equations (2.42) and (2.43) results in the following:

$$Z_{m,OBO} = R_{opt,OBO} \to \frac{Z_{01}^2}{R_L} - Z_{01} \frac{I_{a,OBO}}{I_{m,OBO}} = \frac{Z_{01}^2}{R_L} = \beta R_{opt}$$

(2.50)

$$Z_{m,sat} = R_{opt} \rightarrow \frac{Z_{01}^2}{R_L} - Z_{01} \frac{I_{a,sat}}{I_{m,sat}} = R_{opt}$$

(2.51)

$$Z_{a,sat} = R_{opt,a} \rightarrow Z_{01} \frac{I_{m,sat}}{I_{a,sat}} = R_{opt} \frac{I_{m,sat}}{I_{a,sat}}$$

(2.52)

Solving equations (2.50)–(2.52) results in the following values for  $Z_{01}$ ,  $R_L$ , and  $I_a/I_m$ :

$$Z_{01} = R_{ont} (2.53)$$

$$R_L = \frac{R_{opt}}{\beta} \tag{2.54}$$

$$\frac{I_{a,sat}}{I_{m,sat}} = \beta - 1 \tag{2.55}$$

The conventional DPA design uses equal-sized devices with  $I_{a,sat} = I_{m,sat}$ , with  $\beta = 2$ . The auxiliary transistor turns on at half the input drive level. Figure 2.15 a) and b) plot the corresponding current and voltage profiles, respectively.  $V_m$  rises linearly from  $v_{in} = 0$  to  $v_{in} = 0.5$ , then maintains its peak value, as desired.  $V_L$  rises proportionally to  $v_{in}$  which shows a useful feature of the DPA: it is theoretically linear, and any nonlinearities will be due to transistor nonidealities.

Figure 2.15 c) plots the load modulation of the main and auxiliary transistors:  $Z_m$  varies from  $R_{opt,OBO} = 2R_{opt}$  to  $R_{opt}$  and  $Z_a$  varies from  $\infty$  to  $R_{opt,aux} = R_{opt}$ . Figure 2.15 d) plots  $P_{out}$  for both transistors and the overall DPA against  $P_{in}$ , showing that the auxiliary transistor supplies the additional power to guarantee DPA linearity despite the main transistor load modulation. Figure 2.15 e) plots  $\eta_D$  for the main and auxiliary transistor, as well as the overall DPA, against  $P_{out}$ . This plot highlights the two efficiency peaks in the DPA, occurring at  $P_{sat}$  and  $P_{OBO}$ , which is 6 dB below  $P_{sat}$ . The efficiency of a class B PA is also plotted for comparison, showing the DPA efficiency enhancement factor of 2 at 6 dB OBO.

Figure 2.15 Conventional DPA: a) Current profiles, b) Voltage profiles, c) Load modulation, d) Power profiles, e) Efficiency profiles

The DPA architecture is very suitable for amplifying modern high-PAPR communication signals with high power efficiency, especially in base station applications [1]–[6], [8]–[26], [44], [46]. The main advantage of the DPA over other OBO efficiency enhancement techniques is its simplicity: it is a single input, single output architecture requiring no baseband signal processing unlike EER, ET, and outphasing PAs [1], [11]. This is highly beneficial in MIMO systems with multiple low-power PAs: any additional baseband processing would have to be multiplied by the number of PA units, which would take excessive power and space. Therefore, the DPA is the selected OBO efficiency enhancement technique in this work.

However, the conventional DPA formulation presented above suffers from bandwidth limitations: the  $\lambda/4$  TL has frequency-dependent characteristics, the output capacitance of the auxiliary transistor cannot be absorbed, and broadband phase alignment is difficult [1], [4], [8], [9], [14], [17], [19]–[21], [23]–[24], [44], [46]. Moreover, the conventional DPA with symmetric transistors is limited to 6 dB OBO efficiency enhancement: for higher PAPR signals, performance is limited [12], [44]. Furthermore, several non-idealities of real transistors lead to high nonlinearity in practical DPAs. The next section will cover practical DPA design challenges.

#### 2.4 Practical DPA Design Challenges

#### 2.4.1 Main and Auxiliary Device Biasing

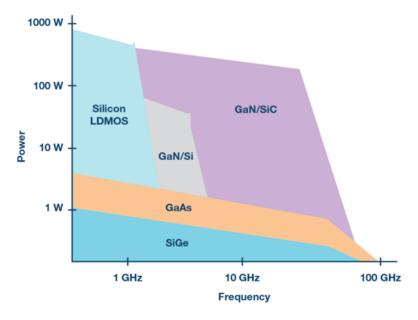

For synthesizing the main current  $I_m$ , which is proportional to  $v_{in}$ , a class B bias should be used in theory since it is perfectly linear. However, this assumption is based on an ideal FET transfer characteristic. The transfer characteristic of a practical Cree CGHV1F006 6 W 15 GHz transistor [47] is shown in Figure 2.16 a), exhibiting a soft transition between cutoff, linear, and saturation regions. This leads to a nonlinear  $g_m$  as shown in Figure 2.16 b). Due to the soft turn-on, class B is very nonlinear at low power in practice. However, in deep class AB ( $V_{GS} \approx -2.7 V$ , near class B), the theoretical nonlinearity of the class AB bias can be used to cancel the practical nonlinearity of the transistor, leading to the flattest  $g_m$  curve. This biasing point is selected for the best overall linearity.

The synthesis of  $I_a$  is significantly more complex. To obtain the required  $I_a$  curve with a turn-on point of  $v_{in} = 1/\beta$ , the transistor must be biased in class C. However, the peak transconductance of class C is significantly lower than in class B: for example, for  $\beta = 2$ ,  $I_a$  will only reach  $I_{max}/5$  instead of the required  $I_{max}/2$  for a turn-on point of  $v_{in} = 1/2$  [37]. Furthermore, the soft turn-on due to the nonlinear  $g_m$  is unavoidable in class C.

Figure 2.16 CGHV1F006 transistor: a)  $I_{ds}$  vs.  $V_{gs}$  transfer characteristic, b)  $g_m$  vs.  $P_{out}$  at various  $V_{gs}$

[37] proposes solutions to the low auxiliary peak current. One option is to use an auxiliary transistor 2.5 times larger than the main so that both transistors reach the same peak current. However, discrete transistors with specific size ratios are usually not available. Furthermore, larger transistors have larger parasitics, which degrade the bandwidth of the circuit. Alternatively, the input power can be split unevenly between the main and auxiliary transistors. By setting the input voltage  $V_{in,aux}$  2.5 times higher than  $V_{in,main}$ , both devices will reach the same peak current. However, this implies that only 13% of the power reaches the main transistor, reducing gain by 5.6 dB. Also, the uneven power divider is more difficult to realize than symmetric dividers. Another solution is to control the main and auxiliary inputs separately: the mixed-signal DPA replaces the single input RF source and power divider with a dual-channel signal generator to exercise full control over the main and auxiliary input signal magnitude and phase relationships and synthesize the desired current profiles exactly. However, both adaptive biasing and mixed-signal DPA suffer from additional design complexity.

#### 2.4.2 Device Capacitances and Package Parasitics

To represent the high-frequency behavior of the transistor, the simplified transistor model of Figure 2.3 must be augmented by adding parasitics components [37]–[39], as shown in Figure 2.17.

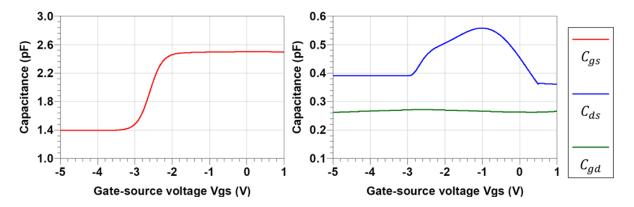

The intrinsic parasitics are part of the transistor die itself, and include gate-source, drain-source, and gate-drain capacitances:  $C_{gs}$ ,  $C_{ds}$ ,  $C_{gd}$ . These are nonlinear: their value depends on the applied voltages  $V_{gs}$  and  $V_{ds}$ . Figure 2.18 shows plots  $C_{gs}$ ,  $C_{ds}$ , and  $C_{gd}$  vs.  $V_{gs}$  for the CGHV1F006 transistor.

Figure 2.17 RF transistor equivalent circuit model

$C_{gs}$  is highly nonlinear, with an abrupt change between the cutoff and linear regions. This nonlinearity generates harmonics in  $V_{gs}$ , so it is crucial to design the gate biasing network (BN) to short-circuit the harmonics. The nonlinear  $C_{gs}$  also causes significant AM-AM and especially AM-PM distortion in PAs [37]–[39]. DPAs suffer from additional AM-PM distortion in the high-power region when the auxiliary transistor is turned on [2], [10], [13], [17], [25].  $C_{ds}$  is more linear than  $C_{gs}$ . However, its presence is still detrimental for PA design because it shifts the ideally resistive load termination  $R_{opt}$  into a reactive region, which is frequency-dependent [37]–[39]. Furthermore, a large value of  $C_{ds}$  will decrease the achievable bandwidth of the matching network. It is imperative to explore topologies for the DPA OCN that allow absorption of  $C_{ds}$  and other drain parasitics to allow access to the main and auxiliary transistor intrinsic current sources and realize the load modulation over broad bandwidths.

The feedback capacitor  $C_{gd}$  is significant despite its small size [37]–[39]. Since it forms a path between the output and input, the transistor is bilateral, which leads to potential instability. Furthermore,  $C_{gd}$  creates a dependence of the OMN on the IMN and vice-versa, so the matching network design becomes iterative.  $C_{gd}$  also causes an additional capacitance at the transistor input due to the Miller effect, given by equation (2.56), where  $A_{v}$  is the voltage gain of the transistor at the frequency of interest.

$$C_{in} = C_{as} + C_{ad} \cdot (1 + A_v) \tag{2.56}$$

The extrinsic parasitics are due to the packaging of the device and include bond wire resistance and inductance for all three terminals ( $L_x$  and  $R_x$ ), as well as pad capacitance for the gate and drain ( $C_{pg}$  and  $C_{pd}$ ) [37]–[39]. Given that these are physical components, not model parameters, they are linear components. Thus, they do not cause parasitics, but degrade the bandwidth and cause an additional shift

in the design space of the matching network on the Smith chart.  $L_s$  and  $R_s$ , also contribute to decreasing the gain due to source degeneration.

Figure 2.18 CGHV1F006 transistor intrinsic capacitances: a)  $C_{gs}$  vs.  $V_{gs}$ , b)  $C_{ds}$  and  $C_{gs}$  vs.  $V_{gs}$

### 2.4.3 Knee Region Effects

The ideal assumption that  $V_k = 0$  implies that the drain voltage can swing from 0 V to  $V_{max}$ . Hence,  $V_{DD}$  is set to  $V_{max}/2$  for maximum voltage swing. However, in a practical PA,  $V_k$  represents a significant portion of  $V_{DD}$ . For example, for the CGHV1F006 transistor with  $V_{DD}$  set to 28 V,  $V_k = 6 V$  or approximately 20% of  $V_{DD}$ . To maintain linearity, the voltage must not be allowed to fall below  $V_k$ . Thus, the fundamental maximum voltage swing is given by the following [37]–[38]:

$$V_1 = V_{DD} - V_k$$

The value of  $R'_{opt}$  and  $P'_{sat}$  (optimum load impedance and saturated power when considering the knee region) are thus the following, assuming class B bias [37]–[38]:

$$R'_{opt} = \frac{V_1}{I_{max}/2} = 2\frac{V_{DD} - V_k}{I_{max}}$$

(2.57)

$$P'_{sat} = \frac{V_1 \cdot I_{max}/2}{2} = \frac{(V_{DD} - V_k) \cdot I_{max}}{4} = \frac{V_{max} \cdot I_{max}}{8} - \frac{V_k \cdot I_{max}}{4}$$

(2.58)

The second term in equation (2.58) shows that the knee region effect reduces  $P_{sat}$  (and  $\eta_D$ ) significantly compared to the ideal class A or B. It is possible to trade off linearity for efficiency by choosing a load resistance between the original  $R_{opt}$  and  $R'_{opt}$ , allowing a slight intrusion into the knee region [37]–[38].

### 2.5 Literature Review of Sub-6 GHz Broadband High-Frequency DPAs

This section highlights the state-of-the-art DPAs in the literature that overcome the bandwidth limitations of the conventional DPA. To restrict the scope, the review focuses on DPAs that feature a single OBO efficiency peak. Multi-way DPAs also exist, with multiple auxiliary transistors that turn on at different OBO levels to provide more than two OBO efficiency peaks [37], [45].

#### 2.5.1 Broadband DPAs

[19] presents two 2.2–3.0 GHz, 40–42 dBm DPAs with 5–6 dB OBO where the OMN of each transistor and OCN are synthesized with the simplified real frequency technique (SRFT). The technique has a limitation: it can only maximize  $P_{out}$  and  $\eta_D$  at OBO or at saturation, leading to two distinct designs. Overall, neither of the two designs show proper DPA behavior: the efficiency curves show limited OBO  $\eta_D$  enhancement and performance is variable across the 2.2 to 3.0 GHz band.

[9] extends the work in [19] with a 2.2–3.7 GHz, 43–45 dBm, 6 dB OBO DPA realized using SRFT. The proposed dual-transformation SRFT algorithm can optimize  $P_{out}$  and  $\eta_D$  at both OBO and saturation. The resulting DPA achieves good OBO  $\eta_D$  enhancement behavior across the entire bandwidth, with some degradation in the low-frequency bands, which were not fully optimized.

[46] features a 3.0–3.6 GHz, 43–44 dBm broadband DPA with 6 dB OBO. The authors first match the individual transistors to 50  $\Omega$  by compensating the transistor parasitics ( $C_{ds}$  and  $L_D$ ). The OCN uses the conventional DPA architecture in Figure 2.14 with an additional  $\lambda/4$  TL to match the output from  $R_L$  to 50  $\Omega$ . However, the DPA behavior falls off quickly across the band: the auxiliary transistor turns on too late at 3.0 GHz and too early at 3.6 GHz, degrading  $\eta_D$  at OBO. Thus, this architecture cannot be considered truly broadband.