# A Serverless Discrete Optimization Service in the Cloud Based on Boolean Circuit Satisfiability

by

Jialing Song

A thesis presented to the University of Waterloo in fulfillment of the thesis requirement for the degree of Master of Applied Science in Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2023

© Jialing Song 2023

### Author's Declaration

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### Abstract

This thesis discusses the implementation of a serverless cloud service designed for solving discrete optimization problems encoded as boolean circuit satisfiability. Boolean circuit satisfiability problem involves determining whether an input assignment exists that satisfies a given boolean circuit. A cloud service is a platform that offers on-demand computing resources and services over the Internet. In a serverless setup, the service automatically manages and scales resources, eliminating the need for manual server management.

The main objective of this thesis is to provide a comprehensive and efficient approach to address problems in NP (nondeterministic polynomial time) by utilizing boolean circuit satisfiability. Our novel cloud service offers clients a more universal, efficient, and userfriendly solution for solving problems in NP.

We proposed an enhanced boolean logical circuit that incorporates sub-circuits capable of performing mathematical operations, simplifying the reduction process and expanding the potential to tackle problems in NP across various domains. Our motivation for this work arises from the fact that the augmented boolean circuit satisfiability problem is NP-complete, and a wide range of discrete optimization problems can be reduced to it. By leveraging a reduction to the proposed enhanced version of boolean circuit satisfiability problem and using oracles such as conjunctive normal form (CNF) or Integer Linear Programming (ILP) solvers, our service can efficiently address problems in NP in which the decision version can be reduced to the improved circuit satisfiability problems within polynomial time.

This thesis covers in-depth knowledge about the fundamentals of computational complexity, presenting reductions from each of Karp's 21 NP-complete problems to the Circuit-SAT problem, demonstrating the versatility and applicability of our approach. Additionally, we discuss a software library we have built that enables the construction of circuits as well, allowing users to efficiently represent and solve problems using our cloud service. Furthermore, the thesis includes details about the service's working principles and deployment aspects.

### Acknowledgements

I would like to sincerely express my gratitude to my graduate supervisor, Professor Mahesh Tripunitara, for his patient guidance and continuous support throughout my master's learning journey. His mentorship has been invaluable in shaping my academic growth and development.

I would like to extend my appreciation to Rahul Punchhi and Liran Tao, for their warmhearted help and support throughout my graduate career.

### Dedication

This is dedicated to my parents Jie and Xiaoqian.

# **Table of Contents**

| Author's Declaration ii |       |           |                                               | ii           |  |

|-------------------------|-------|-----------|-----------------------------------------------|--------------|--|

| A                       | bstra | ict       |                                               | iii          |  |

| A                       | cknov | wledge    | ments                                         | iv           |  |

| D                       | edica | tion      |                                               | $\mathbf{v}$ |  |

| Li                      | st of | Figure    | e <b>s</b>                                    | viii         |  |

| Li                      | st of | Abbre     | eviations                                     | ix           |  |

| Li                      | st of | Symbo     | ols                                           | xi           |  |

| 1                       | Intr  | roduction |                                               |              |  |

|                         | 1.1   | Comp      | utation Complexity                            | 2            |  |

|                         |       | 1.1.1     | Problems and Algorithm                        | 2            |  |

|                         |       | 1.1.2     | Decision Problem and Optimization Problem     | 2            |  |

|                         |       | 1.1.3     | Deterministic and Non-deterministic Algorithm | 3            |  |

|                         |       | 1.1.4     | Reduction                                     | 4            |  |

|                         |       | 1.1.5     | Computation Complexity Classes                | 4            |  |

|                         | 1.2   | Logica    | l Circuits and Circuit Satisfiability Problem | 5            |  |

|                         | 1.3   | The Fa    | amous Karp's 21 NP-complete Problems          | 8            |  |

| 2 Problem Solving                  |                                                                                   |                                  | 13 |  |  |  |

|------------------------------------|-----------------------------------------------------------------------------------|----------------------------------|----|--|--|--|

| 2.1 Research Objectives            |                                                                                   |                                  |    |  |  |  |

|                                    |                                                                                   | 2.1.1 Problem examples           | 14 |  |  |  |

|                                    | 2.1.2 Traditional Solutions                                                       | 16                               |    |  |  |  |

|                                    | 2.2                                                                               | 2 Solution Ideas                 |    |  |  |  |

|                                    | 2.3 Ways of Reducing Karp's 21 NP-C Problems to Circuit-SAT Problems $\therefore$ |                                  |    |  |  |  |

| 3 The Circuit Construction Service |                                                                                   |                                  |    |  |  |  |

|                                    | 3.1                                                                               | Main Components                  | 39 |  |  |  |

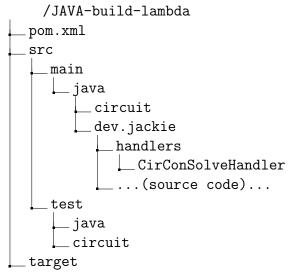

|                                    |                                                                                   | 3.1.1 JSON Encoding of a Circuit | 39 |  |  |  |

|                                    |                                                                                   | 3.1.2 Circuit Library            | 42 |  |  |  |

|                                    |                                                                                   | 3.1.3 Working Principle          | 47 |  |  |  |

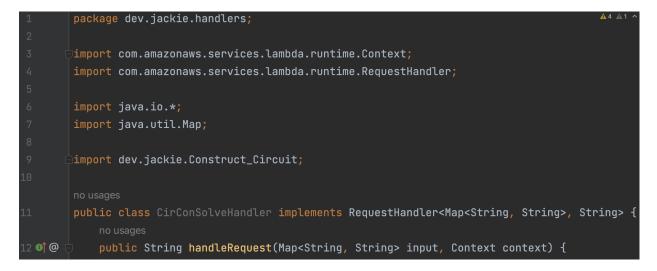

|                                    |                                                                                   | 3.1.4 AWS Lambda Deployment      | 55 |  |  |  |

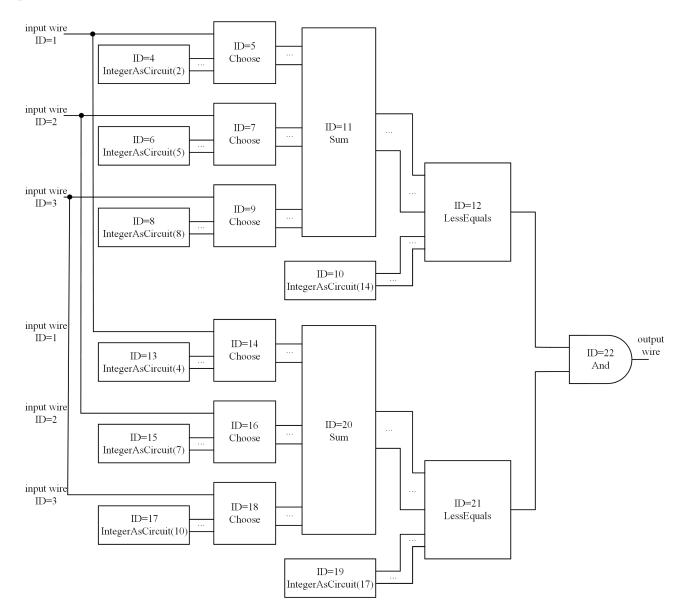

|                                    | 3.2                                                                               | Result Demonstration             | 60 |  |  |  |

| 4                                  | Sun                                                                               | nmary and Future Work            | 63 |  |  |  |

|                                    | 4.1                                                                               | Summary of the Results           | 63 |  |  |  |

|                                    | 4.2                                                                               | Future Work                      | 64 |  |  |  |

| R                                  | efere                                                                             | ences                            | 66 |  |  |  |

# List of Figures

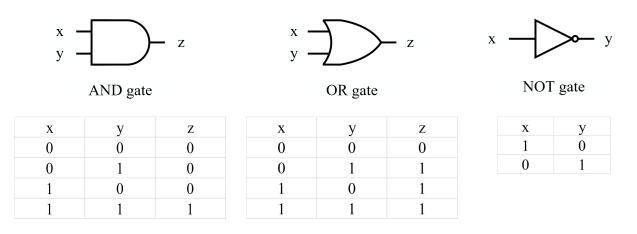

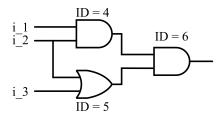

| 1.1 | Three basic logical gates with their gate's operation                                                                                                                                               | 6  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

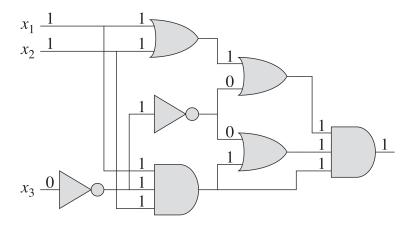

| 1.2 | Instance (a), which is satisfiable since the certificate $x_1 = 1, x_2 = 1, x_3 = 0$<br>of this circuit results in the final output being 1. Source: Adapted from<br>Introduction to algorithms [7] | 7  |

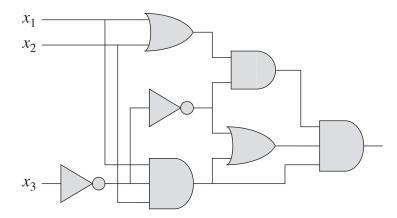

| 1.3 | Instance (b), which is unsatisfiable since there is no assignment to the inputs of this circuit that will cause the final output to be 1. Source: Adapted from Introduction to algorithms [7]       | 7  |

| 2.1 | The AND circuit.                                                                                                                                                                                    | 19 |

| 2.2 | The OR circuit.                                                                                                                                                                                     | 19 |

| 2.3 | The Bit-Not circuit                                                                                                                                                                                 | 20 |

| 2.4 | The IntegerAsCircuit circuit.                                                                                                                                                                       | 20 |

| 2.5 | The Sum circuit.                                                                                                                                                                                    | 20 |

| 2.6 | The LessEquals circuit.                                                                                                                                                                             | 21 |

| 2.7 | The Choose circuit.                                                                                                                                                                                 | 21 |

| 3.1 | An example circuit.                                                                                                                                                                                 | 41 |

| 3.2 | The handler function <i>handleRequest()</i> .                                                                                                                                                       | 58 |

| 3.3 | Adding the path to function $handleRequest()$ .                                                                                                                                                     | 59 |

| 3.4 | The Circuit-SAT problem reduced from the given knapsack problem                                                                                                                                     | 61 |

| 3.5 | The returned results for the satisfiable knapsack problem                                                                                                                                           | 62 |

| 3.6 | The returned results for the unsatisfiable knapsack problem                                                                                                                                         | 62 |

# List of Abbreviations

API Application Programming Interface 43, 55, 65

AWS Amazon Web Services 55

**BFS** Breadth-First Search 64, 65

CNF Conjunctive Normal Form 8, 10, 13, 16, 17

DAG Directed Acyclic Graph 5, 64, 65

**DIMACS** Discrete Mathematics and Theoretical Computer Science 17

ERWA Exponential Recency Weighted Average 18

**FaaS** Function as a Service 55

FVS Feedback Vertex Set 9, 26

IAM Identity and Access Management 65

**IC** Integrated Circuit 16

**IoT** Internet of Things 55

JSON JavaScript Object Notation 39

LRB Learning Rate Branching 18

MAB Multi-Armed Bandit 18

**NP** Nondeterministic Polynomial-time 1

**P** Polynomial-time 1

SAPS Scaling And Probabilistic Smoothing 17

${\bf SAT} \ {\rm Satisfiability} \ {\bf 13}$

**TSP** Traveling Salesman Problem 18

$\mathbf{vCPUs}\,$  virtual Central Processing Units 14

vGPUs virtual Graphics Processing Units 14

$\mathbf{VMs}\,$  Virtual Machines 15

**VPC** Virtual Private Cloud 15

**VSIDS** Variable State Independent Decaying Sum 18

# List of Symbols

- $\cap~$  The "cap" symbol, which is used to indicate the intersection operation between two sets. 10

- $\cup$  The "cup" symbol, which is used to indicate the union operation between two sets. 6, 10

- $\emptyset$  The "empty set" symbol, which is used to indicate a set contains nothing. 12

- $\forall\,$  The "for all" symbol, which is used to make universal general statements to every element in a set of objects. 2

- $\in~$  The "in" symbol, which is used to indicate the affiliation relationship between an element and a set. 2

- $\wedge$  The "and" symbol, which is used to indicate the AND operation. 6

- $\neg$  The "NOT" symbol, which is used to indicate the NOT operation. 6

- $\notin$  The "notin" symbol, which is used to indicate the affiliation relationship between an element and a set. 6

- $\subseteq\,$  The "subset equal" symbol, which is used to indicate the subset relationship between two sets. 10

- $\vee$  The "or" symbol, which is used to indicate the OR operation. 6

# Chapter 1 Introduction

With the rapid advancement of theoretical computer science, Nondeterministic Polynomialtime (NP) class has emerged as a prominent subject of investigation within the field of computational complexity classes. Numerous consequential computational problems arising in diverse domains such as science, engineering, and economics, can be effectively reformulated as problems in NP class. Effective resolutions of these challenges would yield substantial practical implications, including but not limited to enhancements in resource management methodologies, advancements in bio-molecular structural exploration, and the provision of more precise data analysis techniques. Additionally, research pertaining to the reduction of problems in NP and the development of efficient solving techniques holds the potential to offer insights into the long-standing and consequential "Polynomial-time (P) vs. NP" problem, that is, whether there exists a polynomial-time algorithm to solve the problem in NP. This question remains one of the most profound unresolved inquiries in computer science, and substantially impacts cryptography and many other domains related to security, given that numerous modern information security protocols are fundamentally constructed on the premise that  $P \neq NP$ .

This chapter first introduces the basic definition of abstract problem, algorithm, and computational complexity; then elicits the throughout research topic: problems in NP class. Then, a variety of examples of problems in NP and the process of reduction are illustrated. In the second part, the through-out-topic circuit satisfiability problem is introduced, which serves as the foundation for the solution proposed in the subsequent part of the thesis. In the end, 21 famous NP-complete problems are presented, which involve various categories of problems within the field of algorithms.

### 1.1 Computation Complexity

### 1.1.1 Problems and Algorithm

Problems in different fields of study are expressed in different formats. A statement of a "problem" in the computation area generally outlines the desired input and output relationship [7]. Besides, an "instance" of a problem is composed of the input needed to compute a solution to the problem. [7], and an "evidence" (a "certificate" or "witness") that is usually combined with a problem instance, is a piece of information that a deterministic polynomial-time algorithm can be used to verify the correctness. For example, the maximum value problem can be defined as:

**Input:** An array of *n* numerical elements:  $A = [a_1, a_2, ..., a_n]$ . **Output:** An element  $a_i$ , where  $1 \le i \le n$ , such that  $\forall a_i \in A$ , where  $1 \le j \le n$ ,  $a_j \le a_i$ .

A valid instance of this problem is given the input sequence A as [3, 7, 4, 2, 6, 8, 9, 0], and the corresponding certificate should be 9 since 9 is larger than or equal to any of the elements in array A.

Besides, it is of high necessity to introduce the concepts of "abstract problem" and "algorithm" because their further fine-grained classification and new definitions built upon them will be introduced later when computation complexity is involved.

Abstract Problem: Abstract problem is a binary relation on a set I of problem instance and a set S of problem solutions.<sup>[7]</sup>.

Algorithm: Algorithm is a computational procedure which takes a set of values as inputs and generates a set of values as outputs [7].

### 1.1.2 Decision Problem and Optimization Problem

**Decision problem:** A problem with an output that can only be Yes or No [16].

**Optimization problem:** A problem which requires obtaining the best solution (associated with a maximum or minimum value) among all feasible solutions [7].

For example, to find the shortest path between two vertices in an undirected unweighted graph, the optimization version of it presents in the form that given a graph G and a pair of vertices  $\langle u, v \rangle$ , what is the shortest path connecting u and v with the least number of edges? The decision version of a problem usually can be converted from the optimization version by adding boundaries on the associated value [7]. Therefore, the decision version of finding the shortest path is: given a graph G, a pair of vertices  $\langle u, v \rangle$ , and an integer k, if there exists a path from u to v which contains at most k edges?

The integer k mentioned above generally is the boundary of the related value for a possible solution. If there is an algorithm that could solve the decision version of a problem, then by modifying the boundaries on the associated value and other conditions, the optimization version can then be solved as well. Similarly, if an algorithm that could solve an optimization problem exists, then the decision version can be resolved by calculating the associated value based on the solution and comparing it to the boundary. Since the way of changing the boundary k and other attributes until reaching the extremum is usually more difficult than obtaining the related value of an optimized solution, the optimization version of a problem is considered "harder" than the decision version. The words "harder" and "easier" in this context refer to the fact that harder questions need more extra procedures to solve than easier ones.

In the finding shortest path example, if an algorithm exists for the optimization version (it returns the shortest path between u and v), the answer to the decision version can be obtained by counting the number of edges along this path and then comparing it to k. If the number of edges of the shortest path is even larger than the upper boundary k, then it is impossible to find another shortest path which satisfies this property, thus, the decision version should return "False"; otherwise, if the shortest path holds the condition, then the decision version is therefore "True". On the other hand, if there is an algorithm for the decision version, to get the shortest path in the optimization problem, first decrease k to find the number of edges in the shortest path. Then delete the start node (u) in G, and for every neighbour of u (denote as u'), ask if there exists a path from u' to v which contains at most k-1 edges. If returns "True", then repeat the above procedure, if returns "False", try the next u' instead, until finding the satisfied vertex. Finally, all the deleted vertices in order compose the shortest path.

### 1.1.3 Deterministic and Non-deterministic Algorithm

When focusings on decision problems, deterministic and non-deterministic algorithms can be defined as below:

**Deterministic Algorithm:** A class of algorithms which exist only one state at a time before terminating.

**Non-deterministic Algorithm:** A class of algorithms which not only allow multiple states at a time when running, and hold the attributes that:

1. If the correct answer for the decision problem is "True", then at least one of the end

states when the non-deterministic algorithm terminates should be able to interpret it as "True".

2. If the correct answer for the decision problem is "False", then **none** of the end states when the non-deterministic algorithm halts could be interpreted as "True".

The non-deterministic property comes from the fact that instead of picking up parameters according to a specific scheme in a deterministic algorithm, a non-deterministic algorithm picks parameters to compute without any considerations.

### 1.1.4 Reduction

Reduction is the step to prove the "hardness" relationship between two problems. An instance of a problem refers to a particular input to that problem; [7]. For two decision problems A and B, the reduction from A to B is valid if and only if:

- 1. For every instance of A, there exists a polynomial time algorithm to convert it to an instance for problem B.

- 2. Assume there is an algorithm for problem B, the answer for an instance of A is "True" if and only if the algorithm returns "True" for the transformed instance for B.

The reduction from A to B above indicates the difficulty of solving problem A is no harder than the difficulty of solving problem B. Thus, if there doesn't exist an algorithm for solving A within polynomial time, then neither does B.

### 1.1.5 Computation Complexity Classes

Computation complexity is defined for the decision version of a problem. Below are several most common computation complexity classes:

**P class:** The collection of all decisions problems that can be resolved with an algorithm in polynomial time (there exists a constant k and an algorithm whose time-efficiency is  $O(n^k)$ ) is in complexity class P.

**NP class:** The collection of all decisions problems that can be resolved with a nondeterministic algorithm in polynomial time (there exists a constant k and a non-deterministic algorithm whose time-efficiency is  $O(n^k)$ ) is in complexity class NP. Besides, a problem can also be categorized in NP if given a claimed solution of the problem, it can be verified within polynomial time.

**NP-complete class:** The collection of all decision problems in NP that any other problems in NP can be reduced to them within polynomial time.

Problems in NP are ubiquitous in everyday life, for example, checking if a given solution for Sudoku  $(n \times n)$  is valid can be accomplished in polynomial time in n, but it is not possible to find a solution within polynomial time, however, if there exists a non-deterministic algorithm which can non-deterministically pick numbers for each slot then verify, then return a correct solution is possible within polynomial time.

### 1.2 Logical Circuits and Circuit Satisfiability Problem

A logical circuit can be defined as a Directed Acyclic Graph (DAG) which consists of vertices and directed edges with the following constraints:

- Every directed edge is assigned a boolean value (0 or 1) and signifies the information flow from an input terminal to an output terminal in the overall graph.

- Every vertex in the graph represents an input or output terminal or a logical gate (AND gate, OR gate, and NOT gate). Logical gates work like functions that are able to conduct logical operations based on their own input boolean values, while input and output terminals are the boolean information sending and receiving elements in a graph.

Figure 1.1: Three basic logical gates with their gate's operation.

AND gate performs "and" operation where  $z = x \land y$ , and z = 1 if and only if both input x and y are assigned with boolean value 1. OR gate performs "or" operation where  $z = x \lor y$ , and z = 1 if either input x or y, or both are assigned the boolean value 1. NOT gate performs the negation of the original input value, where  $y = \neg x$ .

• The indegree and outdegree of a NOT gate are both 1, while for AND and OR gates, their indegree is 2 and outdegree is 1 for each. The input terminal has an indegree of 0 and an outdegree of 1, while the output terminal has an indegree of 1 and an outdegree of 0.

A logical circuit G can also be composed of two sub-circuits  $G_1$  and  $G_2$ , where  $G_1 = \langle V_1, E_1 \rangle$ ,  $G_2 = \langle V_2, E_2 \rangle$ . The two sub-circuits hold properties that  $\forall u \in V_1, u \notin V_2, \forall e \in E_1, e \notin E_2$  and vice versa. There are two ways to combine sub-circuits:

- 1.  $G = G_1 \cup G_2$ : graph G is the union of  $G_1$  and  $G_2$ . The number of the input terminals in G is the sum of the number of input terminals in  $G_1$  and  $G_2$ , and the same goes for output terminals as well. Besides,  $G_1$  and  $G_2$  do not share any common vertices or edges. Since both  $G_1$  and  $G_2$  are acyclic, their union does not contain any cycle either.

- 2. In the second way of combining  $G_1$  and  $G_2$ , adjustments to  $G_1$  and  $G_2$  is made: new edges are established to connect vertices between sub-graph  $G_1$  and  $G_2$ . Assume  $u_1 \in V_1, u_2 \in V_2$ , in new graph G, there  $\exists e \in E$  such that  $e = \langle u_1, u_2 \rangle$  or  $e = \langle u_2, u_1 \rangle$ . In addition to the original  $G_1$  and  $G_2$  present in G, there are new edges directed from vertices in G1 to vertices in G2, or from vertices in G2 to vertices in G1. The constraint to this modification is to guarantee G is acyclic.

A circuit satisfiability (Circuit-SAT) problem can be stated as: given a logical circuit with a single output terminal, finding a possible assignment of boolean values to the edges originating from the input terminal, such that the value of the edge leading to the output terminal is 1. Below are two instances of the circuit satisfiability problem, and the only difference between them is that the OR gate in the upper right becomes an AND gate.

Figure 1.2: Instance (a), which is satisfiable since the certificate  $x_1 = 1, x_2 = 1, x_3 = 0$  of this circuit results in the final output being 1. Source: Adapted from Introduction to algorithms [7]

Figure 1.3: Instance (b), which is unsatisfiable since there is no assignment to the inputs of this circuit that will cause the final output to be 1. Source: Adapted from Introduction to algorithms [7]

Circuit-SAT problem can be proved to be in NP-complete class by reducing boolean

satisfiability problem to it, which is the first problem to be proved in the NP-complete class by Stephen Cook in 1971[6]. The service proposed in this thesis is based on solving circuit satisfiability problems reduced from other problems in NP, more details will be introduced in chapters 2 and chapter 3.

### 1.3 The Famous Karp's 21 NP-complete Problems

In 1972, Karp listed 21 famous NP-complete computational decision problems by reducing boolean satisfiability problem to each one of them. [15]. These classical problems not only come in various forms, with traces found in everyday life, but also serve as the foundation for many more complex problems in NP-complete. Below is the list of the decision version and optimization version of Karp's 21 problems which are NP-complete.

- 1. Boolean satisfiability problem: Given a boolean formula in Conjunctive Normal Form (CNF), if the variables can be assigned in a way that makes the CNF formula true.

- 2. 0-1 Integer programming: Given integer matrix  $\mathbf{C}$  and an integer vector  $\mathbf{d}$ , if there exist a 0-1 vector  $\mathbf{x}$  such that  $\mathbf{C}\mathbf{x} = \mathbf{d}$ .

- 3. Clique problem

- Decision version: Given an undirected graph  $G = \langle V, E \rangle$  and an integer k, if there exists a clique of size k for graph G?

- Optimization version: Maximize integer k such that find out the maximum clique in a given undirected graph G.

- 4. Set packing

- Decision version: Given a set  $S = \{S_1, \ldots, S_n\}$ , a universal set U, and an integer k, where collection S contains subsets of U. If subsets in S can form a set C of size k such that all subsets in C are pairwise disjoint?

- Optimization version: Find the set C which holds the maximum number of mutually disjoint subsets (k).

- 5. Vertex cover problem

- Decision version: Given a pair  $\langle G, k \rangle$ , where  $G = \langle V, E \rangle$  is an undirected graph and  $k \in \{1, \dots, |V|\}$ , does G have a vertex cover of size  $\leq k$ ?

- Optimization version: Find the smallest vertex cover of graph G such that the size of vertex cover k reaches its minimum.

- 6. Set covering

- Decision version: Given a set  $S = \{S_1, \ldots, S_n\}$ , a universal set U and an integer k, where S is a collection of subsets of U. If there exists a k-size (or less) set cover C, which consists of subsets in S and its union is U?

- Optimization version: Find the smallest set cover for set S such that the size of set cover k reaches its minimum.

- 7. Feedback node set

- Decision version: Given a graph  $G = \{V, E\}$  and an integer k, if there exists a k-size Feedback Vertex Set (FVS) such that if all the vertices in FVS are removed, the whole graph will have no circles.

- Optimization version: Find the smallest FVS for graph G such that the size of FVS k reaches its minimum.

- 8. Feedback arc set

- Given a graph  $G = \{V, E\}$ ,  $E = \{e_1, \ldots, e_n\}$ , and an integer k, if there is a k-size feedback arc set which is a set of edges such that G will not contain any circles if all edges in feedback arc set are removed.

- Optimization version: Find the smallest feedback arc set for graph G such that the size of feedback arc set k reaches its minimum.

- 9. Directed Hamilton circuit

- Decision version: If there exists a Hamiltonian path in the directed graph  $G = \{V, E\}$  which makes it possible for visiting each vertex exactly once.

- Optimization version: Find the longest Hamiltonian path in directed graph G.

- 10. Undirected Hamilton circuit

- If there exists a Hamiltonian path in the undirected graph  $G = \{V, E\}$  which makes it possible for visiting each vertex exactly once.

- Optimization version: Find the longest Hamiltonian path in undirected graph G.

- 11. Satisfiability with at most 3 literals per clause: Given a boolean formula in 3-CNF format, if the variables can be assigned in a way that makes the 3-CNF formula true.

- 12. Chromatic number (Graph Coloring Problem): Given a graph  $G = \{V, E\}$  and an integer k, if there is a way/function  $c(\cdot)$  of labelling k colours to all vertices such that no two vertices connecting by an edge share the same colour,  $c(u) \neq c(v)$  for  $\forall (u, v) \in E$ .

- 13. Clique cover

- Decision version: Given a graph  $G = \{V, E\}$  and an integer k, if there exists a way of partitioning all the vertices V in the graph G into k cliques.

- Optimization version: Minimize the number of cliques k, such that find the smallest clique cover.

- 14. Exact cover

- Decision version: Given a collection set  $S = \{S_1, \ldots, S_n\}$ , a universe set U and an integer k, where collection set S contains subsets of set U. If there exists a subcollection  $S^*$  of S whose size is k, such that every item in U is contained and only contained once in  $S^*$ .

- Optimization version: Minimize k, the size of the subcollection  $S^*$ , such that find the smallest exact cover.

- 15. Hitting set

- Decision version: Given a set  $S = \{S_1, \ldots, S_n\}$ , a universal set U, and an integer k, where S is a collection of subsets of U, and  $S_1 \cup \ldots \cup S_n = U$ . If there exists a k-size hitting set H, which is a subset of U, such that for every collection  $S_i \in S$ , the number of items shared by H and  $S_i$  is only 1,  $|H \cap S| = 1$ .

- Optimization version: Minimize the number of items in hitting set H, so that the size of H reaches its minimum.

- 16. Steiner tree

- Decision version: Given an instance of a Steiner tree problem in an undirected graph,  $\{G = \langle E, V \rangle, T, k\}, V = \{u_1, \ldots, u_n\}$  and  $E = \{e_1, \ldots, e_m\}$ , with non-negative edges  $w(e_i) \ge 0$ . Terminal vertex set T is a subset of vertices of set V, and  $k \in \mathbb{Z}$ . Is there a tree  $H = \langle E', V' \rangle$ , which is a subgraph of G, such that  $T \subseteq V'$  and the weight of the tree  $w(H) \le k$ .

- Optimization version: Minimize k to find the minimum cost tree that connects all the terminals.

- 17. 3-Dimensional matching

- Decision version: Given a 3-dimensional matching (3DM) problem denotes as  $\{X, Y, Z, T, k\}$ , where set X, Y and Z are three finite sets with no sharing elements, and set  $T = X \times Y \times Z$ , that is,  $T = \{t_1, \ldots, t_s\}$ ,  $t_i = \langle x_i, y_i, z_i \rangle$  where  $x_i \in X, y_i \in Y$  and  $z_i \in Z$ . A 3-dimensional matching  $M, M \subseteq T$ , holds the property that for  $\forall t_i \neq t_j, t_i \in M, t_j \in M$ , and  $t_i = \langle x_i, y_i, z_i \rangle$ ,  $t_j = \langle x_j, y_j, z_j \rangle$ , such that  $x_i \neq x_j, y_i \neq y_j$ , and  $z_i \neq z_j$ . If the size of the given 3DM is larger or equal to k?

- Optimization version: Maximize the number of elements in *M* to find the biggest 3-dimensional matching set *M*.

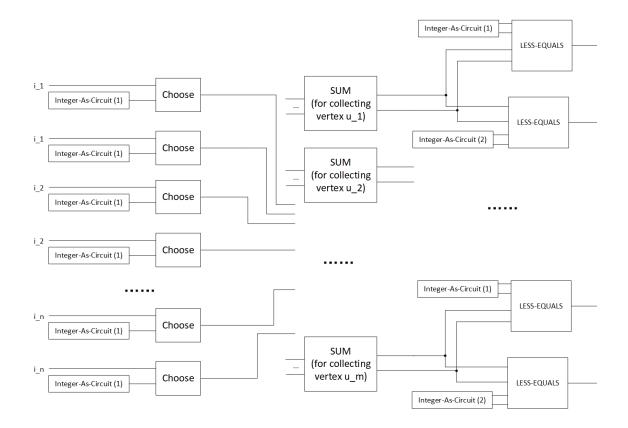

- 18. Knapsack

- Decision version: Given an integer k, a group of n items each has value:  $\{v_1, \ldots, v_n\}$ , and weight  $\{w_1, \ldots, w_n\}$ . Now by picking items into a knapsack, which has a limit to the weight of the picked items W, if the total value of picked items is greater than or equal to k.

- Optimization version: What is the maximum value the knapsack can carry?

- 19. Job sequencing

- Decision version: A description of job-shop scheduling problems: given two finite sets M = {M<sub>1</sub>,..., M<sub>m</sub>} (for machines) and J = {J<sub>1</sub>,..., J<sub>n</sub>} (for jobs), where there are m machines in the processing system, and n jobs are required to be processed. For each J<sub>i</sub>, there is a list L<sub>i</sub> = [(M<sub>ord1</sub>, t<sub>ord1</sub>), (M<sub>ord2</sub>, t<sub>ord2</sub>), ..., (M<sub>ordm</sub>, t<sub>ordm</sub>)] assigned to it to describe in what order J<sub>i</sub> should be completed on different machines including its corresponding time, and L = [L<sub>1</sub>,..., L<sub>n</sub>]. Every job here needs to go through all machines to be processed. Besides, each job must be processed in the order of the process. The task of scheduling is to arrange the processing, scheduling and sorting of all jobs, now given an integer k, if the time cost by the scheduled sequence of jobs is less than or equal to k.

- Optimization version: How to arrange the order of jobs on each machine so that the total time spent is the least.

- 20. Partition: Given an instance of partition problem S, where S is a multi-set of positive integers. If the set S can be partitioned into two sets  $S_1$  and  $S_2$ , and the sum of all

the elements in  $S_1$  equals the sum of all the elements in set  $S_2$ .

- 21. Max cut

- Decision version: Given a graph G = E, V and an integer k, where  $V = \langle u_1, \ldots, u_n \rangle$  and  $E = \langle e_1, \ldots, e_m \rangle$ . If there exists a subset of vertex  $S_1$  such that the number of edges of connecting set  $S_1$  and its complementary subset  $S_2$  is larger than or equal to k.  $S_1 \cap S_2 \emptyset$  and  $S_1 \cup S_2 = S$ .

- Optimization version: Find the subset  $S_1$  which makes the number of edges connecting it and  $S_2$  achieve its maximum.

# Chapter 2

## **Problem Solving**

The diverse forms of problems within the NP class often permit the utilization of wellestablished strategies to address specific problems. For example, a boolean satisfiability problem can be solved by using an SAT solver. However, a notable gap persists in finding a unified solution template for problems in NP. At this stage, the reduction process becomes especially crucial in identifying inherent connections among problems within the same computational complexity class, since it helps identify the hardness of solving a problem and makes it possible to obtain the solution by solving other problems.

The core focus of this thesis revolves around addressing problems in NP in a universal, efficient, and convenient manner. This thesis proposes an optimization service grounded in boolean circuit satisfiability, designed to effectively address problems in the NP complexity class while providing sound and logical solutions. In this chapter, the problems to be tackled are provided and well examined first, along with the most common ways of solving problems in NP class nowadays: by using a CNF Satisfiability (SAT) solver. The solution concepts underlying the service proposed in this thesis are introduced next. Furthermore, drawing upon the service's approach to solving problems in NP, this chapter illustrates the application of the corresponding solving methods to Karp's 21 NP-Complete problems, ultimately offering practical resolutions for each.

### 2.1 Research Objectives

### 2.1.1 Problem examples

The research and development purpose of this service is to help people solve common problems in NP more conveniently. In the first chapter, the well-known 21 Karp's NP-C problems are well elucidated, encompassing a broad spectrum of applications and forming the basis for numerous intricate problems. For instance, the circuit satisfiability problem serves as a crucial component in computer science, facilitating the verification of logical reasoning system consistency. Similarly, the job sequencing problem frequently arises in production planning to optimize job and task scheduling sequences. Furthermore, the clique cover (partition into cliques) problem in an undirected graph, holds significant value in social network analysis as it aids in identifying community structures and social circles.

Apart from the aforementioned 21 problems in NP-Complete class, there are many other problems composed of naive problems in NP that are also the objects that this service intends to solve. Below are two illustrative questions:

- 1. A problem that may arise in distributed cloud resource management services is the allocation of supply resources to meet the demands of a distributed cloud environment. This issue involves determining how resources should be allocated to fulfill the requirements of a particular resource. To well present this problem, two types of resources are represented separately in undirected graphs.

- **Demand Graph**: demonstrates the arrangement/architecture of the intended task and the resources it occupies, which is a set of sub-graphs consisting of nodes and edges.

- **Supply Graph**: demonstrates the arrangement/architecture of the resources that is provided and can be used, which is a set of sub-graphs consisting of nodes and edges.

Both the demand graph and supply graph have node attributes and edge attributes, which is the way to illustrate resources.

• Node Attributes: node is used for representing hardware resources, and its attributes may include but are not restricted to the number of virtual Central Processing Units (vCPUs), virtual Graphics Processing Units (vGPUs), storage, and other components within compute or storage units (such as bare metal servers or database instances).

• Edge Attributes: edge is used for representing resources associated with network connection services, and its attributes may include but are not restricted to the time needed to establish Virtual Private Cloud (VPC) connections, or the cost involved in connecting different clouds.

For both vertices and edges, attributes are always an integer in this case. Finally, the problem requires a way of placement from the demand graph to the supply graph. To be more specific, "placement" means to allocate nodes/edges from the demand graph to nodes/edges of the supply graph, which implies that the resources a supply node/edges provide are capable of implementing the task from demand nodes/edges that are placed into it. Based on common sense, there are several rules for the placement:

- Demand nodes are to be placed on supply nodes only.

- A demand edge is placed on zero or one supply edge. Assume a vertex has an edge to itself with infinite value for all attributes, on which a demand edge may be placed.

- For a specific supply node/edge, it should be satisfied that for every single attribute it has, the sum of that specific attribute values from all the corresponding demand nodes/edges placed into it should be less than or equal to the single attribute value from that supply node/edge.

Besides, customized anti-affinity constraints can also be added as rules for the placements, such as certain two nodes in the demand graph cannot be placed in a same supply node, or certain two demand nodes have to be placed together in a node in the supply graph.

- 2. Another strong example relates to scheduling Virtual Machines (VMs) in server to prevent information leakage in side channels [14]. To enhance service efficiency and optimize resource utilization in cloud computing, it is typical for multiple clients to share a single server running multiple VMs. However, this approach exposes a vulnerability as attackers can exploit the lack of complete isolation between different VMs at the physical layer to execute sub-channel attacks, leading to the unauthorized disclosure of sensitive information from victims through these sub-channels. This problem involves three main subjects: epoch, virtual machine and server.

- **epoch**: One discrete period of time.

- VM: A VM is a unit of computation or execution used for processing client tasks. A client may possess several VMs and the workload on VMs may last several epochs.

• Server: A physical machine equipped with computational capacity that is responsible for running a certain number of VMs.

The placement of a VM on a server is considered valid when the server has sufficient capacity to run all the VMs it hosts at every epoch, which is similar to the problem introduced in the first example. Besides, this problem becomes more intricate as it requires addressing the issue of minimizing mutual sub-channel information leakage between different clients by changing the VMs running in each server at different epochs. Additionally, this thesis illustrates several scenarios for information leakage as well [14]:

- **Replication**: This situation arises when a malicious VM is co-located with multiple VMs belonging to the victim. Consequently, sensitive information runs the risk of being duplicated, as the malicious VM can intercept and extract various informative data fragments.

- Collusion: This scenario occurs when the victim's VMs are confronted by multiple attackers' VMs, all of which can collude to extract a greater amount of valuable information within a fixed epoch. For instance, each attacker's VM can be assigned the task of intercepting different pieces of information, thereby increasing the overall effectiveness of the data extraction process.

By obeying the rules for calculating the potential leaked data, it presents a significant challenge for cloud service providers to devise a strategy for distributing clients' (also possibly to be a potential attacker) VMs across different servers at different time periods.

### 2.1.2 Traditional Solutions

### SAT Solver

Although NP-Complete problems cannot be solved within polynomial time of their inputs, there are ongoing efforts to develop programs that can efficiently tackle such problems. Among these, SAT solvers have emerged as particularly notable, due to their success in solving the boolean satisfiability problem. A SAT Solver takes a boolean formula in CNF form as input, and returns the answer if the formula is satisfiable or not, if so, it will provide one feasible solution as well. SAT Solver has been widely used in many fields since its release, including artificial intelligence, Integrated Circuit (IC) design, software verification, electronic hardware design etc.

SAT solvers typically necessitate a CNF input, commonly stored in a file formatted according to the Discrete Mathematics and Theoretical Computer Science (DIMACS) standard. The DIMACS format serves as a widely adopted standard for representing CNF problems, making it the prevalent input format for SAT solvers, and enables SAT solvers to efficiently process and solve boolean satisfiability problems. DIMACS files typically consist of two sections: the header and clause lines. The problem line, starting with "p", specifies the parameters of the CNF problem. It includes the problem type, the number of literals, and the number of clauses, all separated by spaces. The clause lines contain the contents of individual CNF clauses, with each number separated by spaces. Each number represents a literal, where positive numbers denote normal literals and negative numbers represent the negation of the corresponding literal. The clause lines are terminated by a 0 to indicate the end of each clause. Below is a simple example of CNF formula  $(1 \lor \neg 2 \lor 3) \land (2 \lor 3) \land (1 \lor \neg 3) \land 2$  in DIMACS format.

|  | Listing 2.1: | CNF | formula i | in DIMACS | format |

|--|--------------|-----|-----------|-----------|--------|

|--|--------------|-----|-----------|-----------|--------|

| 1 | р | cnf 3 4                               |

|---|---|---------------------------------------|

| 2 | 1 | -2 3 0                                |

| 3 | 2 | 3 0                                   |

| 4 | 1 | -3 0                                  |

| 5 | 2 | cnf 3 4<br>-2 3 0<br>3 0<br>-3 0<br>0 |

Using a search algorithm, SAT Solvers usually determine the range of potential truth assignments for the variables. The process of exploring the assignment for input variables is progressive. For every search, the algorithm assigns a variable as a value and performs satisfiability reasoning, then update and analyzes the formula in the next search. Whenever the formula cannot be satisfied in a certain phase, the search function goes back to the last assignment of a variable and modify its value, iteratively propagating the assignment to verify if the input formula is satisfiable or not.

It is of high necessity for a SAT Solver to adopt an efficient search algorithm; otherwise, it will be indistinguishable from a normal program using brute force. Thus, to increase the effectiveness of the search, multiple procedures have been proposed; such as clause elimination procedure to simplify CNF [13], Scaling And Probabilistic Smoothing (SAPS) algorithm to make dynamic local search more efficient [12], variable elimination with sub-sumption and self-subsuming resolution in preprocessing to decrease the runtime of SAT solvers[10] etc.

There is a wide selection of SAT solvers available, among which MiniSat stands out as one of the most renowned. Initially presented in 2003 [21], MiniSat employs conflictdriven learning, watched literals technique, and various other algorithms to significantly accelerate computation time while maintaining exceptional performance. It has become the cornerstone upon which many SAT solvers are built, owing to its ability to effectively incorporate clause learning techniques. Furthermore, the Maple series of SAT solvers, enhanced with machine learning-based heuristics developed by Vijay Ganesh et al., have made notable advancements in SAT solving [17]. In particular, MapleSAT has demonstrated improved performance by employing the Learning Rate Branching (LRB) heuristic technique which is built on a Multi-Armed Bandit (MAB) algorithm called Exponential Recency Weighted Average (ERWA), and diverging from the conventional Variable State Independent Decaying Sum (VSIDS) branching heuristic.

The advent of SAT solvers has opened up new possibilities for addressing prevalent problems in the NP domain. This entails reducing the target problem into a boolean satisfiability problem and subsequently employing an SAT solver to solve it. By inverting the solution provided by the SAT solver, one can obtain the desired answer for the original problem. This approach has proven to be an effective strategy for tackling problems in NP using the capabilities offered by SAT solvers. However, the process of reducing the original problem to a boolean satisfiability problem often proves to be intricate and burdensome. This is due to the inherent limitations of boolean satisfiability problems, which only permit three logic operators, whereas many other problems may involve more complex mathematical expressions. For instance, consider the exact cover problem, which relies on graph theory. The task of transforming a graph-based problem into a boolean logic-based problem for its solution is considerably complicated and convoluted. This process entails not only encapsulating the fundamental mathematical numbers and graph characteristics into boolean logic formulas (CNF form) but also meticulously representing each aspect of the basic logic in the exact cover problem through these formulas. It requires careful consideration of how to store and encode the essential components of the problem using boolean logic expressions, and the scale of the final CNF form is expected to be vast, which poses challenges in both the reduction process solving and testing.

### **Other Solvers**

Apart from the SAT solvers that can solve the boolean satisfiability problem, solvers that can directly solve the graph colouring problem have also emerged. FastColor, a graph coloring problem solver released in 2017, introduces a novel reduction rule rooted in the degree bounded independent set concept [18]. As a result, its algorithm outperforms the approach proposed by Rossi in 2016 [20], delivering significantly enhanced performance. Concorde, a highly efficient solver for the Traveling Salesman Problem (TSP) developed by David L. et al. [5], excels at providing rapid solutions for large-scale TSP instances. But still, it should be noted that the aforementioned solvers are specifically designed for a limited set of problems (graph colouring problem and TSP), which may restrict the solver's applicability. Their practicality significantly diminishes when confronted with problems that cannot be easily reduced to these domains, particularly those unrelated to graphs. Hence, this thesis focuses on the broader objective of utilizing solvers to address general problems in NP, transcending the limitations of several specific problems. Besides, it explores methodologies and approaches that enable the solver's applicability to a wide range of problems, aiming to enhance its versatility and effectiveness in solving various NP-complete problems.

### 2.2 Solution Ideas

This thesis presents professional solutions for commonly encountered problems in NP class. The approach first involves reducing a problem in NP to a circuit satisfiability problem in a non-traditional sense. The featured circuit not only encompasses the three very basic logical operators: AND, OR, and NOT gates, but also includes sub-circuits capable of performing arithmetic operations based on numerical numbers. Specifically, below are seven enhanced circuits that can be constructed in the service, and work as nested sub-circuits:

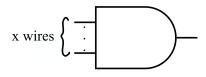

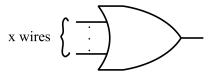

1. AND circuit: A big AND circuit which contains x input wires and perform AND logic.

Figure 2.1: The AND circuit.

2. OR circuit: A big OR circuit which contains x input wires and perform OR logic.

Figure 2.2: The OR circuit.

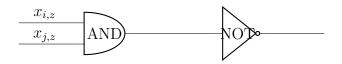

3. **Bit-Not circuit**: A circuit that takes 1-bit input, and has 1-bit output, which is the negation of the input.

Figure 2.3: The Bit-Not circuit.

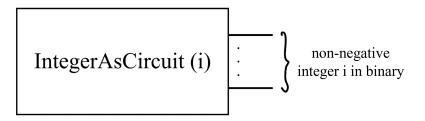

4. IntegerAsCircuit circuit: This circuit encodes a non-negative integer *i* and returns it in binary as a boolean circuit.

Figure 2.4: The IntegerAsCircuit circuit.

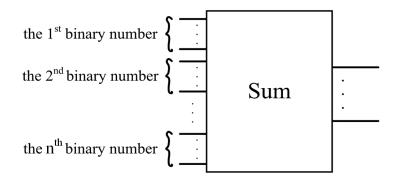

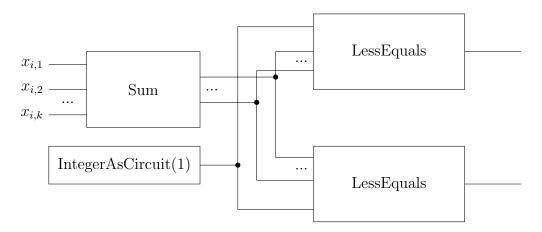

5. Sum circuit: The circuit has a list of wires representing n binary numbers as input and it outputs the number of wires equal to the sum of those binary values.

Figure 2.5: The Sum circuit.

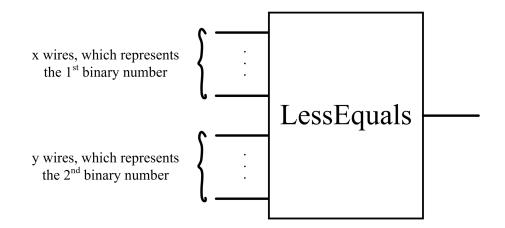

6. LessEquals circuit: A circuit with x + y input wires. It checks whether the binary number represented by the first x bits is less than or equals the binary number

represented by the next y bits. Its output wire will be assigned a boolean value of 1 if the first binary number in x wires is less than or equal to the second binary number in y wires, otherwise 0.

Figure 2.6: The LessEquals circuit.

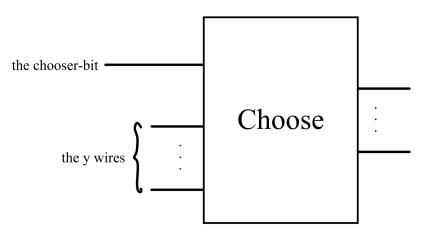

7. Choose circuit: A circuit takes 1 + y input wires and uses the first input wire as the chooser-bit to choose the rest of y bits. If the chooser-bit is assigned a boolean value of 1, the output y wires will be the same as the y input wires; otherwise, they will all be set to a boolean value of 0 which represents the y input wires are not been selected.

Figure 2.7: The Choose circuit.

All of the aforementioned circuits are fundamentally composed of AND, OR, and NOT gates. However, their ability to perform fundamental mathematical operations significantly simplifies the challenges posed by other problems in NP when they are reduced to the Circuit-SAT problem.

Then, to solve the circuit that probably contains the above extra four sub-circuits, it should be encoded into a JSON file that comprehensively includes all its information. The server proposed in this thesis takes that JSON file as input, effectively automates the circuit-building process, and determines its feasible solution. In chapter 3, a comprehensive exploration is provided regarding the library employed for constructing and solving circuits with these new features.

Before delving into the implementation details of the service, at the end of this chapter, the reduction process from all Karp's 21 NP-C Problems to Circuit-SAT Problems is presented as an example manual to provide references for other problems in NP.

### 2.3 Ways of Reducing Karp's 21 NP-C Problems to Circuit-SAT Problems

Below is the reduction process from all of Karp's 21 NP-complete problems to the Circuit-SAT problem. Karp's 21 NP-complete problems come in various forms and cover a wide range of domains. Clients can use this as a reference to reduce their own problems in NP to a Circuit-SAT problem. The ideas for all the reductions presented in Chapter 2.3 of this thesis were conceived independently by the author.

### Boolean satisfiability problem

The boolean satisfiability problem (also known as SAT) is in the NP-complete class, currently, there is no deterministic algorithm that can solve this problem in polynomial time in its input. The reduction from SAT problem to Circuit-SAT problem is achieved by creating input wires for each unique literal, and constructing AND, OR and Bit-Not sub-circuits according to logical operators in the boolean formula.

#### 0–1 integer programming

A 0-1 integer programming problem refers to a list of unknown variables and a few inequalities constraints. Its goal is to find the extreme value for a polynomial of unknowns. A canonical form of it is:

- maximize  $\mathbf{c}^T \mathbf{x}$

- subject to  $\mathbf{A}\mathbf{x} \leq \mathbf{b}, \, \mathbf{x} \geq \mathbf{0}$  and  $\mathbf{x} \in \mathbb{Z}^n$

where  $\mathbf{c} \in \mathbb{R}^n$ ,  $\mathbf{b} \in \mathbb{R}^m$  are vectors and  $\mathbf{A} \in \mathbb{R}^{m \times n}$  is a matrix.

The circuit of the reduction from 0–1 integer programming problems to Circuit-SAT problems has  $k * \dim_{\mathbf{R}}(\mathbf{x})$  input wires, where k is the upper limit of the number of bits the unknown can occupy when represented in binary. Each unknown is represented by k input wires in binary for future calculation.

- 1.  $\mathbf{Ax} \leq \mathbf{b}$  can be expressed as k independent equations and for every inequality, the inequality sign can be reified into a LessEquals sub-circuit. The right-hand side number b of the equation is been expressed as an IntegerAsCircuit and its output is input to the LessEquals sub-circuit. As for the left-hand side, each unknown  $x_i$  is multiplied by an integer  $a_i$  (since IntegerAsCircuit could only generate an integer). This is accomplished by using a Sum sub-circuit, which takes  $a_i$  elements, and then the k wires of  $x_i$  are input  $a_i$  times into the Sum sub-circuit. Finally, a Sum sub-circuit is again used to sum up all the output results of each unknown in the vector, its output is another part of the inputs of the LessEquals sub-circuit.

- 2. To determine the maximum of  $\mathbf{c}^T \mathbf{x}$ , the reduction circuit requires clients to use external code to control the input of an IntegerAsCircuit sub-circuit and let it generate a target value s. According to the feedback on the relationship between the previous target s and  $\mathbf{c}^T \mathbf{x}$ , the maximum can be gradually approached by continuously adjusting the value of s. First, we can convert  $\mathbf{c}^T \mathbf{x}$  to a sub-circuit, the step is similar to the step above when we construct for the left-hand side of a single inequality. The output of the sub-circuit is part of the input for a LessEquals sub-circuit, and the other part of the input is the output of an IntegerAsCircuit for the target s, before finding the maximum value, the value of s is determined by the code used by clients. According to each previous return, clients code should be able to adjust s. For example, if  $\mathbf{c}^T \mathbf{x}$  is less than or equal to the previous target s, then the code should increase s this turn, otherwise make it smaller.

- 3. An AND sub-circuit is used in the end to ensure all the constraints above are guaranteed.

#### Clique

A reduction from clique problem to circuit-sat is as follows. Given an instance of clique problem,  $\langle G = \langle V, E \rangle, k \rangle$ , if there exists a clique of size k for undirected graph G? A clique V' is a complete subgraph of G.

Let  $V = \{u_1, \ldots, u_n\}$ , for every vertex, an input wire is introduced and it is set to 1 if and only if this vertex is chosen to be included in the k-sized clique.

The constraints for the clique problem are encoded as below:

- 1. For two disconnected vertices  $\{u_i, u_j\}$ , their corresponding input wires are both input to an AND sub-circuit and then the output of the AND sub-circuit is then input to a Bit-Not sub-circuit. This is to prevent any disconnected vertices from being selected into the clique at the same time.

- 2. Input all the input wires into a Sum sub-circuit. Then, two LessEquals sub-circuits take the output wires of the Sum sub-circuit as the first and second groups of input, respectively. The other group of input wires for these two LessEquals sub-circuits are the output of IntegerAsCircuit for k. This is to check if the number of vertices in the final clique is exactly k.

- 3. An AND sub-circuit is constructed, with the output wires of the above sub-circuits serving as its inputs. This construction ensures that all the above constraints are satisfied, and its output wire becomes the output wire of the whole circuit.

### Set packing

Suppose the input of an instance of set packing is  $\langle \{S_1, \ldots, S_n\}, X, k \rangle$ , where collection  $S = \{S_1, \ldots, S_n\}$  contains subsets of set X. If there exists a collection C whose size is k or more, such that all sets in C are pairwise disjoint?

The circuit we construct has n input wires, wire i is set to 1 if and only if  $S_i$  has been chosen into collection C.

The reduction is as follows:

- 1. For every pair of subsets  $\langle S_k, S_j \rangle$ , where  $S_k \cap S_j \neq \emptyset$ , input the wires representing both subsets into an AND sub-circuit. Then, input the output of the AND sub-circuit to an OR sub-circuit.

- 2. An AND sub-circuit is built in the end collecting all the output of OR sub-circuits above, and its output is the output of the final whole circuit.

#### Vertex cover

A reduction from vertex cover to circuit-sat is as follows. Assume we are given an instance of vertex cover,  $\langle G = \langle V, E \rangle, k \rangle$ , if there exists a vertex cover of size at most k for undirected graph G? A vertex cover V' is a subset of V such that for all the edges  $uv \in G, u \in V' \lor v \in$ V'.

Assume  $V = \{u_1, \ldots, u_n\}$ . Our output circuit C has n input wires  $\{i_1, \ldots, i_n\}$ . An input wire is set to 1 if and only if  $u_i$  is chosen to be in the vertex cover.

We encode the constraints as follows:

- 1. For every edge  $\langle u_i, u_j \rangle \in E$ , at least one of them has to be in the vertex cover. So for every edge  $\langle u_i, u_j \rangle$ , an OR with  $i_i, i_j$  as its input is built.

- 2. The integer sum  $i_1 + \ldots + i_n \leq k$ . So a Sum sub-circuit which inputs are all the input wires to the full circuit  $i_1, \ldots, i_n$ , an IntegerAsCircuit sub-circuit for k are constructed; and finally, a LessEquals sub-circuit is used to compare the output of the Sum and the IntegerAsCircuit.

- 3. Finally, an AND sub-circuit takes all the output wires of the above two constraints as inputs is built, and the output wire of this AND sub-circuit is the output wire of the full circuit.

#### Set covering

Given an instance of a set covering problem,  $\langle \{S_1, \ldots, S_n\}, U, k \rangle$ , where  $S = \{S_1, \ldots, S_n\}$ is a collection of subsets of union set U. If there exists a k-size (or less) set cover C, which consists of subsets in S and the union is U? That is, if  $C = \{S_{c_j}, \ldots, S_{c_k}\}$ , then for all  $e \in U, \exists S_{c_m} \in C$  such that  $e \in S_{c_m}$ .

The circuit constructed according to set covering has n input wires,  $\{i_1, \ldots, i_n\}$ , and wire  $i_j$  is set to 1 if and only if the  $j^{th}$  subset in collection S is selected into the set cover.

The encoding of constraints for this question is as follows:

1. For each subset  $S_i \in S$ , for every missing element not included in  $S_i$ , use an OR sub-circuit to receive the group of input wires whose corresponding subset contains the missing element. An AND sub-circuit is then built to receive the wire for the subset  $S_i$  and all the output wires of the previous OR sub-circuits. (If there is only one subset containing the missing element, then its wire can directly input to the AND sub-circuit of  $S_i$ ).

- 2. Input all the wires to a Sum sub-circuit, and a LessEquals sub-circuit is built to compare the output of the Sum sub-circuit and the output of IntegerAsCircuit for k, to check if the size of the set cover exceeds k.

- 3. Finally an AND sub-circuit is built, which inputs are all the output wires above and its output is the output of the final whole circuit.

### Feedback node set

Given an instance of a feedback node set problem:  $\langle G = \{V, E\}, k \rangle$ , if there exist a k-size FVS such that if all the vertices in FVS are removed, the whole graph will have no cycles.

Assume  $V = \{u_1, \ldots, u_n\}$ , the circuit for feedback node set problem has *n* input wires,  $\{i_1, \ldots, i_n\}$ , and a wire  $i_j$  is set to 1 if and only if the  $j^{th}$  vertex is chosen into the FVS. The reduction is shown below:

- 1. Clients should first determine all the cycles in graph G, and record every relevant index of vertices included. Then for all the vertices in every cycle, input their wires to an OR sub-circuit to check if at least one of them is selected to be in FVS.

- 2. Input all the wires to a Sum sub-circuit. The Sum sub-circuit's output, along with the output of an IntegerAsCircuit for k, are both input to a LessEquals sub-circuit to check if the number of the selected vertices is less than or equal to k.

- 3. Finally uses an AND sub-circuit to receive all the output wires above and its output is the output of the whole circuit.

#### Feedback arc set

An instance of a feedback arc set problem is  $\langle G = \{V, E\}, k \rangle$ ,  $E = \{e_1, \ldots, e_n\}$ , if there is a k-size feedback arc with a set of edges such that it would not contain any cycles if all of its edges are removed.

Similar to above, instead of creating wires for each vertex, now create n input wires for each edge this time. A wire is set to 1 if and only if it is selected to feedback arc set. The reduction to Circuit-SAT problem is shown below:

1. Number all edges from 1 to n, then clients need to initially identify all the cycles within graph G and record all relevant indices of the included edges. For each cycle, in order to determine if at least one of the edges in it has been chosen to be in the feedback arc set, input the wires of all edges in the circuit to an OR sub-circuit.

- 2. Similarly, a Sum (receiving all the input wires) sub-circuit, a LessEquals sub-circuit and an IntegerAsCircuit for k are used to check if the number of the selected edges is smaller than k.

- 3. An AND sub-circuit whose inputs are all the output wires above is then used in the end to check if all the above constraints are satisfied.

### Directed Hamiltonian path

Directed Hamiltonian path problem is to find out if there exists a path in the directed graph  $G = \{V, E\}$  which makes it possible for visiting each vertex exactly once.

Assume  $G = \{V, E\}$ ,  $E = \{e_1, \ldots, e_n\}$  and  $V = \{u_1, \ldots, u_m\}$ , the reduced circuit possess *n* input wires each represent if an edge, an input wire  $i_j$  is set to 1 if and only if its corresponding edge  $e_j$  is selected into the undirected Hamiltonian path.

The reduction from directed Hamiltonian path problem to Circuit-SAT problem is shown below:

- 1. To make sure no vertices are visited twice or more, for every edge  $e_i$ , where  $e_i = \langle u_a, u_b \rangle$ ,  $u_a$  is the source,  $u_b$  is the destination, all the wires representing edges whose destination is  $u_a$  is connected to a bit-NOT sub-circuit and pass to an AND sub-circuit.

- 2. To ensure all the vertices are visited, for every vertex, input all the wires whose corresponding edges connect to it to an OR sub-circuit.

- 3. Pass all the inputs to a SUM sub-circuit to calculate the number of selected edges. To verify the fact that the number of edges in Hamiltonian path in G equals the number of vertices minus 1, the output of the SUM is input to a LessEquals sub-circuit and the other part of its input is an IntegerAsCircuit for m 1.

- 4. In the end, all the output wires above should be input to an AND sub-circuit to guarantee all the constraints are satisfied.

### Undirected Hamiltonian path

Similar to the directed Hamiltonian path problem, the undirected Hamiltonian path problem is asking if an undirected path in graph  $G = \{V, E\}$  exists, such that each vertex will be visited precisely only once. According to the given graph  $G = \{V, E\}$ ,  $E = \{e_1, \ldots, e_n\}$  and  $V = \{u_1, \ldots, u_m\}$ , the circuit has *n* input wires,  $\{i_1, \ldots, i_n\}$ , each represent an edge, and an wire  $i_j$  is set to 1 if and only if edge  $e_j$  is selected into the undirected Hamiltonian path.

The reduction from undirected Hamiltonian path problem to Circuit-SAT problem is shown below:

- 1. Input all the input wires to a LessEquals sub-circuit to check if the number of the selected edges in the path is exactly m 1, m is the number of the vertices. Thus, the other part of the input is the output of an IntegerAsCircuit sub-circuit for m.

- 2. For each input wire, input it to two Choose sub-circuits both as the chooser-bit (first bit), and the rest of the input wires of the two Choose sub-circuits are the output of two individual IntegerAsCircuit (for 1) sub-circuits. Each of the IntegerAsCircuit sub-circuit represents a vertex to the edge connected, and in the entire whole circuit, all Choose sub-circuits that choose to represent the same vertex need to feed their outputs into a Sum sub-circuit. Later, the output of the Sum sub-circuit is the input of two LessEquals sub-circuits to check if the output is less than or equal to 2 and larger than or equal to 1.

That is, if an edge is selected in an undirected Hamiltonian path, the two vertices it connected will also be selected, finally by checking how many times each vertex has been counted (x), making sure  $1 \le x \le 2$ , then it is guaranteed that every vertex will only be visited once (only the start and end vertex will be counted once and others will be counted twice).

3. In the end, an AND sub-circuit is constructed whose input is all the output wires above, this is to make sure all the above constraints are satisfied.

## Satisfiability with at most 3 literals per clause

3-SAT problem is also NP-complete, which formula contains 3 literals in every clause.

Similar to the original SAT problem, when solving 3-SAT problems by using the circuit solver, the input should be in accordance with the input of the formula, and each unknown variable is assigned to an input wire. The construction of the circuit sub-circuits should be aligned with the connection order between the operators in the formula.

### Graph Coloring Problem (Chromatic number)

Assume our input is an instance of graph colouring problem  $\langle G = \langle V, E \rangle, k \rangle$ , and ask if there is a way/function  $c(\cdot)$  of labelling k colours to all vertices such that no two vertices connecting by an edge share the same colour,  $c(u) \neq c(v)$  for  $\forall (u, v) \in E$ .

Let  $V = \{u_1, \ldots, u_n\}$ , for every vertex  $u_m$ , construct k input wires,  $\{i_{m,1}, \ldots, i_{m,k}\}$ . A wire  $i_{m,j}$  is set to 1 if and only if  $u_m$  is set to the  $j^{th}$  color.

We encode the constraints as follows:

1. For every k input wire constructed according to a vertex, use a Sum sub-circuit to calculate their sum value, checking if it is equal to 1 since each vertex should be and only be assigned to one type of colour. Input both the output of the Sum sub-circuit and the output of an IntegerAsCircuit for 1 to two LessEquals sub-circuits to check if they are the same.

2. For every edge  $\langle u, v \rangle$ , check input wires  $\{i_{u,j}, i_{v,j}\}$  for all  $j \in k$  by inputting them to an AND sub-circuit and concatenate the AND with an OR sub-circuit, to make sure not assigning vertex u and v to the same colour.

3. An AND sub-circuit of the output wires of the above sub-circuits is constructed in the end to make sure all the above constraints are satisfied, whose output wire is the output wire of the full circuit.

#### Clique cover

Assume the input of clique cover is  $\langle G = \{V, E\}, k \rangle$ , if there exists a way of partitioning all the vertices V in the graph G into k cliques. Suppose  $V = \{u_1, \ldots, u_n\}$ , the circuit we built has n \* k input wires. Wire  $i_{j,a}, j \in \{1, \ldots, n\}$  and  $a \in \{1, \ldots, k\}$ , is set to 1 if and only if decide to categorize the  $j^{th}$  vertex into the  $a^{th}$  clique.

The reduction from the clique problem to Circuit-SAT problem is as follows:

- 1. For each vertex, input its k wires into a Sum sub-circuit. Input its output and the output of an IntegerAsCircuit for 1 to two LessEquals sub-circuits to check if they are the same. This is to guarantee the constraint that one vertex should only be grouped into one clique.

- 2. For every two vertices which are not connected, they can not be put into the same clique. Thus, for  $\forall (u, v)$  and  $(u, v) \notin E$ , input k pairs of wires  $i_{u,a}$  and  $i_{v,a}$ ,  $a \in \{1, \ldots, k\}$ , into an AND sub-circuit and then concatenate its output to a Bit-Not sub-circuit.

- 3. Inputs all the output wires above to an AND sub-circuit in the end, this is to make sure all the constraints above are satisfied at the same time.

#### Exact cover

Suppose our input is  $\langle \{S_1, \ldots, S_n\}, X \rangle$ , where collection set  $S = \{S_1, \ldots, S_n\}$  contains subsets of set X. If there exists a subcollection  $S^*$  of S whose size is k, such that every item in U is contained and only contained once in  $S^*$ . Our full circuit has n input wires  $i_1, \ldots, i_n$  where the wire  $i_j$  is set to 1 if and only if  $S_j$  is in the exact cover.

We encode the constraints as follows:

1. For each pair  $S_j, S_k$  that is chosen to be in our solution, we ensure that their intersection is empty.

That is, for each pair of input wires  $i_j, i_k$ , which have the property  $S_j \cap S_k \neq \emptyset$ , we create an AND sub-circuit with  $i_j$  and  $i_k$  as the inputs and then place a Bit-Not sub-circuit directly after its output.

2. For each member  $x \in X$ , an OR sub-circuit is built, whose inputs  $i_{k_1}, \ldots, i_{k_q}$  are all the input wires to the full circuit which corresponding subset contains element x, where  $x \in \{S_{k_1} \cap \ldots \cap S_{k_q}\}$ .

3. An AND sub-circuit of the output wires above is constructed in the end to make sure all the above constraints are satisfied, whose output wire is the output wire of the full circuit.

#### Hitting set / Set cover problem

Given a set  $S = \{S_1, \ldots, S_n\}$ , a universal set U, and an integer k, where S is a collection of subsets of U, and  $S_1 \cup \ldots \cup S_n = U$ . If there exists a k-size hitting set H, which is a subset of U, such that for every collection  $S_i \in S$ , the number of items shared by H and  $S_i$  is only 1,  $|H \cap S| = 1$ .

### Steiner tree

Given an instance of a Steiner tree problem in an undirected graph,  $\{G = \langle E, V \rangle, T, k\}$ ,  $V = \{u_1, \ldots, u_n\}$  and  $E = \{e_1, \ldots, e_m\}$ , with non-negative edges  $w(e_i) \ge 0$ . The terminal vertex set T is a subset of vertices of set V, and  $k \in \mathbb{Z}$ . Is there a tree  $H = \langle E', V' \rangle$ , which is a subgraph of G, such that  $T \subseteq V'$  and the weight of the tree  $w(H) \le k$ .

The circuit has m inputs for each edge, and an input wire is set to 1 if and only if the edge is selected into the tree. The reduction from this problem to Circuit-SAT problem is shown below:

- 1. To check that all the vertices in the terminal set are included, for every vertex  $u_k \in T$ , all the edges connected to it are passed to an OR sub-circuit. This is used to ensure that at least one of the edges is chosen, and the vertex is in the final output tree H.

- 2. To ensure all the vertices in H are connected, for each pair of vertices  $\{u_i, u_j\}$   $(u_i \in T$ and  $u_j \in T$ ), clients should record all the possible pass connecting  $u_i \in T$  and  $u_j \in T$ . For every possible path, use an AND sub-circuit to receive all the input of edges included. Finally, the output of the AND for each path should then be input to a SUM sub-circuit, this is to calculate how many paths are there between  $u_i \in T$  and  $u_j \in T$ . The output of the SUM will be input to a LessEquals sub-circuit, the other part of the LessEquals input is the output of an IntegerAsCircuit for value 1. This is to make sure there exists only one path between two vertices in the tree H and prevent cycles.

- 3. Every input wire is passed to a Choose sub-circuit as the chooser bit, and the other input is the output of an IntegerAsCircuit for the weight of that edge. The output

of all the Choose sub-circuits is input to a Sum sub-circuit to calculate the sum of the weight of selected edges. Then the output of the Sum sub-circuit and an IntegerAsCircuit for k is compared, and both are input to a LessEquals sub-circuit.

4. An AND sub-circuit is used to take all the sub-circuit output above as input to ensure those constraints are satisfied. Its output is the final output of the entire circuit.

### **3-dimensional matching**

Given a 3-dimensional matching (3DM) problem denotes as  $\{X, Y, Z, T, k\}$ , where set X, Y and Z are three finite sets with no sharing elements, and set  $T = X \times Y \times Z$ , that is,  $T = \{t_1, \ldots, t_s\}$ ,  $t_i = \langle x_i, y_i, z_i \rangle$  where  $x_i \in X$ ,  $y_i \in Y$  and  $z_i \in Z$ . A 3-dimensional matching M,  $M \subseteq T$ , holds the property that for  $\forall t_i \neq t_j$ ,  $t_i \in M$ ,  $t_j \in M$ , and  $t_i = \langle x_i, y_i, z_i \rangle$ ,  $t_j = \langle x_j, y_j, z_j \rangle$ , such that  $x_i \neq x_j$ ,  $y_i \neq y_j$ , and  $z_i \neq z_j$ . If the size of the given 3DM is larger or equal to k?

The circuit for 3DM problem contains s inputs  $\{i_1, \ldots, i_s\}$  where s is the size of the set T. A wire  $i_j$  is set to 1 if and only if the  $j^{th}$  element in T is selected into set M. The reduction from 3DM problem to Circuit-SAT problem is shown below:

- 1. For each pair of subset  $\langle t_i, t_j \rangle$ , both  $t_i$  and  $t_j \in T$ , if they contain any common elements, for example,  $x_i = x_j$  or  $y_i = y_j$  or  $z_i = z_j$ , then pass the  $i^{th}$  and  $j^{th}$  input wires into an AND sub-circuit and then the output of the AND sub-circuit should then pass to an OR sub-circuit. This is to make sure any two triples with no empty intersection should not be selected into a 3DM at the same time.