# ADVANCEMENTS IN CURRENT-SOURCED INVERTER METHODOLOGIES FOR USE IN SMALL-SCALE POWER GENERATION

by

## Nathan Stretch

A thesis

presented to the University of Waterloo

in fulfillment of the

thesis requirement for the degree of

Master of Applied Science

in

Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2007

© Nathan Stretch 2007

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

# **ABSTRACT**

As the costs of large-scale power generation and transmission rise, distributed generation is becoming a prevalent alternative used by a growing number of both residences and businesses. Distributed generation systems typically consist of two main components: a small-scale, often high-efficiency or renewable power source, such as a fuel cell, solar panel, or wind turbine, and a power electronic converter to convert the raw power produced by the source to a usable form.

In North America, the majority of power used in residential and light commercial locations is provided in a form known as *single-phase three-wire*, or *split-phase*. This consists of two *half-phase* AC voltages, each of 110 to 120V rms, and one combined AC voltage of 220 to 240V rms. It is therefore necessary for distributed generation systems to supply power in this same form so that it can be used by standard loads such as lighting or appliances, and the excess power can be fed back into the distribution grid. The most common type of converter used to make this conversion is the voltage-sourced inverter (VSI). There are, however, some advantages to using a current-sourced inverter (CSI) instead. These include improved output voltage waveform quality, built-in voltage boost, and built-in overcurrent protection. However, there are also two obstacles that have prevented the adoption of current-sourced inverters to date.

The first obstacle to the use of current-sourced inverters is that they require a DC current input to operate. Therefore, a circuit and control algorithm must be developed to produce a DC current from a low DC voltage source. The first part of this thesis deals with the generation of a suitable DC current.

The second major obstacle to adopting current-sourced inverters is that no algorithm for producing single-phase three-wire outputs with a CSI presently exists in literature. The second part of this thesis develops such a switching algorithm, using a three-leg current-sourced inverter. The algorithm is demonstrated using simulation and experimental results, which show that the proposed system is able to successfully generate balanced output voltages under unbalanced loading conditions while equalizing switch utilization and minimizing output voltage ripple.

# **ACKNOWLEDGEMENTS**

First of all, I would like to extend my heartfelt thanks to my supervisor, Dr. Mehrdad Kazerani, for his excellent guidance throughout my degree. His skill and effort are unsurpassed in my experience, and I truly cannot imagine anyone with whom I would rather work.

Also, thank you to Dr. El-Shatshat and Dr. Cañizares for their valuable suggestions on this thesis. In addition, I would like to recognize the National Science and Engineering Research Council for financial support provided to me and countless other deserving students.

Many thanks to my family and friends back home in Victoria for tolerating my two-year absence, and for giving me excellent motivation to work hard and finish quickly! Also, thanks to my friends and lab-mates here for making these two years fun as well as productive. A special thank-you to my good friend Laura for taking the time to proofread parts of this work, as well as to my parents, Lorne and Jan, and my sister, Sarah, for all their love and support.

Most importantly, my thanks and my love to Shauna for standing by me in spirit always, even when we were 4000 km apart. (Although I must say I'm looking forward to a future when we're not!) You truly enrich my life.

# TABLE OF CONTENTS

| CHAP | TER | 1 INTRODUCTION                              | 1  |

|------|-----|---------------------------------------------|----|

| 1.1  | BA  | CKGROUND AND LITERATURE REVIEW              | 1  |

| 1.   | 1.1 | Distributed Generation                      | 1  |

| 1.   | 1.2 | Power Electronics Converters                | 3  |

| 1.2  | Co  | NTRIBUTIONS                                 | 9  |

| 1.3  | Тн  | esis Outline                                | 10 |

| СНАР | TER | 2 VOLTAGE SOURCE-TO-CURRENT SOURCE TOPOLOGY | 11 |

| 2.1  | In  | TRODUCTION                                  | 11 |

| 2.2  | Ov  | TERVIEW                                     | 12 |

| 2.3  | RE  | VIEW OF CURRENT-SOURCED INVERTER OPERATION  | 12 |

| 2.4  | DO  | CURRENT CONTROL                             | 13 |

| 2.   | 4.1 | Ideal DC Current                            | 17 |

| 2.   | 4.2 | Required and Minimum DC Current             | 20 |

| 2.5  | ΑĽ  | DITIONAL ENERGY STORAGE                     | 23 |

| 2    | 5.1 | Supplemental Energy-Storage Circuit         | 24 |

| 2    | 5.2 | Steady-State Operation                      | 28 |

| 2    | 5.3 | Method of Control                           | 30 |

| 2.6  | Dy  | NAMIC CURRENT REFERENCE SETTING             | 36 |

| 2.7  | Ex  | PERIMENTAL RESULTS                          | 38 |

| 2.8  | ΑĽ  | VANCED ALGORITHM                            | 43 |

| 2.   | 8.1 | Overview                                    | 43 |

| 2.   | 8.2 | Description of Algorithm                    | 44 |

| 2.   | 8.3 | Supporting Results                          | 49 |

| 2.   | 8.4 | Practical Modifications                     | 50 |

| 2.   | 8.5 | Advantages                                  | 54 |

| 2.9  | SU  | MMARY                                       | 55 |

| СНАР | TER | 3 GENERATION OF SPLIT-PHASE OUTPUTS         | 56 |

| 3 1  | In  | TRODUCTION                                  | 56 |

| 3.2 R   | EQUIREMENTS                                                     | 58  |

|---------|-----------------------------------------------------------------|-----|

| 3.2.1   | Regulation of Output Voltages                                   | 58  |

| 3.2.2   | Optimizing Switch Usage                                         | 60  |

| 3.3 F   | IRST PROPOSED ALGORITHM                                         | 60  |

| 3.3.1   | Overview                                                        | 60  |

| 3.3.2   | Description of Algorithm                                        | 61  |

| 3.3.3   | Simulation Results                                              | 65  |

| 3.3.4   | Experimental Results                                            | 71  |

| 3.3.5   | Discussion                                                      | 73  |

| 3.4 S   | ECOND PROPOSED ALGORITHM                                        | 78  |

| 3.4.1   | Review of Algorithm for Three-Phase Inverters                   | 78  |

| 3.4.2   | Application of Three-Phase Method to Split-Phase Inverter       | 80  |

| 3.4.3   | Application of Three-Phase Algorithm with Equal Current Sharing | 84  |

| 3.4.4   | Additional Simulation Results                                   | 89  |

| 3.4.5   | Experimental Results                                            | 91  |

| 3.5 S   | UMMARY                                                          | 94  |

| CHAPTE  | R 4 EXPERIMENTAL PROTOTYPE DESIGN                               | 95  |

| 4.1 In  | NTRODUCTION                                                     | 95  |

| 4.2 H   | ARDWARE DESIGN                                                  | 95  |

| 4.2.1   | Power Circuit                                                   | 95  |

| 4.2.2   | Measurement and Filtering Circuitry                             | 98  |

| 4.3 S   | OFTWARE DESIGN                                                  | 101 |

| 4.3.1   | Modified Digital PWM                                            | 102 |

| 4.3.2   | Synchronization of A/D Operations                               | 103 |

| 4.4 S   | UMMARY                                                          | 103 |

| CHAPTE  | R 5 CONCLUSIONS AND FUTURE WORK                                 | 104 |

| 5.1 C   | ONCLUSIONS                                                      | 104 |

| 5.2 S   | uggestions for Future Work                                      | 107 |

| REFEREN | NCES                                                            | 108 |

# LIST OF TABLES

| TABLE 2-1. DC CURRENT REFERENCE LEVELS                                                    | . 31 |

|-------------------------------------------------------------------------------------------|------|

| TABLE 2-2. CAPACITOR VOLTAGE REFERENCE LEVELS                                             | . 31 |

| TABLE 3-1. RELATIONSHIP BETWEEN CONTROL SIGNALS AND OUTPUTS                               | . 63 |

| TABLE 3-2. PSEUDO-CODE FOR $V_{C1}$ , $V_{C2}$ , AND $V_{COM}$                            | . 65 |

| TABLE 3-3. PSEUDO-CODE FOR $V_{C1}$ , $V_{C2}$ , AND $V_{COM}$ , INCLUDING OPTIMAL LIMITS | . 75 |

| TABLE 3-4. ALLOWABLE INVERTER LEGS TO BE USED FOR EACH SHOOT-THROUGH STATE, TO            | С    |

| MAINTAIN MINIMAL SWITCHING                                                                | . 85 |

# **LIST OF FIGURES**

| FIG. 1-1. STANDARD TOPOLOGY USED TO PRODUCE SPLIT-PHASE UTILITY-VOLTAGE OUTPUTS                |    |

|------------------------------------------------------------------------------------------------|----|

| FROM A LOW-VOLTAGE DC SOURCE                                                                   | 4  |

| FIG. 1-2. SPLIT DC CAPACITOR METHOD                                                            | 5  |

| Fig. 1-3. Third-leg method.                                                                    | 6  |

| Fig. 1-4. Single-output current-sourced inverter topology                                      | 7  |

| Fig. 2-1. Current-sourced inverter with voltage source-to-current source                       |    |

| CONVERSION BLOCK                                                                               | 12 |

| FIG. 2-2. IMPLEMENTATION OF VOLTAGE SOURCE-TO-CURRENT SOURCE CONVERSION CIRCUIT                | Γ  |

|                                                                                                | 13 |

| Fig. 2-3. Case 1: Reflected voltage under ideal operating conditions                           | 15 |

| FIG. 2-4. CASE 2: EFFECT OF REFLECTED VOLTAGE EXCEEDING SUPPLY VOLTAGE                         | 16 |

| Fig. 2-5. Case 3: Insufficient DC current resulting in system failure                          | 17 |

| Fig. 2-6. Simulated variations in DC current using Matlab ODE-solving script $^{\circ}$        | 23 |

| Fig. 2-7. Current-Sourced Inverter with voltage source-to-current source                       |    |

| CONVERSION CIRCUIT AND SUPPLEMENTAL ENERGY STORAGE                                             | 25 |

| Fig. 2-8. Basic boost converter                                                                | 26 |

| Fig. 2-9. Failure of Current-Sourced Inverter due to turn-on transient                         | 27 |

| Fig. 2-10. Successful supply of 1800W turn-on transient, using supplemental                    |    |

| ENERGY-STORAGE CIRCUIT                                                                         | 27 |

| Fig. 2-11. Reduction of required DC current for steady-state operation, due to                 |    |

| ADDITION OF SUPPLEMENTAL ENERGY-STORAGE CIRCUIT                                                | 29 |

| Fig. 2-12. Comparison of $I_{DC}$ and $V_{C}$ to reference levels                              | 30 |

| Fig. 2-13. Operation of supply switch when reflected voltage is nearly equal to                |    |

| SUPPLY VOLTAGE                                                                                 | 32 |

| Fig. 2-14. Operation of supply switch when reflected voltage is approximately                  |    |

| ZERO                                                                                           | 33 |

| Fig. 2-15. Operation of <i>V-to-I</i> circuit controller                                       | 35 |

| Fig. 2-16. Switching operation of $V$ - $T$ 0- $I$ 1 circuit controller over short time period | )  |

|                                                                                                | 36 |

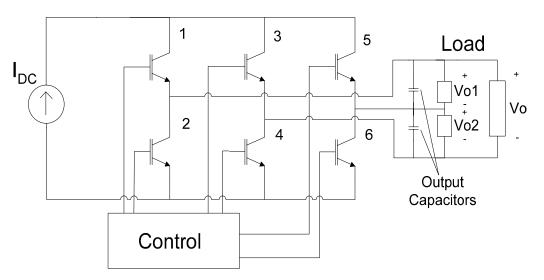

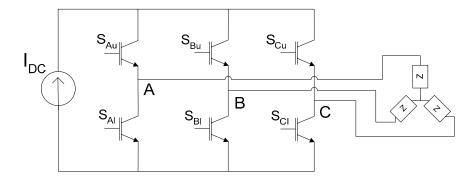

| FIG. 2-17. THREE-LEG CURRENT-SOURCED INVERTER                                          | 38    |

|----------------------------------------------------------------------------------------|-------|

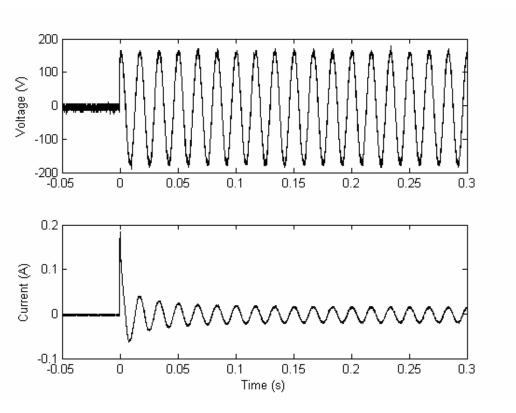

| Fig. 2-18. Turn-on transient of 150-W incandescent light bulb                          | 40    |

| Fig. 2-19. Failure of experimental prototype Current-Sourced Inverter due to           |       |

| TURN-ON TRANSIENT                                                                      | 41    |

| FIG. 2-20. SUCCESSFUL OPERATION OF EXPERIMENTAL PROTOTYPE CURRENT-SOURCED              |       |

| INVERTER DURING TURN-ON TRANSIENT, WITH ADDITIONAL ENERGY-STORAGE CIRCUI               | IT 42 |

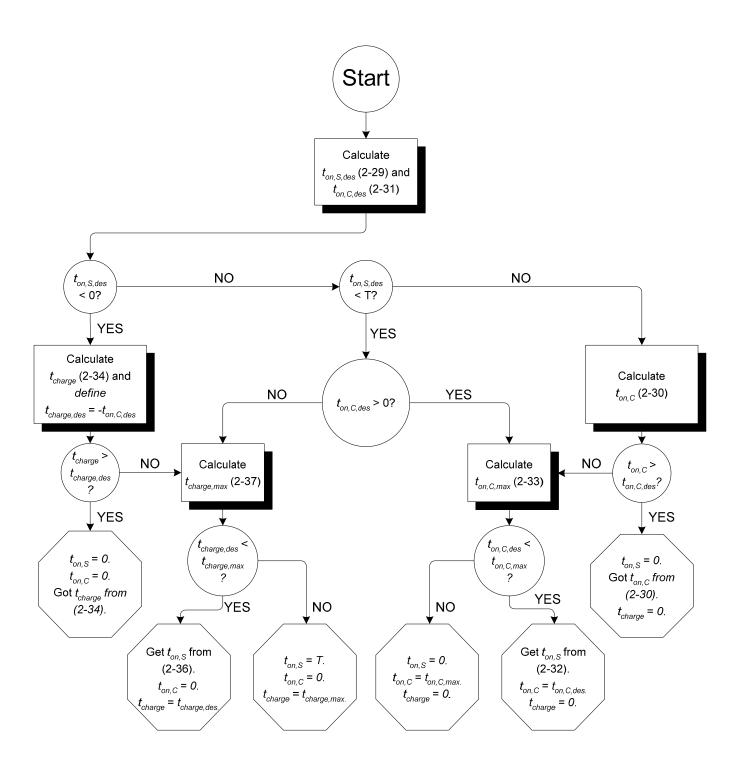

| Fig. 2-21. Flowchart showing advanced control algorithm for $V$ - $to$ - $I$ circuit   | 48    |

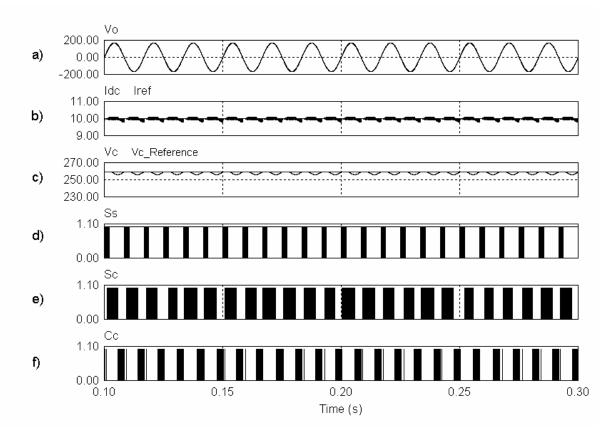

| Fig. 2-22. V-to-I circuit controller operation with new control algorithm              | 50    |

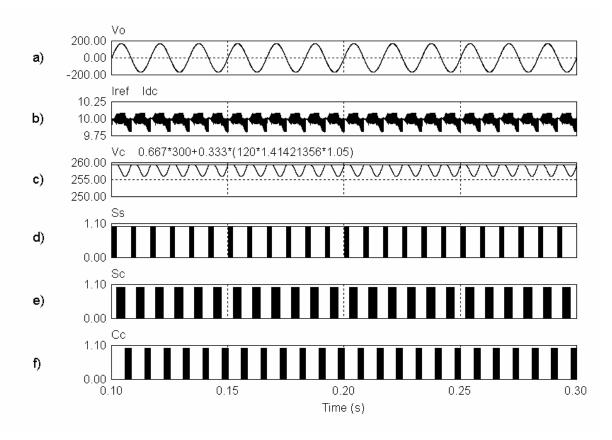

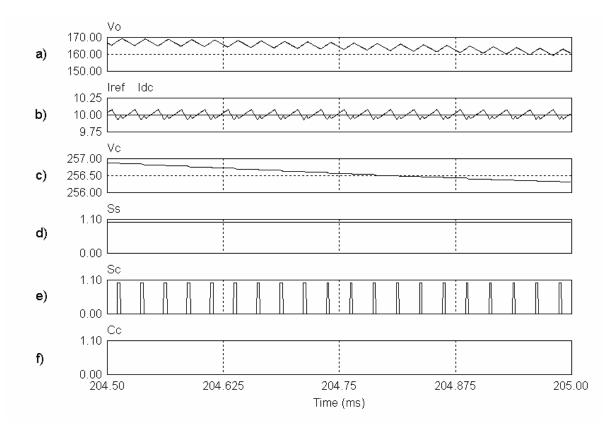

| Fig. 2-23. Final $V$ - $T$ 0- $I$ 1 circuit controller operation, including practical  |       |

| MODIFICATIONS                                                                          | 52    |

| Fig. 2-24. Final <i>V-to-I</i> circuit controller operation: DC current being maintain | IED   |

| THROUGH USE OF THE ENERGY-STORAGE CAPACITOR                                            | 53    |

| Fig. 2-25. Final $V$ - $T$ 0- $I$ 1 circuit controller operation: During and following |       |

| CHARGING OF CAPACITOR                                                                  | 54    |

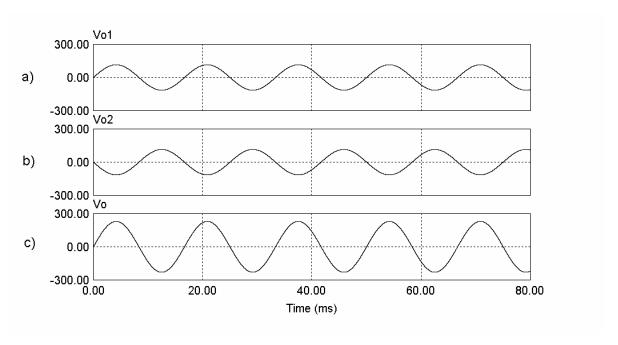

| Fig. 3-1. Split-phase outputs from distribution transformer                            | 56    |

| FIG. 3-2. EXAMPLE OF SPLIT-PHASE OUTPUT VOLTAGES                                       | 57    |

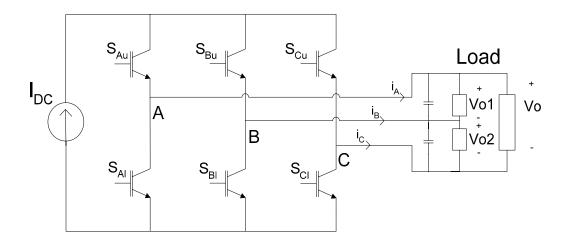

| Fig. 3-3. Three-leg current-sourced inverter, designed to produce split-phase          |       |

| OUTPUT VOLTAGES                                                                        | 58    |

| Fig. 3-4. Output voltage ripple due to inverter switching                              | 59    |

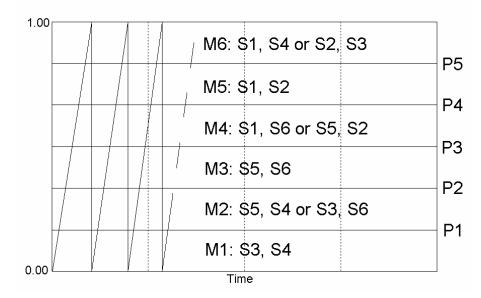

| FIG. 3-5. MULTIPLE-REFERENCE PWM IMPLEMENTATION                                        | 61    |

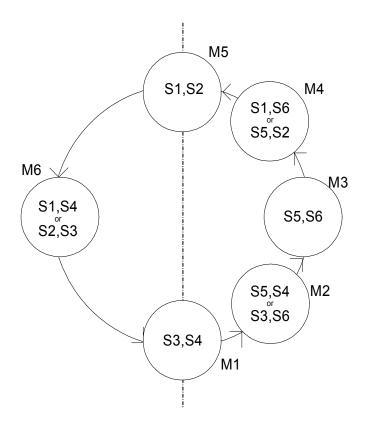

| FIG. 3-6. SWITCHING STATE DIAGRAM                                                      | 62    |

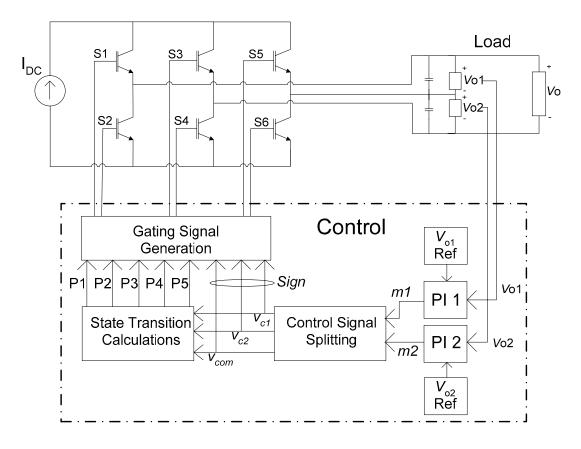

| FIG. 3-7. CONTROL PATH.                                                                | 64    |

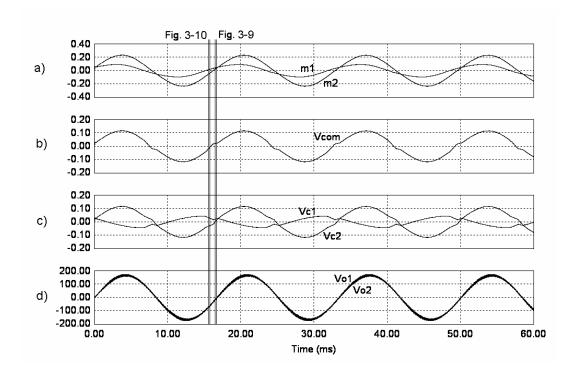

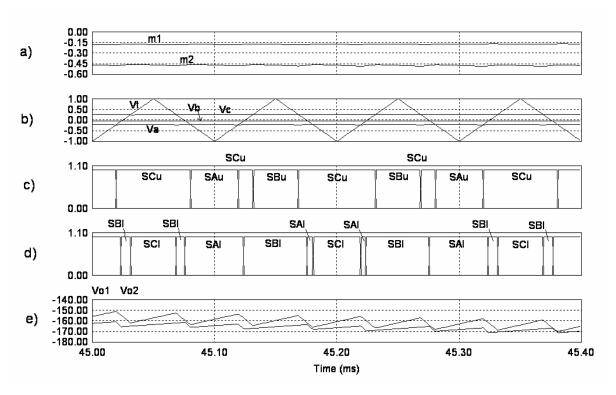

| FIG. 3-8. SIMULATION RESULTS FOR UNBALANCED, RESISTIVE LOAD                            | 66    |

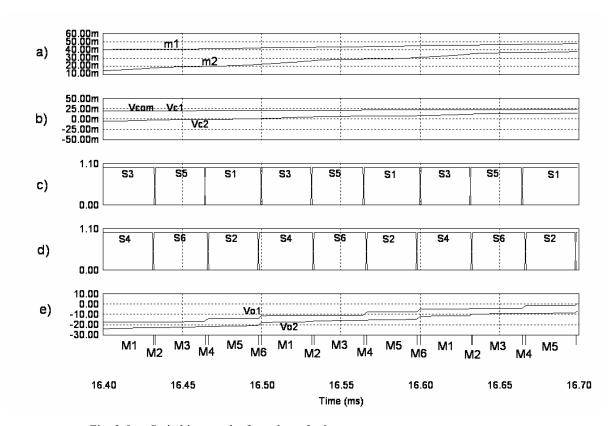

| Fig. 3-9. Switching results for $MI > M2 > 0$ .                                        | 68    |

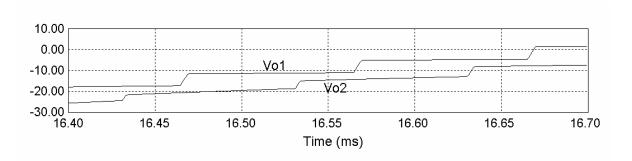

| FIG. 3-10. VOLTAGE RIPPLE WITH ONLY ONE ACTIVE STATE FOR EACH OUTPUT (V)               | 68    |

| Fig. 3-11. Switching results for <i>M1</i> >0, <i>M2</i> <0                            | 69    |

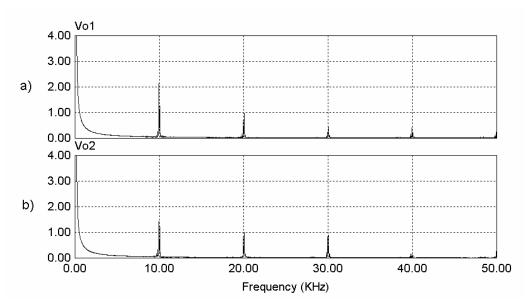

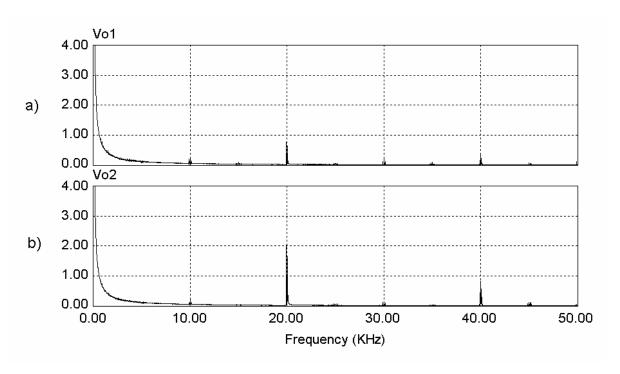

| Fig. 3-12. Frequency domain results                                                    | 70    |

| Fig. 3-13. Frequency domain results with M6 active state set to zero                   | 70    |

| FIG. 3-14. INVERTER OPERATION WITH NON-LINEAR LOAD.                                    | 71    |

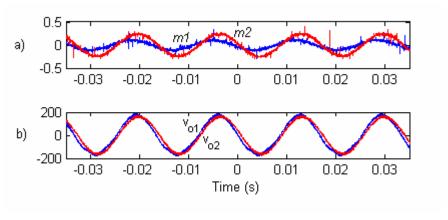

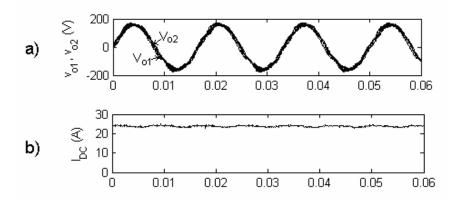

| FIG. 3-15. EXPERIMENTAL RESULTS: RESISTIVE LOADS                                       | 72    |

| Fig. 3-16. Experimental results: Inductive and resistive loads                         | 73    |

| Fig. | 3-17. STANDARD THREE-LEG, THREE-PHASE CSI                                                 | 78        |

|------|-------------------------------------------------------------------------------------------|-----------|

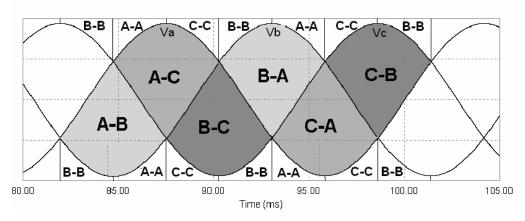

| Fig. | 3-18. Three-reference PWM for three-phase current-sourced inverters                       | 79        |

| Fig. | 3-19. SPLIT-PHASE CSI WITH SWITCHES AND LEGS LABELLED IN THE THREE-PHASE                  |           |

|      | FORMAT                                                                                    | 81        |

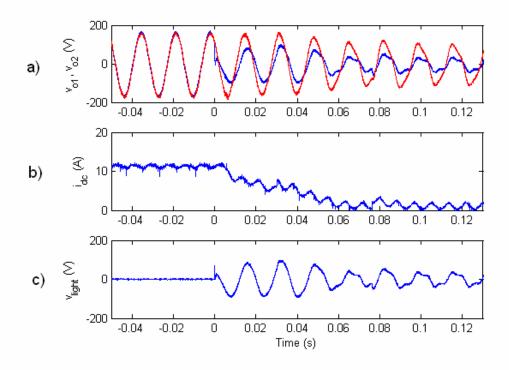

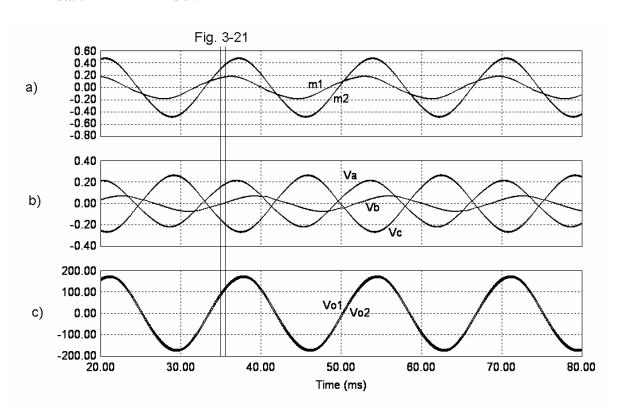

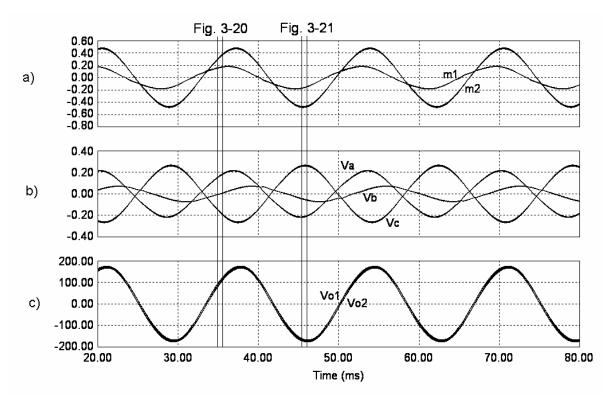

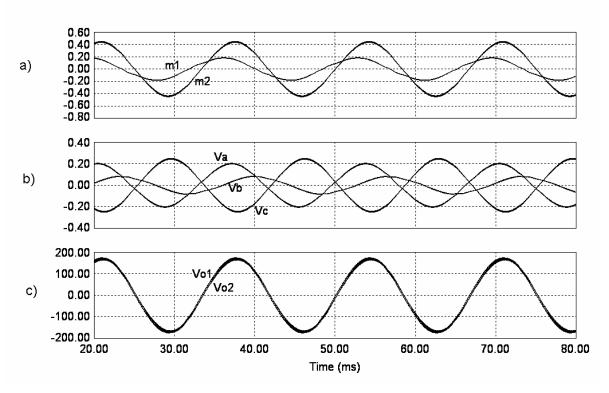

| Fig. | 3-20. Simulation results using three-phase algorithm to produce split-pha                 | SE        |

|      | OUTPUTS                                                                                   | 82        |

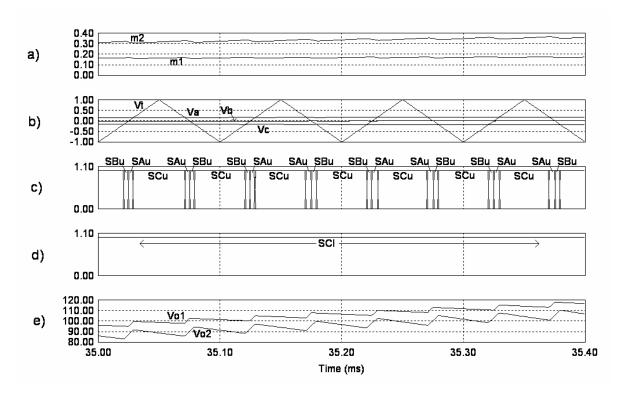

| Fig. | 3-21. Individual switching events from previous figure                                    | 83        |

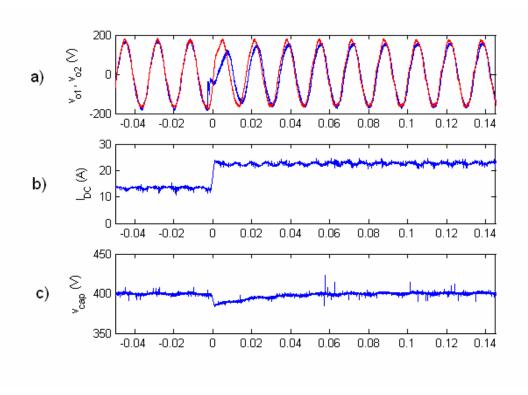

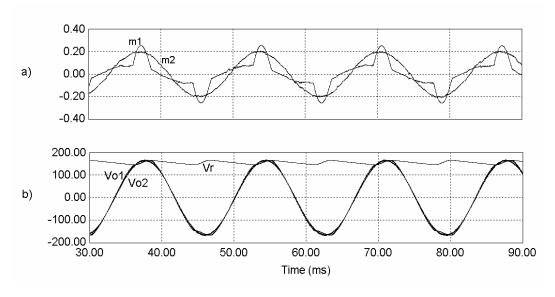

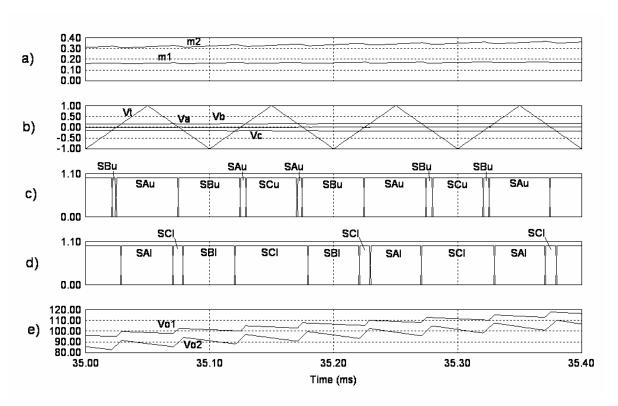

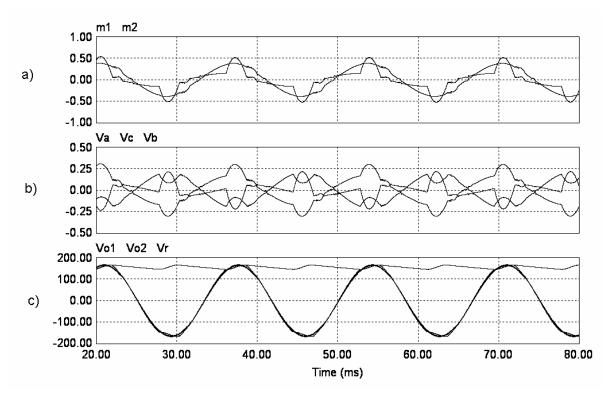

| Fig. | 3-22. SIMULATION RESULTS WITH MODIFICATION OF SHOOT-THROUGH STATES                        | 86        |

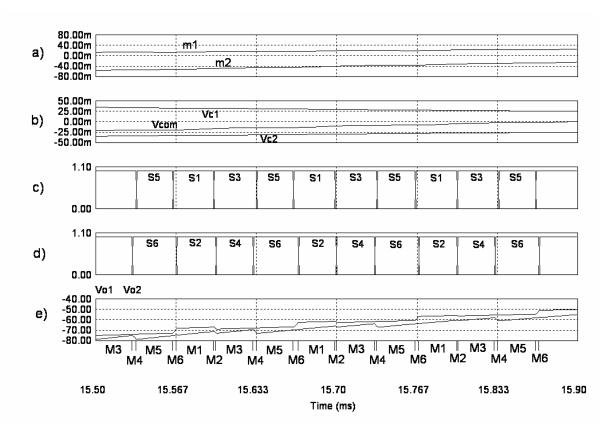

| Fig. | ${\it 3-23.}\ \ Individual\ switching\ events\ showing\ modified\ shoot-through\ states,$ |           |

|      | POSITIVE HALF-CYCLE                                                                       | 87        |

| Fig. | 3-24. Individual switching events showing modified shoot-through states,                  |           |

|      | NEGATIVE HALF-CYCLE                                                                       | 88        |

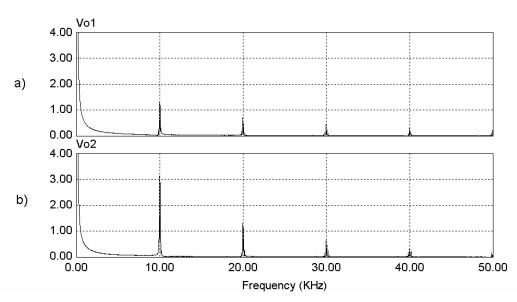

| Fig. | 3-25. Frequency domain results for second method                                          | 89        |

| Fig. | 3-26. Simulation results of modified three-phase method with inductive lo                 | AD        |

|      |                                                                                           | 90        |

| Fig. | 3-27. SIMULATION RESULTS OF MODIFIED THREE-PHASE METHOD WITH NONLINEAR LO                 | )AD       |

|      |                                                                                           | 91        |

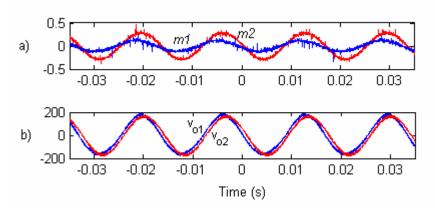

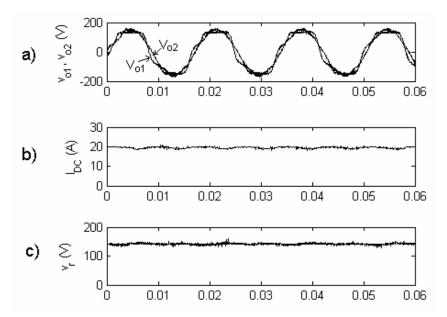

| Fig. | 3-28. Experimental results for Method 2: resistive and inductive loads                    | 93        |

| Fig. | 3-29. Experimental results for Method 2: resistive, inductive, and nonline                | AR        |

|      | LOADS                                                                                     | 93        |

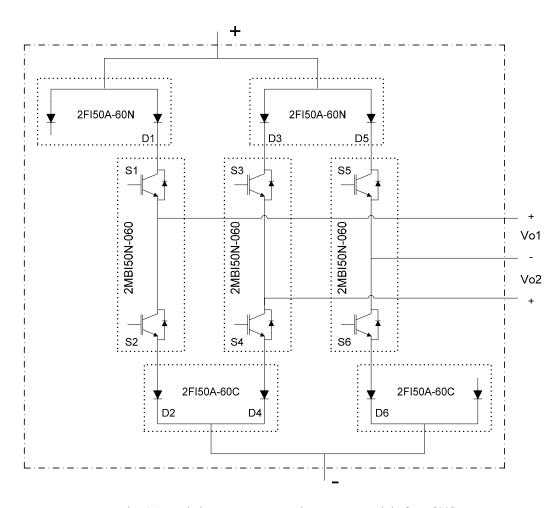

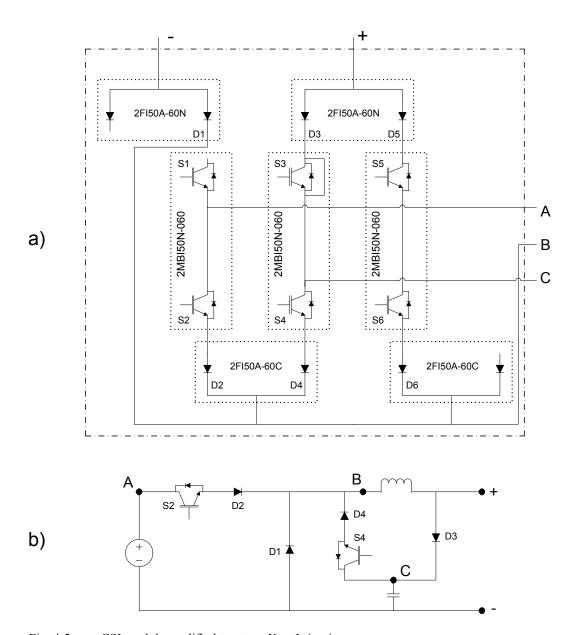

| Fig. | 4-1. Existing current-sourced converter module from [22]                                  | 97        |

| Fig. | 4-2. CSI MODULE MODIFIED TO ACT AS <i>V-TO-I</i> CIRCUIT                                  | 98        |

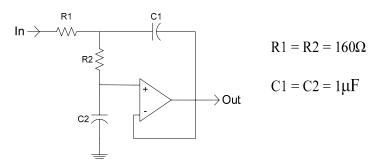

| Fig. | 4-3. OUTPUT VOLTAGE MEASUREMENT LOW-PASS FILTER                                           | 99        |

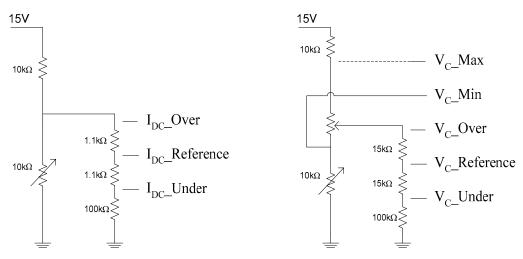

| Fig. | 4-4. CIRCUITS TO GENERATE REFERENCE THRESHOLDS FOR DC CURRENT AND ENERGY                  | <b>?-</b> |

|      | STORAGE CAPACITOR VOLTAGE                                                                 | 100       |

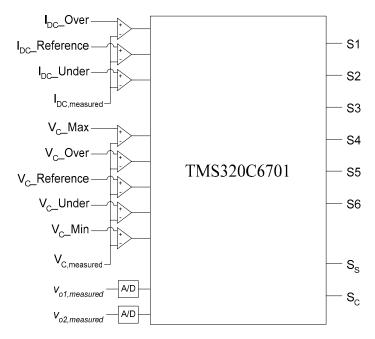

| Fig  | 4-5 CONTROL PROCESSOR I/O                                                                 | 101       |

# LIST OF ABBREVIATIONS

| DG            | Distributed Generation (Generator) |

|---------------|------------------------------------|

| DC            |                                    |

| AC            | Alternating Current                |

| RPM           |                                    |

| VSI           | Voltage-Sourced Inverter           |

| CSI           |                                    |

| PWM           | Pulse Width Modulation             |

| FACTS         | Flexible AC Transmission Systems   |

| IGBT          | Isolated Gate Bipolar Transistor   |

| GTO           |                                    |

| RMS           | Root-Mean-Square                   |

| RB-NPT (IGBT) | Reverse Blocking Non-Punch-Through |

| ODE           | Ordinary Differential Equation     |

| DSP           | Digital Signal Processor           |

| THD           | Total Harmonic Distortion          |

| PI            | Proportional-Integral (controller) |

| MOV           | Metal Oxide Varistor               |

# **CHAPTER 1**

## INTRODUCTION

#### 1.1 BACKGROUND AND LITERATURE REVIEW

#### 1.1.1 DISTRIBUTED GENERATION

With energy costs rising worldwide and concerns being raised regarding the environmental impact and increasing scarcity of fossil fuels, distributed generation, or DG, is becoming viable and cost-effective as both a supplement and an alternative to large-scale power generation. Distributed generation refers to the generation of power on a small scale, at the distribution system level. It consists of low-power generators such as microturbines, solar cells, wind turbines and fuel cells, used to power houses or small businesses, and connected to the distribution grid. There are a number of advantages to distributed generation. Many distributed generators (DGs) make use of renewable energy sources that would not be viable on a larger scale. Combining a distributed generator with a grid connection provides a backup power source in case of an outage, as well as a potential source of income if the power generated by the DG exceeds the local requirements. In addition, many power utilities are adopting variable pricing schemes in an attempt to improve time distribution of loading throughout the day. This is known as *peak-shaving*, and is intended to reduce the peak requirements on the network, thereby delaying the need to add generation capacity. A distributed generator allows a customer to avoid paying for power during the expensive, peak periods of the day [1]. If the DG system has energy

storage capability, it is then possible to recharge the energy storage element during the less expensive periods.

Any distributed generation system requires two basic components. The first is a source of electrical power. Depending on the type of source, the raw power produced may be DC, constant frequency AC, or variable frequency AC. The voltage may be constant or variable. Therefore, the second basic component is a converter circuit to convert this raw power to the same standardized voltage and frequency as are supplied by the distribution grid. This allows it to either be used by local loads, such as lighting or appliances, or to be fed back into the grid. The most common types of power sources used in DG systems are the following:

#### Microturbine

Microturbines are small combustion turbines that operate with a turbine and compressor on the same shaft as the electrical generator. They can burn a number of fuels, such as natural gas, propane, and biofuel. Microturbines operate at speeds from 50,000 to 120,000 RPM, resulting in very high frequency AC power generation. The capacities of commercially-available microturbines range from tens to hundreds of kilowatts [2].

#### • Wind Turbine

Wind turbines are not strictly distributed generators, as their most common implementation is in large numbers as part of a *wind farm*. These farms generally consist of up to a hundred wind turbines, each of which can produce as much as 6MW of power, with average units producing 1 to 1.5MW. Individual units are also common, particularly in the form of small, non-commercial turbines in remote areas. Individual units are found in a wide range of capacities, from the commercial units of over 1MW to residential units of as low as several hundred watts. Wind turbines generally produce AC power at variable frequency, depending on wind speed [3]. Since they rely on the presence of wind to provide power, they must be combined with energy storage or an alternate power source [4].

#### Solar Cells

A solar cell is another device for producing electrical power from a renewable

source, in this case, light from the sun. These cells are generally combined into solar panels, which can be placed on the roofs of buildings among other locations. A solar panel produces variable, low-voltage DC power. The level of the voltage, as well as the amount of power produced, depends on the intensity of the light shining on the panel [5][6]. Therefore, like wind turbines, solar cells must be paired with an alternative power source or an energy storage device to provide uninterrupted power.

#### • Fuel Cell

Fuel cells produce electricity through a chemical reaction between hydrogen fuel and oxygen, usually derived from the atmosphere. Operating at steady-state, they produce a constant DC voltage; however, the voltage level does vary based on loading. A fuel cell behaves like a combination of a battery and a generator in that it produces a relatively constant DC voltage, but operates on external fuel, continuing to operate as long as that fuel is supplied.

### • Battery Pack

Technically, this is not a form of distributed generation because it does not actually produce electrical power. However, it does offer many of the same benefits, including providing backup power and redistributing load to less expensive, off-peak periods. Batteries produce a constant, low DC voltage through an internal chemical reaction. They must be recharged electrically, however, as they do not produce electricity from an external power source.

#### 1.1.2 POWER ELECTRONICS CONVERTERS

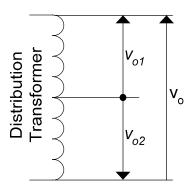

The purpose of the converter in a distributed generation system is to convert the raw power generated into a form compatible with the local distribution grid, thereby allowing the power to be used by standard appliances or to be fed back into the grid. Residential and light-commercial power in North America is provided in *single-phase three-wire* form (also known as *split-phase*). Generally, this arrangement is implemented using a center-tap on the distribution transformer. It provides two outputs at 110 to 120V rms, referred to as *half-phases*. Together, these also form one high-voltage output at 220V to 240V rms. The type

of converter required to produce these outputs from a DG depends on the type of generator used.

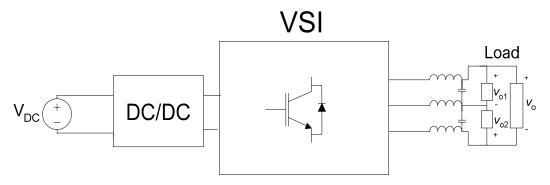

A very common type of conversion is from low-voltage DC to split-phase, utility-voltage AC. Solar cells, fuel cells, and battery packs all require this type of conversion. It is generally done in two stages. First, the low, potentially variable, DC voltage is converted to a higher, constant DC voltage, using a boost DC/DC converter. Next, the higher DC voltage is inverted to produce the desired single-phase three-wire outputs, usually with a voltage-sourced inverter (VSI). This system is shown in Fig. 1-1. Conversions from AC sources such as wind turbines and microturbines are most often done by adding an AC/DC converter (rectifier) before the DC/DC boost stage in Fig. 1-1. The AC voltage is converted to DC by the rectifier, and from there the process remains the same.

Fig. 1-1. Standard topology used to produce split-phase utility-voltage outputs from a low-voltage DC source

#### 1.1.2.1 Voltage-Sourced Inverters

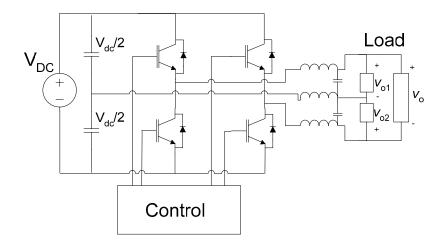

Existing voltage-sourced inverter topologies producing split-phase outputs are divided into two main categories: split DC capacitor or 'neutral point clamped' inverters, and three-leg inverters. An overview of some existing topologies is given in [7]. The split DC capacitor method establishes a loosely regulated balance of output voltages. An implementation of this scheme for photovoltaic systems is found in [8], and the basic topology is shown in Fig. 1-2. Two large DC capacitors hold the neutral point of the output approximately halfway between the positive and negative voltage rails. This approach successfully balances the output voltages when the difference between loads is not too large.

Fig. 1-2. Split DC capacitor method

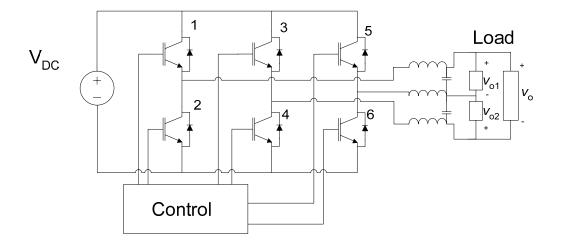

The second category of VSI split-phase topologies relies on a third leg of switches to regulate the neutral point voltage (Fig. 1-3). Generally, the original four switches (numbered 1 to 4 in the figure) are used to control the total output voltage,  $V_o$ . The additional two switches (numbered 5 and 6) maintain the neutral point voltage at  $V_{dc}/2$ . This can be accomplished with very simple, decoupled control, where switches 1 to 4 work as in the single-phase case and switches 5 and 6 alternate with a 50% duty cycle to hold the average neutral point voltage halfway between the DC rails. While straightforward, this technique improves upon the results of the split capacitor method, at the cost of two additional switches.

Fig. 1-3. Third-leg method

More complex switching schemes, such as state-feedback control, may also be implemented for this topology. These still tend to deal with switches 5 and 6 independently from switches 1 to 4 in terms of individual switching events. However, the modulation signals used to control the two groups of switches may be incorporated into a single control scheme in order to generate better regulated outputs [9][10]. These techniques provide better output voltage regulation, but are more complex and require measurement and feedback of output currents as well as voltages.

#### 1.1.2.2 Current-Sourced Inverters

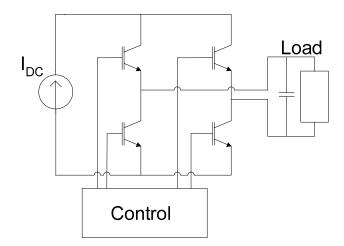

An alternative to the voltage-sourced inverter is the current-sourced inverter (CSI), shown in Fig. 1-4.

Fig. 1-4. Single-output current-sourced inverter topology

The CSI is the dual topology of the VSI. A VSI is supplied from a DC voltage, whereas a CSI is supplied from a DC current. The output of a VSI is a PWM-switched voltage, which must be low-pass filtered to achieve the desired output voltage waveform. The CSI's output is a PWM-switched current, which produces the desired voltage across an output filter capacitor. There are a number of advantages to using a CSI rather than a VSI. Several have previously been documented for FACTS converters [11][12][13] and medium- to high-voltage induction motor drives [14][15]. These benefits are also expected to be advantageous in split-phase generation:

- CSIs have built-in voltage boost capability, eliminating the need for a front-end DC/DC boost converter.

- Only a capacitor is required to filter the output, rather than an LC filter, because

the output current is controlled directly. This reduces the filter components

required and results in improved regulation of the output voltage.

- Since the DC current is regulated, usually using a large DC inductor, the CSI

provides automatic short-circuit and over-current protection.

- The output capacitor limits the dv/dt values seen by the inverter's switches. This and the over-current protection both tend to improve inverter reliability.

• The CSI facilitates grid connection. Since the grid provides a strong voltage, the power transferred can be controlled directly by controlling the output current from the inverter. This is essentially equivalent to the operation of a CSI-based STATCOM [12][13]. Using a VSI, the power transferred to the grid must be controlled indirectly, by varying the voltages across the output filter inductors.

However, there are also a number of obstacles that have prevented the use of CSIs in distributed generation to date:

- The current-sourced inverter must be supplied with a DC current input.

Therefore, while a DC/DC boost converter is not necessary, a front-end circuit is required to produce this DC current from a DC voltage source.

- Voltage-sourced inverters require switching elements that are unipolar in voltage and bidirectional in current. In other words, current must be able to flow in either direction, and only positive polarity voltage must be blocked. As the dual of the VSI, the CSI requires switching elements that are bipolar in voltage and unidirectional in current. They should be able to block voltage of either polarity, and current should flow in the forward direction only. This precludes the use of standard IGBTs, the most common type of switch used in medium-power voltage-sourced inverters, due to a lack of reverse voltage blocking capability. The alternatives to date have been less easily-controlled switches, such as GTOs, or the addition of series diodes to block reverse voltage, resulting in increased conduction losses. Recently, however, switches have been developed that combine the controllability of IGBTs with reverse voltage blocking capability, at the cost of a slight decrease in the switching speed. These are known as reverse-blocking non-punch-through, or RB-NPT, IGBTs [16].

- Existing current-sourced inverter topologies lack sufficient energy storage for use in distributed generation. During turn-on transients in the connected loads, the power requirements from the inverter may be several times those at steady-state. The energy storage device in a current-sourced inverter is a DC inductor, which cannot cost-effectively store energy on the same scale as a DC capacitor.

Therefore, without modification, this topology will be less able than a voltage-sourced inverter to withstand power transients at its outputs.

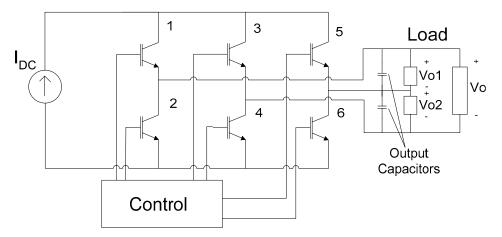

• There is no existing implementation of a current-sourced inverter producing splitphase outputs in literature. The third-leg approach for producing split-phase outputs from a voltage-sourced inverter could be adapted to suit current-sourced inverters. However, a new control technique will have to be developed, integrating all six switches into a single switching scheme in order to continuously provide a path for the DC current. Also, to maintain constant-RMS output voltages, the inverter control will have to vary based on the load impedances.

#### 1.2 CONTRIBUTIONS

Through the completion of the research described in this thesis, the following contributions were made:

- 1. Development of a topology and control algorithm to create an artificial current source for use with current-sourced inverters. This includes an energy storage technique that allows the DC current to be held constant in the presence of large power transients at the inverter's output(s).

- Modification of an existing control algorithm for three-phase current-sourced inverters, to allow its use with unbalanced or split-phase loads. This algorithm successfully balances the output voltages under severely unbalanced loading conditions, as well as with inductive and nonlinear loads.

- Additions to the existing three-phase algorithm include calculation of control signals based on split-phase output voltage feedback, and management of shootthrough current to equalize conduction losses among the inverter switches under split-phase loading conditions.

- Construction of a laboratory prototype current source preconditioning circuit and split-phase current-sourced inverter, based on existing current-sourced converter modules and measurement circuitry.

#### 1.3 THESIS OUTLINE

The goals of this thesis are to overcome the main challenges in the adoption of CSIs listed above, and to design a viable split-phase distributed generation system based on a low-voltage DC source and a current-sourced inverter. The thesis is composed of the following five chapters:

Chapter 1 reviews the existing technologies and literature, and outlines the advantages and obstacles faced in designing a current-sourced inverter-based distributed generation system. It then provides an outline of the subsequent chapters and summarizes the contributions of the thesis.

Chapter 2 describes the method of generating a constant DC current from a DC input voltage. An analysis is given of how to calculate the DC current reference level to achieve the desired performance. In addition, a novel topology and control scheme is developed to enhance the energy storage capabilities of the current-sourced inverter, allowing the DC current to be held constant even in the presence of large power transients at the inverter's output(s).

Chapter 3 presents two switching algorithms to produce equal split-phase output voltages using a three-leg current-sourced inverter. The algorithms use different methods to successfully generate balanced, split-phase output voltages under highly unbalanced loading conditions, while minimizing switching losses and high-frequency voltage ripple at the outputs.

The designs in Chapters 2 and 3 are verified using simulation and experimental results.

Chapter 4 describes the hardware and software of the experimental setup in greater detail, outlining several challenges encountered and the steps taken to resolve them. It also lists some practical techniques used to improve the performance of the control hardware.

Finally, Chapter 5 summarizes the results and contributions, and outlines potential future research

## **CHAPTER 2**

# **VOLTAGE SOURCE-TO-CURRENT SOURCE**

# **TOPOLOGY**

#### 2.1 INTRODUCTION

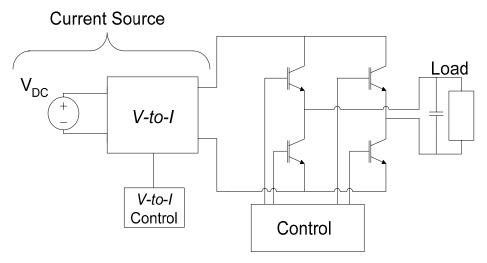

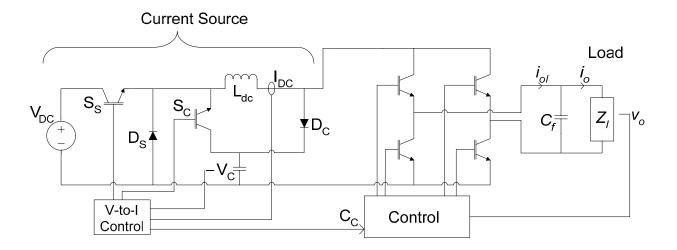

In order to produce a constant-RMS AC voltage using a current-sourced inverter, a DC input current is required. To use a current-sourced inverter for distributed generation, it is therefore necessary to convert the available low DC voltage to a DC current. The desired value of that DC current must also be determined. Finally, the current must be held constant under a wide range of inverter loading conditions. The required block is labelled *V-to-I* in Fig. 2-1. The combination of this block and the supply voltage source must be made equivalent to a current source. It is assumed that the connected current-sourced inverter is using pulse-width modulation (PWM) [17] to produce a sinusoidal output voltage.

Fig. 2-1. Current-sourced inverter with voltage source-to-current source conversion block

#### 2.2 OVERVIEW

This chapter begins with a brief review of current-sourced inverter technology, in section 2.3. Next, a basic circuit is presented in section 2.4 to produce a DC current from a DC voltage source, under relatively static loading conditions. Section 2.4 also covers the effects of ordering the DC current to various levels. Sections 2.5 and 2.6 build upon the earlier results, adding enhanced energy storage and a dynamic current reference level, to handle varying loads. Experimental results for this circuit are given in section 2.7. Finally, an optimized control algorithm is demonstrated in section 2.8.

#### 2.3 REVIEW OF CURRENT-SOURCED INVERTER OPERATION

A current-sourced inverter controls its output voltage by alternately directing its DC input current into an output filter capacitor in the forward and reverse directions. The output capacitor is charged when current is injected into its positively-charged rail and discharged when current is injected into its negatively-charged rail. (Note that the positively-charged rail alternates, since the output is AC.) Periods when the capacitor is being actively charged or discharged will be referred to as *active states*. There is a third mode of operation, in which the DC current circulates through the two switches in a single leg of the inverter and does not enter the output capacitor in either direction. This is known as a *shoot-through*

state. When the inverter is in a shoot-through state, the output capacitor will slowly discharge through the connected load.

#### 2.4 DC CURRENT CONTROL

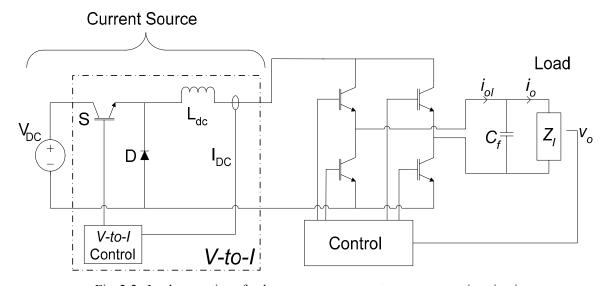

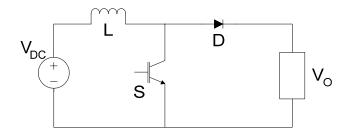

It was realized in [18] that when the DC current for a closed-loop controlled CSI was supplied using only a DC voltage source and an inductor, the current in the inductor tended to rise uncontrollably. A circuit composed of a switch S and a diode D (marked *V-to-I* in Fig. 2-2) was therefore used to limit the DC current to a set value. The circuit is essentially a buck DC-DC converter. When the DC current is lower than the reference, the switch is turned on. This supplies energy to the DC inductor, causing the DC current to rise. When the DC current is higher than the reference, the switch is turned off, causing the inductor current to circulate through the freewheeling diode. This results in a loss of stored energy in the DC inductor and a drop in the DC current. The DC current can therefore be regulated by controlling the duty ratio of the switch in a closed loop.

Fig. 2-2. Implementation of voltage source-to-current source conversion circuit

As implemented in [18], however, a large DC current ripple was experienced with this method. This can be understood by examining the effect of the reflected voltage at the input terminals of the current-sourced inverter (to the right of the inductor, L<sub>dc</sub>). This switched voltage is dependent on the output voltage of the inverter and on its switching action. The DC plus low-frequency (120-Hz) component of the reflected voltage is equal to the output

<u>Chapter 2 – Voltage Source-to-Current Source Topology</u>

voltage times the modulating signal of the inverter. (From this point forward, the 'reflected

voltage' will refer to this DC plus low-frequency component only.) For a single-output

inverter with an assumed constant DC current, the modulating signal is proportional to the

output current. Therefore, the reflected voltage is proportional to output voltage times

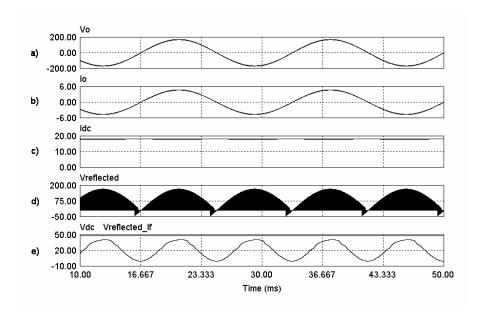

output current, i.e. instantaneous output power. Fig. 2-3 shows the resulting reflected

voltage when the circuit in Fig. 2-2 is run under the following conditions (Case 1):

DC Supply Voltage: 48V

AC Voltage: 120V rms

DC Inductor: 5mH

AC Filter Capacitor: 15μF

These specifications will be used for all simulations in this chapter, unless otherwise

noted. Case 1 also uses the following values for the DC current and load:

DC Current: 18A

Load: 400W (36- $\Omega$  resistor)

14

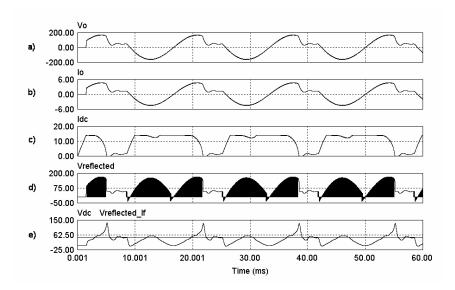

Fig. 2-3. Case 1: Reflected voltage under ideal operating conditions

a) Output voltage (V)

b) Output current (A)

c) DC Current (A)

d) Actual reflected voltage (switched) (V)

e) DC plus low-frequency components of reflected voltage compared to DC supply voltage (V)

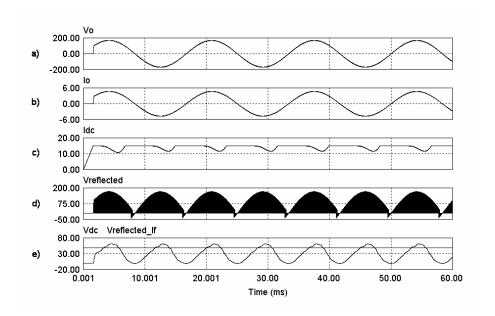

Because the load is resistive,  $v_o$  and  $i_o$  are in phase. The impedance of  $C_f$  at the fundamental frequency should be much larger than that of  $Z_i$ ; therefore, the fundamental component of  $i_{ol}$ , the switched current output from the inverter (Fig. 2-2), should also be nearly in phase with  $v_o$ . The resulting reflected voltage is a positively DC-shifted 120-Hz sine wave. If the peak of this voltage is higher than  $V_{DC}$ , the net voltage across the inductor at the peak will remain negative even with the switch on, and the DC current will fall below its reference. This is demonstrated in Case 2 (Fig. 2-4), where the DC current reference is 15A. This lower reference current results in a higher modulation index and a higher reflected voltage. As the low-frequency reflected voltage exceeds the supply voltage, the DC current dips lower. When the reflected voltage falls back below the supply voltage, the DC current is able to recover.

Fig. 2-4. Case 2: Effect of reflected voltage exceeding supply voltage

a) Output voltage (V)

b) Output current (A)

c) DC Current (A)

d) Actual reflected voltage (switched) (V)

e) DC plus low-frequency components of reflected voltage

compared to DC supply voltage (V)

If the current falls too far, however, it may not be possible to recover. As the current falls, the modulation index rises to maintain the output voltage. This increases the reflected voltage, further decreasing the DC current. The result can be a complete loss of stored energy in the inductor and a failure in operation. This is seen in Case 3 (Fig. 2-5), where the current reference setting is 14A.

Fig. 2-5. Case 3: Insufficient DC current resulting in system failure

a) Output voltage (V)

b) Output current (A)

c) DC Current (A)

d) Actual reflected voltage (switched) (V)

e) DC plus low-frequency components of reflected voltage

compared to DC supply voltage (V)

However, this failure can be prevented by maintaining a sufficiently high initial DC current. Just as a drop in the DC current causes the inverter's modulation index to increase, a higher DC current results in a lower modulation index and a reduction in the reflected voltage. Therefore, if the DC current is kept sufficiently high, the peak value of the 120-Hz reflected voltage will be lower than the supply voltage, and the current level will be sustainable. This circuit can then approximate an ideal current source, as was seen in Case 1.

#### 2.4.1 IDEAL DC CURRENT

The exact DC current level required to maintain the peak reflected voltage below the supply voltage can be calculated. The goal is to maintain the supply voltage,  $V_{DC}$ , higher than the peak of the reflected voltage,  $v_{reflected}$ , i.e.,

$$V_{DC} > v_{reflected.}$$

(2-1)

Also, one can write

$$v_{reflected} = v_o * m, \tag{2-2}$$

where  $v_o$  is the AC output voltage, and m is the modulating signal of the PWM inverter. Assuming the effect of the filter capacitor is negligible,

$$m = \frac{i_o}{I_{DC}}. (2-3)$$

By substituting (2-2) and (2-3) into (2-1), the following relationship is derived:

$$V_{DC} > \frac{v_o i_o}{I_{DC}} \tag{2-4}$$

Note that this is equivalent to

$$V_{DC}I_{DC} > v_o i_o. (2-5)$$

It is in fact possible to restate this entire reflected voltage problem as one of power balance. If the *instantaneous* output power,  $v_o i_o$ , exceeds the available input power,  $V_{DC}I_{DC}$ , energy will be removed from the system. (The *available* input power is the input power when the switch S is turned on. When the switch is off, the input power is zero.) The energy storage component in this system is the DC inductor. Therefore, as energy is removed, the DC current decreases, as was seen. The following analysis will continue in terms of reflected voltage; however, the same results can be achieved through power balance by simply moving  $V_{DC}$  and  $I_{DC}$  to the same side of the inequalities.

From (2-4), the supply voltage must be greater than the peak of the reflected voltage. Assuming the load is resistive, and so output voltage and current are in phase, this gives

$$V_{DC} > \frac{\sqrt{2}V_{O,rms}\sqrt{2}I_{O,rms}}{I_{DC}} = \frac{2P_{O}}{I_{DC}}.$$

(2-6)

The minimum current required to satisfy this inequality is defined as I<sub>DC,ideal</sub>, and is given by

$$I_{DC,ideal} \cong \frac{2P_O}{V_{DC}}, \tag{2-7}$$

where the approximately equal to sign is used because the effect of the output capacitor is being neglected. For the test conditions used in Cases 1 to 3 above, this results in  $I_{DC,ideal}$  = 16.67A, which is below the level used in Case 1 and above that used in Case 2, as expected.

The above analysis can be expanded to include inductive loads. Also, the effect of the output filter capacitor can be included in the calculations by considering it to be part of the load. To do so,  $i_o$  in (2-4) is replaced by the low-frequency component of the switched output current from the inverter,  $i_{ol}$  (shown in Fig. 2-2):

$$V_{DC} > \frac{v_o i_{oI,ff}}{I_{DC}}, \qquad (2-8)$$

where lf denotes the low-frequency component.  $i_{ol,lf}$  can be expressed in terms of  $v_o$  through the combined impedance of load and capacitor:

$$\vec{Z}_{O} = \left| \vec{Z}_{O} \right| \angle \vec{Z}_{O} = \vec{Z}_{L} \parallel \vec{X}_{C} \tag{2-9}$$

The instantaneous reflected voltage is then given by

$$v_{reflected} = \frac{v_o i_{oI,lf}}{I_{DC}} = \frac{\sqrt{2} V_{O,rms} \sin(\omega t) \left( \frac{\sqrt{2} V_{O,rms}}{\left| \vec{Z}_O \right|} \sin(\omega t - \angle \vec{Z}_O) \right)}{I_{DC}}, \quad (2-10)$$

which has a peak value of

$$V_{\text{reflected, peak}} = \frac{2V_{\text{O,rms}}^2 \cos^2\left(\frac{\angle \vec{Z}_{\text{O}}}{2}\right)}{\left|\vec{Z}_{\text{O}}\right|I_{\text{DC}}}.$$

(2-11)

Again,  $V_{DC}$  must be greater than  $V_{reflected,peak}$ . Therefore, substituting  $V_{DC}$  for  $V_{reflected,peak}$  and solving for  $I_{DC}$  gives  $I_{DC,ideal}$ :

$$I_{DC} > \frac{2V_{O,rms}^2 \cos^2\left(\frac{\angle \bar{Z}_O}{2}\right)}{\left|\bar{Z}_O\right| V_{DC}} \equiv I_{DC,ideal}$$

(2-12)

As before, this is equivalent to maintaining the input power greater than the peak of the instantaneous output power.

Given a 15- $\mu$ F filter capacitor, the result is  $I_{DC,ideal} = 16.84$ A. Comparing this to the earlier result of 16.67A from equation (2-7), it is clear that neglecting the effect of the capacitor was reasonable.

#### 2.4.2 REQUIRED AND MINIMUM DC CURRENT

There is another DC current threshold that is of interest: the lowest DC current reference level for which steady-state operation can be maintained. If the reference is set below this level, the current will fall below the reference and not recover, as in Case 3 above. This minimum reference level is the level at which the average real input power is equal to the real output power. Therefore, for steady state operation, the following inequality must be maintained:

$$V_{DC}\bar{I}_{DC} > \frac{V_{O,rms}^2}{|\bar{Z}_O|} \cos(\angle \bar{Z}_O) = P_O$$

(2-13)

This is equivalent to maintaining the supply voltage above the average reflected voltage:

$$V_{DC} > \frac{P_{O}}{\bar{I}_{DC}} = \bar{v}_{reflected}$$

(2-14)

The average DC current must be used here because once the reflected voltage exceeds the supply voltage, the DC current will not be constant. The threshold resulting from solving for  $\bar{I}_{DC}$  is defined as  $I_{DC,minimum}$ , and is given by

$$\bar{I}_{DC} > \frac{V_{O,rms}^2}{V_{DC} |\bar{Z}_O|} \cos(\angle \bar{Z}_O) \equiv I_{DC,minimum}. \tag{2-15}$$

This is referred to as  $I_{DC,minimum}$  because, given an infinite DC inductor, and therefore a constant DC current, this is the minimum current reference that would be required to maintain steady-state operation. Returning to the example above,  $I_{DC,minimum} = 8.33A$ .

Clearly this reference level is insufficient in practical circumstances, as failure was seen in Case 3 (Fig. 2-5), with a reference current of 14A.

When the current is allowed to vary, there is no closed-form solution for the current reference that will result in an average DC current of  $I_{DC,minimum}$ , as required by (2-15). This threshold, denoted as  $I_{DC,required}$ , can be found through simulation, using a process of elimination. In the above example,  $I_{DC,required}$  is already known to be between 12A and 14A from test cases 2 and 3. However, this method is slow and inefficient. The low-frequency variations in the current can instead be calculated using an ordinary differential equation.

$$\dot{I}_{DC} = \frac{\left(V_{DC} - v_{reflected}\right)}{L_{DC}} = \frac{\left(V_{DC} - \frac{2V_{O,rms}^2}{\left|\bar{Z}_O\right|} \sin(\omega t) \sin(\omega t - \angle \bar{Z}_O)\right)}{L_{DC}}$$

(2-16)

A Matlab script was written to test the sufficiency of a given DC current reference level,  $I_{REF}$ , using this formula. The formula is only valid when  $I_{DC} < I_{REF}$  because when  $I_{DC}$  exceeds  $I_{REF}$ , the switch S is turned off to prevent it from rising further. Therefore, the first step is to find the angle  $\omega t_0$  at which  $\dot{I}_{DC}$  becomes negative, for  $I_{DC}$ = $I_{REF}$ . This is done through simple iteration, although a more advanced algorithm for finding zero-crossings could be used.

Once this starting angle is found, it is used as the initial point for Matlab's ODE solver, *ode45*. The solution of the differential equation given in (2-16) is followed until one of the following four exit conditions is reached.

- 1. Current reference is sufficient: I<sub>DC</sub> returns to the reference level, I<sub>REF</sub>.

- 2. Current reference is not sufficient: The DC current falls below the required output current:

$$I_{DC} < \frac{\sqrt{2}V_{O,rms}}{\left|\vec{Z}_{O}\right|} \sin\left(\omega t - \angle\vec{Z}_{O}\right) = i_{oI,lf}$$

(2-17)

At this level, the inverter's modulating signal will be at its maximum value. If the DC current falls further, the inverter will be unable to maintain the output voltage.

- 3. Current reference is not sufficient: After one complete period ( $\omega t = \omega t_0 + \pi$ ),  $I_{DC}$  is still below the reference level,  $I_{REF}$ . If the current cannot recover within one complete period, it will continue to drop in subsequent cycles, until condition 2 is reached.

- 4. Current reference is not sufficient: I<sub>DC</sub> reaches a local maximum below the reference level. If the current reaches a local maximum and begins dropping again, it is not necessary to continue solving to the end of the period because it is known that eventually condition 2 will be reached.

Exit conditions 1 and 2 are sufficient to achieve the desired results; however, 3 and 4 prevent unnecessary calculations, improving execution time.

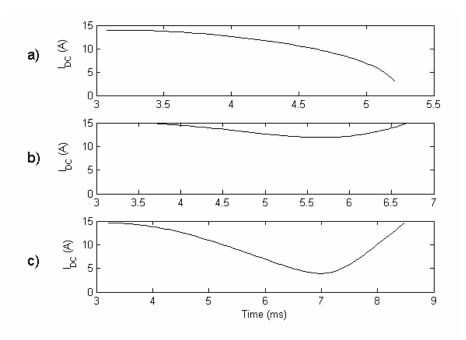

Fig. 2-6 shows the results of this script for Case 2 and Case 3 above. These results are consistent with the simulation results in Fig. 2-4 and Fig. 2-5. Through further iterations of the script, the approximate required current is found:

$$I_{DC.required} \cong 14.6A$$

, (2-18)

which is between 14A and 15A, as expected.

Fig. 2-6. Simulated variations in DC current using Matlab ODE-solver script

a) Current reference level of 14A: current cannot be maintained.

b) Current reference level of 15A: current can be maintained.

c) Current reference level of 14.6A = I<sub>DC,required</sub>: minimum level at which current can be maintained.

A wrapper script was written to prepare a matrix of required current reference levels over the entire range of possible loads. This matrix can be calculated offline, and then used to dynamically set the DC current reference level during inverter operation, based on the measured load. If step changes in loading are possible, the current reference must be sufficient to maintain operation not only under current conditions, but also given the new load following a step change.

#### 2.5 ADDITIONAL ENERGY STORAGE

The current source topology described in section 2.2 is capable of producing a constant current if the current reference is set greater than or equal to  $I_{DC,ideal}$ , or a sustainable current with DC and 120Hz components if the reference is set greater than or equal to  $I_{DC,required}$ . However, as well as the existent load, the current reference must be set to accommodate the worst-case step change in load, since it is no longer possible to increase the DC current level once the output power exceeds the available input power. Keeping a high DC current results

in larger losses and increased component stresses. Moreover, most loads do not exhibit step changes, but rather have a transient power spike during turn-on. These transients can be as high as ten times the steady-state power requirements for a period of several milliseconds (in the case of a light bulb), or two to three times the steady-state power for up to several seconds (in the case of an induction motor [19]). It is not feasible for the DC current reference to be set high enough to accommodate these transient loads. One alternative would be to store sufficient energy in the DC inductor to supply the power during these turn-on transients without the current dropping below the I<sub>DC,required</sub> threshold. However, this is not feasible either, given a practical inductor size. For example, a light bulb turn-on transient of 1000W for 10ms would require on the order of 10J of energy. To provide this energy from a DC inductor with a current of 20A, without the current falling below 15A, a 114mH inductor would be required. For a motor turn-on transient, the requirement would be much higher. If this current source topology is to function with transient power spikes, an additional energy storage technique is required.

#### 2.5.1 SUPPLEMENTAL ENERGY-STORAGE CIRCUIT

Additional energy storage was introduced in the circuit of Fig. 2-2, as shown in Fig. 2-7. A high power draw at the output of the inverter, such as during a turn-on transient, results in a high reflected voltage at the inverter's input terminals, at the right side of the DC inductor. Therefore, in order to maintain the current in the DC inductor during these events, it is necessary to apply an equally high voltage to its left side. This is done by turning on the switch  $S_C$ . The capacitor is kept charged to a voltage above the peak of the output voltage. From (2-2), the maximum reflected voltage is equal to the output voltage, and occurs when the modulating signal, m, is equal to 1. Therefore, if the capacitor voltage,  $V_C$ , is kept higher than the peak of  $v_O$ , it will be possible to maintain the DC current under any loading condition.

Fig. 2-7. Current-sourced inverter with voltage source-to-current source conversion circuit and supplemental energy storage

The energy-storage capacitor is charged through the diode  $D_C$ . Another reason for keeping  $V_C > \max(v_o)$  is that a diode can be used in this position rather than a switch. During normal inverter operation, the diode will always be reverse biased, and will therefore not conduct. The capacitor can then be charged by opening the current path through the inverter, forcing the DC current into the diode path. Since the switch  $S_C$  is also off during charging, the DC current flows into the capacitor. This charging can only occur during shoot-through states, since interrupting the current through the inverter during an active state would affect the output current, and thereby the output voltage. During capacitor charging, the circuit behaves identically to a boost converter. A standard boost converter is shown in Fig. 2-8 for comparison. The entire inverter block in Fig. 2-7 corresponds to the switch S in Fig. 2-8. The diode  $D_C$  corresponds to the diode D. The capacitor voltage,  $V_C$ , corresponds to the output voltage of the boost converter,  $V_O$ . While the circuit is operating as a boost converter to charge the capacitor, the switch  $S_S$  remains closed and the switch  $S_C$  remains open. There is no theoretical limit to the capacitor voltage; although, to reduce switching losses, it is advantageous not to charge it higher than necessary.

Fig. 2-8. Basic boost converter

The energy required to supply a transient power surge is equal to the power level of the surge times its length in time:

$$E_{T} = P_{T} * t_{T} \tag{2-19}$$

The available stored energy in the capacitor is

$$E_{C} = \frac{1}{2}C(V_{C}^{2} - v_{o,peak}^{2})$$

(2-20)

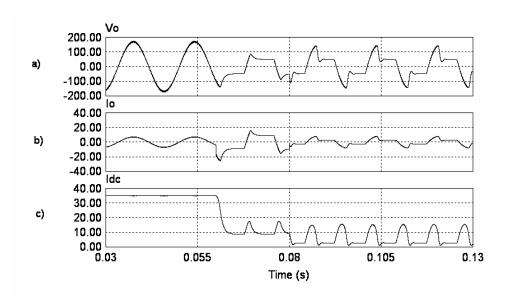

because the capacitor voltage cannot be allowed to fall below the peak output voltage. This supplemental energy-storage circuit can therefore supply the required power to any transient with energy  $E_T < E_C$ . Once the transient power spike has ended, the capacitor can be recharged during shoot-through states. The operation of this circuit is demonstrated through simulation in Fig. 2-9 and Fig. 2-10. The output power is 600W until time 0.06s, and then steps up to 1600W for approximately one cycle, before dropping back to 800W. This simulates the turn-on transient of a 200W incandescent light. For both tests, the DC current reference is 35A. Fig. 2-9 shows the results without the supplemental energy storage. When the spike in output power results in  $I_{DC} < I_{DC,required}$ , the DC current drops and is unable to recover. In Fig. 2-10, the effect of the additional energy-storage circuit is seen. Energy is taken from the capacitor to maintain the DC current level until the transient passes. The capacitor is then slowly recharged to its steady-state (constant) value. A 2.2-mF capacitor was used in this simulation. In order to supply larger transients, such as during turn-on of a motor, a larger capacitor or an ultracapacitor could be used.

Fig. 2-9. Failure of Current-Sourced Inverter due to turn-on transient

a) Output (load) voltage (V)

b) Output (load) current (A)

c) DC Current (A)

Fig. 2-10. Successful supply of 1800W turn-on transient, using supplemental energy-storage circuit

- a) Output (load) voltage (V)

- b) Output (load) current (A)

- c) DC Current (A)

- d) Capacitor Voltage (V)

#### 2.5.2 STEADY-STATE OPERATION

As well as supplying transient power spikes, this supplemental energy-storage circuit can improve the steady-state operation of the inverter. In section 2.4, several thresholds for the DC current reference level were introduced. If the reference is set to at least I<sub>DC,ideal</sub>, given in (2-12), the DC current can be held constant for a constant load. If the reference is set below I<sub>DC,ideal</sub>, but above I<sub>DC,required</sub>, steady-state operation can be maintained, but the DC current will exhibit cyclical 'dips' at 120Hz. Finally, I<sub>DC,minimum</sub> (2-15) is the theoretical minimum DC current for the input power to be at least equal to the output power. However, it is only valid if the DC current is held constant, which was not the case for the initial current source circuit described in section 2.4.

With the addition of the supplemental energy-storage circuit shown in Fig. 2-7, the DC current can in fact be held constant, regardless of its level, as long as the capacitor has sufficient stored energy. To maintain the energy in the capacitor at steady-state, it is simply necessary that the available input power to the circuit be at least equal to the output power:

$$V_{DC}I_{DC} \ge P_{O}, \qquad (2-21)$$

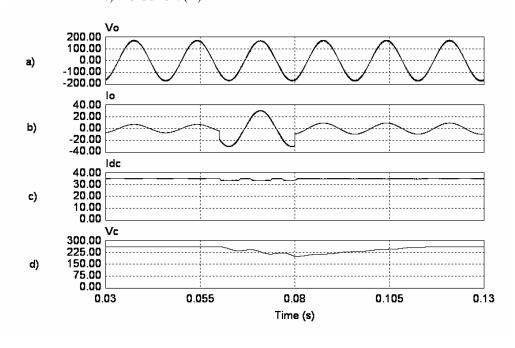

or equivalently,  $I_{DC} \ge I_{DC,minimum}$ , as given by (2-15). The minimum DC current required for steady-state operation is reduced from  $I_{DC,required}$  to  $I_{DC,minimum}$ . For the example given in section 2.4 above, this is a reduction from 14.6A to 8.33A, i.e., by 42.9%. The difference will be most pronounced when a small DC inductor is used.

In Fig. 2-11, a load power of 400W is drawn. While all other elements are unchanged from section 2.4, the additional energy storage allows this circuit to function with a DC current of only 10A. It failed with a current of 14A in Case 3 (Fig. 2-5) without the benefit of supplemental energy storage.

Fig. 2-11. Reduction of required DC current for steady-state operation due to addition of supplemental energy-storage circuit

- a) Output (load) voltage (V)

- b) Output (load) current (A)

- c) DC Current (A)

- d) Capacitor Voltage (V)

Reducing the operating DC current will result in lower conduction losses. Lower current and the elimination of 120Hz variations in the current result in lower stresses on the switching components. However, any switching (charging or discharging) of the energystorage capacitor does increase switching losses, both in the six inverter switches and in the capacitor switch, S<sub>C</sub>. Although the current being switched is lower, the voltage is higher. In addition, high-frequency variations in the DC current will be greater, as a large capacitor voltage,  $V_C$ , produces a large di/dt when applied across the DC inductor. (The precise switching action of the energy-storage circuit and its effect on the DC current at the switching frequency will be examined in section 2.5.3.) The benefit of lower DC current must be weighed against these drawbacks to determine whether operation of the capacitor energy-storage circuit at steady-state is desirable. Regardless of this choice, the circuit will allow recovery from turn-on transients or large step changes in loading, which otherwise would have resulted in failure. If it is only used during transients, no additional steady-state losses are incurred, since no components are added to the current path. The addition of this simple energy-storage circuit is therefore clearly beneficial.

#### 2.5.3 METHOD OF CONTROL

The straight-forward control technique used for the tests presented thus far will be described in this section. Section 2.8 will present an alternative, optimized algorithm. Note that the results given in this chapter are intended to demonstrate the operation of the voltage source-to-current source preconditioning circuit, and do not cover the various possible inverter loading conditions. Chapter 3 investigates inverter control, and gives several test cases for various inverter loads.

The *V-to-I* control system controls the supply switch, the capacitor switch, and the charge-capacitor control signal, based on feedback of the DC current and the capacitor voltage, as was shown in Fig. 2-7. The primary goal of this system is to keep the DC current, I<sub>DC</sub>, as close as possible to its reference level, I<sub>REF</sub>. In the most basic implementation, the reference level is constant and pre-defined. The secondary goal is to hold the capacitor voltage near its reference level. As described in section 2.5.1, this level must be at least equal to the peak output voltage plus a sufficient amount to supply the necessary energy for the largest expected transient (2-20).

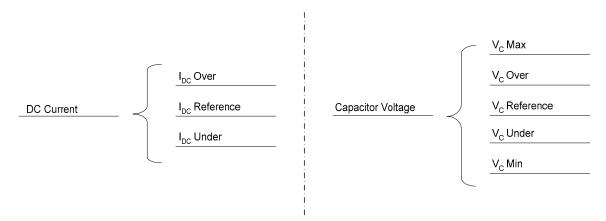

A digital control block is used both for the simulations throughout this chapter and for the experimental results of section 2.6. At each operation of the control block, the measured DC current and capacitor voltage are compared to a set of reference levels, as shown in Fig. 2-12. These levels are defined in Table 2-1 and Table 2-2.

Fig. 2-12. Comparison of I<sub>DC</sub> and V<sub>C</sub> to reference levels

Table 2-1. DC Current Reference Levels

| I <sub>DC</sub> Over      | Set slightly above $I_{DC}$ Reference (1% to 4%). If $I_{DC}$ rises above this level, it indicates that the reflected voltage is negative, and so the DC current is rising even with the supply switch, $S_{S}$ , turned off.                      |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I <sub>DC</sub> Reference | The desired DC current level.                                                                                                                                                                                                                      |

| I <sub>DC</sub> Under     | Set 1% to 4% below $I_{DC}$ Reference. If $I_{DC}$ falls below this level, it indicates that the reflected voltage is greater than the supply voltage, and that the current is continuing to fall, even with the supply switch, $S_S$ , turned on. |

Table 2-2. Capacitor Voltage Reference Levels

| V <sub>C</sub> Max       | The maximum safe capacitor voltage, based on component tolerances.  The capacitor will never be charged beyond this level.                                                                                                   |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>C</sub> Over      | Set slightly above $V_{\rm C}$ Reference (4% to 5%). If $V_{\rm C}$ rises above this level, the controller will attempt to bring it back down to $V_{\rm C}$ Reference without disrupting the DC Current level.              |

| V <sub>C</sub> Reference | The desired capacitor voltage level.                                                                                                                                                                                         |

| V <sub>C</sub> Under     | Set slightly below $V_{\mathbb{C}}$ Reference (4% to 5%). If $V_{\mathbb{C}}$ falls below this level, the controller will attempt to bring it back up to $V_{\mathbb{C}}$ Reference without disrupting the DC Current level. |

| V <sub>C</sub> Min       | The minimum allowable capacitor voltage, equal to the peak output voltage plus a margin of error of several percent. The capacitor will never be discharged below this level, except at turn-on and shut-down.               |

As long as  $I_{DC}$  and  $V_{C}$  are between their respective 'Over' and 'Under' reference levels, the supplemental energy-storage circuit is not used. The supply switch,  $S_{S}$ , will simply be turned on if the DC current is below  $I_{DC}$  Reference, and turned off if it is above. Therefore, the maximum possible operating frequency of the switch is one half the frequency of the digital control block. However, the switch will only operate at this maximum frequency when the reflected voltage is equal to approximately half the supply voltage. When the reflected voltage is close to the supply voltage, the magnitude of the negative voltage across the DC inductor when the switch is off will exceed the magnitude of the positive voltage when the switch is on.  $I_{DC}$  will therefore fall faster than it rises, and so the switch will be left

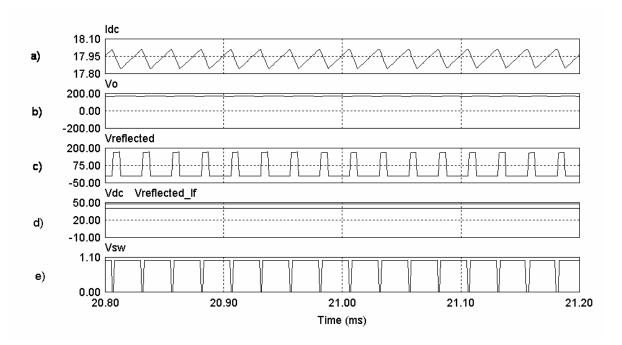

on for several cycles for each cycle that it is turned off, as shown in Fig. 2-13. Likewise, when the reflected voltage is less than half the supply voltage, the supply switch must be off for several cycles for eachs one that it is on, as seen in Fig. 2-14. The circuit operation in these figures is as in Case I of section 2.4.

Fig. 2-13. Operation of supply switch when reflected voltage is nearly equal to supply voltage

- a) DC Current (A)

- b) Output voltage (V)

- c) Reflected voltage (V)

- d) Low frequency component of reflected voltage compared to supply voltage (V)

- e) Gating signal to supply switch

Fig. 2-14. Operation of supply switch when reflected voltage is approximately zero

- a) DC Current (A)

- b) Output voltage (V)

- c) Reflected voltage (V)

- d) Low frequency component of reflected voltage compared to supply voltage (V)

- e) Gating signal to supply switch

If either  $I_{DC}$  or  $V_C$  moves outside of the range defined by its 'Over' and 'Under' reference values, they are controlled using either the capacitor switch,  $S_C$ , or the charge-capacitor control signal,  $C_C$ . When  $C_C$  is on during a shoot-through state of the current-sourced inverter, all inverter switches are turned off, forcing the DC current into the diode,  $D_C$ , path, and charging the energy-storage capacitor. This is the purpose of the control path shown between the *V-to-I* and inverter control blocks in Fig. 2-7.

Since it is not necessary to hold the capacitor voltage at a precise level, the signals specifying whether the capacitor voltage is under or over the reference range are latched. No attempt is made to correct the capacitor voltage until it reaches the  $V_C$  Over or  $V_C$  Under reference level. At that point, the respective  $V_C$  High or  $V_C$  Low signal is set to *true* until the voltage is returned to its ideal level. The control signals for the two switches and for charging of the capacitor are set as follows:

$$S_S = ((I_{DC} \le I_{REF}) \text{ AND NOT}(V_C = High)) \text{ OR } ((I_{DC} \le I_{DC} = Over) \text{ AND } (V_C = Low))$$

(2-22)

$$S_C = ((I_{DC} < I_{DC} Under) AND (V_C > V_C Min)) OR ((I_{DC} < I_{REF}) AND (V_C High)) (2-23)$$

$$C_C = ((I_{DC} > I_{DC} - Over) AND (V_C < V_C - Max)) OR ((I_{DC} > I_{REF}) AND (V_C - Low))$$

(2-24)

The supply switch is turned on whenever energy needs to be added to the system. This is evidenced by one of I<sub>DC</sub> and V<sub>C</sub> being below its desired level while the other is not above its range. The capacitor switch is turned on when the DC current is too low or the capacitor voltage is too high. However, the current takes precedence, so the switch will never be turned on if the DC current is above its reference level. Likewise, the charge-capacitor control signal is set high when the DC current is too high or the capacitor voltage is too low, as long as the DC current is at least at its reference level. At steady-state, if the DC current reference level is set below I<sub>DC.required</sub>, as described in section 2.4.2, these controls will result in periodic charging and discharging of the capacitor. When the reflected voltage rises above the supply voltage (the instantaneous power exceeds the input power), the capacitor switch is turned on when necessary to keep  $I_{DC} > I_{DC}$  Under. For each control cycle when the switch is on, the capacitor voltage is reduced slightly. Once the reflected voltage drops below the supply voltage, the DC current will return to its reference level. Each time the current exceeds its reference while the capacitor voltage is still low, the charge-capacitor signal will go high, and the capacitor will be charged during inverter shoot-through states. Assuming the DC current reference is greater than I<sub>DC.minimum</sub> (2-15), and so steady-state operation is sustainable, the capacitor voltage will return to its original level by the end of the 120-Hz cycle.

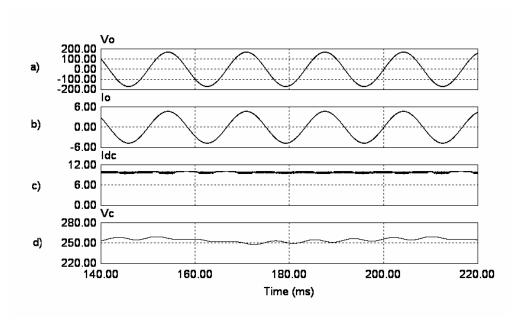

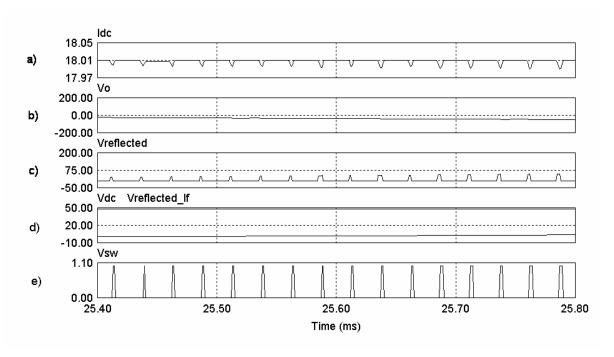

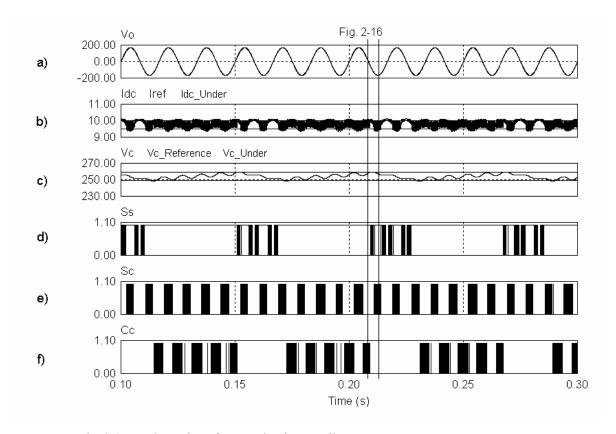

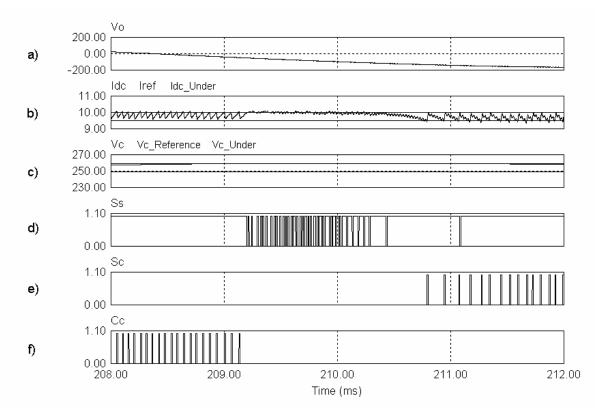

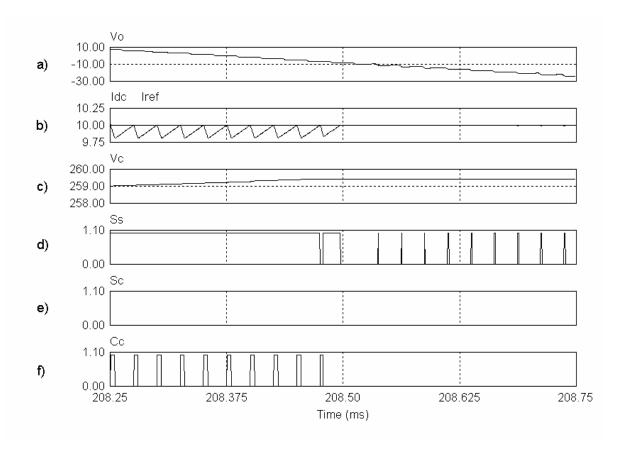

Fig. 2-15 shows control signals for the test given in Fig. 2-10. Because the DC current is very near to I<sub>DC,minimum</sub>, the supply switch remains on a majority of the time. The capacitor switch is used periodically, as expected, whenever the instantaneous output power exceeds the supplied power, or equivalently, the 120Hz reflected voltage exceeds the supply voltage. At points in the cycle when the instantaneous power draw and reflected voltage are low, and the DC current is able to reach its reference level, the capacitor can be recharged. If the capacitor voltage is not low, the supply switch is turned off instead.

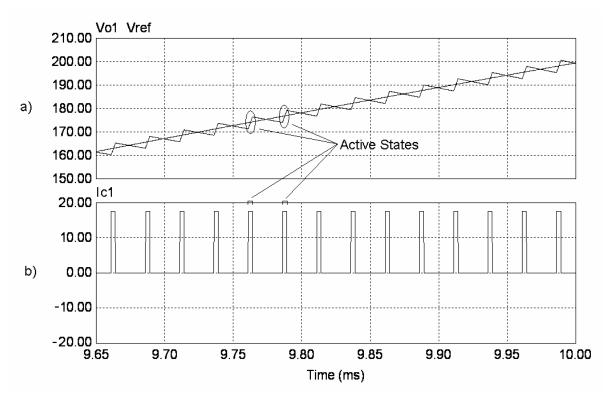

Fig. 2-16 shows a small time-slice of the previous figure, so that the switching action can be seen clearly. Small ripples are seen in the DC current due to switching of the inverter and of the supply switch. Larger ripples are seen due to charging and discharging of the capacitor. The higher the capacitor voltage, the larger these ripples will be, so it is desirable to keep the voltage as low as possible, while maintaining sufficient energy to supply any possible transients.

Fig. 2-15. Operation of *V-to-I* circuit controller

- a) Output voltage (V)

- b) Comparison of DC current to reference levels (A)

- c) Comparison of capacitor voltage to reference levels (V)

- d) Supply switch gating signal

- e) Capacitor switch gating signal

- f) Charge-capacitor control signal

Fig. 2-16. Switching operation of *V-to-I* circuit controller over short time period

- a) Output voltage (V)

- b) Comparison of DC current to reference levels (A)

- c) Comparison of capacitor voltage to reference levels (V)

- d) Supply switch gating signal

- e) Capacitor switch gating signal

- f) Charge-capacitor control signal

# 2.6 DYNAMIC CURRENT REFERENCE SETTING

In order to keep losses minimal, it is desirable to modify the DC current reference level as the load changes, so that the current is never higher than necessary. Several schemes could be used to do this, depending on the objectives.

1. For constant DC current and minimal use of the energy-storage capacitor:

As covered in section 2.4.1, to keep a constant DC current without using supplemental energy storage at steady-state, it is necessary to set the current reference level greater than or equal to  $I_{DC,ideal}$  (2-12).  $I_{DC,ideal}$  is equal to the peak

of the instantaneous output power divided by the DC source voltage, and therefore varies with changes in loading. The peak output power can be easily determined by tracking  $v_o$  and  $i_o$  over a single 120-Hz period and taking the maximum value. ( $v_o$  is measured directly, and  $i_o$  is known to be equal to  $I_{DC}*m$ .) The DC current reference can then be updated once each period. If a change in load causes  $I_{DC,ideal}$  to rise above  $I_{DC}$ , the current can be maintained until the next reference update using the energy-storage capacitor.

2. For minimal DC current (allowing some 120-Hz ripple) and minimal use of the energy-storage capacitor:

In this case, the current reference must be set greater than or equal to  $I_{DC,required}$ , which also varies with the loading level. There are two ways to determine  $I_{DC,required}$  at run-time. The first is to produce a matrix of  $I_{DC,required}$  values over the range of possible loading levels (resistive and inductive), using the scripts described in section 2.4.2. Then, at run-time, the real and reactive output powers can be calculated from the output voltage and current, measured as in case 1. The operating power is then compared to the matrix to find a value for  $I_{DC,required}$ . Also as in case 1, the DC current can be maintained by the energy-storage circuit if its required level changes between reference updates.

The second method is to perform the analysis done by the script of section 2.4.2 in real-time, using the physical converter rather than a simulation. A series of potential current reference levels would be tested to determine whether they are sustainable without the use of the energy-storage circuit. If condition 2, 3, or 4 of section 2.4.2 is reached, the current reference is not sustainable. The energy-storage circuit would then be used to bring the DC current back up to the next potential level to be tested. Once a minimal sustainable level is found, the energy-storage circuit is not required again until a change in load is detected and the process is repeated. This method is preferable if nonlinear loads are expected, as their current requirements may be different from linear loads at the same power levels.

3. For minimal, constant DC current, using energy-storage capacitor at steady state:

In this case, the DC current reference must be set greater than or equal to  $I_{DC,minimum}$ , as given by (2-15).  $I_{DC,minimum}$  is equal to the RMS output power divided by the DC source voltage. The output power can be calculated using  $v_o$  and  $i_o$ , as in case 1.

# 2.7 EXPERIMENTAL RESULTS