# High IF Digitizer Based on Quantized Feedback

by

### Ardeshir Namdar Mehdiabadi

A thesis

presented to the University of Waterloo

in fulfilment of the

thesis requirement for the degree of

Doctor of Philosophy

in

Electrical Engineering

Waterloo, Ontario, Canada, 1998

©Ardeshir Namdar Mehdiabadi 1998

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre reférence

Our file Notre reférence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-32846-5

The University of Waterloo requires the signatures of all persons using or photocopying this thesis. Please sign below, and give address and date.

### **Abstract**

This thesis discusses the issues and solutions of quantized feedback for high IF digitizers in wireless communication systems. The first part of the thesis examines different types of architectures that can be used for IF digitizers. In the second part of the thesis, the quantized feedback and its effect on the distortion is examined and compared with the continuous amplitude feedback method. A new sigmadelta modulator architecture is proposed to improve quantized feedback behavior and a brief theoretical analysis is mentioned. Design problems due to the new architecture are investigated and a 400MHz IF digitizer with low distortion using the new technique is designed. The prototype design achieves a very low distortion and suppresses the loop distortion created by conventional architectures by more than 40dB. The IM3 for this prototype is also reduced by more than 20dB.

### Acknowledgements

This thesis is the outcome of the help and goodwill of many people over the last six years of my stay here at the University of Waterloo, some whom I can readily remember and some whom I cannot. The debts of gratitude owed to some of these people acknowledged here.

First I would like to thank the Iranian government who supported me for the first four years of my research. Then I would like to thank Prof. Bosco Leung for his effort to guide my research and to encourage my efforts. I also want to thank him and the graduate chair of the Department of Electrical and Computer Engineering of the University of Waterloo. Prof. Vannelli. for their financial support in the last two years. I would like to thank Prof. Brodersen from the University of California at Berkeley. Prof. Lipshitz of the Department of Mathematics at the University of Waterloo. and Prof. Opal. Prof. Selvakumar. and Prof. Barby from the Department of Electrical and Computer Engineering of the University of Waterloo. who agreed to read my thesis and attend my defense.

My fellow friends and colleagues, some of whom have already left the University and some of whom still studying: Dr. Feng Chen, Dr. Subhajit Sen, Dr. Sameti. Dr. Sheikhzadeh, Dr. Dabiri, Dr. Hessabi, Kerwin Johnson, Yalin Ren, Stephen Au, John Wu, Mohsen Mousavi, Tom Dryburgh, Dr. Aflatooni and many other friends whose help on my research or having chat sessions over cups of coffee or in the VLSI lab make life easy for me and helped me to forget the hard times.

The staff of the Department of Electrical and Computer Engineering for their willingness to help whenever I approached them: Wendy Boles, Gini Ivan-Roth.

Dona Obrecht. and Lynda Lang.

Our computer administrator Phil Regier who kept the computers going for 24 hours a day without any interruption and with his numerous help on the programs and CAD and computer problems.

I would also like to thank Peter Edmonson of RIM. Waterloo for his eagerness to help, and for lending me equipment and components.

I would like to thank CMC personnel with their support, technically and financially in terms of fabricating my chips, and especially for their patience on the late chip submission.

Last but not the least. I would like to express my indebtedness to my parents for their support and encouragement without which I would not be here, and my wife who supported me for all the long housr I stayed in the lab.

# Contents

| 1 | Intr | oducti   | on                                               | 1  |

|---|------|----------|--------------------------------------------------|----|

|   | 1.1  | Resear   | ch Objectives                                    | 2  |

|   | 1.2  | Thesis   | Organization                                     | 3  |

| 2 | IF 1 | Digitize | er Architectures                                 | 4  |

|   | 2.1  | A/D c    | converters in wireless and digital communication | 4  |

|   |      | 2.1.1    | Analog and digital domain demodulation           | 4  |

|   |      | 2.1.2    | IF digitization                                  | 8  |

|   | 2.2  | Sampl    | e/Hold Circuit and Sampling Mixer                | 11 |

|   | 2.3  | Low-p    | ass sigma-delta modulator                        | 14 |

|   |      | 2.3.1    | Hardware architectures                           | 15 |

|   |      |          | 2.3.1.1 Single stage architectures               | 15 |

|   |      |          | 2.3.1.1.1 First order architecture               | 15 |

|   |      |          | 2.3.1.1.2 Higher-order architecture              | 18 |

|   |      | 2.3.2    | Design issues of low-pass sigma-delta Modulator  | 24 |

|   |      |          | 2.3.2.1 Extra gain in Feed forward path          |    |

|   |      |          | 2.3.2.2 Non ideal integrator                     | 25 |

|     |         | 2.3.2.2.1 Leakage in the integrators                         | 25 |

|-----|---------|--------------------------------------------------------------|----|

|     |         | 2.3.2.2.2 Integrator settling time                           | 26 |

|     |         | 2.3.2.3 Comparator Requirement                               | 31 |

|     |         | 2.3.2.4 Clock Jitter                                         | 31 |

|     | 2.3.3   | Design procedure                                             | 33 |

|     |         | 2.3.3.1 Design Example                                       | 36 |

| 2.4 | band-   | pass architecture                                            | 40 |

|     | 2.4.1   | Band-Pass structure definition                               | 43 |

|     | 2.4.2   | Low-pass to band-pass conversion                             | 46 |

|     | 2.4.3   | Hardware requirement                                         | 52 |

|     |         | 2.4.3.1 Capacitor and $1/f$ Noise                            | 52 |

|     |         | 2.4.3.2 opamp Speed                                          | 53 |

|     |         | 2.4.3.3 opamp gain                                           | 55 |

|     |         | 2.4.3.4 Sample-and-Hold Circuits                             | 56 |

|     | 2.4.4   | Design procedure                                             | 56 |

|     |         | 2.4.4.1 Design Example                                       | 57 |

| 2.5 | Band-   | pass vs low-pass                                             | 60 |

| 2.6 | Summ    | nary                                                         | 62 |

| The | eory of | Distortion Behavior in a Quantized Feedback Loop             | 63 |

| 3.1 | Introd  | luction                                                      | 63 |

| 3.2 | Theo    | ory of Nonlinear Component's Distortion Behaviour in a Clas- |    |

|     | sical l | Feedback loop                                                | 64 |

| 2 2 | 1 hit   | Quantized Feedback                                           | 70 |

3

|   |     | 3.3.1  | CASE 1: $f(u)$ is nonlinear but time invariant                | 75  |

|---|-----|--------|---------------------------------------------------------------|-----|

|   |     | 3.3.2  | CASE 2: $f(u)$ is nonlinear but time varying                  | 76  |

|   | 3.4 | A new  | architecture for a single-bit quantized feedback              | 81  |

|   | 3.5 | Stabil | ity consideration for the new architecture                    | 83  |

|   | 3.6 | Simula | tion results                                                  | 85  |

|   | 3.7 | White  | Noise Modeling of the new architecture                        | 87  |

|   |     | 3.7.1  | A white noise model for low frequency applications of the new |     |

|   |     |        | architecture                                                  | 88  |

|   |     | 3.7.2  | A white noise model for high frequency applications of the    |     |

|   |     |        | new architecture                                              | 90  |

|   | 3.8 | Summ   | ary                                                           | 92  |

| 4 | Des | ign of | the IF Digitizer                                              | 93  |

|   | 4.1 | Adder  | Design                                                        | 94  |

|   |     | 4.1.1  | An Adder Design Using a Current Approach                      | 95  |

|   |     |        | 4.1.1.1 Linear Region Technique                               | 97  |

|   |     |        | 4.1.1.2 Saturation region technique                           | 98  |

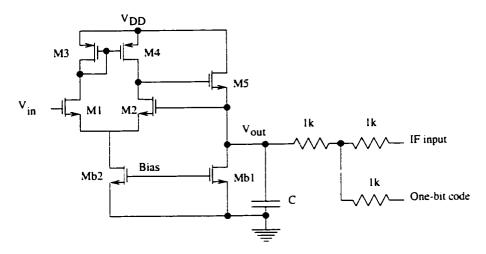

|   |     |        | 4.1.1.3 Circuit Design for a Voltage to Current Converter     | 99  |

|   |     | 4.1.2  | Voltage Summing                                               | 103 |

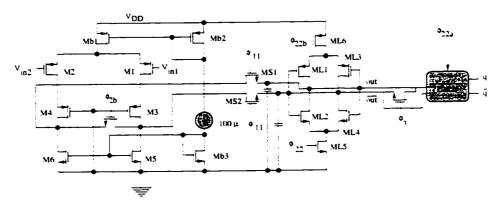

|   | 4.2 | Loop   | Filter Design                                                 | 104 |

|   | 4.3 | Recon  | struction Filter Design                                       | 109 |

|   |     | 4.3.1  | Linearity of The Reconstruction Filter                        | 110 |

|   |     | 4.3.2  | CMOS Buffer Design                                            | 112 |

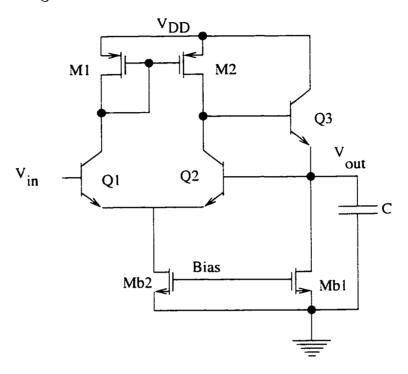

|   |     | 4.3.3  | BICMOS Buffer Design                                          | 115 |

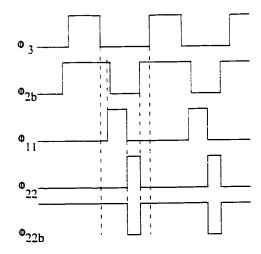

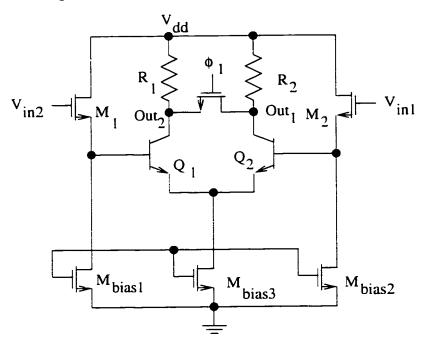

|   | 4.4   | Comparator Design                                 | 16          |

|---|-------|---------------------------------------------------|-------------|

|   |       | 4.4.1 CMOS Comparator                             | 16          |

|   |       | 4.4.2 BiCMOS Comparator                           | 18          |

|   | 4.5   | Sampling Mixer Design                             | 21          |

|   | 4.6   | Summary                                           | .22         |

| 5 | Exp   | perimental Results                                | 23          |

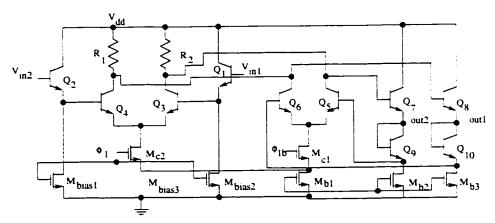

|   | 5.1   | IF Digitizer Using A Current Approach for Summing | 23          |

|   |       | 5.1.1 IC Implementation                           | .24         |

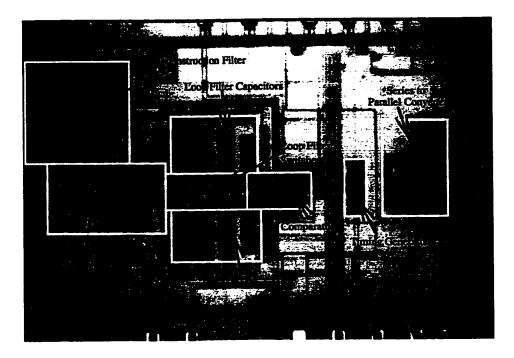

|   |       | 5.1.2 Test Results                                | 25          |

|   | 5.2   | IF Digitizer Using a Voltage Approach for Summing | <b>12</b> 9 |

|   |       | 5.2.1 IC Implementation                           | <b>29</b>   |

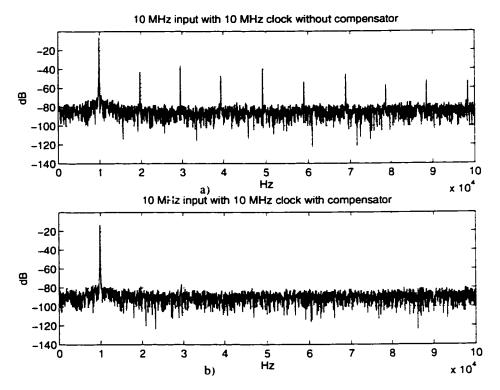

|   |       | 5.2.2 Test Results                                | 129         |

|   | 5.3   | Test Setup                                        | 132         |

| 6 | Cor   | nclusions and Future Work 1                       | 34          |

|   | 6.1   | Key Contributions                                 | 134         |

|   | 6.2   | Future Work                                       | 135         |

| В | iblio | graphy 1                                          | .36         |

# List of Figures

| 2.1  | Phase-shift discriminator of quadrature detector                                | 5  |

|------|---------------------------------------------------------------------------------|----|

| 2.2  | Analog and digital domain demodulation                                          | 7  |

| 2.3  | Resolution vs. sampling rate for A/D                                            | 9  |

| 2.4  | Power versus sampling rate for an 8-bit A/D converter implemented               |    |

|      | in different architecture                                                       | 10 |

| 2.5  | Sampling mixer a) top sampling b) bottom sampling                               | 12 |

| 2.6  | Equivalent circuit for top sampling mixer                                       | 13 |

| 2.7  | Distortion graph regarding the analytical approach                              | 14 |

| 2.8  | First order architecture                                                        | 16 |

| 2.9  | Model of first order architecture                                               | 17 |

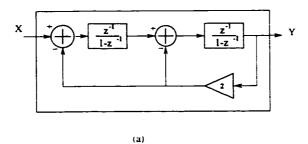

| 2.10 | Modified architecture of second-order modulator                                 | 19 |

| 2.11 | Power spectral density for first and second order sigma-delta modu-             |    |

|      | lators.                                                                         | 19 |

| 2.12 | Range of amplitudes that can be accommodated by multilevel quantizer            | 22 |

| 2.13 | Third order sigma-delta modulator                                               | 23 |

| 2.14 | Block diagram of a $\Delta\Sigma$ modulator including a gain $G$ in the forward |    |

|      | path                                                                            | 24 |

| 2.15 | Illustration of dead zone caused by leakage in the accumulators of                         |            |

|------|--------------------------------------------------------------------------------------------|------------|

|      | second-order $\Delta\Sigma$ quantization. The dc gain of each accumulator is               |            |

|      | 64. and the oversampling ratio is also 64. The range of input and                          |            |

|      | output amplitudes that can be accommodated is $\pm 1V$                                     | 27         |

| 2.16 | Single-ended switched capacitor integrator                                                 | 27         |

| 2.17 | A general noise-shaping bandpass structure                                                 | 42         |

| 2.18 | Linear model for sigma-delta modulator where the noise transfer                            |            |

|      | function and signal transfer function are separated                                        | 43         |

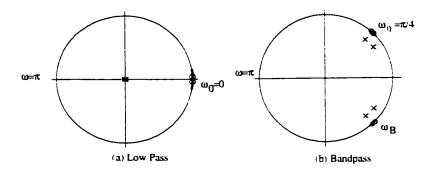

| 2.19 | The pole/zero locations and pass bands of the noise transfer functions                     |            |

|      | for (a) low-pass and (b) band-pass $\Sigma\Delta$ modulation                               | 46         |

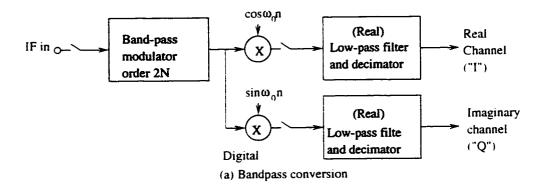

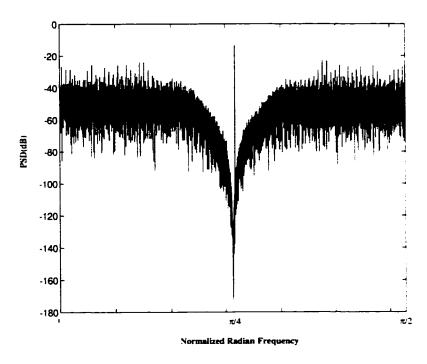

| 2.20 | Comparison of radios using band-pass $\Delta\Sigma$ and a zero IF with low-                |            |

|      | pass $\Delta\Sigma$                                                                        | <b>5</b> 0 |

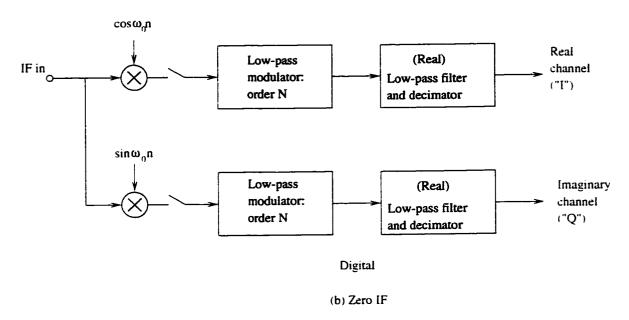

| 2.21 | The spectrum of an example fourth-order modulator                                          | 51         |

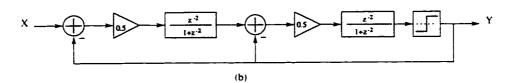

| 2.22 | Realized band-pass architecture. (a) $\frac{z^{-2}}{1+z^{-2}}$ structure (b) the final re- |            |

|      | alization of the fourth order architecture                                                 | 59         |

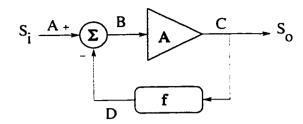

| 3.1  | A non-linear amplifier in the feedback system                                              | 65         |

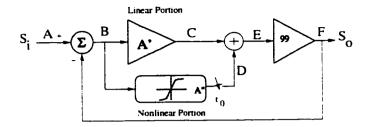

| 3.2  | A non-linear amplifier in which the linear part and nonlinear part                         |            |

|      | are separated in two paths in the feedback system                                          | 67         |

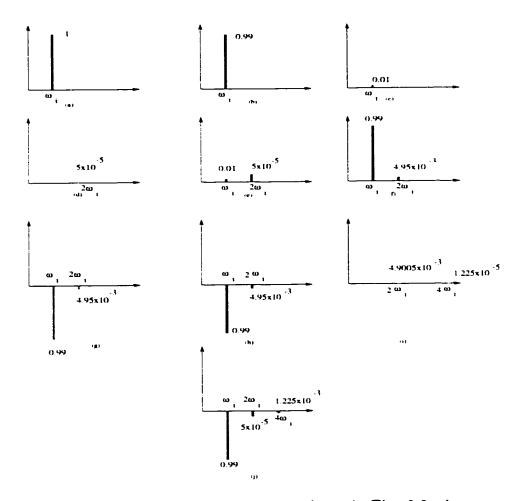

| 3.3 | Frequency spectrum of the system shown in Fig. 3.2. given a mono-              |    |

|-----|--------------------------------------------------------------------------------|----|

|     | tone sinusoidal input. during iteration mode a) the spectrum at node           |    |

|     | A b) the spectrum at node F in the steady state condition c) the               |    |

|     | spectrum at node B in steady-state d) the spectrum at node Dat                 |    |

|     | $t>t_0$ e) the spectrum at node ${f E}$ f) the spectrum at node ${f F}$ g) the |    |

|     | spectrum at node B h) the spectrum at node C i) spectrum at node               |    |

|     | D and j) spectrum at node E                                                    | 69 |

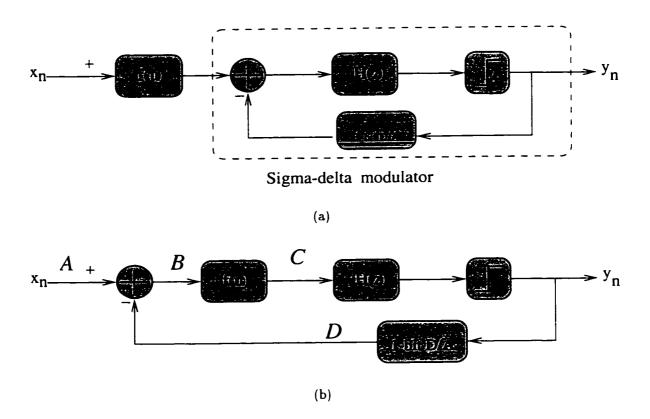

| 3.4 | A sigma-delta modulator with a third order non-linear component                |    |

|     | f(u) a)outside the feedback loop b)inside the feedback loop                    | 71 |

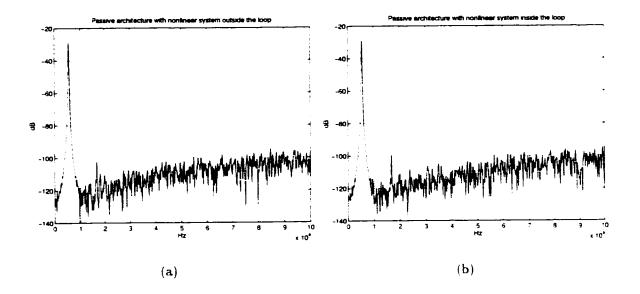

| 3.5 | The frequency response of an original sigma-delta modulator archi-             |    |

|     | tecture with a non-linear component a) outside the feedback loop(              |    |

|     | Fig. 3.4a) b) inside the feedback loop (Fig. 3.4b)                             | 72 |

| 3.6 | A block diagram of a nonlinear component                                       | 72 |

| 3.7 | Input and output of the nonlinear component shown in Fig. 3.6 a)               |    |

|     | Single-bit input b) Three-bits input c) Single-bit output d) Three-            |    |

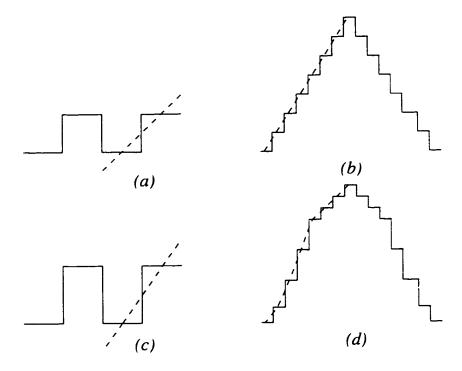

|     | bits output                                                                    | 73 |

| 3.8 | Frequency spectrum of the system shown in Fig. 3.4(b) during it-               |    |

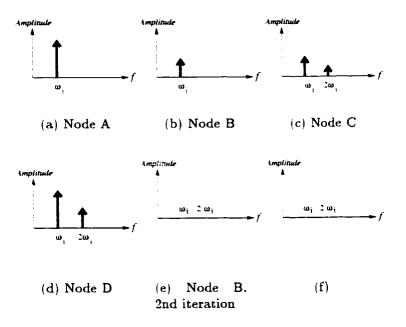

|     | erations mode a) the spectrum at node A b) the spectrum at node                |    |

|     | B in the first iteration c) the spectrum at node C d) the spectrum             |    |

|     | at node D e) the spectrum at node B in the second iteration f) the             |    |

|     | spectrum at node C The black in the positive amplitude is due to               |    |

|     | the input signal. The grey is due to the linear frequency response             |    |

|     | for the feedback signal                                                        | 77 |

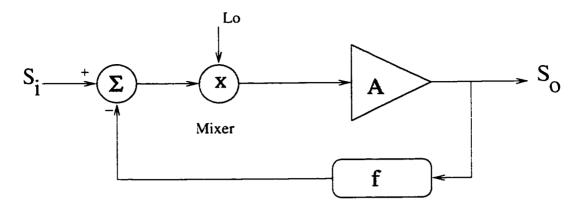

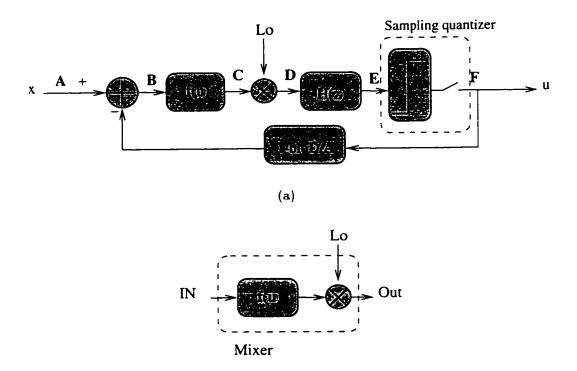

| 3.9  | A classical feedback system with a mixer in the forward path                                | 78 |

|------|---------------------------------------------------------------------------------------------|----|

| 3.10 | A classical feedback system with only a mixer in feedback and for-                          |    |

|      | ward path                                                                                   | 78 |

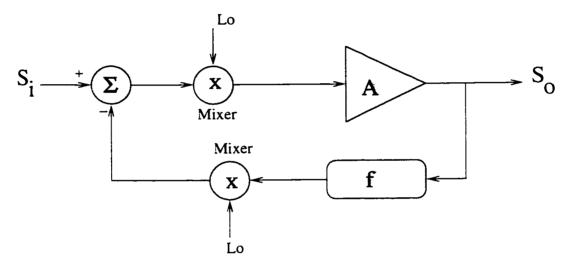

| 3.11 | a)A quantized feedback system with mixer inside the loop b) A model                         |    |

|      | for a nonlinear mixer                                                                       | 79 |

| 3.12 | Frequency spectrum of the system shown in Fig. 3.11(a). a) Input                            |    |

|      | signal at frequency of $\omega_1 + \omega_0$ b) b)node <b>B</b> of Fig. 3.11(a)at $t = 0^+$ |    |

|      | c) frequency spectrum after the nonlinear component d) frequency                            |    |

|      | spectrum after the ideal mixer e) frequency spectrum of the signal                          |    |

|      | at the output of the loop filter f) frequency spectrum of the out-                          |    |

|      | put g) frequency spectrum at the input of the nonlinear component                           |    |

|      | h) frequency spectrum at the output of the nonlinear component                              |    |

|      | i)frequency spectrum at the output of the loop filter                                       | 82 |

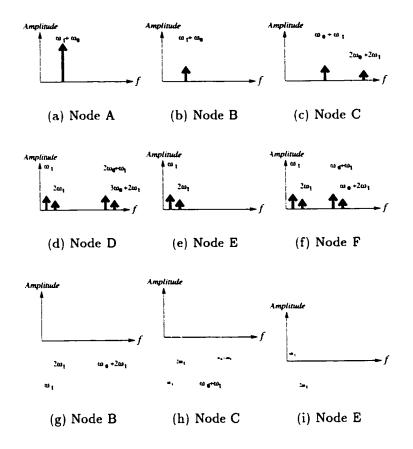

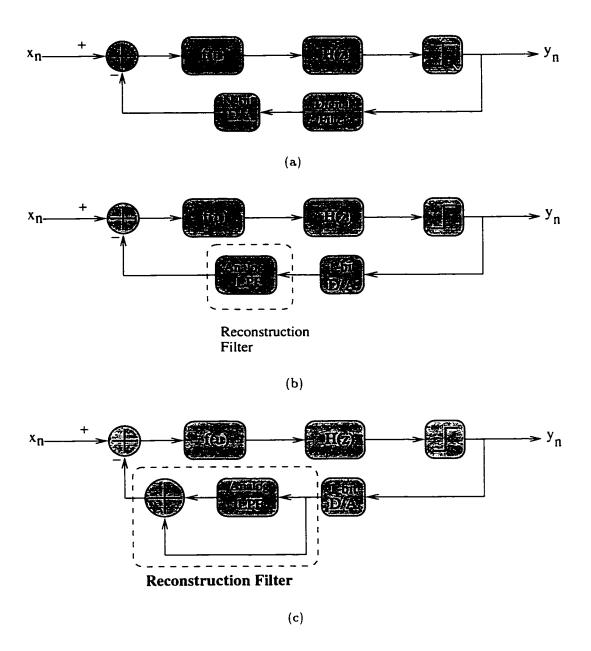

| 3.13 | A new architecture for sigma-delta modulator to reduce the distor-                          |    |

|      | tion a)using Digital filter and multi-bit D/A converter in the feed-                        |    |

|      | back path b) using single-bit D/A converter and analog filter in the                        |    |

|      | feedback path c) stable architecture with the filter in the feedback                        |    |

|      | path                                                                                        | 84 |

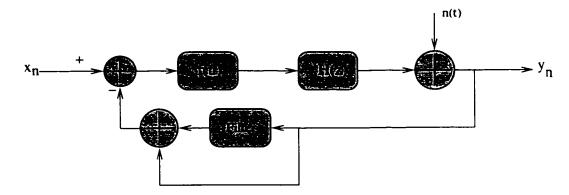

| 3.14 | White noise model of the new architecture                                                   | 85 |

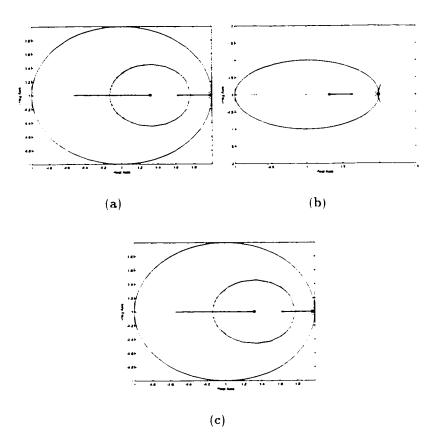

| 3.15 | The stability issue of the architecture a) root locus plot the original                     |    |

|      | architecture without reconstruction filter b) root locus plot of the                        |    |

|      | architecture in Fig. 3.13b c) root locus plot of the architecture in                        |    |

|      | Fig. 3.13c                                                                                  | 86 |

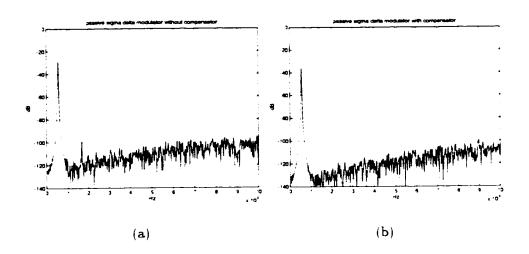

| 3.16 | A comparison between the frequency response of the output of the       |     |

|------|------------------------------------------------------------------------|-----|

|      | a)new architecture and b) conventional architecture                    | 87  |

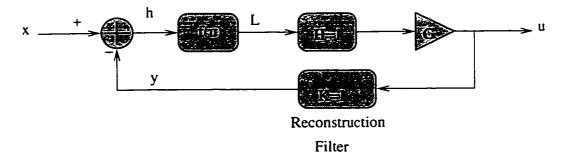

| 3.17 | A model for the new base-band architecture                             | 88  |

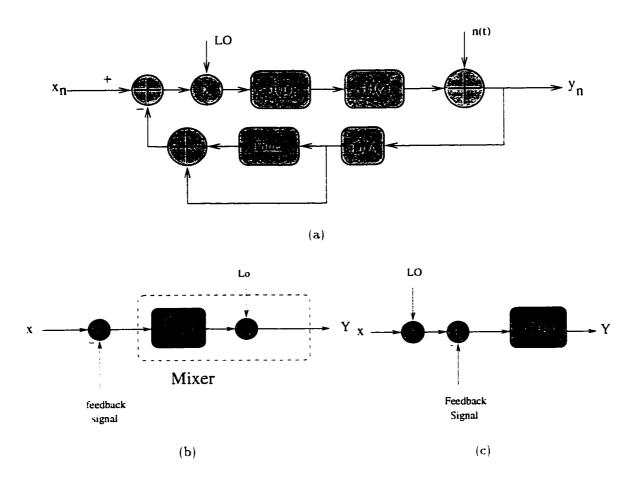

| 3.18 | a) white noise model of the high frequency architecture b) Mixer model |     |

|      | with the feedback c) simplified model of the mixer                     | 91  |

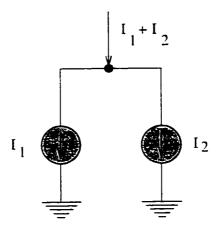

| 4.1  | A simple summing feature in the current domain                         | 95  |

| 4.2  | A Linear Voltage to Current Converter Whose Input Transistor is in     |     |

|      | The Triode Region [1]                                                  | 98  |

| 4.3  | A linear composite MOSFET voltage to current converter                 | 99  |

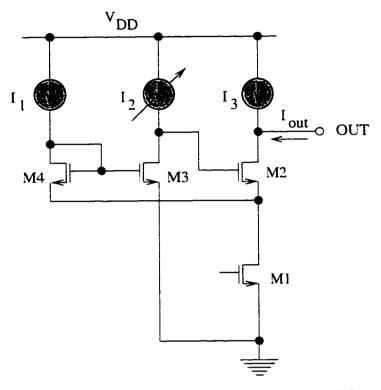

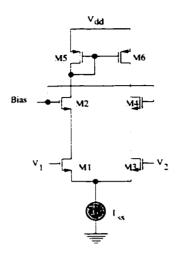

| 4.4  | The designed circuit schematic for Voltage to current converter        | 100 |

| 4.5  | The gain block used for the linear VI converter                        | 101 |

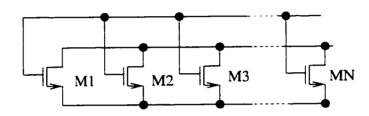

| 4.6  | N parallel transistor                                                  | 102 |

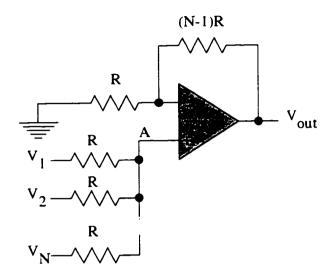

| 4.7  | An analog adder using operational amplifier to sum the signal in       |     |

|      | Voltage domain                                                         | 104 |

| 4.8  | A passive sigma-delta modulator with a linear quantizer model          | 105 |

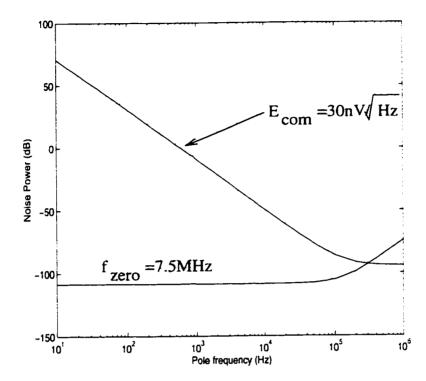

| 4.9  | Baseband quantization noise and comparator input noise versus fre-     |     |

|      | quency(2 identical poles)                                              | 106 |

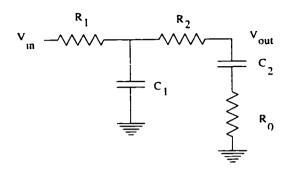

| 4.10 | Continuous time schematic of the loop design                           | 107 |

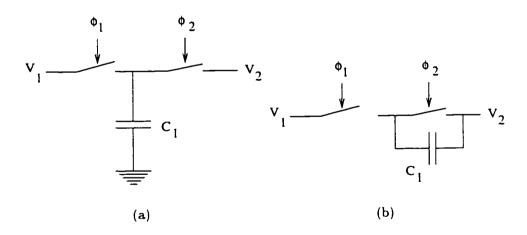

| 4.11 | Resistor realization in switched capacitor circuits a) Shunt b) Series | 107 |

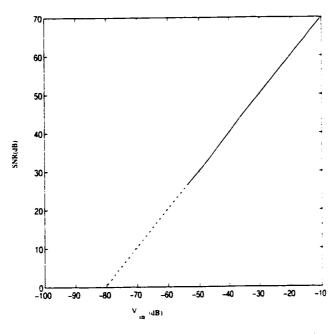

| 4.12 | Dynamic range of the designed system in simulation                     | 108 |

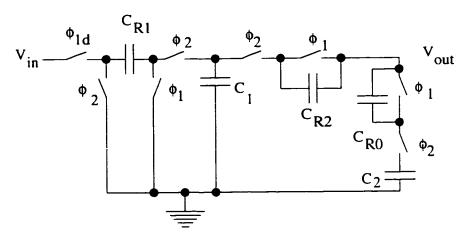

| 4.13 | Schematic of the loop filter                                           | 109 |

| 4.14 | Reconstruction filter with MOS switches                                | 111 |

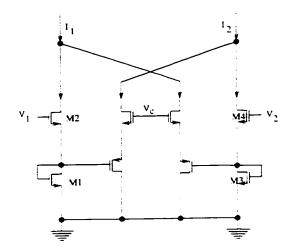

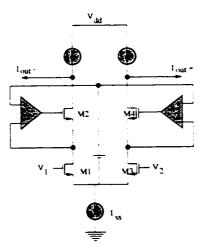

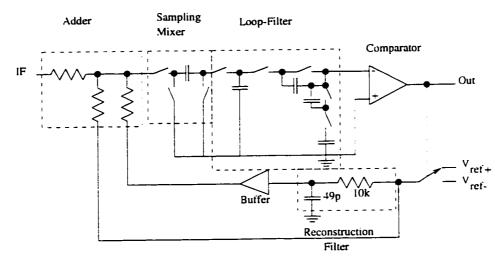

| 4.15 | A single-ended schematic of the proposed architecture                  | 112 |

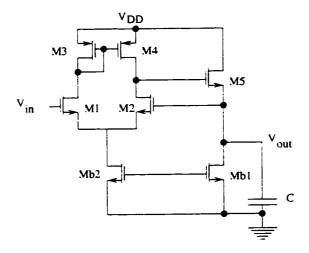

| 4.16 | Linear Unity gain buffer                                          | 113 |

|------|-------------------------------------------------------------------|-----|

| 4.17 | Linear Unity gain buffer with the voltage adder                   | 114 |

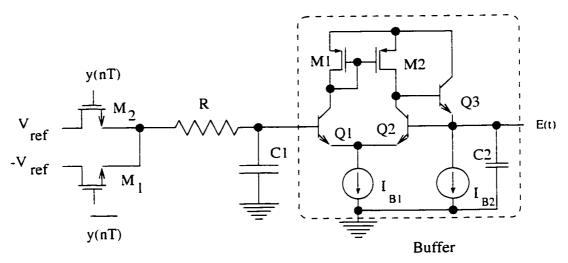

| 4.18 | Schematic of a buffer in the BiCMOS technology                    | 115 |

| 4.19 | Schematic of A low noise CMOS comparator used in IF digitizer     | 116 |

| 4.20 | The timing schedule for the CMOS comparator                       | 117 |

| 4.21 | Pre-amplifier Schematic in BiCMOS Comparator                      | 119 |

| 4.22 | ECL latch in BiCMOS comparator                                    | 120 |

| 5.1  | Micro photograph of the IF digitizer with current adder           | 125 |

| 5.2  | Measurement result of the IF digitizer with 10.01MHz input and    |     |

|      | 10MHz sampling clock a) without the reconstruction filter b) with |     |

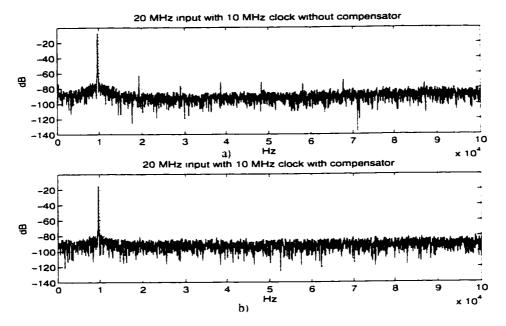

|      | reconstruction filter                                             | 126 |

| 5.3  | Measurement result of the IF digitizer with 20.01MHz input and    |     |

|      | 10MHz sampling clock a) without the reconstruction filter b) with |     |

|      | reconstruction filter                                             | 127 |

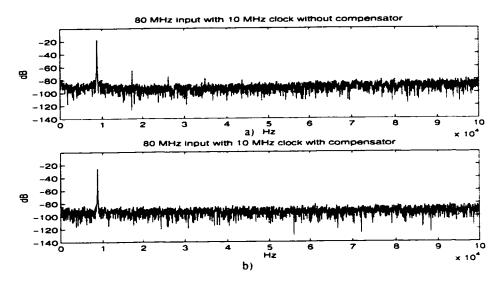

| 5.4  | Measurement result of the IF digitizer with 80.01MHz input and    |     |

|      | 10MHz sampling clock a) without the reconstruction filter b) with |     |

|      | reconstruction filter                                             | 128 |

| 5.5  | Micro photograph of the IF digitizer with voltage adder           | 130 |

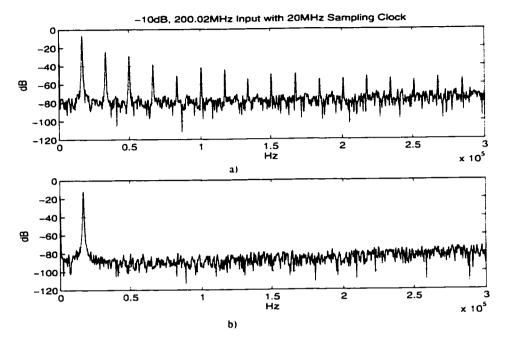

| 5.6  | Measurement results of the IF digitizer with 200.02MHz input and  |     |

|      | 20MHz sampling clock a) without the reconstruction filter b) with |     |

|      | the reconstruction filter                                         | 131 |

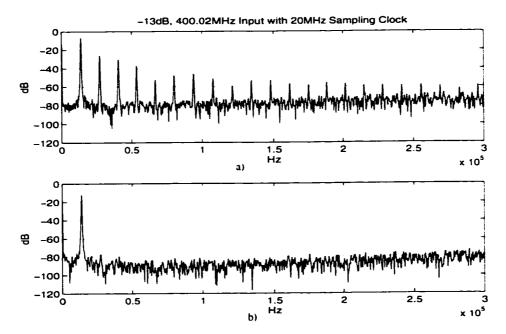

| 5.7 | Measurement results of the IF digitizer with 400.02MHz input and  |     |

|-----|-------------------------------------------------------------------|-----|

|     | 20MHz sampling clock a) without the reconstruction filter b) with |     |

|     | the reconstruction filter                                         | 132 |

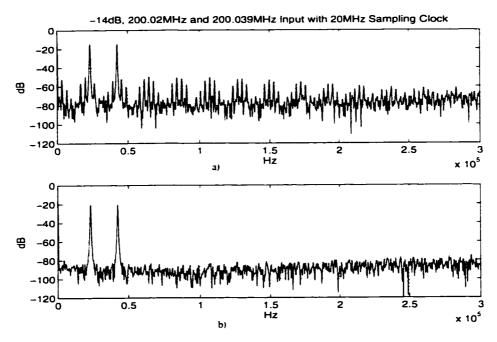

| 5.8 | Measurement results of the IF digitizer for IM3 with 200.02MHz.   |     |

|     | and 200.039MHz input and 20MHz sampling clock a) without the      |     |

|     | reconstruction filter b) with the reconstruction filter           | 133 |

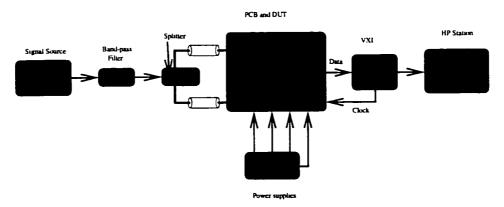

| 5.9 | A test setup for the implemented IF digitizer                     | 133 |

# List of Tables

| 2.1 | comparison between low-pass and band-pass architecture               | 61  |

|-----|----------------------------------------------------------------------|-----|

| 3.1 | The coefficients of the loop filter transfer function                | 87  |

| 4.1 | Parameters of RC passive loop filter and its equivalent switched ca- |     |

|     | pacitor value at $f_S = 100MHz$                                      | 107 |

| 4.2 | The coefficients of the loop filter transfer function                | 108 |

| 4.3 | Transistors size in Buffer                                           | 113 |

| 4.4 | Comparator transistor sizes                                          | 118 |

| 4.5 | Consumed power by each block of the IF digitizer architecture in     |     |

|     | CMOS technology                                                      | 118 |

| 4.6 | The MOS size in BiCMOS preamplifier                                  | 120 |

| 4.7 | power consumed by the designed BiCMOS IF architecture                | 121 |

#### 1

# Chapter 1

# Introduction

A conventional digital radio receiver chain consists of a few band-pass filters with different center frequencies, two or three mixers, a low noise amplifier, a frequency synthesizer and an A/D converter. The recent development of advanced technology for VLSI circuits gives one the opportunity to develop a compact system. However, the external components such as the tank circuits for the LNA, image rejection filters. SAW filters, etc. prevent one from reducing the size of the system considerably.

In order to reduce the size considerably, one should get rid of as many of the external components as possible. The oversampled IF digitizer will reduce the number of external components or relax the required performance of the external components. For example, a band-pass sigma-delta modulator eliminates the quadrature mixers which are required at the input of the A/D converter. This will eliminate the mismatch of the two paths. However, the image rejection filter is still required because the IF input is still at low-frequencies (10MHz). Increasing the IF fre-

2

quency has two advantages: It relaxes the performance of the image rejection filter and eliminates one of the IF stages.

There are many standards, such as DECT. WCPE, PCS1900, GSM, etc. Some of these standards, such as PCS1900 and GSM, have the same specifications in terms of bandwidth, the modulation scheme, data rate per channel, etc. One of the main differences between them is the carrier frequency. Switching between the two standards in the current approach is not easy because of the presence of two carrier frequencies. The system requires either a frequency synthesizer whose function is to sweep both carriers with the same performance or using two different frequency synthesizers. Usually the latter technique is used to have a multi standard system. To make the system compact and simple motivates us to pursue the idea that developing a high IF digitizer the two carriers can be converted to one IF using only one local frequency. Therefore this relaxes the frequency synthesizer requirements. In addition at high IF frequency the image signal frequency is larger than one decade in the frequency domain. This will also reduce the requirements of the filter.

## 1.1 Research Objectives

The aim of this research is to develop an IF digitizer whose input frequency can be increased as high as 300-400MHz for GSM or PCS1900 application. The main goal is to develop a technique that can digitize the information with minimum distortion. Since this project is intended for wireless applications, being a low power architecture is another goal of this project. Our goal is to reduce the distortion to

12-bit level with only 25 milliwatts of power dissipation.

### 1.2 Thesis Organization

In chapter 2, two types of oversampled A/D converters are investigated. In this chapter different architectures of sigma-delta modulators are highlighted. A design procedure for two general architectures, that is, a band-pass sigma-delta modulator and a low-pass sigma-delta modulator, are mentioned and a design example for each architecture has been mentioned. At the end, the two architectures are compared.

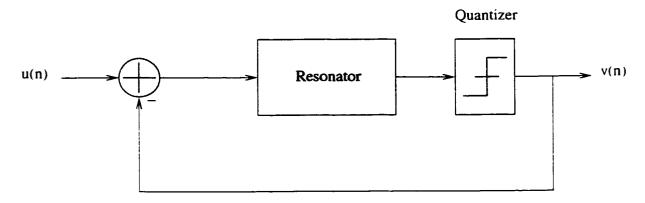

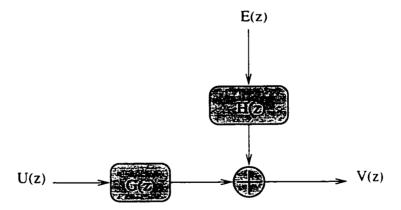

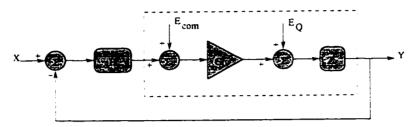

In chapter 3, quantized feedback is discussed and a new architecture is proposed to reduce the sampling mixer distortion. Simulation results from MATLAB and the advantages of this architecture are discussed.

In chapter 4, the IF digitizer design will be highlighted. Each block in the new architecture will be examined in terms of the circuit performance.

In chapter 5, the issues concerning IC implementation will be discussed and experimental results along with the testing guidelines will be presented.

Concluding remarks and comments on further investigation of this approach are made in chapter 6.

#### 4

# Chapter 2

# IF Digitizer Architectures

# 2.1 A/D converters in wireless and digital communication

In wireless applications, A/D converters are used in the demodulation scheme. After the RF signal is mixed down to IF, it is further demodulated from IF signal to baseband signal. In digital communication systems, the carrier signal is still analog. The message which is carried on the carrier is digital information. After demodulation, the digital information is restored and processed to get the information contained in the digital signals.

### 2.1.1 Analog and digital domain demodulation

Traditionally in a receiver chain, upon mixing the input signal from RF frequency to IF frequency, subsequent processing can be performed in one of two ways. One is the

conventional way of performing demodulation directly at IF. Traditionally one can do a FM to AM translation (by differentiation) followed by an AM demodulation. Recently, with the advent of high speed ADCs, one can digitize the signal and perform all the demodulation digitally. This has the advantage of having to build only one IF strip and demodulate different modulation schemes (from different standards) using the same strip. An IF digitizer normally consists of an IF mixer (which operates at lower frequency than the RF mixer) that mixes the incoming IF signal to baseband as well as a baseband ADC that digitizes the subsequent baseband signal. In the case of a bandpass sigma-delta modulator, the digitizing is done directly in IF and a separate analog mixer is not needed. An alternative architecture includes a hybrid solution: e.g. one architecture discussed in this thesis includes a mixer which mixes the IF signal down to baseband, performs a coarse digitization, reconverts the coarse signal back to an analog form, mixes the analog signal back up to IF frequency, and subtracts this feedback signal from the incoming IF frequency. In this case the mixing and sampling functions are distinct from one another.

The different ways of implementing demodulators are now discussed in more detail. One is analog demodulation. It can be illustrated in Fig.2.1.

Figure 2.1: Phase-shift discriminator of quadrature detector.

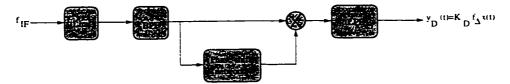

Fig. 2.1 represents a phase-shift discriminator built with a network having

group delay  $t_1$  and carrier delay  $t_0$  such that  $\omega_c t_0 = 90^\circ$ - which accounts for the name quadrature detector. The phase-shifted signal is proportional to  $\cos[\omega_c t - 90^\circ + \phi(t - t_1)] = \sin[\omega_c t + \phi(t - t_1)]$ . Multiplication by  $\cos[\omega_c t + \phi(t)]$  followed by lowpass filtering yields an output proportional to

$$\sin[\phi(t) - \phi(t - t_1)] \approx \phi(t) - \phi(t - t_1)$$

assuming  $t_1$  is small enough that  $|\phi(t) - \phi(t - t_1)| \ll \pi$ . Therefore,

$$y_D(t) \approx K_D f_\Delta x(t)$$

where the detection constant  $K_D$  includes  $t_1$ . Despite these approximations, a quadrature detector provides better linearity than a balanced discriminator and is often found in high-quality receivers. The IF receiver LMX2240, made by National Semiconductor, is one of the commercial realizations using this approach. This chip consists of a hard limiter at the input with an input impedance of 150 ohms and having a -80 dB sensitivity for the IF signal. A Gilbert-quad mixer is used for the discriminiator in this architecture. To get the quadrature signal an external tank circuit is required whose bandwidth is approximately 1% of the IF frequency and a steep phase response is required. As a result the above approach suffers from

- a) Need to have external capacitors and inductors for its tank circuit.

- b) Need to have a narrowband analog filter.

To circumvent the above mentioned problems, the approaches shown in Fig. 2.2 can be used.

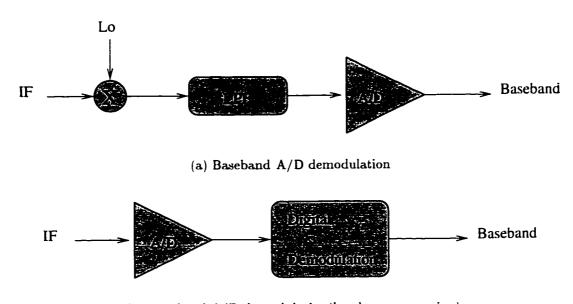

(b) Pass band A/D demodulation(bandpass conversion)

Figure 2.2: Analog and digital domain demodulation

In Fig. 2.2a, the incoming IF signal is multiplied by the LO signal which is of the same frequency and phase as the carrier signal. After the multiplication, a low pass filter is used to eliminate the frequency component at  $(\omega 1 + \omega 2)$ . Only the baseband signal is left upon low-pass filtering. A baseband analog-to-digital (A/D) converter is then used to convert the analog signal to its digital form and the baseband digital circuits will perform the demodulation. This approach is given the name "baseband demodulation". An alternative denoted as bandpass demodulation is shown in Fig. 2.2b. This has become possible only after high speed, high accuracy A/D converters became available recently. The IF signal is fed directly into the A/D converter. The A/D digitizes the IF signal directly into its digital form. Then the demodulation is done entirely in the digital domain in the passband.

There are two terms which can easily raise confusion here: digital demodulation and digital domain demodulation. Digital demodulation is named after those methods like PSK. FSK because in these demodulators, the information is in the digital domain, while the demodulation can be done in the analog domain. Digital domain demodulation means the signal representation in the demodulator is in digital form and the information is also in digital form.

Why did digital domain demodulation come into being? This is mainly because of the more and more powerful digital signal processing techniques. The speed and function of DSP has developed quickly and now it is easy for DSP to handle signals with frequency in the order of several hundred MHz. Also digital processing. like filtering, multiplication, is less prone to error than their analog counterparts. The major challenge is that there is an accurate and fast enough A/D converter to convert the IF signal into its digital form. Consequently the design of a high accuracy, high speed A/D converter is a key issue in digital radio.

### 2.1.2 IF digitization

In digital radio applications [2], the IF signal typically has a center frequency of 10-100 MHz, with bandwidth varying from a few kHz to more than 1 MHz. The A/D converter used in this application needs to handle signals at these frequencies and with these bandwidths, while maintaining of resolution around 70 dB. First, let us take a look at the different A/D converter architectures to see which one is promising for IF digitization.

There are two general ways of doing data conversion at IF: wideband and nar-

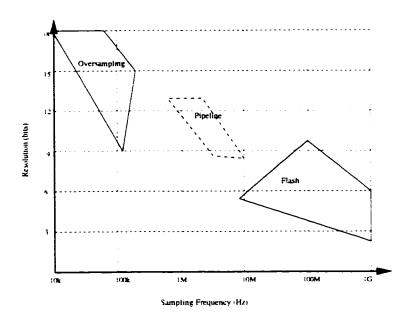

rowband conversion. Oversampling A/D converters such as sigma-delta converters fall in the narrowband category. Wideband converters will include architectures such as pipelined and flash converters. Fig.2.3 summarizes the speed and resolution of different A/D converters.

Figure 2.3: Resolution vs. sampling rate for A/D

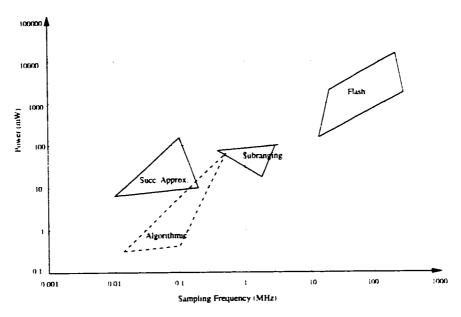

In wireless communication, there is also a stringent power requirement for A/D converters. Fig.2.4 is the comparison of power consumption in various A/D converters.

In Fig.2.3, we can see that flash A/D converters have the highest speed but the lowest resolution. The oversampling A/D converters have the highest resolution but the lowest sampling rate. Between them are pipelined A/D converters which offer a trade-off between speed and resolution. As shown in Fig.2.4, the flash A/D converters have the highest power consumption. Because there are very few

Figure 2.4: Power versus sampling rate for an 8-bit A/D converter implemented in different architecture

oversampling and pipelined A/D converters operating at an 8-bit resolution, they are not presented in this figure. In general oversampling A/D converters have the same order of power consumption as the algorithmic ones and pipelined A/D converters have similar power consumption as subranging A/D converters.

Typically for wide signal bandwidth (such as DECT. CDMA. or wireless video) applications. Nyquist rate ADCs are used. On the other hand, for narrow signal bandwidth applications (such as AMPS. GSM) oversampled architectures will be used. As mentioned above since the power is one of the most important issues in wireless applications, so architectures which dissipate high power are avoided. With this in mind three types of architectures are usually used. For wide signal bandwidth applications pipelined architecture is selected, because its power dissipation is the lowest among high speed Nyquist rate A/D converters (e.g. Flash

type A/D converters and subranging type A/D converters). Note interpolative and folding A/D converters are becoming a big contender in this area. For narrow signal bandwidth applications, two types of sigma-delta modulators are considered: low-pass architecture and band-pass architecture. In this chapter, the important parameters which have to be selected for each architecture in narrow signal bandwidth architectures is explained and a design procedure will be presented to obtain the required parameters for designing an A/D converter for IF applications.

# 2.2 Sample/Hold Circuit and Sampling Mixer

Even though band-pass sigma-delta modulators do not explicitly need a mixer (its mixer and S/H circuit is merged), it still needs a S/H circuit. As a side note, the other architectures (pipelined, low-pass sigma-delta modulator) can also use a sampling type mixer and then merge it with its sample and hold circuit. Of course they can also have a continuous time mixer in front (like a Gilbert mixer). This section will discuss the S/H circuits and briefly exhibits its difference from the sampling mixer. (Note the S/H circuit is very different from other types of mixer).

Nyquist rate A/D converters and the oversampled architecture both require sample and hold circuits. The location of the S/H depends on the type of architecture employed. If the architecture processes signals in the continuous time domain. the S/H is used at the input to the comparator, whereas, if the signal is processed in discrete time we need a S/H at the input.

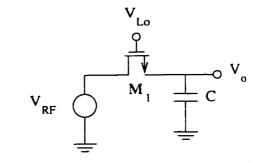

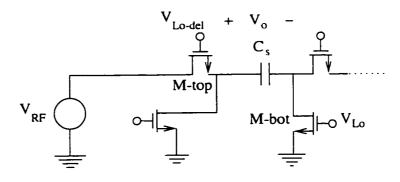

In IF digitizers, since the sampling clock frequency is equal to or less than that of the input frequency, the sample and hold is used as the sampling mixer. There are two types of sampling mixers which are shown in Fig. 2.5. Both of these structures create distortion at the output and degrade the signal quality.

(a) top plate sampling

(b) bottom plate sampling

Figure 2.5: Sampling mixer a) top sampling b) bottom sampling

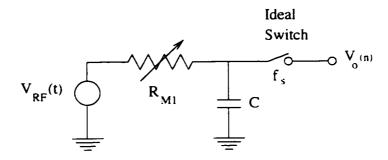

The distortion of this type of mixer has been characterized in [3.4]. Three types of distortion are defined for this type of mixer. The first type is the time invariant distortion, produced by circuit characteristics of the mixer switch. An NMOS transistor can be characterized as a nonlinear resistor when the gate is connected to high voltage. The equivalent circuit for a top sampling mixer is shown in Fig. 2.6. It can easily be shown that the time invariant distortion linearly depends on the frequency as well as the sampling capacitor and is inversely proportional to the size of the switch [3,4].

Figure 2.6: Equivalent circuit for top sampling mixer

The second type of distortion is called non uniform distortion. This type of distortion is due to the fall time of the clock edge and the input voltage. Analytical solution shows that the distortion depends on the input frequency and the clock edge fall time in a quadratic fashion.

The third type of distortion is due to the change of the device characteristic during the fall time of the sampling clock. The device characteristic changes with time so the time varying characteristic creates distortion. In general, calculating this type of distortion is difficult. But in this case the sampling time is important and the distortion is dependent only on the value of the sample instant. Analytical results show that the distortion depends on the cube of the input frequency [5].

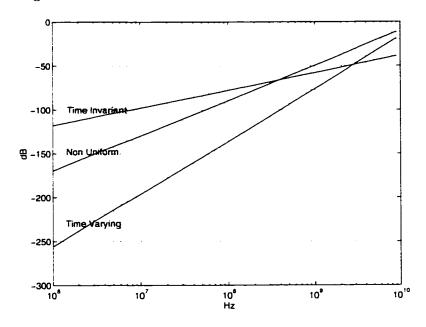

The above discussion shows that the sampling mixer distortion changes with input frequency. At low frequency the time invariant distortion dominates. However, at high frequency the other two types dominate. Fig. 2.7 shows a comparison of analytical results of the three type distortion and gives a quick estimation of the dominant distortion sources at different frequencies. It shows that at high enough frequencies the time varying distortion, which increases as the cube of input frequency, dominates. It also gives the motivation that a new architecture, like the

one discussed in this thesis, is needed to achieve acceptable levels of distortion as the IF moves higher.

Figure 2.7: Distortion graph regarding the analytical approach

### 2.3 Low-pass sigma-delta modulator

In this section, a review of the low-pass sigma-delta modulator is presented. This type of A/D converter has been used by industries and researchers because they have fewer problems than the conventional architecture used for A/D converters and D/A converters. This type of architecture is usually used for high resolution requirements and narrowband signals. In IF digitizers, the input frequency is large, but the band of interest compared to the sampling clock frequency is narrow. So this type of architecture can be used to digitize the information directly at IF. Different types of low-pass sigma-delta modulator architectures will be discussed in

this section. Then non idealities that produce degradation of the performance of each architecture will be explained. At the end of this section, a design guide with an example will be explained.

#### 2.3.1 Hardware architectures

Sigma-delta modulators can be categorized into different categories depending on the number of output bits, the number of stages, or the number of loops. These architectures are denoted as: first order, second order, higher order, multi stage, and interpolative architectures. Any of these architectures can be one-bit or multibit or both. Each of these categories will be explained below.

#### 2.3.1.1 Single stage architectures

Single stage architectures consist of only one quantizer. The noise shaping is done by a single or multi-loop consisting of one or more integrators as loop filter in the loop. One of the important issues in sigma-delta is the quantization noise. In the following sections in each architecture the quantization noise will be discussed and an estimation of SNR will be given.

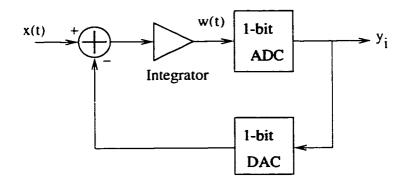

2.3.1.1.1 First order architecture A first order architecture is shown in Fig. 2.8. This architecture consists of an integrator and a quantizer. Since the integrator has infinite gain at DC, the loop gain is infinite at DC and therefore the DC component or the average of the output from the feedback D/A converter will be identical to the DC component of the input signal. This means that even though the quantization error at every sample is large because of the use of two level quantizer.

the average of the quantized signal, and therefore the modulator output  $y_k$ , tracks the analog signal x(t). This average is computed by a decimation filter that follows the modulator.

Figure 2.8: First order architecture

In general, the amplitude resolution of the modulator increases when more samples are included in the averaging process, or as the oversampling ratio (OSR) increases. However, the bandwidth is decreased at the same time when the sampling frequency is kept constant. Consequently, the resolution of the modulator is a function of the ratio of the sampling rate to the bandwidth of the modulator. The principle of operation of sigma-delta modulators relies on this fundamental trade-off between resolution and time.

Compared to the Nyquist rate A/D converters, the quantization error is a differential error. In the other words, the modulator tries to cancel the error by subtracting quantization error from two adjacent samples. This principle of reducing the error source by exploiting the statistics between them can be extended to higher order modulators, where more past error samples are involved in the cancelation process to reduce the overall error. Viewed from the frequency domain this

difference operation acts to attenuate the quantization noise at low frequencies. thus shaping the noise. The first order modulator can be proved to be inherently stable, provided that the input is within  $[V_r, -V_r]$ , where  $V_r$  is the output of the feedback D/A converter, or the reference voltage.

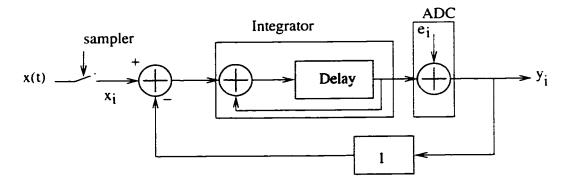

Figure 2.9: Model of first order architecture

Quantization noise in this architecture depends on the input signal. For busy signals the quantization noise is like white noise whereas for dc input the quantization noise is colored. To calculate the effective resolution of the  $\Delta\Sigma$  modulator. it is assumed that the input signal is sufficiently busy that the error e behaves like a white noise which is uncorrelated with the input signal. The modulation noise is expressed as:

$$n_i = e_i - e_{i-1} \tag{2.1}$$

and the spectral density may be expressed as:

$$N(f) = E(f)(1 - e^{(-j\omega T)})$$

(2.2)

The noise power density is described as:

$$|N(f)| = 2e_{rms}\sqrt{2T}\sin\left(\frac{\omega T}{2}\right) \tag{2.3}$$

where  $\omega = 2\pi f$ .

Clearly, feedback around the quantizer reduces the noise at low frequencies but increases it at high frequencies. The total noise power in the signal band is

$$n_0^2 = \int_0^{f_0} |N(f)|^2 df \approx e_{rms}^2 \frac{\pi^2}{3} (2f_0 T)^3 \qquad f_s^2 \gg f_0^2$$

(2.4)

where  $2f_0T$  is defined as the inverse of the OSR, so its rms value is approximately  $e_{rms} \frac{\pi}{\sqrt{3}} (OSR)^{-3/2}$ . Each doubling of the OSR of this circuit reduces the noise by 9 dB and provides 1.5 bits of extra resolution. The improvement in the resolution requires that the modulated signal be decimated to the Nyquist rate with a sharply selective digital filter. Otherwise, the high-frequency components of the noise will spoil the resolution when it is sampled at the Nyquist rate.

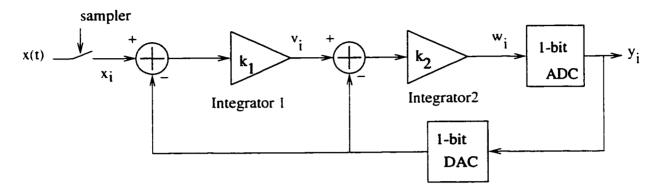

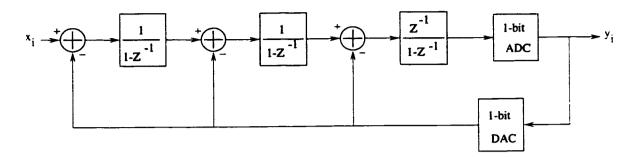

2.3.1.1.2 Higher-order architecture The procedure for increasing the resolution with feedback can be reiterated by replacing the internal quantizer of a first-order modulator as shown in Fig. 2.10 by an identical first order modulator. The resulting circuit is shown in Fig.2.10 [6]. As before the integrators may or may not contain delays. Usually one does and the other does not. The gains  $k_1$ .  $k_2$  are used to optimize the output signal range of the integrators. Modulators with a second-order transfer function involve the cancellation of the two past samples and thus exhibit stronger attenuation at low frequencies. The noise shaping function of

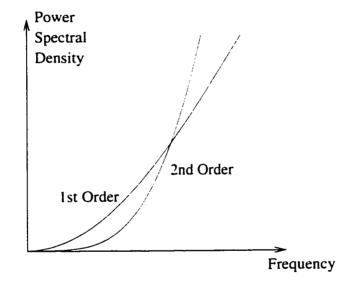

a first and second-order modulator are compared in Fig. 2.11 [7]

Figure 2.10: Modified architecture of second-order modulator

Figure 2.11: Power spectral density for first and second order sigma-delta modulators.

A second-order modulator can be shown to be conditionally stable. The stability depends on total delay in feedback loop, signal amplitude and coefficients  $k_1$ ,  $k_2$ . To avoid saturation, the maximum signal levels at the amplifier outputs should be adjusted by scaling.

The above analysis can be formalized to yield quantitative results for the resolution of sigma-delta modulators, provided that the spectral distribution of the quantization error  $e_i$  can be assumed to be uncorrelated [8]. The modulator can be regarded as linear system for which the power spectral density of the noise can be calculated [9].

For a busy signal the system is assumed linear. So the output of the modulator can be expressed as

$$y_i = x_{i-1} + (e_i - 2e_{i-1} + e_{i-2})$$

(2.5)

so that the modulation noise is now the second difference of the quantization error.

The spectral density of this noise is

$$N(f) = E(f) (1 - \exp(-j\omega T))^{2}$$

(2.6)

For busy signals

$$|N(f)| = 4e_{rms}\sqrt{2T}\sin^2\left(\frac{\omega T}{2}\right) \tag{2.7}$$

and the rms noise in the signal band is given by

$$n_0 \approx e_{rms} \frac{\pi^2}{\sqrt{5}} (2f_0 T)^{5/2} = e_{rms} \frac{\pi^2}{\sqrt{5}} OSR^{-5/2} \qquad f_s^2 \gg f_0^2$$

(2.8)

This noise falls by 15 dB for every doubling of the sampling frequency. providing extra bits of resolution [7.10].

In general, the dynamic range (DR) of an ADC is defined as the ratio of the output power for a full scale sinusoidal input to the output signal power for a small input whose SNR is unity (0 dB). Extending the above analysis to the second-order sigma-delta modulator yields the following formula for DR [11]

$$DR = \frac{3}{2} \frac{5}{\pi^4} (OSR)^5 \tag{2.9}$$

The white noise technique can be extended to provide higher order predictions by adding more feedback loops to the circuit [7]. In general, when a modulator has L loops and is not overloaded, it can be shown that the spectral density of the modulation noise is

$$|N_L(f)| = e_{rms} \sqrt{2T} \left[ 2 \sin\left(\frac{\omega T}{2}\right) \right]^L \tag{2.10}$$

For oversampling ratios greater than 2, the rms noise in the signal band is given approximately by

$$n_0 = e_{rms} \frac{\pi^L}{\sqrt{2L+1}} (2f_0 T)^{L+1/2} \tag{2.11}$$

This noise falls 3(2L+1) dB for every doubling of the sampling rate, providing  $(L+\frac{1}{2})$  extra bits of resolution, but we shall see that there are difficulties in implementing circuits containing more than two integrators.

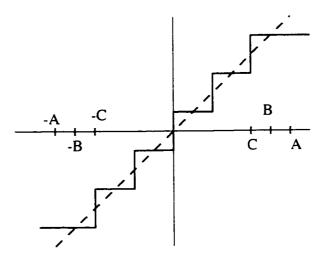

The oscillation of the signal uses up some of the dynamic range of the circuit. and for a non overloaded quantizer the input amplitude to the modulator needs to be limited. Fig. 2.12 shows the range of inputs that can be accommodated in several modulators, each employing six-level quantization. Ordinary PCM requires that its input be restricted to  $\pm A$  in order that the quantization error lie in the range  $\pm \Delta/2$ , where  $\Delta$  is the output bin. Inputs to a corresponding first-order  $\Delta\Sigma$  modulator

need be restricted to  $\pm B$  for them to be interpolated by oscillation between two levels. Inputs to a second-order modulator need be restricted to  $\pm C$  to prevent frequent overloading of its quantizer. This permits the output to oscillate between three levels, but overload can occur occasionally when the oscillation attempts to step outside this three-level range.

Figure 2.12: Range of amplitudes that can be accommodated by multilevel quantizer

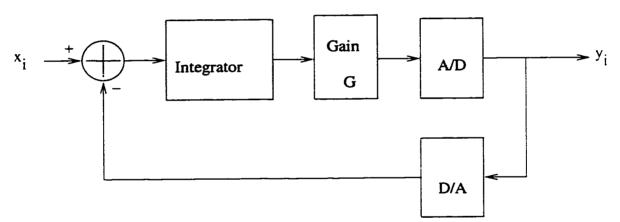

Simple linear theory predicts that the third-order modulator shown in Fig.2.13 has an rms noise given by Eq. (2.11) with L=3. This can be realized in practice with a multilevel quantizer that does not overload [7]: but the circuit is much more sensitive to circuit values than the first and second-order ones. For example, the equivalent linear circuit of this modulator becomes unstable with quantizer gains G in excess of 1.15 compared with 2.0 and 1.33 for first and second-order modulators.

More seriously, the third-order circuit is also unstable when its quantizer gain falls below 0.3. When the quantizer saturates, its effective gain falls, and this usually results in instability in which the circuit settles into a large-amplitude low-frequency

Figure 2.13: Third order sigma-delta modulator

limit cycle. In this state the clipped signals fed back via the two inner feedback paths are small compared with the signal emerging from the integrators. Properties of the outer loop dominate: it contains three integrators and a delay, a strong basis for instability. Unembellished, two-level, third-order  $\Delta\Sigma$  modulators cannot escape from this condition. Their circuits can be made stable by clipping the outputs of the integrators or including other nonlinearities that make the inner feedback effective when the quantizer saturates. The noise performance of these modified modulators is considerably worse than Eq.(2.10) predicts. Better performance is obtained by redesigning the filter used in the feedback loop.

The above summarizes the basics of sigma-delta modulators. Below is a list of other alternative architectures:

- Interpolative architecture [12]

- MASH architecture [13]

- Local feedback loop [14.15]

- Passive Structure [16.17]

Next we discuss the implementation issues.

# 2.3.2 Design issues of low-pass sigma-delta Modulator

In real life implementations there are non idealities (such as finite operational amplifier gain, operational amplifier settling time, clock jitter) which appear in the chips and which affect the chip performance. In this section, non ideal issues and their effects will be highlighted.

### 2.3.2.1 Extra gain in Feed forward path

Our discussion has so far assumed unity gain in every component of the modulator.

Fig. 2.14 shows a modulator that includes a constant gain G in the forward path.

Figure 2.14: Block diagram of a  $\Delta\Sigma$  modulator including a gain G in the forward path

In a first order modulator small deviations of this from unity have little effect on the overall properties, provided the net gain in the feedback loop is large. In higher order modulators the extra gain may create instability. The gain of the accumulator is

$$H(f) = \frac{z^{-1}}{1 - z^{-1}} \approx (j\omega T)^{-1} = [j\pi(2fT)]^{-1} \qquad fT \ll 1$$

(2.12)

where  $z = \exp(j\omega T)$ . In the signal band this gain has a modulus greater than one quarter of the OSR.. which is usually sufficiently large. Measurements on real modulators and simulation [7,18,19] have demonstrated that with small gains (i.e. G < 0.7), the circuit responds sluggishly to changing inputs. With gains greater than 1.3, the quantized signal bounces by more than two levels and eventually goes unstable when the gain exceeds 2, as can be predicted from the linearized model of Fig. 2.8. For most applications 10% gain accuracy is tolerable for this circuit. For higher orders the condition for instability changes. For example, for the second order modulator the maximum gain is 1.3 and for third order this gain reduces to 1.15.

### 2.3.2.2 Non ideal integrator

In switched-capacitor circuits, an integrator consists of an opamp, two capacitors and some switches. The integrating function is affected by operational amplifier dc gain, bandwidth, settling time and the switch non idealities. In this section, these issues will be addressed.

2.3.2.2.1 Leakage in the integrators First-order modulators need integrators with dc gain  $H_0$  that is greater than the OSR, in order to have low noise. Calculations of noise in second-order modulators indicate that somewhat lower gains

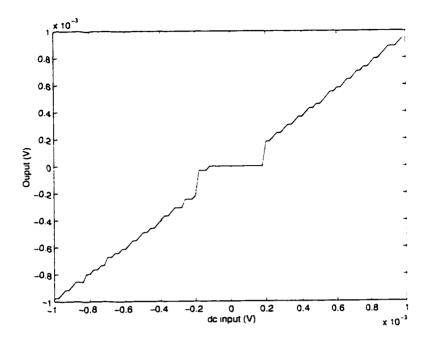

could be tolerated because the gains of two integrator amplifiers are cascaded in the outer loop. But there is another consideration: leakage can permit the oscillation of the quantized signal to settle into regular patterns when there is insufficient long-term memory to randomize it. This is most noticeable at the center of the range where the output can settle into a +1, -1, +1, -1 pattern. The effect is illustrated by Fig. 2.15, which shows the filtered output of a modulator responding to a very slowly changing ramp. The full range of the output signal is  $\pm 1$ V. At the center of the range the output locks into the pattern and the input is ignored in the range  $\pm 0.2$ mV. It may be shown that the width of the dead zone is given approximately by  $1.5\Delta H_0^{-2}$ , and for this to be less than twice the rms noise requires that the dc gain of each integrator satisfy

$$H_0 \ge (2f_0T)^{-5/4} \tag{2.13}$$

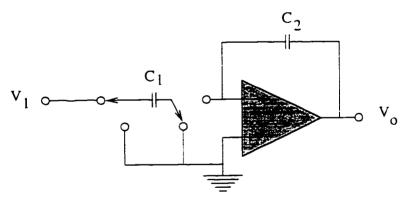

The dead zone is seldom noticeable because it is present only in very slowly changing signals: It takes time for the oscillations to settle into a pattern. For a single-ended configuration of an integrator in a switched-capacitor circuit, the integrator transfer function with finite operational amplifier gain can be expressed as (Fig. 2.16)

$$H(z) = \frac{(C_1/C_2)z^{-1/2}(1 - 1/A - C_1/(AC_2))}{1 - (1 - C_1/(AC_2))z^{-1}}$$

(2.14)

2.3.2.2.2 Integrator settling time Incomplete settling of the integrator outputs due to the finite bandwidth of operational amplifiers translates into an equivalent gain error as long as the settling process is linear. As an example, consider an

Figure 2.15: Illustration of dead zone caused by leakage in the accumulators of second-order  $\Delta\Sigma$  quantization. The dc gain of each accumulator is 64. and the oversampling ratio is also 64. The range of input and output amplitudes that can be accommodated is  $\pm 1 \text{V}$ .

Figure 2.16: Single-ended switched capacitor integrator

integrator whose transient response during each sampling period is characterized

by a single-pole exponential:

$$\Delta V_{\text{out}} = V_{\text{in}} (1 - e^{-T/\tau}) \tag{2.15}$$

where T is the sampling period and  $\tau$  is the settling time constant. For a constant sampling period, the term in parentheses represents a constant reduction in the gain of the integrator. A settling time as short as  $\frac{T}{4}$  reduces the equivalent gain of the integrator by less than 2%. Slew rate limiting in the response of the integrator causes a departure from the linear settling characterized by Eq.(2.15) and must be avoided.

The maximum speed at which the integrator can be clocked is of particular interest in the design of  $\Delta\Sigma$  modulators, because of their oversampled nature and because of the dramatic reduction of in-band quantization noise achieved with increased OSRs. Switched-capacitor circuits operate on the assumption that the complete settling occurs during each time slot. Therefore, unless the signal is used as a continuous-time signal, the manner in which the circuit settles is unimportant. Since the output of an A/D converter is digital, the only place the continuous-time properties of the signal are important is at the sampler input. The only time the value of the voltages at the integrator outputs matters is at the end of each time slot.

The circuit has to settle completely in one time slot. In a two phase clocking scheme, the length of a time slot is equal to one-half of a clock period minus the delays put in for nonoverlap and charge injection reduction purposes. There are basically two factors that determine the settling time of the integrator: the

RC time constants of the MOSFET switches in series with the switched capacitors and the response time of the operational amplifier. The response time of the operational amplifier is determined by the slew rate. the unity-gain bandwidth. and configuration in which it is placed. A very important distinction needs to be made between settling that is signal independent (linear settling) and settling that is signal dependent (nonlinear settling). Nonlinear settling may be due to operational-amp slewing, or the fact that the characteristics of the MOSFET devices will be operating-point dependent. If the integrator does not settle fully but the settling process is linear, then the resultant error shows up as a gain error in the integrator. If, however, the settling process is nonlinear, the resultant error will show up as distortion. Of the two factors, nonlinear settling is by far the more serious problem. A linear settling error has very little effect on the performance of a single-loop modulator, and a linear settling to within 0.1% is more than adequate for most cascaded modulators. A nonlinear settling error, on the other hand, will degrade the performance of both single-loop and cascaded modulators. If the input capacitor of the modulator does not charge completely and the degree of charging is signal dependent, then the effect is the same as if the input capacitor were nonlinear. The error will show up as harmonic distortion and is not affected by the oversampling ratio.

The most straightforward solution for eliminating the effects of nonlinear settling is to make sure the circuit settles completely enough so that no matter what the signal dependence may be, the dynamic range requirements are still satisfied. For example, if the circuit settles to within 0.001% of final value, then a 100-dB dynamic

range is guaranteed regardless of the nature of the settling. Settling problems due to the RC time constant of the MOS switch and the switched capacitor can usually be solved simply by increasing the width of the switch. the limitation being that as the switch becomes larger in comparison to the switched capacitor, the effects due to channel charge injection and the parasitic junction capacitances also increase. The settling of the opamp is a bit more involved since it depends on several factors: slew rate, unity-gain bandwidth, and gain configuration.

To summarize the above discussion for the integrator shown in Fig. 2.16, the integrator transfer function will differ from the ideal because of nonzero switch resistance, and finite opamp bandwidth. With finite opamp bandwidth B (in hertz) the transfer function can be written as

$$H(z) = \frac{(C_1/C_2)z^{-1/2}[(1-\epsilon) + z^{-1}\epsilon C_2/(C_1 + C_2)]}{1-z^{-1}}$$

(2.16)

where

$$\epsilon = e^{-\pi BT_s}. (2.17)$$

where  $T_S$  is the sampling period. For nonzero switch resistance  $R_{on}$ , the transfer function is written as

$$H(z) = \frac{(C_1/C_2)z^{-1/2}(1 - 2e^{-T_s/4R_{on}C_1})}{1 - z^{-1}}$$

(2.18)

When all of the non idealities are considered together, i.e. the finite gain, the finite bandwidth, and the non ideal switches, they will interact with each other. For a complete analysis see [20].

### 2.3.2.3 Comparator Requirement

In switched-capacitor circuits the comparator specification is not as important as that of the integrators. If there is any offset, the gain of the integrator will transfer the offset to the input. On the other hand, in the continuous time circuits, the output of the comparator is latched on every clock pulse, and the latched comparator decision is used to apply a  $+V_{ref}$  or  $-V_{ref}$  voltage to a resistor connected to the integrator summing junction. This voltage is continuously applied to the integrator during the entire clock period. Note that the amount of charge delivered to the integrator is a function of the width of the clock pulse, the rise and fall times of the voltage feedback waveform, and, in the case of unequal rise and fall times, the previous bit decision. The use of a "return-to-zero" scheme can in theory eliminate the effect of previous bit decisions and rise-fall mismatches, but it increases the sensitivity to jitter [21].

### 2.3.2.4 Clock Jitter

Calculating the effect of clock jitter on a  $\Delta\Sigma$  A/D converter implemented in switched-capacitor technology is a fairly simple matter. The operation of switched-capacitor circuits depends on complete charging during each phase of the clock. Once the analog signal has been sampled, the switched-capacitor circuit is similar to an analog sampled-data computer. The lengths of the time slots and the variations in the lengths of the time slots have no direct effect. Therefore, the effect of clock jitter on a switched-capacitor circuit can be analyzed by examining its effect on the sampling of the input signal and on the reconstruction of the output signal.

Since the output of an A/D converter is digital, the effect of clock jitter on the performance of a  $\Delta\Sigma$  A/D converter is completely accounted for by taking into account the effect that it has on the sampling of the input signal. This also implies that the effect of clock jitter on switched-capacitor  $\Delta\Sigma$  modulator is independent of the structure or order of the modulator.

Consider the effect of clock jitter on the sampling of the input signal. A sinusoidal time jitter with amplitude  $\alpha$  and frequency  $\omega$  will cause the sampling of the input signal at time  $\tau$  to instead occur at time  $\tau + \alpha \sin(\omega \tau)$ . (The effect is the same as if the input signal .  $A\cos\omega_0\tau$ , were instead  $A\cos[\omega_0(\tau+\alpha\sin\omega\tau)]$ ). This can also be written in the form  $A\cos(\omega_0\tau + \alpha\omega_0\sin\omega\tau)$ , which is recognizable as the expression for frequency modulation (FM). For  $\alpha\omega_0\ll 1$ , the jitter will give rise to a pair of sidebands at  $\omega_0 - \omega$  and  $\omega_0 + \omega$  with an amplitude  $A\alpha\omega_0/2$ . It can be seen that the jitter is modulated by the input signal and its power is scaled by the factor  $A^2\omega_0^2/2$ . Whether oversampling will help to reduce the output error caused by the jitter depends on the nature of the jitter. If the jitter is assumed to be white [6] and has a power  $(\Delta \tau)^2$ , then the resultant error will have uniform power spectral density from 0 to  $f_s/2$ , with a total power of  $(A\omega_0\Delta\tau)^2/2$ . In this case, the in band noise power will be reduced by the OSR. On the other hand, if the clock jitter has a 1/f characteristic ("close-in noise"), then the error will have a spectrum that appears as a "skirt" on the spectral line of the fundamental. In this latter case, oversampling will not reduce the in-band noise, and a  $\Delta\Sigma$  converter will have the same sensitivity to jitter as a Nyquist-rate converter. Note that for continuous-time loop filters the effects are much more complex and harmful.

## 2.3.3 Design procedure

In this section we would like to explain the steps to design an IF or RF digitizer using low-pass sigma-delta modulators. In [22-24], complete design techniques for high order or multi-stage sigma-delta modulators for audio applications are shown. Since we are using these architectures for high frequency applications, we should consider other parameters like the distortion in the sample and hold or sampling mixer as well as the parameters discussed in the above mentioned references. The design procedure can be summarized as:

- 1. SNR. Bandwidth, and dynamic range(DR) have to be chosen.

- 2. The input carrier frequency is the second parameter which has to be chosen.

- 3. Using the above information, the order of the modulator for a given OSR is next determined:

- (a) from SNR value, the ideal equations should be used for different architectures to calculate the order of sigma-delta modulators. For example, for a single stage first order modulator the SNR can be determined by

$$SNR_{max} = 6.02N - 3.41 + 30\log(OSR)$$

(2.19)

or for a second-order modulator the SNR can be determined by:

$$SNR_{max} = 6.02N - 11.14 + 50\log(OSR)$$

(2.20)

or in general  $SNR = 6.02N + 20 \log(OSR)^{\frac{L+1}{2}}$ . The number of output bits. N. can be chosen arbitrarily. In most applications a one bit structure is required, therefore, the OSR can be calculated for a given order. L.

- (b) After determining the OSR, the sampling clock frequency can be calculated for a given bandwidth. If the calculated sampling clock frequency is too large, the order must be increased.

- 4. The next step is to determine the noise transfer function(NTF) and signal transfer function (STF). The NTF and STF transfer function can be determined by the following steps [22]:

- (a) Choose a modulator order and a NTF filter family. Modulator order already has been chosen in the previous step. For the NTF filter family. high-pass Butterworth. Chebyshev. or maximally flat all-pole filters can be chosen.

- (b) Pick a value for cut off frequency which is larger than that of the required bandwidth. Then scale the transfer function so that the first sample of the impulse response is 1.

- (c) Construct a modulator with this NTF and either simulate it or use the describing function method [25] to determine its maximum stable input and peak SNR. The maximum stable input gives the dynamic range.

- (d) If the modulator is unstable, reduce the out-of-band gain of the NTF.

(e) If the modulator is stable but SNR is not adequate, then increase the out-of-band gain of the NTF.

To determine which architecture should be chosen, one of the five following options should be used [23]:

- (a) Chain of integrators with weighted feed forward summation.

- (b) Chain of integrators with feed forward summation and local resonator feedbacks.

- (c) Chain of integrators with distributed feedback

- (d) Chain of integrators with distributed feedback and distributed feed forward inputs

- (e) Error feedback only.

- 5. Determine the minimum requirement for each block of the sigma-delta modulator to meet the specification. Designing the architecture in ideal form is not enough. To complete the design, opamp specifications such as dc gain, settling time, unity gain bandwidth have to be found. The important parameters can be summarized as:

- (a) Minimum gain for the opamp. One simple rule is that the minimum gain should be  $\frac{OSR}{\pi}$ .

- (b) The settling time as was explained in the previous section is dependent on the sampling clock frequency.

(c) In IF applications the linearity of this circuit is very important. The design guide presented in [3-5] can be used to design a highly linear sampling mixer. That is also used as in the S/H circuit.

In the next section, a design example is discussed in detail to present a step-by-step design framework for the reader.

### 2.3.3.1 Design Example

In this section, by using the design steps explained in the previous section a complete design cycle for an IF digitizer will be presented.

Example: A 40 MHz IF digitizer with a 200kHz bandwidth and a 70dB SNR is required.

#### Solution:

Step 1: Finding the order of the modulator. OSR, and the sampling clock frequency: The ideal second order modulator SNR can be written as:

$$SNR_{max} = 6.02M - 11.14 + 50\log(OSR). \tag{2.21}$$

where M is the number of output bits. In general, any number of bits can be chosen. But practically, producing a highly linear multi-bit D/A converter is very difficult. Therefore, usually the designers try to design a single-bit modulator. In this design, a single-bit modulator is designed. Therefore, the above equation can be written as:

$$70 = 6.02 - 11.14 + 50 \log OSR \tag{2.22}$$

Or.

$$OSR = 31.79$$

(2.23)

It is round up to 32. With an OSR of 32 and a 200kHz bandwidth, the clock should be chosen to be at least 12.8MHz. To simplify the implementation the ratio of the input frequency to the sampling clock should be an integer. As a result the sampling clock frequency is 20MHz or the OSR is 50.

Step 2: Determine the NTF: A single-bit second-order structure is chosen. so, using the standard second-order design which is shown in [7] can provide the required SNR. For this structure the NTF can be written as:

$$NTF = \frac{4(1-z^{-1})^2}{3z^{-2} - 6z^{-1} + 4}$$

(2.24)

Step 3: Determine the architecture: A chain of integrators with distributed feedback shown in Fig. 2.10 is used for this design.

Step 4: Determining the minimum requirement for each block.

- 1. Opamp gain: The minimum required opamp gain can be calculated using g > OSR. Therefore a gain of 150 will satisfy the condition.

- 2. Settling time: Since the clock is chosen to be 20MHz, the integrator output has to settle in 25 ns for a two phase clock. Assume linear settling and 0.1% settling. Let us use equation (2.16) and assume H(z) to settle to 0.1%. The ε is to be 0.003. Using equation (2.17) the B (opamp bandwidth) is calculated to be 73MHz.

- 3. Sampling Capacitor  $C_1$ : The noise regarding the sampling capacitor is  $\frac{KT}{C}$ . where K is the Boltzmann constant and T is the room temperature. For a requirement of one volt input, a 0.5pF capacitor for  $C_I$  is large enough to exceed a SNR of 70dB. From Fig. 2.10,  $C_S = \frac{C_I}{2} = 0.25pF$ . Because of noise reduction due to oversampling (3dB/octave), the noise decreases by another 12 dB, therefore, the C can be selected from a 58dB criterion instead of 70dB. As a result the C required can be smaller.

- 4. Sampling mixer design: In the first section of this chapter, the sampling mixer is explained. The sampling capacitor is already chosen due to SNR criteria. The fall time of the clock edge and the switch size are the two parameters that have to be chosen. Since the input frequency is not high, the dominant distortion is from time invariant distortion.  $HD_3$  can be written as: [3-5]

$$HD_3 = \frac{A^2}{4} \frac{\omega C}{K(V_G - V_t)^3} \tag{2.25}$$

in which A,  $\omega$ , C, K,  $V_G$ , and  $V_t$  represent the input amplitude, input frequency in rad/sec, sampling capacitor,  $\mu_n C_{ox} \frac{W}{L}$ , gate voltage, threshold voltage of the sampling switch respectively. The harmonic distortion must now degrade the signal-to-noise plus distortion ratio (SNDR). Arbitrarily set the harmonic distortion (HD) to -80dBm with the 0dBm input for a 50 $\Omega$  input impedance. 3.3 volts power supply can be used with  $0.5\mu m$  CMOS technology. In this technology the NMOS transistor threshold is about 0.8 volts.

The size of the transistor is calculated as:

$$\frac{W}{L} = 255.9 \tag{2.26}$$

therefore, with the minimum length transistor.  $154\mu m$  is the width of the sampling mixer transistor. This is one of the three types of distortion which is discussed in detail in [3-5]. The other two types depend on the fall time of the clock and in one of the cases depends on the size as well. Since the sampling mixer is operating at IF (low enough frequency) the other two types of distortion can be ignored. To ignore the other two types of distortion, the maximum allotted fall time of the sampling clock has to be determined. The sampling distortion can be written as:

$$HD_3 = \frac{3A^2}{32} \left(\frac{\omega T_f}{V_G}\right)^2 \tag{2.27}$$

in which  $T_f$ ,  $V_G$ , A, and  $\omega$  represent fall time of the sampling clock, gate voltage of the sampling switch, input signal amplitude, and the input frequency respectively. When the transistor size was calculated, it was assumed that the allotted distortion was -80dBm for 0dBm input. The fall time of the clock edge must be small enough so that the distortion created by fall time is much smaller than that of the time invariant distortion. Assuming the distortion due to sampling distortion is -100dBm, the fall time can be calculated as:

$$T_f = 214ps \tag{2.28}$$

The time varying distortion can be evaluated to make sure that the distortion produced by this type is much less than that of the time invariant distortion. For the present case this type of distortion can be determined by:

$$HD_3 = \omega^3 \sqrt{\frac{C}{K}} \left(\frac{T_f}{V_G}\right)^{5/2} \times 0.0913$$

(2.29)

Therefore, distortion for the third type is around -100dBm which is acceptable.

In summary, it can be seen as one moves to higher frequencies (>100MHz) designing a low distortion sampling mixer becomes more and more difficult to achieve as  $\frac{W}{L}$  becomes unacceptably large. Therefore, the sampling mixer becomes the major bottleneck in the design.

5. Comparator Speed: The issue about comparator speed is due to the availability of the output code for less than half of the clock period to do the subtraction properly. In active architectures, the offset or the noise of the comparator is not very important because the effect is noise shaped.

# 2.4 band-pass architecture