## Process Spaces

# and Formal Verification of Asynchronous Circuits

by

## Radu Negulescu

A thesis

presented to the University of Waterloo in fulfilment of the thesis requirement for the degree of Doctor of Philosophy

in

Computer Science

Waterloo. Ontario. Canada. 1998

©Radu Negulescu 1998

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre reférence

Our file Notre reférence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-32848-1

The University of Waterloo requires the signatures of all persons using or photocopying this thesis. Please sign below, and give address and date.

We are not seeking simplicity in art. but we usually arrive at it as we approach the true nature of things.

Constantin Brancusi. 1876-1957

#### Abstract

This thesis proposes process spaces, a simple and unified treatment for concurrency issues such as parallel composition, refinement, deadlock, livelock, and starvation. Processes are modeled as contracts over which executions may occur. The main innovation is that executions are abstract: this leads to a very general model. For trace-based executions, process spaces relate closely to trace theory and CSP, except that we do not attach alphabets or connectivity restrictions to processes.

We revise several algebraic properties of process compositions and comparisons that are commonly known from concurrency theory. A novel transform reveals symmetries among usual process operations.

For finite-trace processes, we have a tool that uses a public-domain BDD library. This tool fully supports modular and hierarchical verification, and draws on the flexibility of the underlying formalism to address several niche applications. One application is to detect switch-level faults in asynchronous MOS circuits. Another is to verify sufficiency of relative delay constraints by handling them as metric-free processes, without requiring post-layout numerical information on delays.

By comparing processes for liveness and progress, we obtain a classification of concurrency faults. We also determine links among implicit liveness, progress, and safety properties, so one can specify just the simpler safety properties, and then assume typical liveness and progress properties. We briefly discuss some promising applications that involve analog trajectories and true concurrency.

To handle relabelings, hidings, and derivatives, we construct them as process maps arising from relations on execution sets. We obtain several algebraic properties, including criteria for performing verifications on images of processes by overapproximation, under-approximation, and independence with respect to such maps.

#### Acknowledgements

My thesis is a product of interaction with the Maveric group at the University of Waterloo, and I wish to thank everyone involved: Janusz A. Brzozowski, my supervisor, has invested valuable ideas and a considerable amount of effort in directing and reviewing my work: Jo C. Ebergen has introduced me to a modern view of asynchronous circuits through a very interesting graduate course and has made key suggestions as well: Robert T. Berks, Robert D. Black, Chuan-Jin (Richard) Shi. Piotr R. Sidorowicz, Signe J. Silver, and the other student members of the Maveric group have contributed constructive feedback for my presentations and writings, and a friendly and supportive environment; and, inspiration has also come from discussions with Charles E. Molnar, Tom Verhoeff, and other visitors to our group.

My external examiner. David L. Dill. and the other members of my thesis committee. Joanne M. Atlee, Janusz A. Brzozowski, Jo C. Ebergen, and Bruno R. Preiss. have provided insightful suggestions and relevant bibliography; I thank them for their interest and careful reading of the manuscript.

I wish to express my gratitude to the late Charles E. Molnar for offering me a summer internship at Sun Microsystems Laboratories, which allowed me to synchronize my theory and tool with the asynchronous practice. This internship has been one of the bright spots of my PhD program, and I would like to thank the entire asynchronous team at Sun Microsystems Laboratories for their pleasant cooperation. I also thank Ad M.G. Peeters from Philips Research Laboratories and André Bouwer, John F. Chappel, and Craig Farnsworth from Cogency Technology for their help in applying my tool to their circuits. Ad Peeters has made a direct contribution to the applications reported in Chapter 4, by co-authoring a paper. These collaborations have been very beneficial for my work.

The Model Checking Group at Carnegie Mellon University is gratefully acknowledged for making available a BDD library that I have used in the tool described in Chapter 3. Also, I thank Dan Calistrate from the University of Calgary for quick briefings regarding mathematical background.

Special thanks go to Maria. my wife, who has done so much to help me, comfort me, and improve my morale throughout the ups and downs of graduate studies. My parents and my sister have always been cheering from afar, never failing in their support, and they have encouraged me greatly. Also, I am obliged to all my friends for many a social occasion and other gratifying activities.

Finally. I would like to acknowledge the financial support for my PhD studies. provided by grant OGP0000871 from the Natural Sciences and Engineering Research Council of Canada (NSERC). by an Ontario Graduate Scholarship. by a grant and a scholarship from the Information Technology Research Centre of Ontario. by teaching assistantships from the Department of Computer Science at the University of Waterloo, and by Sun Microsystems Laboratories directly through an internship salary and indirectly through a grant to our group that has prompted matching funds from NSERC.

# Contents

| 1 | Intr | oduction                                            | 1  |

|---|------|-----------------------------------------------------|----|

|   | 1.1  | Objectives of the Thesis                            | 3  |

|   | 1.2  | Previous Work                                       | 7  |

|   |      | 1.2.1 Models of Concurrency                         | 7  |

|   |      | 1.2.2 Methods for Asynchronous Circuit Verification | 11 |

|   |      | 1.2.3 Liveness and Progress                         | 12 |

|   |      | 1.2.4 Process Abstractions                          | 14 |

|   | 1.3  | Notes on Terminology                                | 15 |

| 2 | Pro  | cess Spaces                                         | 16 |

|   | 2.1  | The Model                                           | 17 |

|   | 2.2  | Correctness Conditions                              | 22 |

|   | 2.3  | Operations                                          | 28 |

|   | 2.4  | Manipulation of Processes                           | 38 |

|   | 2.5  | Sets of Processes                                   |    |

|   | 2.6 | Lattice Properties                              | 47  |

|---|-----|-------------------------------------------------|-----|

|   | 2.7 | Symmetries of Process Spaces                    | 49  |

| 3 | Han | dling Safety and Finalization                   | 56  |

|   | 3.1 | Safety and Finalization                         | 57  |

|   | 3.2 | Process Automata                                | 60  |

|   | 3.3 | A BDD-Based Implementation                      | 63  |

| 4 | Rel | ative Delay Assumptions                         | 73  |

|   | 4.1 | Cell Models                                     | 75  |

|   | 4.2 | Chain Constraints                               | 80  |

|   |     | 4.2.1 Extended Isochronic Fork Assumptions      | 86  |

|   |     | 4.2.2 Thresholds and Constraint Interpretations | 88  |

|   |     | 4.2.3 Safety Margins                            | 91  |

|   |     | 4.2.4 Case Studies: Handshake Circuits          | 91  |

|   | 4.3 | Stocktaking                                     | 103 |

| 5 | Swi | tch-Level Correctness Concerns                  | 105 |

|   | 5.1 | Switch-Level Correctness Concerns               | 107 |

|   | 5.2 | Local Isochrony                                 | 114 |

|   | 5.3 | Case Study: A Self-Timed RAM                    | 117 |

|   | 5.4 | Detecting Persistent Shorts                     | 128 |

|   | 55  | Stocktaking                                     | 131 |

| 6 | Han | dling Liveness and Progress                | 134   |

|---|-----|--------------------------------------------|-------|

|   | 6.1 | Liveness                                   | 137   |

|   | 6.2 | Progress                                   | 143   |

|   | 6.3 | A Taxonomy of Lock Faults                  | 146   |

|   | 6.4 | Implicit Liveness and Progress Properties  | 151   |

|   |     | 6.4.1 Finite-Trace Structures              | 152   |

|   |     | 6.4.2 Implicit Liveness Properties         | 154   |

|   |     | 6.4.3 Implicit Progress Properties         | 161   |

|   |     | 6.4.4 Limitations of the Default Processes | 164   |

| 7 | Вез | ond Trace-Based Applications               | 167   |

|   | 7.1 | Steady-State Networks                      | . 167 |

|   | 7.2 | Dynamical Systems                          | . 169 |

|   | 7.3 | Input Control                              | . 171 |

|   | 7.4 | Timing                                     | . 173 |

|   | 7.5 | True Concurrency                           | . 174 |

| 8 | Pro | ocess Abstractions                         | 177   |

|   | 8.1 | Preliminaries                              | . 178 |

|   | 8.2 | Process Abstractions                       | . 188 |

|   | 8.3 | Verifications on Images                    | . 194 |

|   |     | 8.3.1 Optimistic Approximations            | . 196 |

| Bi | iblio | graphy  | •                                | 219 |

|----|-------|---------|----------------------------------|-----|

|    | 9.2   | Curre   | nt Limitations and Further Work  | 217 |

|    | 9.1   | Contr   | ibutions of the Thesis           | 214 |

| 9  | Cor   | ıcludin | ng Remarks                       | 213 |

|    | 8.5   | Furth   | er Applications                  | 211 |

|    |       | 8.4.7   | Divergence                       |     |

|    |       | 8.4.6   | Process Compositions             | 210 |

|    |       | 8.4.5   | Reflection and Rotations         | 209 |

|    |       | 8.4.4   | Deletion, Hiding, and Projection | 209 |

|    |       | 8.4.3   | Process Derivatives              | 207 |

|    |       | 8.4.2   | Restricted Execution Sets        | 207 |

|    |       | 8.4.1   | Relabeling of Actions            | 206 |

|    | 8.4   | Examp   | ples of Applications             | 205 |

|    |       | 8.3.3   | Independence                     | 203 |

|    |       | 8.3.2   | Pessimistic Approximations       | 200 |

# List of Tables

| 2.1 | Substitutions made by the ternary symmetry principle. | • | • | • | • | • | <b>5</b> 4 |

|-----|-------------------------------------------------------|---|---|---|---|---|------------|

| 4 1 | Simulated logic thresholds                            |   |   |   |   |   | 88         |

# List of Figures

| 2.1  | Execution sets of a process           | 18         |

|------|---------------------------------------|------------|

| 2.2  | Etiquette machine.                    | 19         |

| 2.3  | Watch your mouth!                     | 20         |

| 2.4  | Process of etiquette machine.         | 21         |

| 2.5  | Examples for refinement               | 24         |

| 2.6  | The product operation                 | 28         |

| 2.7  | Listener and Speaker                  | 29         |

| 2.8  | Example for product                   | <b>3</b> 0 |

| 2.9  | Charting a process space              | 36         |

| 2.10 | Modular and hierarchical verification | 39         |

| 2.11 | Forward rotation                      | <b>5</b> 0 |

| 3.1  | Safety process of etiquette machine   | 59         |

| 3.2  | Example of a process automaton.       | 61         |

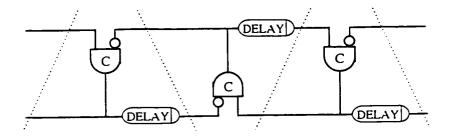

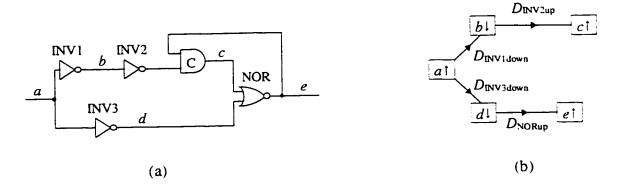

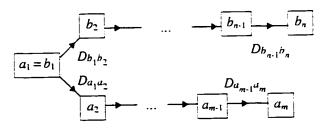

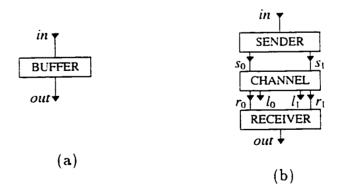

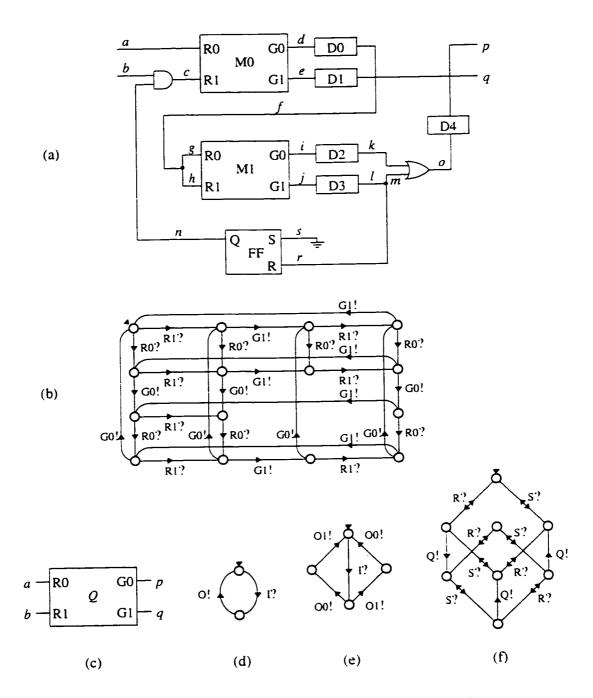

| 3.3  | Basic micropipeline control circuit.  | <b>7</b> 0 |

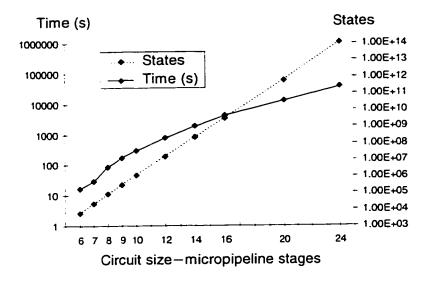

| 3 4  | Performance plot                      | 71         |

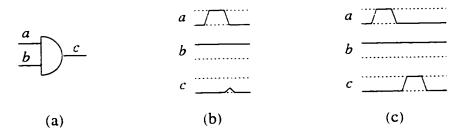

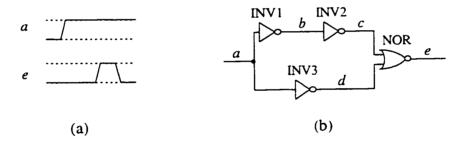

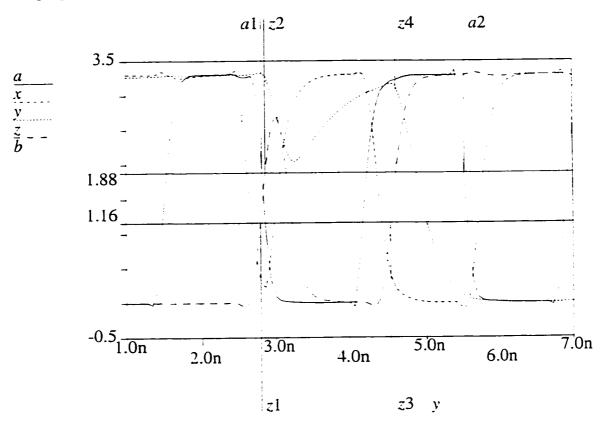

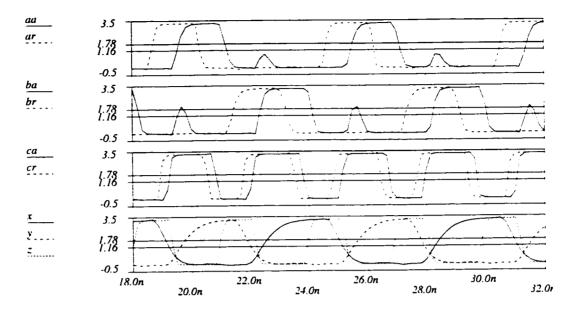

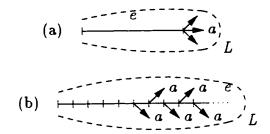

| 4.1  | Waveform of a buffer                                    | 76  |

|------|---------------------------------------------------------|-----|

| 4.2  | Responses to a short pulse                              | 77  |

| 4.3  | Hazard-intolerant model                                 | 78  |

| 4.4  | Inertial model                                          | 79  |

| 4.5  | Is the waveform realized by the circuit?                | 80  |

| 4.6  | Ensuring correct behavior                               | 81  |

| 4.7  | General form of competing delay chains                  | 81  |

| 4.8  | Specification process                                   | 83  |

| 4.9  | Process for a chain constraint                          | 84  |

| 4.10 | Meaning of a delay constraint.                          | 88  |

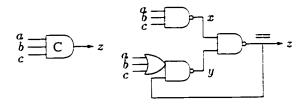

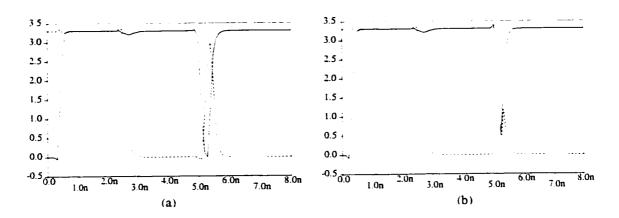

| 4.11 | Three-input C-element                                   | 92  |

| 4.12 | Simulated response to an input pulse                    | 94  |

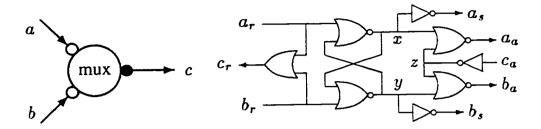

| 4.13 | Multiplexer component and control circuit               | 96  |

| 4.14 | Simulation of a failure mode                            | 99  |

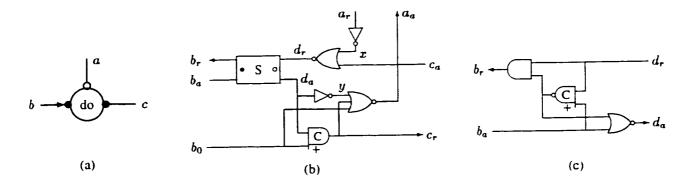

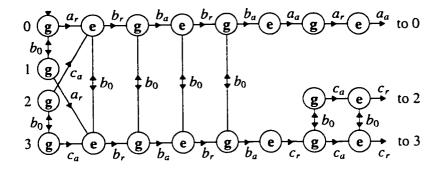

| 4.15 | DO-component                                            | 101 |

| 4.16 | Finalization process for the DO-component specification | 102 |

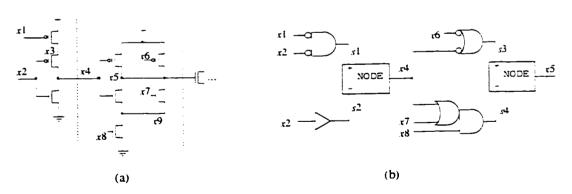

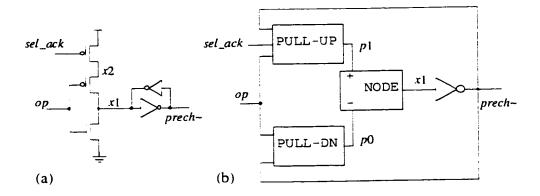

| 5.1  | Modeling a switch-level network.                        | 107 |

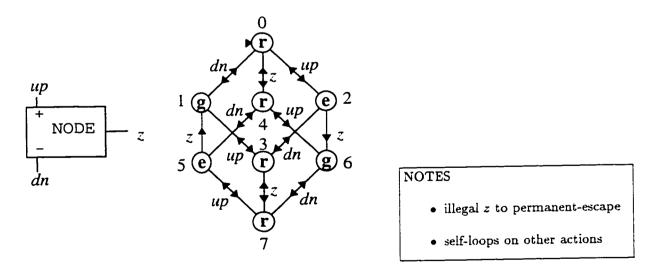

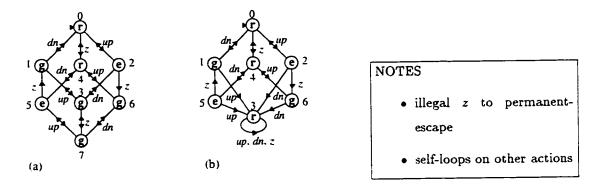

| 5.2  | Node icon and possible node process                     | 109 |

| 5.3  | Do we forbid collisions?                                | 110 |

| 5.4  | Do we forbid switching during collisions?               | 111 |

| 5.5  | Modeling paths                                          | 113 |

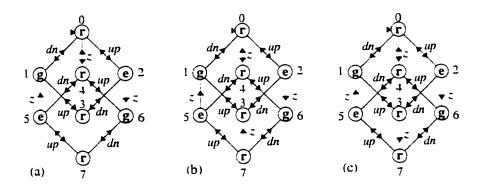

| 5.6  | Obtaining a quickened model                           | 115 |

|------|-------------------------------------------------------|-----|

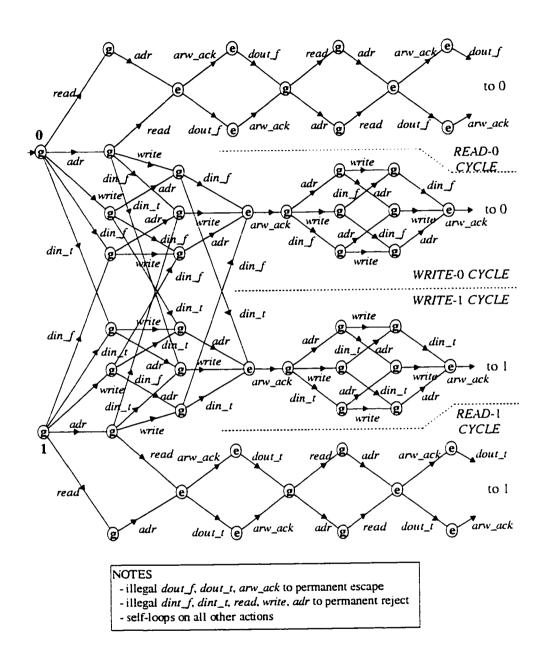

| 5.7  | Schematic of self-timed RAM circuit                   | 118 |

| 5.8  | Circuit specification.                                | 120 |

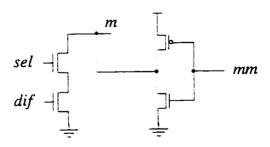

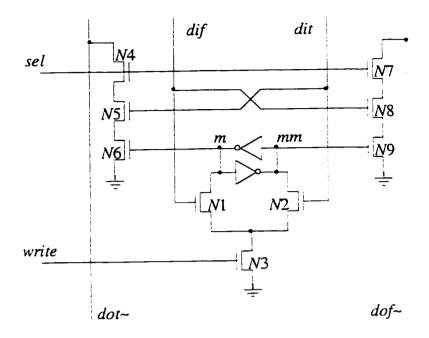

| 5.9  | Part of memory cell                                   | 122 |

| 5.10 | Speed-independent RAM                                 | 126 |

| 5.11 | Model for detecting persistent shorts                 | 129 |

| 6.1  | Example circuit and gate.                             | 138 |

| 6.2  | Specification for starvation example.                 | 141 |

| 6.3  | Implementation for starvation example                 | 142 |

| 6.4  | Communication protocol for livelock example           | 144 |

| 6.5  | Absolute lock faults.                                 | 148 |

| 6.6  | Relative lock faults                                  | 149 |

| 6.7  | Aspirins for lock headaches                           | 150 |

| 6.8  | A behavior automaton                                  | 154 |

| 6.9  | Recurrently enabled and fired symbols.                | 155 |

| 6.10 | Unfair implementation of mutual exclusion             | 159 |

| 6.11 | Continuously enabled symbols                          | 162 |

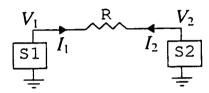

| 7.1  | Electrical network for steady-state parameter example | 168 |

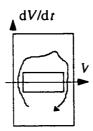

| 7.2  | Requirement of Brockett ring type.                    | 170 |

| 73   | Goal set for multiple-winner example                  | 178 |

| 8.1 | Example of a Galois connection. | ٠ | ٠ | ٠ | • | • | • | • | • | • |     | • |       | <br>٠ | • | • | • | 179 |

|-----|---------------------------------|---|---|---|---|---|---|---|---|---|-----|---|-------|-------|---|---|---|-----|

| 8.2 | Example relation                |   |   |   |   |   |   | - |   |   | . , | • | <br>• |       |   |   |   | 187 |

# Chapter 1

## Introduction

Discrete-state systems are practically everywhere: some examples are digital circuits (synchronous and asynchronous). programs and data structures. communication protocols. and work flows in a factory. Discrete-state systems have finite or countable state spaces. Because such systems may consist of several interacting parts, they are sometimes referred to as concurrent systems; however, sequential programs are also important members of this class. Discrete-state systems are exposed to diverse modes of failure, including illegal inputs and outputs, deadlock, livelock, unfairness, and performance faults. Many models have been proposed to capture these diverse phenomena in research areas such as software engineering, digital circuits, and distributed systems.

Despite their diversity, discrete-state systems have several common aspects. The fact that their state spaces are finite or countable is essential for their analysis, but it is not the main unifying aspect. More importantly, there are common mechanisms by which such systems can be composed and compared, and these compositions and comparisons satisfy several common properties that are basic and useful.

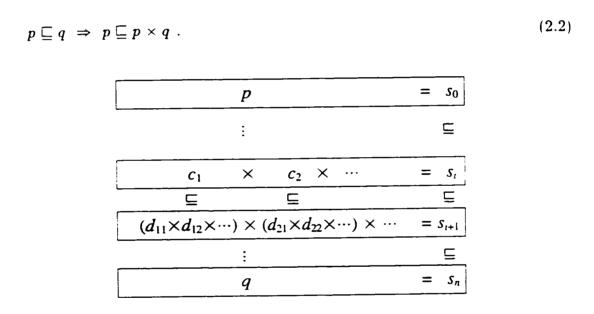

For an example of common properties of discrete-state systems, consider the phrase 'implementation r satisfies specification q': that is, r can replace q in a system, without introducing new dangers of incorrect operation in that system. Furthermore, the specification q may be an implementation for a higher-level specification p. (This viewpoint tacitly assumes that the specification and the implementation are represented by formal objects of the same nature, although implementation models typically contain more details than the higher-level specifications.) Then, a common-sense property is that, if q satisfies p and p satisfies p, and this can be applied for several levels of specifications. This property is known as successive refinement or hierarchical verification.

The discussion of hierarchical verification above is not tied to particular models or their levels of detail. and not even to the criteria for comparison. On the basis of this observation, we believe it is beneficial to keep such discussions simple and general, by postponing, as much as possible, references to modeling details or specific correctness concerns. We propose to study discrete-state systems by means of abstract executions, that is, without referring to the form or structure of the executions. Executions can be finite sequences, infinite sequences, time-stamped sequences, etc., but we consider them to be just elements of an arbitrary set.

Just as concepts from Newtonian mechanics are modeled by numbers, properties of discrete-state systems can be modeled by sets of abstract executions. Then, common-sense laws like hierarchical verification can be studied by elementary set calculus. It may be non-trivial to relate abstract executions to real systems, just as it is non-trivial to explain to a novice what force is: however, the modeling disciplines should become easy with practice. The eventual benefit of such an approach is that one could apply generic laws, like F = ma, for very diverse systems and at all levels of analysis where the general paradigm applies.

## 1.1 Objectives of the Thesis

The purpose of this thesis is to take steps towards a general theory of discrete-state systems along the lines suggested above, while making sure that sufficiently many practical applications exist to serve as proofs of concept. This often involves reworking some operations and properties from previous theories of concurrency (which will be discussed below), but some novel operations and properties are introduced as well. More importantly, we adopt an original viewpoint that regards executions as an abstract notion, and makes no references to states, variables, events, ports, or actions: this results in some distinguishing aspects of the proposed approach.

In terms of theory, two main steps are taken. One is a general formalism that models processes by means of abstract executions, that is, without references to structural details of the executions. We call this formalism process spaces. The other step is a study of maps between processes by means of relations between executions: we call the mappings in this study process abstractions.

We give examples from several fields. ranging from concurrent programs to electrical networks. For in-depth applications, we focus on formal verification techniques for asynchronous circuits. Asynchronous circuits are designed without the assumption of a global clock, and can be viewed as networks of digital components that operate in parallel and synchronize on voltage transitions of the interconnecting wires. For this reason, asynchronous circuits make good test-benches for any theories that deal with concurrency issues in general discrete-state systems. Formal verification aims to search exhaustively for flaws of certain types in a given system, which might be composed of several parts and compared to a specification. Thus, formal verification of asynchronous circuits offers a practical setting for

experimenting with correctness concerns and operations on discrete-state systems.

After establishing the basis for verifying asynchronous circuits in process spaces. we develop two niche applications that are of practical interest, and we illustrate them on published designs. We needed a high-performance tool to allow us to study non-trivial examples. We have implemented the process space operations and conditions for execution sets that are regular languages of finite words. BDDs (binary decision diagrams) are data structures and algorithms for manipulating Boolean functions. Many verification problems are computationally intensive, and this applies for BDD-based algorithms too in the worst cases; however, in typical cases BDDs are known to increase performance by many orders of magnitude compared to traditional algorithms for these problems. Our tool represents large state spaces by characteristic functions of sets, and uses a public-domain BDD library for the routine operations on large Boolean functions.

Many recent asynchronous designs tend to rely on timing to achieve speed (see [MJCL97]) or energy and area savings (see [BHP95] and [Pee96]). In the VLSI design of asynchronous circuits, the numerical bounds on component delays are not known with sufficient precision until after setting the layout, transistor sizes, and wire lengths. On the other hand, the effort for optimizing the layout is substantial, and thus it is important to verify a circuit, as much as possible, before layout. We model relative delay constraints of a certain form as metric-free processes that simply ensure orderings of events; this way, the verification does not refer to numerical bounds on delays, can be performed before layout, and all the generic laws deduced for processes fully apply.

Another problem we address is the detection of switch-level faults in MOS transistor networks. At the switch level, the behavior of MOS transistor networks is approximated by on/off switches. Depending on the design style and local op-

timizations. switch-level faults include floating states. collisions. and shorts. In floating states, certain circuit nodes are disconnected from both ground and power supply: in collisions and shorts, certain circuit nodes are connected to both ground and power supply, with the additional problem that the connections are of roughly equal strengths in the case of collisions. We propose a verification technique that detects such switch-level faults in asynchronous circuits.

Given the generality of process spaces, one may wonder what non-trivial properties of discrete-state systems can be captured. It turns out that many important parts of the theory of concurrency can be adapted to abstract executions. Also, we have found some new properties. Certain things are lost or gained, however, in this generalization. Properties like hierarchical verification were usually given in previous formalisms under various restrictions pertaining to connectivity: no two outputs can be connected, only processes with the same inputs and outputs can be compared, etc. Since we do not refer to structural detail of executions, we do not impose similar restrictions. This generalization is done not by extending existing models with new features, but rather by removing existing features. Using case studies, we confirm that the unrestricted properties do apply and are sufficient at least for our formal verification applications. In addition, we have indications that the generalized properties apply to other systems and types of analysis as well.

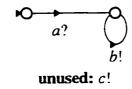

Our investigation was started as a study of correctness concerns for asynchronous circuits. Finitary descriptions are regarded as insufficiently powerful for various correctness concerns, like liveness, which are treated by means of infinite words (see for instance [AS85] and [Dil89] for two prominent treatments of liveness): [Bla86] even gives an argument that general liveness properties cannot be captured by finite traces. On the other hand, many of the common descriptions of circuits available in practice are equivalent in power to such finitary descriptions.

Accordingly, we had undertaken to define and study whatever correctness concerns we can in terms of finitary descriptions only. Although we do not challenge the argument of [Bla86], we have noticed that default liveness properties can be uniquely associated to such descriptions in a way that does correspond to our expectations for liveness properties in many asynchronous circuits. The same holds for a slightly different class of properties, known as progress properties.

We also study the algebraic properties of liveness and progress representations. and we propose a classification of liveness and progress faults that matches our intuitive notions of deadlock. livelock. and starvation: we call them collectively lock faults. For these purposes, we found it more natural to refer to infinite traces rather than to finitary descriptions. Nevertheless, users can still apply finitary descriptions for ease of specification, extract the default liveness and progress properties mechanically from such descriptions, and then apply the generic properties of processes or the classification of lock faults on the resulting processes, also mechanically. This way, users can have the best of both worlds. Finally, there are strong indications that our treatment of liveness and progress applies to other types of discrete-state systems as well: we point that out with small examples.

We continue the general theory of process spaces by a study of maps that preserve binary operations: these maps (called process abstractions) generalize other process operations, and allow for reduced verifications of processes. Some important operations in concurrency theory take as arguments not just processes, but also sets or sequences of actions: some examples are projections and hidings, where certain actions are deleted from executions, and derivatives, where an initial part of an execution is deleted. Is it possible to study all these operations without referring to the structure of executions? It turns out that projections, hidings, derivatives, and several other operations are just particular cases of process abstractions: as such, we

could indeed assimilate these operations within the abstract execution framework. At the same time, general process abstractions capture many properties of practical interest. We give particular emphasis to criteria that authorize us to perform verifications on images of processes through a process abstraction rather than directly on the original processes. These criteria and other generic algebraic properties we study for process abstractions are inherited by projections, relabelings, derivatives, and other operations, as particular cases of process abstractions.

#### 1.2 Previous Work

The literature on process modeling is vast. and unfortunately we cannot do justice to all of it within the scope of this thesis. We therefore restrict our survey to some of the better-known approaches from the asynchronous community and elsewhere.

#### 1.2.1 Models of Concurrency

Process spaces are closely related to several previous treatments of concurrency that model discrete-state systems essentially by their finite or infinite sequences of events: let us refer to models of this type as language-oriented models. Some of these related models are: the prefix-closed and complete trace theories in [Dil89]. the trace theory used in [Ebe91a]. the trace, failure, and divergence semantics in [Hoa85], the receptive process theory in [Jos92], the CFFD (chaos-free failures divergences) model in [VK98, VT95], and the theory of delay-insensitive systems in [Ver94b].

Our model for a process consists of two sets of abstract executions, representing an assumption/guarantee specification: one set represents guarantees about the be-

havior of the device, and the other set represents assumptions about the behavior of the environment. Assumption/guarantee specifications are a natural idea, which can be traced as far back as [Pnu77] and even Hoare's triples [Hoa69]. In CSP (communicating sequential processes) [Hoa85], non-deterministic processes are formalized essentially by two sets of behaviors (failures and divergences). In [Dil89], the two sets contain behaviors of the same type (sequences of symbols), and the idea is applied at two different levels of detail, using finite and infinite sequences. The processes of the extended DI (extended delay-insensitive) model in [Ver94b] also introduce assumptions and guarantees regarding two correctness issues (safety and deadlock), resulting in specifications with several sets of finite sequences of symbols. A separate development regarding assumption/guarantee specifications has been proposed in [AL95], using temporal logic [Lam94].

Although several theories of concurrency cited above use more than one type of sequence of events to describe the behaviors of their systems, they have made no proposals to use abstract executions. This is an important difference between process spaces and the theories cited above. Even for those process spaces that use sequences of events as executions, there are further differences regarding unusual connectivity cases. We discuss the impact of these differences on our niche applications, where we exploit precisely these connectivity cases that are ruled out by other models. We do not aim to prove that any of these models, including ours, is right or wrong; we only argue that our model is useful, because it fits naturally at least some applications that might contort other models, and because our model captures credible algebraic properties for these applications.

Although there are some differences on connectivity restrictions and other technicalities. we believe there is a basic agreement between particular instances of process spaces and the theories cited above, and among the theories above. In

particular. several of the generic properties of processes. such as hierarchical verification, have been known in many of these previous theories: our contribution, nevertheless, is to generalize them for arbitrary types of executions, without major modifications. In addition, we have found several new properties, mostly referring to maps between processes and to symmetries of process spaces.

Several of the theories above have a reflection or mirroring operation that induces a duality between devices and their environments: [Ver94b] even employs a symmetric notation. However, we are the first to complete this duality and to state it formally. Also, we propose a rotation operation that induces a ternary symmetry between common process operations. J. A. Brzozowski was the first to notice that process spaces are particular cases of ternary algebras [BLN96]. However, the rotation operation, the principle of ternary symmetry, and the resulting links between common process operations are our contribution and do not exist in general ternary algebras as presented for instance in [BS95] and [BLN96].

Since the early days of concurrency theory, there have been extensive efforts to establish an abstract view of discrete-state systems by axiomatic approaches. The resulting models, to which we refer as process algebras, define processes by the laws they satisfy. CSP, for instance, combines a process algebra viewpoint with the language-oriented viewpoint. Other algebraic approaches include, but are not limited to, the algebraic theory of processes of [Hen88], ACP (algebra of communicating processes) of [BK85], the laws of CCS (calculus of communicating systems) [Mil89]. Circal [Mil94], and, for asynchronous circuits, the algebraic model of [BC88] and the algebra for delay-insensitive circuits of [JU90]. Term algebras have been used to describe general concurrent systems in [Hen88] and VLSI circuits in [Car82], subsuming both the behavior and the connectivity of such systems.

Process algebras have captured many of the generic properties of processes. like

hierarchical verification. but those process algebras known to us also include laws that refer to structural details of executions. Some examples are laws for occurrence of individual events, laws for sequential composition (which assume that executions can be concatenated), and references to alphabets of actions. In our opinion, such references to structure have prevented the development of a general theory that would be truly independent of the level of analysis of a discrete-state system.

Other main approaches to the verifications of discrete-state systems are based on Petri nets. temporal and modal logics. and various types of automata ("operational semantics"). These formalisms provide data structures and algorithms for handling languages of finite or infinite words. but they are not concerned with reasoning in terms of abstract (structure-less) executions, relying instead on occurrences of events. Still, a discussion of modeling paradigms is in order.

It has been noted that the CCS notion of correctness relative to a specification, called "observation equivalence", makes finer distinctions than some language-oriented models: see for instance [Mil90]. On the other hand, a notion of relative correctness based on equivalence between specification and implementation is not very meaningful for our verification problems, because typically an implementation corresponds to just one of many behavior cases permitted by a specification; what we need is a directed (one-way) notion of relative correctness which allows an implementation to fill in some of the "don't care" parts of the specification. Consider for instance a circuit with two data outputs a and b specified to switch from low to high concurrently. Let  $a\uparrow$  and  $b\uparrow$  be rising transitions on the voltage signals a and b, and consider that the specification permits these transitions to occur in either order; that is, both  $a\uparrow b\uparrow$  and  $b\uparrow a\uparrow$  are legal behaviors. However, due to relative timing, the implementation might always issue the  $a\uparrow$  transition first, that is,  $b\uparrow a\uparrow$  might never happen. This is a common situation in many real-life systems, but

the "observation equivalence" viewpoint would consider it incorrect, because the behavior  $b\uparrow a\uparrow$  cannot be observed in the implementation. By contrast, unless the specification imposes some fairness constraints, we would consider that this circuit meets this specification. (Fairness constraints can also be specified in our model and in some of the language-oriented models above, simply by ruling out certain infinite executions; see Chapter 6.) This is not to say that CCS cannot be used in other manners to fit our problems or other problems, but just to explain our basic reason for adopting a language-oriented modeling paradigm in spite of the differences from CCS. We demonstrate in applications how our paradigm works. A critique of CCS is beyond the scope of this thesis.

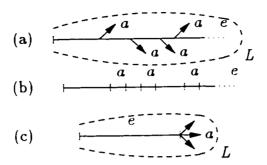

The language-oriented models cited above represent situations where two events occur at the same time by considering that the two events may occur in both orders. although not precisely at the same time: this viewpoint is known as "interleaving semantics". A different paradigm, known as "true concurrency", is offered by models such as [Maz86] that distinguish between two events occurring at the same time and two events that may occur in either order. Although the usual interleaving semantics lose some information regarding causal dependences between events, they are often more tractable than the true concurrency models. For convenience, we adopt interleaving semantics in most of our treatment, but we briefly show in Chapter 7 how a true concurrency viewpoint can also be accommodated in process spaces.

## 1.2.2 Methods for Asynchronous Circuit Verification

Our technique for including relative delay constraints in a metric-free analysis of asynchronous circuits appears to be novel. Previous timing analysis methods for asynchronous circuits from [ACD+92]. [AD94]. [CDYC97]. [LMBSV92]. [MD92].

[Mye95]. or [RM94]. allow one to perform a more detailed analysis than we do here. but they require numerical bounds on individual delays, whereas in our case studies such bounds were not even available. The timing-reliability problems in [KN94] are related to the problem we are studying, but [KN94] focuses on quantitative analysis for known delay constraints, rather than on finding and verifying the constraints. In [BY75] and [BY76], almost-equal-delay models were proposed to analyze a circuit in a metric-free way under the assumption that the gate delays are roughly equal; however, [BY75] and [BY76] do not address our problems because their delay constraints are fixed (always a triangle inequality).

Switch-level analysis methods have been proposed in [BCDM86]. [Bry87]. [BS95]. [KS95]. [KSL95]. and [ZH92]. among others. However, except for [BS95], these methods have focused only on steady-state or synchronous behavior. The technique we propose here aims to complement the methods above and to provide additional flexibility. Our analysis is event-driven, in the sense that it focuses on signal transitions rather than signal levels and does not assume (nor forbid) synchrony or stabilization of voltage signals.

### 1.2.3 Liveness and Progress

The complete trace structures of [Dil89] can be used to capture both liveness and progress properties, and the differences between our general liveness and progress processes and [Dil89] have to do mainly with connectivity restrictions and other technicalities. The models of [Ver94b] also capture some progress and liveness faults, in the form of global deadlock, where everything may stop in a system while some events are demanded. We use related finalization processes that differ from [Ver94b] mainly on connectivity and other technicalities.

On the other hand, our idea of liveness properties implicitly attached to finitary specifications appears to be new. Without challenging the argument of [Bla86] that finitary specifications are insufficiently powerful to capture arbitrary liveness properties, we point out that in many discrete-state systems the liveness properties are not arbitrary, but they are correlated to safety properties, and we demonstrate this on the main example from [Bla86]. In [AS85], an exhaustive characterization of liveness properties has been proposed. However, nothing is said about which of the properties in the class defined by [AS85] should be used for a liveness condition. The models of [LT87] provide more insight in this respect, but their condition for liveness fails to detect certain cases of unfairness [Neg95, p. 30]. The condition for "completeness with respect to specification" in [Ebe91a] prescribes essentially that every specified behavior must have a counterpart in the implementation. This condition does not seem very meaningful for our problems, for reasons similar to those mentioned in regards to process equivalences; besides, many of the liveness and progress faults we study are outside the scope of [Ebe91a].

Our models of default progress processes that capture progress properties implicitly attached to finitary specifications appear to be related to a "finitary fairness" type of assumption recommended in [AH94] and [VK98]. However. [AH94] does not investigate the algebraic properties of finitary fairness specifications. focusing instead on modeling issues and case studies. A notion of 'an implementation satisfies a specification' is given in [VT95], and it is shown in [VK98] that it can capture finitary fairness, but there connectivity restrictions play an important role.

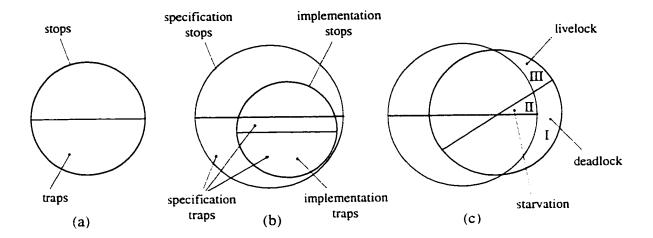

Our general liveness and progress processes induce a formal classification of liveness and progress faults into deadlock, livelock, and starvation. This classification appears to capture common intuition as expressed for instance in certain examples from [Dil89] and [Ver94b]. Although diverse formalizations have been proposed

for deadlock or other lock faults. (see for instance [BS95], [Hoa85], [Sme90], and [Ver94b]), we are not aware of a formal classification related to ours.

#### 1.2.4 Process Abstractions

Most of the theories of concurrency mentioned above incorporate some notion of hiding internal events of a system from an externally visible interface. Also, most of these previous theories have some notion of derivative of a process, representing the behavior of a system after certain events have occurred. However, structural details, such as occurrences of actions, have been given key roles in studying such maps between processes. By contrast, we unify these concepts and investigate them on the basis of abstract executions. Besides, in process spaces we impose no restrictions on actions, and we do not even distinguish between input, output, internal, and external actions: instead, we rely on different effects of such actions on the legality of executions.

Reduced representation of systems is also a natural idea, which has received a lot of attention in previous treatments of concurrency. Using reduced representations, one can verify circuits at lower levels of modeling [KM91], or of larger sizes [CGL92]. The criterion for exact approximation in [CGL92] is related to a particular case of a criterion for independence that we propose: these criteria determine cases where verifications on images of processes through a map are equivalent to direct verifications on the original processes. Also, abstractions have been studied by means of Galois connections in [LGS+95] and [Sif83], and we also give Galois connection properties that correlate orders in different process domains. However, none of the methods above has been aimed towards abstract executions: in fact, [CGL92], [LGS+95], and [Sif83] take an operational viewpoint based on transi-

tion systems. Moreover. [KM91] does not allow for uncertainty of representations because their maps attach exactly one image to each execution or trajectory of a system. Methods that approximate state sets have been used. for instance, in [CDYC97], [DWT95], and [SYP+97], but they are also based on an operational approach.

## 1.3 Notes on Terminology

From our introduction of process spaces in [Neg95], we have changed some inappropriate terms. The 'goal' executions used to be called 'contract' executions, but that label could be confused with the idea of a contract between environment and device, to which we refer frequently. More importantly, 'escape' executions were called 'error' executions. We have changed this term because of possible confusion with the idea of an error state of a computer program or a pocket calculator, that may be reached following illegal inputs: such error states should normally be related to our 'reject' executions rather than to 'escape' executions.

We use double quotes " for citations. and single quotes " for some informal or undefined terms.

Also, we do not include within quotes punctuation from the surrounding text. We follow the advice of P. R. Halmos in [SHSJ73] that "the comma or period should come where the logic of the situation forces it to come", although, as P. R. Halmos also mentions. "There appears to be an international typographical decree that a period or a comma immediately to the right of a quotation is "ugly".".

## Chapter 2

# **Process Spaces**

We introduce process spaces, a formalism that deals with the idea of a contract between a device and its environment in a general manner. Such contracts specify the device-environment interface in terms of allowed executions, but we build our formalism without reference to a particular type or interpretation for executions. Executions can be sequences of events, functions of time, etc., but we consider them to be just elements of an arbitrary set  $\mathcal{E}$ . In fact, we postpone the decision of what the executions are until after determining the algebraic structure of our theory. In this sense, our approach is based on abstract executions. This approach permits the users to choose the levels of complexity and precision of a particular application by varying the amount of detail contained in the executions.

We generalize several operations on processes and notions of correctness that form the core of concurrency theory, such as relative and absolute correctness, parallel composition, and non-deterministic choice. (Process abstractions are discussed in a later chapter, also at a general level, but as a separate development.) We also discuss several algebraic properties of these conditions and operations, as well as

their use for handling processes in a structured manner.

The correctness conditions of process spaces are abstract patterns for particular correctness concerns, such as safety, liveness, progress, and deadlock-freedom. By this, we obtain a unified theory for all particular concerns that can be cast into the general patterns.

Because we make no assumptions about the structure of the elements of  $\mathcal{E}$ . the algebraic structure of process spaces boils down to elementary set calculus on subsets of  $\mathcal{E}$ : this facilitates the proofs of algebraic properties for our processes. In other words, not only do we capture several correctness concerns for the price of one, but also the price we pay is not very high.

The process operations naturally extend to infinite families of processes. Certain process properties can also be taken to the limit, in the sense that they are generalized for infinite families of processes.

The operations and conditions of process spaces are linked by six-way symmetries. We formalize an environment-device symmetry as a duality principle. and also we formulate a ternary symmetry principle based on a 'rotation' transform.

#### 2.1 The Model

Let  $\mathcal E$  be an arbitrary set, whose elements are called executions.

**Definition 2.1** A process over set  $\mathcal{E}$  is a pair (X,Y) of subsets of  $\mathcal{E}$  such that

$$X \cup Y = \mathcal{E} . \tag{2.1}$$

The process space of  $\mathcal{E}$ , denoted by  $\mathcal{S}_{\mathcal{E}}$ , is the set of all processes over  $\mathcal{E}$ .

18

In the remainder of this chapter, we consider all processes to be defined over the same execution set  $\mathcal{E}$ ; we simply say "a process" instead of "a process over  $\mathcal{E}$ ". The set  $\mathcal{E}$ , however, may vary among applications.

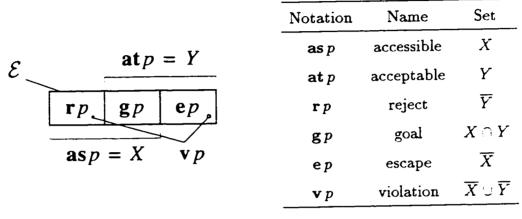

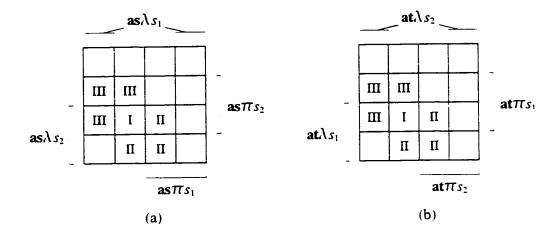

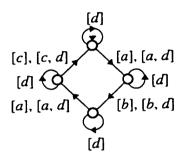

Figure 2.1: Execution sets of a process p = (X, Y).

A process (X,Y) represents a contract between a device and its environment: the device guarantees that only executions from X may occur, whereas the environment guarantees that only executions from Y may occur. Executions from X are called accessible and those from Y are called acceptable—the device can 'access' and 'accept' them, respectively. Thus, a process can be regarded as an assumption/guarantee specification: assuming that only executions from Y may occur, it guarantees that only executions from X may occur.

Our model of processes is closely related to several previous theories of concurrency, mentioned in Section 1.2. The main distinguishing aspect is that our executions are abstract: there are no notions of inputs, outputs, actions, states, or variables involved in a process or its executions. This holds throughout the development of the process space theory in this chapter: many of the operations and properties are similar to usual notions from concurrency theory, and we generalize them for abstract executions. In particular, this generalization requires elimination

of connectivity restrictions from process operations. correctness conditions. and their algebraic properties, by making no references to inputs, outputs, etc. Nevertheless, we show in examples how to use our processes to handle discrete-state systems with states and actions; other interpretations for processes are discussed in later chapters.

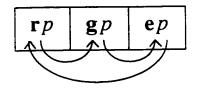

A process (X,Y) partitions  $\mathcal{E}$  into three disjoint subsets, as in Figure 2.1. Executions from  $\overline{Y}$  are called *rejects* and must be avoided by the environment: executions from  $\overline{X}$  are called *escapes* and must be avoided by the device: executions from  $X \cap Y$  are called *goals* and are legal for both device and environment. Executions from  $\overline{X} \cup \overline{Y}$ , called *violations*, are illegal either for the device or the environment. The accessible, acceptable, escape, reject, goal, and violation sets of process p are denoted by as p, at p, e p, r p, g p, v p, respectively.

Equation (2.1). written equivalently  $\overline{X} \cap \overline{Y} = \emptyset$ , formalizes a separation of responsibilities between device and environment: none of the executions needs to be avoided by both device and environment. For this reason, the fourth intersection  $(\overline{X} \cap \overline{Y})$  is absent from the Venn diagram in Figure 2.1.

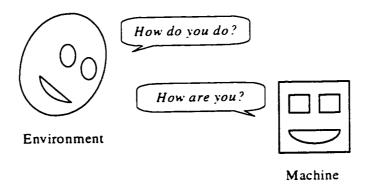

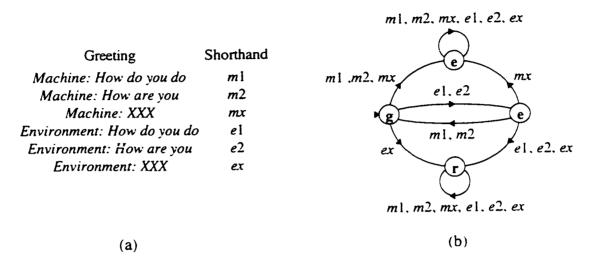

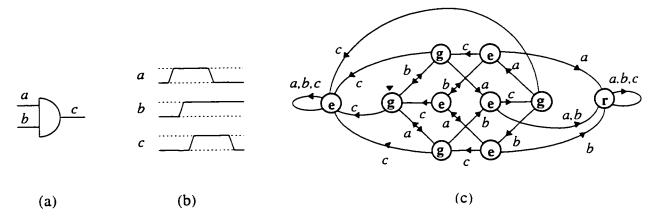

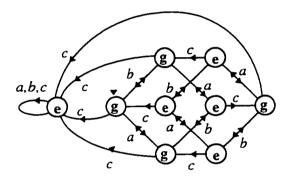

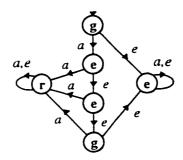

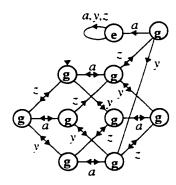

Figure 2.2: Etiquette machine.

Example 2.1 Imagine a simple etiquette machine. Proper etiquette is defined as a conversation containing any number of the phrases "How do you do" and "How are you". The conversation can be arbitrarily long, but finite. However, the available vocabulary includes another phrase. "XXX", that nobody wants to hear. If our machine hears "How do you do" or "How are you", it responds by "How do you do" or "How are you". If it hears "XXX", the machine might become out of order and may produce an arbitrary response or no response at all.

To model this machine in process spaces, we represent conversations as executions, consisting of strings of greetings between the machine and the environment. For instance, (Environment: How are you) (Machine: XXX) (Machine: How are you) is in  $\mathcal{E}$ , but (Environment: How do you do XXX) is not in  $\mathcal{E}$  because "How do you do XXX" is not one of the available greetings. In this example we indicate in each greeting who delivered it, because it does matter who says "XXX", for instance.

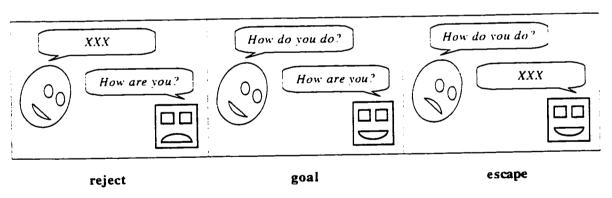

Figure 2.3: Watch your mouth!

Figure 2.3 gives examples of goals, rejects, and escapes for the etiquette machine. In a goal execution, everybody behaves and everybody is content. In a reject execution, the environment behaves improperly and violates the requirements of

the machine, whereas in an escape execution, the machine behaves improperly and violates the requirements of the environment.

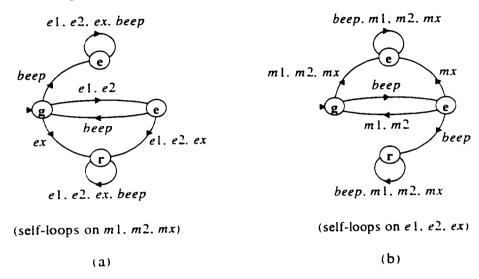

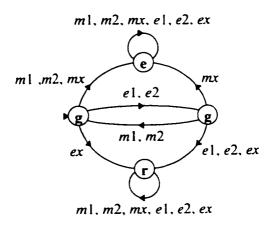

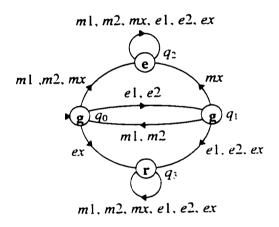

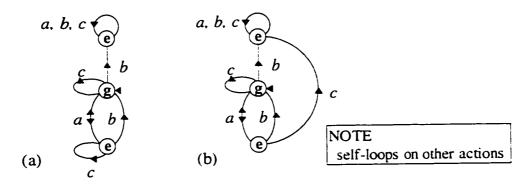

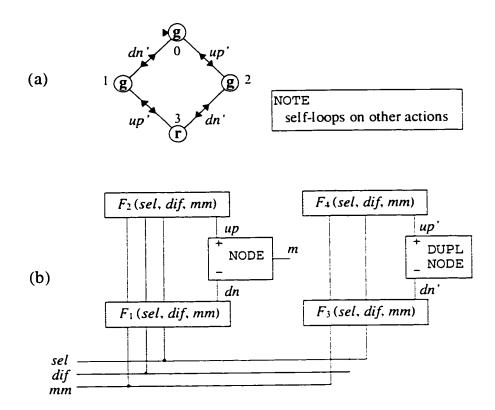

Figure 2.4: Process of the etiquette machine: (a) actions: (b) process.

Figure 2.4 shows in full detail a process for the etiquette machine. as a state machine. The edges are labeled with greetings. To reduce clutter, we use shorthands for the greetings, and we sometimes put several greetings on a single edge. The shorthands are listed in Figure 2.4 (a). The state markings  $\mathbf{r}$ ,  $\mathbf{g}$ , and  $\mathbf{e}$  in Figure 2.4 (b) stand for reject, goal, and escape, respectively. The initial state is marked with an incoming arrowhead. A string of greetings is a reject, goal, or escape for this process if that string is spelled by a path starting at the initial state and ending at a state marked  $\mathbf{r}$ ,  $\mathbf{g}$ , or  $\mathbf{e}$ , respectively. Since every greeting is possible in every state, and thus every string in  $\mathcal{E}$  is on a path starting at the initial state, the rejects, goals, and escapes cover all of  $\mathcal{E}$ . Any conversations are considered possible, because we don't know what the environment or the machine would do. However, we forbid the environment or the machine from doing certain things by qualifying those things as rejects or escapes.

The formal representation requires us to classify every string of greetings. including some which were more or less hand-waved in the informal descriptions above. This way we obtain a formal description of the interface between the etiquette machine and its environment. For instance, (Environment: XXX) (Machine: XXX) is a reject, because the environment violated the contract first: (Machine: How do you do) (Environment: XXX) (Machine: How are you) is an escape, because the machine is not allowed to speak out of turn: (Environment: How do you do) (Environment: How do you do) (Machine: How are you) is a reject, because the environment is not allowed to speak out of turn, either: the empty string is a goal, because neither the environment nor the machine have done anything wrong; and, the execution consisting of just (Environment: How are you) is an escape, because it would be impolite for the machine not to respond to the greeting. Notice that the machine must leave the escape state on the right by a polite greeting in order to reach a goal state.

Note that, in this example, not only do we forbid undesired greetings to occur, but also we force desired greetings to occur by forbidding stopping at certain states. Although these two types of interdictions are of different nature, they both amount to imposing that certain executions be avoided. More complex properties can be specified by the same mechanism if one uses infinite-word executions or other more detailed types of executions.

### 2.2 Correctness Conditions

We use an absolute correctness condition, that a process has all by itself, and a relative correctness condition, by which an 'implementation' process is compared to a 'specification' process.

The property of absolute correctness in process spaces formalizes that a device operates correctly all by itself, that is, the device imposes no requirements upon the environment: in this sense the device is said to be robust. In terms of avoided executions, this property amounts to an empty reject set of the corresponding process, as in the definition below. A symmetric property (albeit not a desirable one) is that a device offers no guarantees to the environment as to which executions are avoided: in this sense the device is said to be chaotic. This amounts to an empty escape set.

Definition 2.2 Process p is robust if

$$\mathbf{r} p = \emptyset$$

.

Process p is chaotic if

$$e p = \emptyset$$

.

The sets of robust and chaotic processes are denoted by  $\mathcal{R}_{\mathcal{E}}$  and  $\mathcal{C}_{\mathcal{E}}$ . respectively.

Example 2.2 The process in Figure 2.4 is not robust. because the executions beginning with (Environment: XXX) are rejects for that process.

The only process that is both robust and chaotic has the accessible and acceptable sets equal to  $\mathcal{E}$ .

**Definition 2.3** The process void, denoted by  $\Phi$ , is  $(\mathcal{E}, \mathcal{E})$ .

Void has no escapes and no rejects; thus it neither offers guarantees nor imposes requirements upon the environment. Its behavior reminds one of vacuum.

The property of relative correctness in process spaces formalizes that a process q is a satisfactory substitute for a process p. For this, q should impose fewer requirements and offer more guarantees than p does. In terms of avoided executions, this means that q has a larger acceptable set and a smaller accessible set.

**Definition 2.4** Process p is refined by process q. written  $p \sqsubseteq q$ . if

$$(\operatorname{at} p \subseteq \operatorname{at} q) \wedge (\operatorname{as} p \supseteq \operatorname{as} q)$$

.

Why is it undesirable to have many accessible executions? If the set of accessible executions is smaller, the behavior of the device is more specified, in the sense that the device has less freedom and obeys tighter constraints.<sup>1</sup>

Figure 2.5: Examples for refinement: (a) repeat machine: (b) quiet machine.

Example 2.3 A 'repeat machine' behaves similarly to the etiquette machine. except that, after a polite greeting by the environment, the repeat machine responds

<sup>&</sup>lt;sup>1</sup>This notion should not be confused with that of 'determinism': we can, for instance, constrain an arbiter device to behave fairly, but for that we use infinite words as executions, in later chapters.

with the same greeting. The process in Figure 2.5 (a) for the repeat machine was obtained from the process in Figure 2.4 (b) by splitting the rightmost state, to remember the particular greeting used by the environment. Now, observe that the repeat machine is not refined by the etiquette machine, since execution  $e1\ m2$  is accessible for the etiquette machine but not for the repeat machine. In other words, the etiquette machine is not a good substitute for the repeat machine, since the etiquette machine might commit a gaffe if the environment is stiff enough to require identical responses.

Example 2.4 A 'quiet machine' imposes upon the environment the same requirements as the original etiquette machine, but does not respond to greetings. The process for such a machine is shown in Figure 2.5 (b). Execution el is accessible because it is legal for the quiet machine to stop after el. However, execution el is not accessible for the etiquette machine. The quiet machine is not a good substitute for the etiquette machine, because of stopping after el: the fault is detected as an extraneous accessible execution.

The repeat machine does refine the etiquette machine, as is easily verified. However, it might be considered unfair to respond always by the same greeting. Such unfairness faults are ignored by the process space over finite strings that we use in this example: still, such faults can be detected by a process space that uses infinite words for executions, as will be discussed in later chapters.

One can also verify that neither the repeat machine nor the etiquette machine refines the quiet machine, and the quiet machine does not refine the repeat machine. We perform such verifications by a tool.

The following property shows that refinement is a partial order.

Proposition 2.1 For processes p. q and r.

(a)

$$p \sqsubseteq p$$

. (reflexivity)

(b)

$$p \sqsubseteq q \land q \sqsubseteq r \Rightarrow p \sqsubseteq r$$

. (transitivity)

(c)

$$p \sqsubseteq q \land q \sqsubseteq p \Rightarrow p = q$$

. (antisymmetry)

**Proof** This follows from Definition 2.4 by reflexivity. transitivity. and antisymmetry of the subset relationship.

Reflexivity and transitivity are common-sense properties that one would expect from a 'worse-than-or-as-good-as' relationship. The antisymmetry property above (Proposition 2.1) concerns the level of abstraction of the model. A model is fully abstract if it makes no irrelevant distinctions among its objects (see for instance [Hen88]), where irrelevance is defined by some equivalence relationship, and distinctions are defined by the formal features of the model. In our case, the objects are processes as constructed in Definition 2.1, and they are distinguished or identified by their execution sets. Irrelevance is with respect to an equivalence relationship derived from the relative correctness condition: two processes are equivalent if they refine each other. Proposition 2.1 (c) determines that process spaces are fully abstract, referring to this equivalence.

The following statement determines that robustness as a predicate on processes is monotonic with respect to refinement.

Proposition 2.2 For processes p and q.

$$p \in \mathcal{R}_{\mathcal{E}} \ \land \ p \sqsubseteq q \ \Rightarrow \ q \in \mathcal{R}_{\mathcal{E}}$$

.

Proof From the hypothesis, we have:

$$\mathcal{E} = \operatorname{at} p \text{ and at } p \subseteq \operatorname{at} q$$

:

thus. at

$$q = \mathcal{E}$$

. meaning that q is robust.

If p is 'correct by itself' and q is 'at least as good as' p, then one would expect q to be 'correct by itself' as well.

The void process gives another connection between robustness and refinement.

Proposition 2.3 For process p.

$$p \in \mathcal{R}_{\mathcal{E}} \Leftrightarrow \Phi \sqsubseteq p$$

.

Proof By the definitions of the refinement relationship and the void process.

$$\Phi \sqsubseteq p \iff \operatorname{as} p \subseteq \mathcal{E} \wedge \operatorname{at} p \supseteq \mathcal{E} .$$

Since as  $p \subseteq \mathcal{E}$  is trivially satisfied. we have

$$\Phi \sqsubseteq p \Leftrightarrow \mathbf{at}\, p \supseteq \mathcal{E} \Leftrightarrow p \in \mathcal{R}_{\mathcal{E}} .$$

In words, p is 'correct by itself' iff p is 'at least as good as' a process that is so indifferent to its environment that can be regarded as 'vacuum'.

Refinement admits the following extremal elements.

**Definition 2.5** The process  $(\emptyset, \mathcal{E})$  is called top and is denoted by  $\top$ . The process  $(\mathcal{E}, \emptyset)$  is called bottom and is denoted by  $\bot$ .

Proposition 2.4 For every process p.

$$\bot \sqsubseteq p \sqsubseteq \top \ .$$

Proof We have

$$\mathbf{as} \perp = \mathcal{E} \supseteq \mathbf{as} p \supseteq \emptyset = \mathbf{as} \top$$

.

$\mathbf{at} \perp = \emptyset \subseteq \mathbf{at} p \subseteq \mathcal{E} = \mathbf{at} \top$ .

Notice that top is robust and bottom is chaotic.

### 2.3 Operations

For dealing with concurrency, it is important to handle a system of interacting processes as a single process that represents their joint behavior. As we shall see, however, there is a difference in whether we consider the devices or the environments of these processes to be interacting. We define two operations for computing joint behaviors: product can be regarded as the law of composition for devices, while exclusive sum can be regarded as the law of composition for environments.

**Definition 2.6** The product of processes p and q is a process  $p \times q$  such that

$$\begin{cases} as (p \times q) = as p \cap as q \\ at (p \times q) = (at p \cap at q) \cup \overline{as p \cap as q} \end{cases}$$

and the exclusive sum of p and q is a process  $p \oplus q$  such that

$$\begin{cases} as (p \oplus q) = (as p \cap as q) \cup \overline{at p \cap at q} \\ at (p \oplus q) = at p \cap at q \end{cases}$$

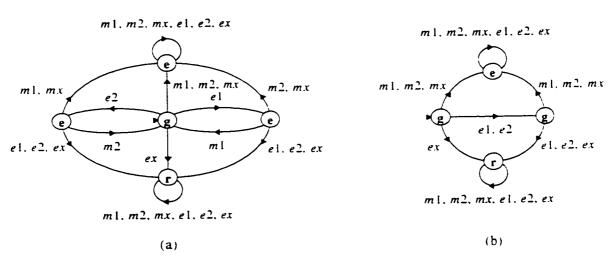

Figure 2.6: The product operation.

To interpret the formal definitions of product and exclusive sum, notice that executions that are accessible to both participating devices are accessible for the system, and executions that are acceptable to both devices are acceptable for the system. However, these two intersections do not cover the entire execution set  $\mathcal{E}$ : the executions marked '!' in Figure 2.6 have not been accounted for so far.

The '!' executions are escapes for one of the operand processes and rejects for the other. They are violations for the resulting system too, but the question is whether they should be escapes or rejects. If we consider devices to be interacting, we take the position that the system device avoids all executions that are avoided by at least one of the component devices. Accordingly, we define the acceptable set of the product by augmenting at  $p \cap$  at q by the executions marked '!'. (Notice that at  $(p \times q) = (at \ p \cap at \ q) \cup (r \ p \cap e \ q) \cup (e \ p \cap r \ q)$ .)

The exclusive sum operation is similar to the product, except that the '!' executions are rejects, rather than escapes, for the exclusive sum process. This way, if an execution is avoided by the environment of either one of the operand processes. that execution is avoided by the environment of the exclusive sum process too.

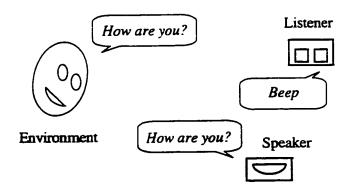

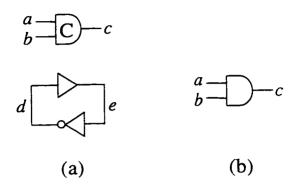

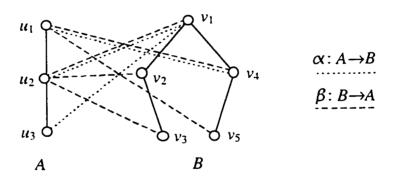

Figure 2.7: Listener and Speaker.

Example 2.5 Consider an etiquette machine which is realized as a system of two parts, call them Listener and Speaker. Listener emits a "beep" each time it hears a greeting from the environment, provided that the greeting is not out of turn and not an "XXX". Speaker delivers a polite greeting each time it hears a "beep".

Figure 2.8: Example for product: (a) Listener: (b) Speaker.

The processes for Listener and Speaker are shown in Figure 2.8. These processes are over the execution set  $\mathcal{E} = \{e1, e2, ex, m1, m2, mx, beep\}^*$ , using the shorthands from Figure 2.4 (a) and a new beep action. These processes are similar to the process in Figure 2.4, except that certain actions have been omitted from the state machines. We normally omit those actions that are ignored by a device, in the sense that they do not change the state of the device. More precisely, at every state there should be self-loops labeled with those actions. For instance, m1, m2, mx are ignored by Listener and are omitted from Figure 2.8 (a): these actions would only produce self-loops at every state of Listener.

Now. let us discuss some of the executions of the product of Listener and Speaker. Execution e2 beep m1 is accessible and acceptable for both Listener and

Speaker, since it leads each of them to a goal state. By the definition of product and Figure 2.6, this execution is acceptable and accessible for the product process as well. Execution el el is accessible and not acceptable for Listener and it is accessible and acceptable for Speaker, since the environment has spoken too fast for Listener, but Speaker has stayed in its initial state, which is a goal state: this execution is accessible and not acceptable for the product process.

An execution corresponding to a square marked '!' in Figure 2.6 is el beep beep: this execution is acceptable and not accessible for Listener and it is accessible and not acceptable for Speaker: thus this execution is acceptable and not accessible for the product process. If a participating device guarantees to avoid a certain execution, the system of devices also guarantees to avoid that execution.

Example 2.6 The omission of actions that produce self-loops at every state permits us to specify the same machine over different execution sets. The process in Figure 2.4 (b) looks the same if the executions can have action beep. One can verify that the process in Figure 2.4 (b) (considered over  $\{e1.\ e2.\ ex.\ m1.\ m2.\ mx.\ beep\}$ ) is refined by the product of Listener and Speaker. As will be discussed in Chapter 3. we perform such verifications by a tool.

Some basic properties of product and exclusive sum are established in the following statement. These operations are idempotent, associative, commutative, and admit the void process as the identity element.

Proposition 2.5 For processes p. q and r, we have:

(a)

$$p \times p = p$$

, (idempotency)

(b)

$$(p \times q) \times r = p \times (q \times r)$$

. (b')  $(p \oplus q) \oplus r = p \oplus (q \oplus r)$ . (associativity)

(c)

$$p \times q = q \times p$$

. (c)  $p \oplus q = q \oplus p$ . (commutativity)

(d)

$$p \times \Phi = p$$

. (identity element)

**Proof sketch** We only consider properties for  $\times$ : those for  $\oplus$  follow by symmetry. as will be discussed later in this chapter.

- (a) By idempotency of  $\cap$ .

- (b) Equality of the accessible sets follows immediately from associativity of  $\cap$ . To show equality of the acceptable sets, we simplify at  $((p \times q) \times r)$  by routine calculations, obtaining:

$$at ((p \times q) \times r)$$

$$= (at p \cap at q \cap at r) \cup \overline{as p \cap as q \cap as r}.$$

Noting that the final form is symmetric in p, q, and r, we also have:

$$(\operatorname{at} p \cap \operatorname{at} q \cap \operatorname{at} r) \cup \overline{\operatorname{as} p \cap \operatorname{as} q \cap \operatorname{as} r}$$

$$= \operatorname{at} ((q \times r) \times p)$$

$$= \operatorname{at} (p \times (q \times r)) . \qquad (\text{by commutativity of } \times (\operatorname{Part} (c) \text{ below}))$$

(c) By commutativity of  $\cap$ .

Informally speaking, the identity element properties above ensure that introducing a void process in a system does not alter the behavior of the system.

A process represents a contract between a device and its environment from the device's point of view; we sometimes need to 'turn the table' by referring to a process that represents the environment's point of view in the same contract.

**Definition 2.7** The reflection of process p is a process -p such that

$$-p = (at p, as p)$$

.

In defining reflection, we simply swap the acceptable and accessible sets of the original process.

Reflection is its own inverse, it inverts refinement, and it swaps  $\mathcal{R}_{\mathcal{E}}$  and  $\mathcal{C}_{\mathcal{E}}$ .

Proposition 2.6 For processes p and q.

- $(a) \quad p = --p.$

- (b)  $p \sqsubseteq q \Leftrightarrow -q \sqsubseteq -p$ .

- (c)  $p \in \mathcal{R}_{\mathcal{E}} \Leftrightarrow -p \in \mathcal{C}_{\mathcal{E}}$ .

**Proof** This follows directly from the definitions of -.  $\sqsubseteq$ .  $\mathcal{R}_{\mathcal{E}}$ . and  $\mathcal{C}_{\mathcal{E}}$ .

Situations where we do not have complete information about the behavior of a device or environment can be regarded as choices between behavior alternatives. Such situations are modeled by two operations on processes: one operation for choice between devices, and the other for choice between environments.

**Definition 2.8** The meet of processes p and q is a process  $p \sqcap q$  such that

$$p \sqcap q = (as p \cup as q. at p \cap at q).$$

and the join of p and q is a process  $p \sqcup q$  such that

$$p \sqcup q = (as p \cap as q, at p \cup at q)$$

.

Given two alternative processes, the meet and join processes can behave like either of the alternatives, and this behavior choice is made for each execution.

Meet models a choice between devices. If an execution is accessible for either of the alternative devices, the meet device will not guarantee to avoid that execution, since we don't know which device was chosen. If an execution is a reject for one of the alternative devices, the meet device will also require its environment to avoid that execution, to forestall the possibility of choosing a device that rejects that execution. Meet can be viewed as an adversary situation. In which we choose the execution and then an adversary chooses a device so as to maximize the possibility of occurrence of faults in a system consisting of the device and its environment.

Dually, join models a non-deterministic choice between environments. The device of  $p \sqcup q$  has an acceptable set just large enough and an accessible set just small enough to accommodate an environment that can choose to behave either like -p or like -q.

Top and bottom have several notable properties.

Proposition 2.7 For process p.

```

(a) p \sqcap \top = p. (a') p \sqcup \bot = p. (identity elements for \sqcap and \sqcup)

```

(b)

$$p \sqcup \top = \top$$

. (b')  $p \sqcap \bot = \bot$ . (dominant elements for  $\sqcup$  and  $\sqcap$ )

(c)

$$p \times \top = \top$$

. (c')  $p \oplus \bot = \bot$ . (dominant elements for  $\times$  and  $\oplus$ )

(d)  $-\top = \bot$ .

Proof This follows directly from the definitions.

<sup>&</sup>lt;sup>2</sup>We thank D. L. Dill for suggesting this interpretation.

Top. a fictitious process, has the miraculous property that all possible flaws in a system of processes are eliminated if top is inserted in that system. Proposition 2.7 (c) indicates that inserting a top process in an arbitrary system will make that system a top too, thus making the system robust.

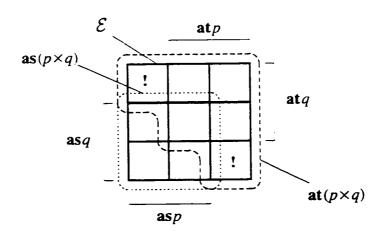

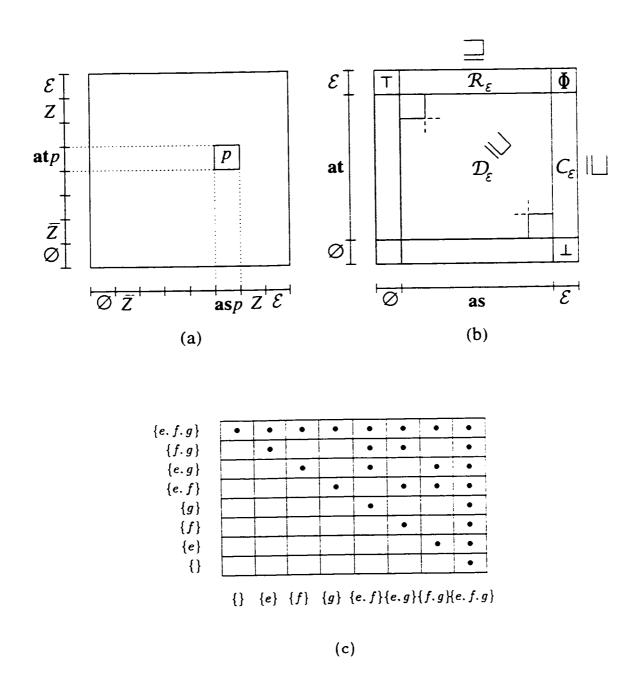

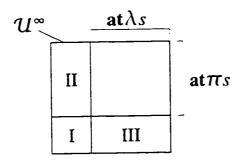

Figure 2.9 gives a pictorial representation for process spaces. Figure 2.9 (a) indicates the conventions for the diagrams in this figure. Figure 2.9 (b) illustrates a general process space with distinguished processes and the refinement relation. and Figure 2.9 (c) illustrates a process space over a three-element execution set.

In these diagrams, the subsets of  $\mathcal{E}$  are represented by disjoint segments on the coordinate axes. Every subset has two segments, one on each axis, equidistant from the origin: notice the positions of Z on the two axes in Figure 2.9 (a). Complementary subsets are represented by segments equidistant from the middle of an axis: notice the segments for  $\overline{Z}$  and Z in Figure 2.9 (a). Each pair of subsets of  $\mathcal{E}$  is represented by a square whose projections on the axes are the segments of the subsets in the pair: notice the positions of p, as p, and at p in Figure 2.9 (a).

With these conventions, a process space  $\mathcal{S}_{\mathcal{E}}$  is represented in Figure 2.9 (b):  $\mathcal{S}_{\mathcal{E}}$  contains none of the pairs in the heavily shaded area, some of the pairs in the lightly shaded area, and all the pairs in the delimited blank area of Figure 2.9 (b). The upper and right borders in Figure 2.9 (b) are the sets of robust and chaotic processes, denoted by  $\mathcal{R}_{\mathcal{E}}$  and  $\mathcal{C}_{\mathcal{E}}$ , respectively, since the processes on the upper border have the set of acceptable executions equal to  $\mathcal{E}$ , and the processes on the right border have the set of accessible processes equal to  $\mathcal{E}$ . The set  $\mathcal{D}_{\mathcal{E}}$  contains the pairs of the form  $(Z, \overline{Z})$ , called diagonal processes (just because of their position). The  $\sqsubseteq$  signs indicate the direction of the refinement order on sets  $\mathcal{R}_{\mathcal{E}}$ .  $\mathcal{C}_{\mathcal{E}}$  and  $\mathcal{D}_{\mathcal{E}}$ .

Figure 2.9: Charting a process space: (a) drawing convention: (b) chart: (c) process space over  $\{e, f, g\}$ .

Figure 2.9 (c) represents  $S_{\{e,f,g\}}$  by the conventions above. Notice that there are 27 processes in this process space: in general, the cardinality of a finite process space is  $3^{|\mathcal{E}|}$ , where  $\mathcal{E}$  is the execution set, also finite.<sup>3</sup> This is because each process assigns one of three designations (reject, goal, escape) to each execution in  $\mathcal{E}$ .

Throughout our presentation of process spaces, we have mentioned symmetries between environment and device. We formalize these symmetries as follows.

Proposition 2.8 (de Morgan's laws) For processes p and q.

(a)

$$-(p \times q) = -p \oplus -q$$

. (a')  $-(p \oplus q) = -p \times -q$ .

(b)

$$-(p \sqcap q) = -p \sqcup -q$$

. (b')  $-(p \sqcup q) = -p \sqcap -q$ .

**Proof** This follows immediately from the definitions of the process space operators involved.

Together. Propositions 2.6 and 2.8 essentially say that reflection is an isomorphism of process spaces. On the basis of these statements, we formulate a duality principle for process spaces.

Remark (duality) Let S be a statement about process spaces. The dual of S is a statement  $S^{\partial}$  obtained by replacing in S every occurrence of  $\sqsubseteq$  by  $\beth$ , of  $\sqcup$  by  $\sqcap$ , of  $\times$  by  $\oplus$ , of  $\mathcal{R}_{\mathcal{E}}$  by  $\mathcal{C}_{\mathcal{E}}$ , of as by at, of  $\mathbf{r}$  by  $\mathbf{e}$ , and vice versa. ( $\Phi$ , -,  $\mathbf{g}$ ,  $\mathbf{v}$ ,  $\mathcal{E}$ ,  $\mathcal{S}_{\mathcal{E}}$ , and  $\mathcal{D}_{\mathcal{E}}$  are their own duals.) Notice that  $S^{\partial\partial} = S$ . If statement S holds, then  $S^{\partial}$  holds, too.

In fact, the meet and join operations endow process spaces with a lattice structure, as will be discussed later.

<sup>&</sup>lt;sup>3</sup>We thank J. A. Brzozowski for these observations.

### 2.4 Manipulation of Processes

The complexity of manipulating processes grows very rapidly with the sizes of their representations. Therefore, a key idea is to divide a problem into parts, treat the parts separately, and combine the results. We discuss several algebraic properties that support such approaches.

Theorem 2.9 (monotonicity) For processes p. q. and r.

$$p \sqsubseteq q \Rightarrow p \times r \sqsubseteq q \times r .$$

Proof First, we show inclusion of the accessible sets.

$$as (p \times r) \supseteq as (q \times r)$$

$$\Rightarrow as p \cap as r \supseteq as q \cap as r$$

$$\Rightarrow \overline{(as p \cap as r)} \cap (as q \cap as r) = \emptyset$$

$$\Rightarrow (\overline{as p} \cup \overline{as r}) \cap (as q \cap as r) = \emptyset$$

$$\Rightarrow (\overline{as p} \cap as q \cap as r) \cup (\overline{as r} \cap as q \cap as r) = \emptyset$$

$$\Rightarrow \overline{as p} \cap as q \cap as r = \emptyset$$