# Concurrent Error Detection in Finite Field Arithmetic Operations

by

Siavash Bayat-Sarmadi

A thesis

presented to the University of Waterloo in fulfilment of the thesis requirement for the degree of Doctor of Philosophy

in

Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2007

©Siavash Bayat-Sarmadi 2007

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

### Abstract

With significant advances in wired and wireless technologies and also increased shrinking in the size of VLSI circuits, many devices have become very large because they need to contain several large units. This large number of gates and in turn large number of transistors causes the devices to be more prone to faults. These faults specially in sensitive and critical applications may cause serious failures and hence should be avoided.

On the other hand, some critical applications such as cryptosystems may also be prone to deliberately injected faults by malicious attackers. Some of these faults can produce erroneous results that can reveal some important secret information of the cryptosystems. Furthermore, yield factor improvement is always an important issue in VLSI design and fabrication processes. Digital systems such as cryptosystems and digital signal processors usually contain finite field operations. Therefore, error detection and correction of such operations have become an important issue recently.

In most of the work reported so far, error detection and correction are applied using redundancies in space (hardware), time, and/or information (coding theory). In this work, schemes based on these redundancies are presented to detect errors in important *finite field* arithmetic operations resulting from hardware faults. Finite fields are used in a number of practical cryptosystems and channel encoders/decoders. The schemes presented here can detect errors in arithmetic operations of finite fields represented in different bases, including polynomial, dual and/or normal basis, and implemented in various architectures, including bit-serial, bit-parallel and/or systolic arrays.

### Acknowledgements

I would like to express sincere gratitude to Professor M. A. Hasan for his supervision and guidance throughout the course of my graduate studies.

The insightful review of this work by the thesis examiners, Professor Israel Korn, Professor Alfred Menezes, Professor Gord Agnew and Professor Guang Gong is also greatly appreciated.

I also would like to thank Dr. Miguel F. Anjos for letting me run part of the simulations of this work on his computer. I was also grateful for being able to use some of the computing facilities of the Shared Hierarchical Academic Research Computing Network (SHARCNET:www.sharcnet.ca).

I would like to acknowledge my family, mainly my parents, for their endless moral support and encouragement.

My special thanks goes to my beloved wife, Zohreh Mesbah-Moosavi, for her help and patience in the process of this work, without which I would not have succeeded.

## Dedication

To my beloved wife, Zohreh.

To my dear parents, Azam and Hormoz.

# Contents

| 1        | Intr | roduction                           | 1  |

|----------|------|-------------------------------------|----|

|          | 1.1  | Motivation                          | 1  |

|          | 1.2  | Scope of this Work                  | 4  |

|          | 1.3  | Thesis Outline                      | 5  |

|          | 1.4  | Research Contributions              | 7  |

| <b>2</b> | Bac  | kground                             | 9  |

|          | 2.1  | Finite Fields                       | 9  |

|          | 2.2  | Field Arithmetic Operations         | 14 |

|          |      | 2.2.1 Multiplication over $GF(2^m)$ | 15 |

|          |      | 2.2.2 Inversion over $GF(2^m)$      | 19 |

|          | 2.3  | Fault Tolerant Systems              | 21 |

|          |      | 2.3.1 Faults                        | 21 |

|          |      | 2.3.2 Fault Tolerant Techniques     | 23 |

|          |      | 2.3.3 Information Redundancy        | 23 |

| 3        | Con  | ncurrent Error Detection Using RESO | 27 |

|          | 3.1  | RESO Method                         | 28 |

|          | 3 2  | Concurrent Error Detection Strategy | 20 |

|   |      | 3.2.1   | CED for Polynomial Basis (PB) Arithmetic Operations    | 30 |

|---|------|---------|--------------------------------------------------------|----|

|   |      | 3.2.2   | CED for Dual Basis (DB) Arithmetic Operations          | 33 |

|   |      | 3.2.3   | CED for Normal Basis (NB) Arithmetic Operations        | 35 |

|   | 3.3  | Pipeli  | ne Architecture and Overhead Analysis                  | 36 |

|   |      | 3.3.1   | Overheads in PB Operations                             | 38 |

|   |      | 3.3.2   | Overheads in DB Operations                             | 39 |

|   |      | 3.3.3   | Overheads in NB Operations                             | 39 |

|   | 3.4  | A Clo   | ser Look at PB, DB and NB Multipliers with CED         | 41 |

|   |      | 3.4.1   | A Systolic PB Multiplier with CED                      | 41 |

|   |      | 3.4.2   | A Systolic DB Multiplier with CED                      | 45 |

|   |      | 3.4.3   | A Systolic NB Multiplier with CED                      | 48 |

|   |      | 3.4.4   | Some Notes About Delays of Cells and Equality Checkers | 58 |

|   | 3.5  | Error   | Detection Capability                                   | 62 |

|   | 3.6  | Concu   | arrent Error Correction                                | 66 |

|   | 3.7  | Summ    | nary                                                   | 68 |

| 4 | Sing | gle Inp | out Multiple Parity Scheme for PB Multipliers          | 69 |

|   | 4.1  | Concu   | arrent Error Detection Strategy                        | 71 |

|   |      | 4.1.1   | Multiple Parity Prediction in SR Module                | 73 |

|   |      | 4.1.2   | Parity Prediction in SM and VA Modules                 | 77 |

|   |      | 4.1.3   | Parity Checking Circuit                                | 78 |

|   |      | 4.1.4   | Polynomial Basis Multiplier with CED                   | 79 |

|   | 4.2  | Error   | Detection Capability                                   | 80 |

|   |      | 4.2.1   | Error Modelling                                        | 80 |

|   |      | 4.2.2   | Probability of Error Detection                         | 82 |

|   |      | 4.2.3   | Frequency of the Check Points                          | 84 |

|   | 4.3  | Result | ts                                               | 86  |

|---|------|--------|--------------------------------------------------|-----|

|   |      | 4.3.1  | Simulation-Based Fault Injection                 | 86  |

|   |      | 4.3.2  | Time and Area Overheads                          | 88  |

|   | 4.4  | Altern | native Partitioning                              | 95  |

|   |      | 4.4.1  | Structure of SR Module                           | 97  |

|   |      | 4.4.2  | Comparison of SR-P Modules                       | 100 |

|   | 4.5  | Summ   | nary                                             | 101 |

| 5 | Ext  | ending | g SIMP                                           | 102 |

|   | 5.1  | Doubl  | le Input Multiple Parity (DIMP) Scheme           | 103 |

|   |      | 5.1.1  | Parity Prediction in DIMP                        | 104 |

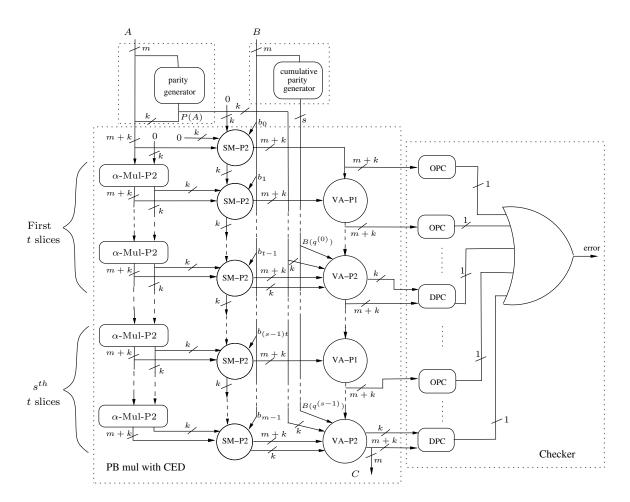

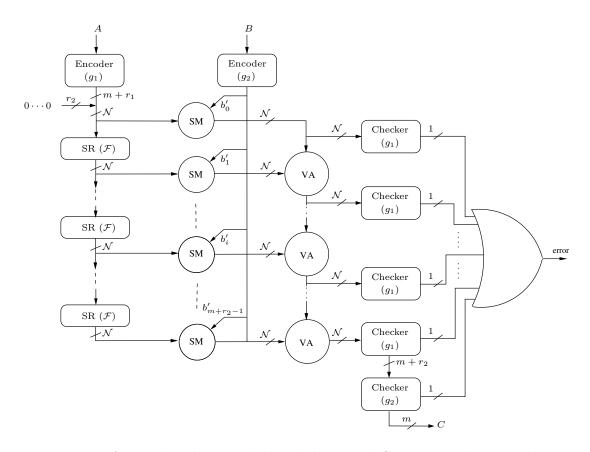

|   |      | 5.1.2  | Polynomial Basis Multipliers with CED Using DIMP | 108 |

|   |      | 5.1.3  | CED Capability of DIMP                           | 110 |

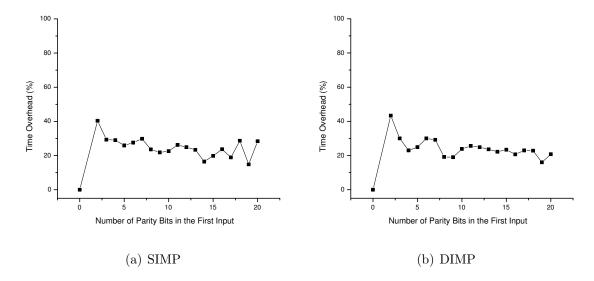

|   | 5.2  | Exper  | rimental Results                                 | 112 |

|   |      | 5.2.1  | Simulation-Based Fault Injection                 | 112 |

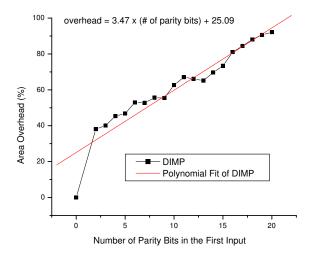

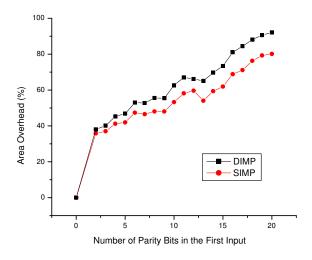

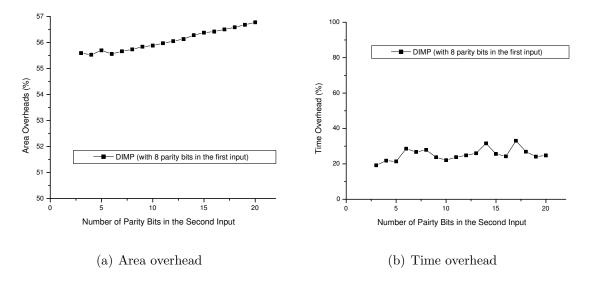

|   |      | 5.2.2  | Analysis of Time and Area Overheads              | 115 |

|   | 5.3  | Exten  | ding SIMP and DIMP to Dual and Normal Bases      | 120 |

|   |      | 5.3.1  | SIMP and DIMP in Dual Basis                      | 120 |

|   |      | 5.3.2  | SIMP and DIMP in Type I Normal Basis             | 125 |

|   |      | 5.3.3  | SIMP and DIMP in Type II Normal Basis            | 128 |

|   | 5.4  | Summ   | nary                                             | 132 |

| 6 | Line | ear Co | ode Based Error Detection Schemes                | 134 |

|   | 6.1  | A Cla  | ss of Linear Codes: $\mathcal{L}$ Code           | 135 |

|   | 6.2  | Concu  | urrent Error Detection Schemes                   | 136 |

|   | 6.3  | SIE B  | ased Error Detectable Multipliers                | 137 |

|   |      | 6.3.1  | SM and VA Modules                                | 138 |

|             |     | 6.3.2   | SR Module                                                            | 138 |

|-------------|-----|---------|----------------------------------------------------------------------|-----|

|             |     | 6.3.3   | Bit-serial and Bit-parallel Polynomial Basis Multipliers $\ . \ .$ . | 140 |

|             |     | 6.3.4   | ${\cal L}$ Code Encoders and Checkers                                | 141 |

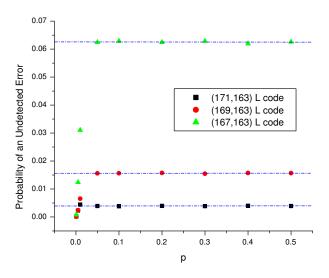

|             | 6.4 | Error   | Detection Capability                                                 | 142 |

|             |     | 6.4.1   | Error Modelling                                                      | 142 |

|             |     | 6.4.2   | Probability of an Undetected Error                                   | 143 |

|             |     | 6.4.3   | Frequency of Check Points                                            | 145 |

|             | 6.5 | Double  | e-Input Encoding (DIE)                                               | 145 |

|             |     | 6.5.1   | Polynomial Basis Multipliers with CED Capability $\dots$             | 146 |

|             |     | 6.5.2   | Error Detection Using DIE                                            | 146 |

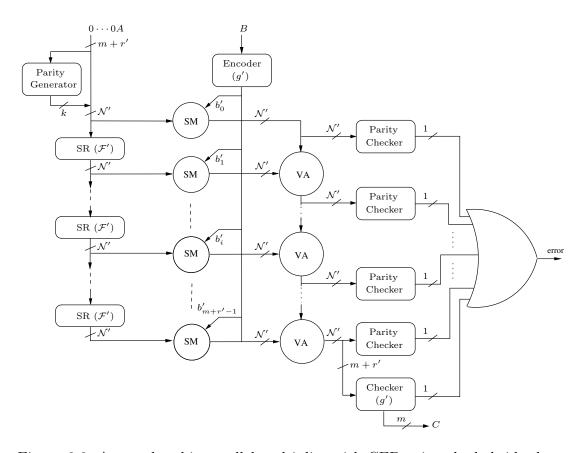

|             | 6.6 | Hybrid  | d Scheme                                                             | 148 |

|             |     | 6.6.1   | Polynomial Basis Multipliers with CED Capability                     | 148 |

|             |     | 6.6.2   | Error Detection Using Hybrid Scheme                                  | 150 |

|             | 6.7 | Simula  | ation-Based Fault Injection                                          | 151 |

|             |     | 6.7.1   | Single Stuck-at Fault Injection                                      | 152 |

|             |     | 6.7.2   | Multiple Stuck-at Fault Injection                                    | 153 |

|             | 6.8 | Analys  | sis of Time and Area Overheads                                       | 153 |

|             | 6.9 | Summ    | ary                                                                  | 155 |

| 7           | Con | clusio  | ns and Future Work                                                   | 157 |

|             | 7.1 | Summ    | ary and Conclusions                                                  | 157 |

|             | 7.2 | Future  | e Work                                                               | 159 |

| ٨           | Sim | ulatiar | n-Based Fault Injection                                              | 161 |

| <b>-1</b> . |     |         | ·                                                                    |     |

|             | A.1 |         | Injection in Information Redundancy Based Schemes                    |     |

|             | A 2 | Haiiit. | Injection in RESO Based Schemes                                      | 164 |

Bibliography 167

# List of Tables

| 2.1 | Open fault table                                                        | 22 |

|-----|-------------------------------------------------------------------------|----|

| 2.2 | Stuck-at fault table                                                    | 22 |

| 3.1 | The time overheads for the different pipelined architectures            | 38 |

| 3.2 | The area overheads of PB, DB and NB arithmetic operations with          |    |

|     | the proposed CED $\dots$                                                | 41 |

| 3.3 | Space and time complexities of the semi-systolic PB multiplier          | 44 |

| 3.4 | Space and time complexities of a number of systolic or semi-systolic    |    |

|     | PB multipliers                                                          | 46 |

| 3.5 | Space and time complexities of a number of systolic or semi-systolic    |    |

|     | DB multipliers                                                          | 49 |

| 3.6 | Space and time complexities of a number of systolic or semi-systolic    |    |

|     | ONB multipliers                                                         | 59 |

| 3.7 | Percentage of error detection of the RESO based scheme for finite       |    |

|     | field multipliers against single stuck-at faults                        | 64 |

| 4.1 | Percentage of error detection of the SIMP scheme for a $GF(2^{163})$ PB |    |

|     | multiplier against stuck-at faults                                      | 87 |

| 4.2 | Nonzero time overheads for bit-serial implementation which belong       |    |

|     | to the $GF(2^{163})$ PB multiplier                                      | 91 |

| 4.3 | FPGA area consumption for a bit-parallel $GF(2^{163})$ PB multiplier.                             | 94  |

|-----|---------------------------------------------------------------------------------------------------|-----|

| 4.4 | XOR counts for PPC of an SR module for NIST recommended irre-                                     |     |

|     | ducible polynomials for ECDSA application                                                         | 100 |

| 5.1 | Single stuck-at fault injection in a slice of a bit-parallel $GF(2^{163})$ PB                     |     |

|     | $\   \text{multiplier}  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  $ | 113 |

| 5.2 | Multiple stuck-at fault injection in a slice of a bit-parallel $GF(2^{163})$                      |     |

|     | PB multiplier                                                                                     | 115 |

| 5.3 | Injection of low weight multiple stuck-at faults in a slice of a bit-                             |     |

|     | parallel $GF(2^{163})$ PB multiplier                                                              | 115 |

| 5.4 | FPGA area consumption for a bit-parallel $GF(2^{163})$ PB multiplier .                            | 117 |

| 5.5 | The number of 2-input gates needed for the bit-parallel ONB2 mul-                                 |     |

|     | tiplier                                                                                           | 129 |

| 6.1 | Single stuck-at fault injection in a slice of a bit-parallel $GF(2^{163})$ PB                     |     |

|     | $\   \text{multiplier}  . \ . \ . \ . \ . \ . \ . \ . \ . \ .$                                    | 152 |

| 6.2 | Multiple stuck-at fault injection in a slice of a bit-parallel $GF(2^{163})$                      |     |

|     | PB multiplier                                                                                     | 153 |

| 6.3 | The time and the area overheads for the bit-serial implementations                                |     |

|     | of the SIE, the DIE and the hybrid schemes $\ \ldots \ \ldots \ \ldots$                           | 154 |

| 6.4 | The time and the area overheads for the bit-parallel implementations                              |     |

|     | of the SIE, the DIE and the hybrid schemes $\ \ldots \ \ldots \ \ldots \ \ldots$                  | 155 |

| 7.1 | Comparison of the SIMP, DIMP, SIE, DIE and hybrid schemes                                         | 159 |

# List of Figures

| 2.1  | SR module                                                              | 17 |

|------|------------------------------------------------------------------------|----|

| 2.2  | Low-to-high bit-serial multiplication                                  | 18 |

| 2.3  | Bit-parallel multiplication                                            | 19 |

| 2.4  | Open fault example                                                     | 21 |

| 2.5  | Stuck-at fault example                                                 | 22 |

| 3.1  | General architecture for the arithmetic operations with CED            | 30 |

| 3.2  | General pipelined architecture of an arithmetic operation with the     |    |

|      | proposed CED                                                           | 37 |

| 3.3  | (a) Scaling and (b) inverse scaling in PB operations                   | 38 |

| 3.4  | (a) Scaling and (b) inverse scaling in DB operations                   | 40 |

| 3.5  | (a) Squaring and (b) taking the square root in NB operations           | 40 |

| 3.6  | General cell architecture for a semi-systolic PB mutliplier            | 43 |

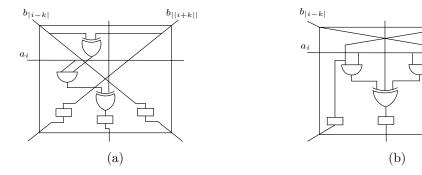

| 3.7  | (a) Type 1 cell and (b) type 2 cell of a semi-systolic PB multiplier . | 43 |

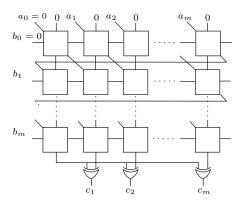

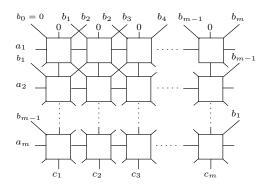

| 3.8  | A semi-systolic PB mutliplier                                          | 44 |

| 3.9  | (a) Type 1 cell and (b) type 2 cell of a semi-systolic DB multiplier . | 47 |

| 3.10 | A semi-systolic DB multiplier                                          | 48 |

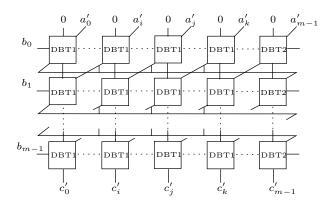

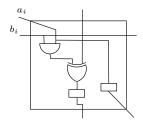

| 3.11 | The cell of a semi-systolic ONB1 multiplier                            | 52 |

| 3.12 | A semi-systolic ONB1 multiplier                                        | 52 |

| 3.13 | A semi-systolic ONB1 multiplier with $m$ rows                                       | 53 |

|------|-------------------------------------------------------------------------------------|----|

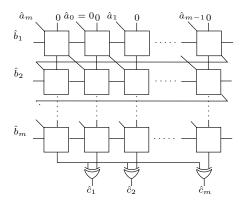

| 3.14 | Two cells of a semi-systolic ONB2 multiplier with same functionality                | 57 |

| 3.15 | A semi-systolic ONB2 multiplier                                                     | 58 |

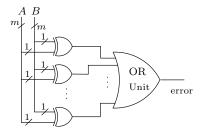

| 3.16 | An $m$ -bit equality checker                                                        | 60 |

| 3.17 | The propagation delays for different ways of implementing an $m$ -                  |    |

|      | input OR unit                                                                       | 61 |

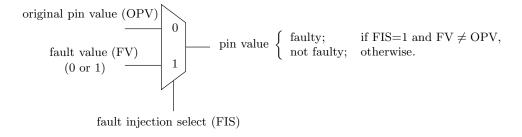

| 3.18 | Conventional fault injection at a gate pin                                          | 63 |

| 3.19 | General architecture for the arithmetic operations with CEC (using                  |    |

|      | a 2-of-3 system)                                                                    | 67 |

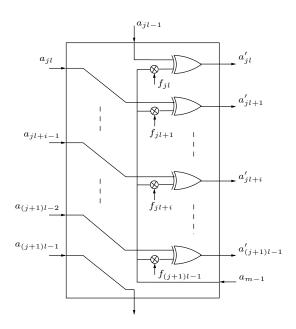

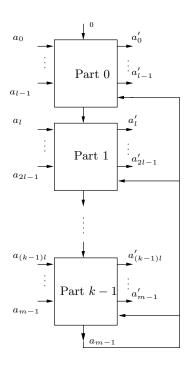

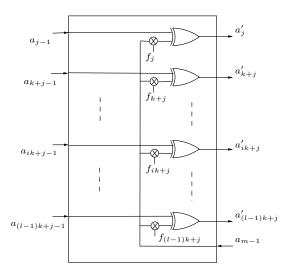

| 4.1  | The $j^{th}$ part of the SR module                                                  | 75 |

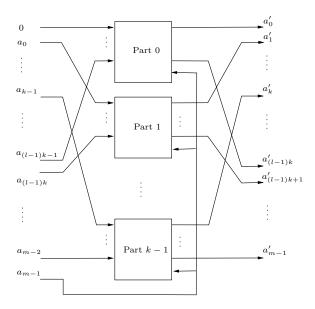

| 4.2  | SR module                                                                           | 76 |

| 4.3  | Parity prediction circuit of the $j^{th}$ part of the SR module                     | 76 |

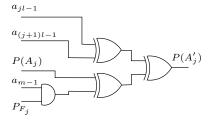

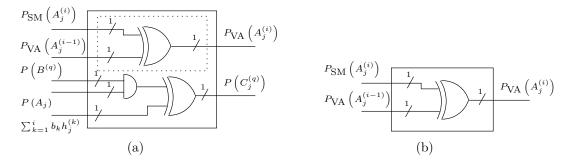

| 4.4  | PPC for a) SM module and b) VA module                                               | 78 |

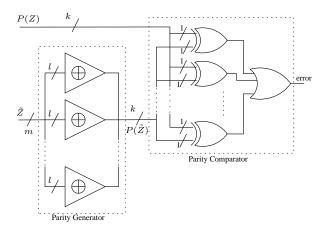

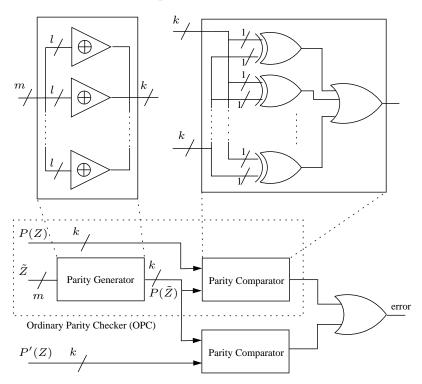

| 4.5  | Multiple-bit parity checker                                                         | 78 |

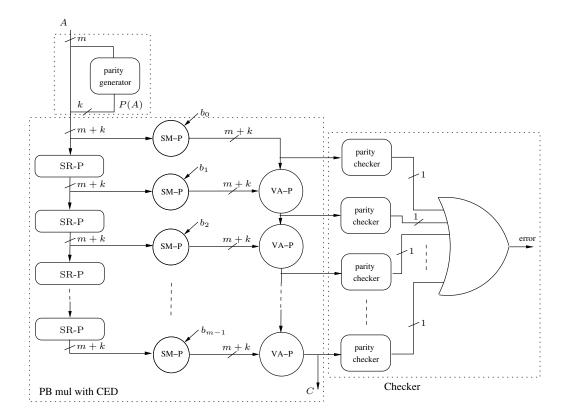

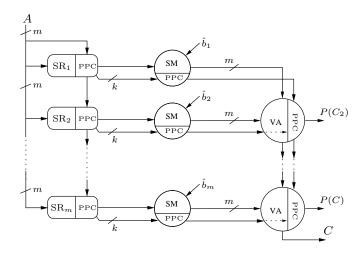

| 4.6  | Bit-serial polynomial basis multipliers with parity prediction circuit              | 79 |

| 4.7  | Bit-parallel polynomial basis multipliers with parity prediction circuit ${\cal P}$ | 80 |

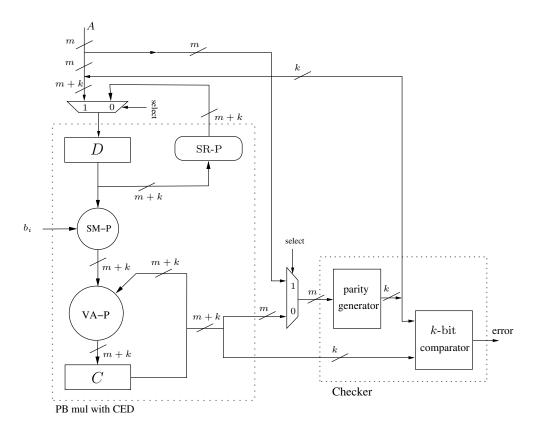

| 4.8  | A complete bit-serial multiplier with CED                                           | 89 |

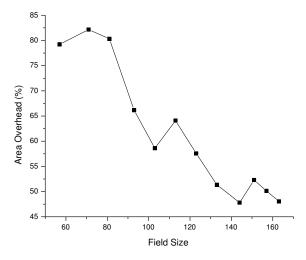

| 4.9  | Area (i.e., slice) overhead for bit-serial PB multipliers for different             |    |

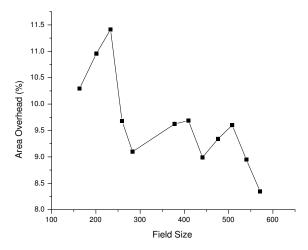

|      | size of fields                                                                      | 90 |

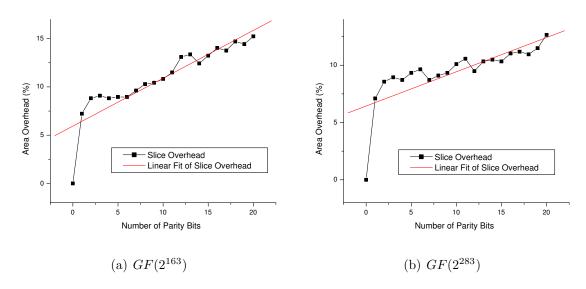

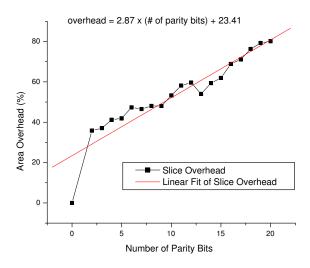

| 4.10 | Area overhead vs. parity-bit number                                                 | 91 |

| 4.11 | A complete bit-parallel multiplier with CED                                         | 92 |

| 4.12 | Area (i.e., slice) overhead for bit-parallel PB multipliers for different           |    |

|      | size of fields                                                                      | 93 |

| 4.13 | Area overhead vs. parity-bit number for the field $GF(2^{163})$                     | 94 |

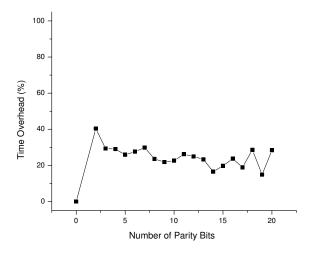

| 4.14 | Time overhead vs. parity-bit number for the field $GF(2^{163})$                     | 95 |

| 4.15 | The $j^{th}$ part of the SR module using the vertical partitioning                  | 98 |

| 4.16 | SR module                                                                         | 99  |

|------|-----------------------------------------------------------------------------------|-----|

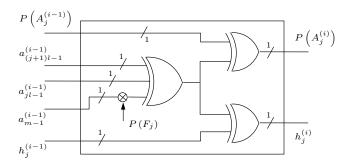

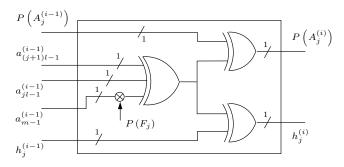

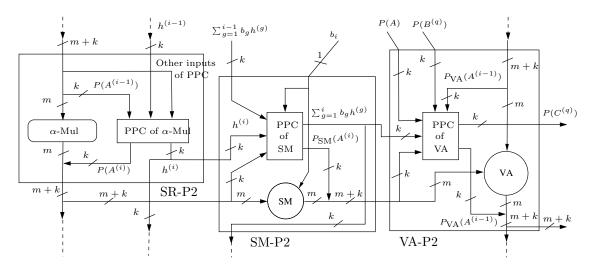

| 5.1  | PPC of the $j^{th}$ part of an SR module                                          | 107 |

| 5.2  | PPC of the $j^{th}$ part of an SM module                                          | 107 |

| 5.3  | PPC of the $j^{th}$ part of VA for (a) every $t^{th}$ slice, (b) all other slices | 108 |

| 5.4  | One of every $t^{th}$ slices of the PB multiplier with CED                        | 108 |

| 5.5  | Double parity checker (DPC)                                                       | 109 |

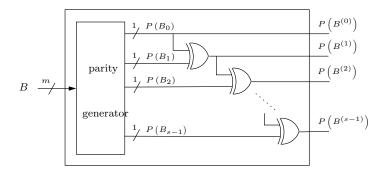

| 5.6  | Cumulative parity generator                                                       | 110 |

| 5.7  | Possible fault locations in $b_i$ input of the SM module                          | 114 |

| 5.8  | A complete bit-parallel multiplier with CED                                       | 116 |

| 5.9  | Area overhead of DIMP vs. parity-bit number for the field $GF(2^{163})$           | 118 |

| 5.10 | Area overhead DIMP vs. SIMP for the field $GF(2^{163})$                           | 119 |

| 5.11 | Time overhead vs. parity-bit number for the field $GF(2^{163})$                   | 120 |

| 5.12 | Area and time overheads of DIMP vs. parity-bit number of the                      |     |

|      | second input for the field $GF(2^{163})$                                          | 121 |

| 5.13 | A slice of a bit-parallel DB multiplier                                           | 122 |

| 5.14 | A slice of a bit-parallel ONB1 multiplier                                         | 126 |

| 5.15 | A bit-parallel ONB2 multiplier                                                    | 129 |

| 5.16 | Parity prediction strategy for SIMP in ONB2                                       | 131 |

| 6.1  | SR module: (a) with unencoded input, SR depends on $f(x)$ , (b) with              |     |

|      | encoded input, SR depends on $F(x)$                                               | 139 |

| 6.2  | SR module with encoded input                                                      | 140 |

| 6.3  | Polynomial-basis multiplication                                                   | 141 |

| 6.4  | Probability of an undetected error vs. $p$                                        | 144 |

| 6.5  | A complete bit-parallel multiplier with CED using the DIE scheme                  | 147 |

| 6.6  | A complete bit-parallel multiplier with CED using the hybrid scheme               | 150 |

### List of Abbreviations

AOP All-Ones Polynomial.

CED Concurrent Error Detection.

CEC Concurrent Error Correction.

DB Dual Basis.

DIE Double Input Encoding.

DIMP Double Input Multiple Parity.

DMR Dual Modular Redundancy.

DPC Double Parity Checker.

ECDSA Elliptic Curve Digital Signature Algorithm.

FIS Fault Injection Select.

FPGA Field Programmable Gate Arrays.

FV Fault Value.

GF Galois Field.

NB Normal Basis.

NIST National Institute of Standards and Technology.

NMOS N-type Metal Oxide Semiconductor.

ONB1 Type I Optimal Normal Basis.

ONB2 Type II Optimal Normal Basis.

OPC Ordinary Parity Checker.

OPV Original Pin Value.

PB Polynomial Basis.

PMOS P-type Metal Oxide Semiconductor.

PPC Parity Prediction Circuit.

$P_{r_D}$  Probability of Error Detection.

$P_{r_U}$  Probability of an Undetected Error.

RESO REcomputing with Shifted Operands.

SIE Single Input Encoding.

SIMP Single Input Multiple Parity.

SM Scalar Multiplication.

SR Shift-and-Reduce.

VA Vector Addition.

VHDL VHSIC hardware description language.

VHSIC Very-High-Speed Integrated Circuits.

VLSI Very Large Scale Integration.

# Chapter 1

### Introduction

### 1.1 Motivation

"A fault-tolerant system is one that can continue the correct performance of its specified tasks in the presence of hardware and/or software faults. Fault detection is the process of recognizing that a fault has occurred. Fault detection is often required before any recovery procedure can be implemented" [51].

Recently a number of schemes have been developed for the detection and/or correction of errors in hardware implementation of some arithmetic operations [24, 55–57], which have applications in cryptography [9, 10, 14–16, 20, 32–36, 68, 69], deep space channel coding [66], VLSI testing [52]. The main reasons for increased interest in such schemes are as follows:

• Having correct functionality in the presence of faults: Digital systems that require large number of circuits for their implementation can be more prone to produce erroneous results simply because of the increase in the probability that one of the circuits may become faulty while in use. As a result, for

1.1 Motivation 2

sensitive or critical applications large digital systems are generally designed with some kind of mechanism to provide correct functionality or to detect errors.

• Avoiding fault-based attacks [13, 29, 63]: Fault attacks are based on injecting some faults into a cryptosystem and observing any leak of secret information. Boneh et al. presented the first fault-based attack [15, 16]. Their attack has been applied to some public key cryptosystems such as RSA and the Rabin signature scheme. Since RSA is usually implemented using the Chinese Remainder theorem (CRT), having one correct signature and one faulty signature of the same message can lead to the modulus factorization. In [11], Biham and Shamir presented a fault-based side channel cryptanalysis of DES. They recovered the last round key by less than 200 cipher texts and then they found the round key of the second-last round and so on. They extended their work to show that it could uncover the structure of an unknown cryptosystem in a smart card. Anderson and Kuhn [3] introduced some other fault based attacks using fault injection into instruction memory of a smart card and by overwriting specific memory locations of a smart card.

One technique to detect errors in hardware implementation is on-line testing or concurrent error detection (CED). CED is used to concurrently test a system while the system is operating normally [26,53,60]. CED can test the circuit at full operating speed without stopping the system or switching it to test mode. Accordingly, CED can detect transient faults, which may not be detected in off-line testing, since they may not occur in test mode. Furthermore, concurrent error correction (CEC) can offer some advantages such as higher yield factors and increased availability in addition to the above mentioned advantages for CED.

To detect or correct errors, some kinds of redundancy are usually required: hardware, time, and/or information [53]. This thesis focuses mainly on the detection

1.1 Motivation 3

and/or correction of random errors in extension field arithmetic operations. The cause of such errors can be natural faults. Moreover, some faults deliberately injected by attackers may cause random errors, e.g., some faults resulting from electro magnetic interferences (EMIs). It is worth mentioning that some random errors in a number of hardware based cryptosystems or their arithmetic accelerators can be detected at an upper level operation, e.g., in elliptic curve cryptography (ECC), if a point leaves the curve it can be easily detected by point verification [10, 20]. This is, however, not always possible. In the case of ECC, a fault may move a point to another point without leaving the curve and this has been exploited in the so-called sign change fault attack<sup>1</sup> [14]. As a result, some kind of mechanisms for error detection in finite field operations can be quite important in cryptography as well as other critical applications where finite field operations of various sizes are used.

Although the schemes proposed in this thesis does not provide a complete solution to the problem of deliberately injected faults, they may reduce the success probability of an attack. This is because the number of faults that can be injected by an attacker is reduced to the number of faults that cannot be detected by the scheme. Furthermore, these schemes are more suitable mainly for large finite field arithmetic and may not be very suitable for those systems that use small finite field operations such as  $GF(2^8)$  operations of AES [21].

The majority of the work of this thesis is for extended binary field multipliers mainly because the complexity of multiplication is higher than the basic operations such as addition and subtraction. Also, other complex finite field arithmetic operations such as inversion and exponentiation over binary extension fields can be preformed by repeated multiplications [2,67].

<sup>&</sup>lt;sup>1</sup>Note that a random fault may move one point on the curve to another point on the curve with a very low probability [22].

### 1.2 Scope of this Work

In order to detect and/or correct random errors in finite field operations, a number of approaches can be considered, including:

- Using parity bits: In this approach, basically, the parity of the output is predicted and compared against its actual party. In [24], Fenn et al. presented a concurrent error detection scheme for bit-serial multipliers, using a number of bases for representation of fields, defined by an irreducible all-ones polynomial. In [55–57], parity based error detection schemes for both bit-serial and bit-parallel polynomial basis multipliers are presented. However, these schemes are not generic and can detect mostly odd number of erroneous bits and one of them can correct one bit.

- Scaling techniques: The second approach, which is also used in [27], is for example to scale the inputs of a multiplier by a factor and at the end of the multiplication the correctness of the result is checked by one or two divisions.

- Nonlinear techniques: One example for this approach [28] is to compute a non-linear residue for each input of the operation and then predict the residue of the output using these residues. To assure the correctness of the operation, one can compare the predicted residue against the actual output residue. This approach is expensive in terms of area and time and in turn may not be very efficient for detecting random errors.

- Time redundancy based techniques: In this approach some methods such as recomputing with shifted operands are used to detect errors in operations.

In [19,41], this method is used for detecting errors in polynomial basis multipliers.

1.3 Thesis Outline 5

Additionally, a number of schemes for detecting errors in arithmetic operations of the symmetric block ciphers are presented in [17]. These schemes are mostly based on parity and/or residue codes.

This thesis presents a number of schemes for concurrent error detection of the arithmetic operations over binary extension fields based on some of the above-mentioned approaches. These schemes are more generic than previous schemes in the sense that they can be applied to different implementations, e.g., bit-serial, bit-parallel and/or digit-serial, and also they can be applied to different bases for the field representation such as polynomial, dual and optimal normal bases. Additionally, the schemes presented in this thesis have high error detection capability, e.g., based on our simulations, the majority of the schemes have a percentage of error detection higher than 99% with a moderate amount of redundancies.

### 1.3 Thesis Outline

The organization of the remainder of the proposal is as follows. A brief overview of required background is presented in Chapter 2.

Chapter 3 presents a number of schemes for detecting errors concurrently in polynomial, dual and normal bases arithmetic operations. These schemes are based on recomputing with shifted operands technique and are efficient for pipelined architectures such as systolic arrays. To investigate more on this scheme, one finite field semi-systolic multiplier is presented for each of the polynomial, dual, type I and type II optimal normal bases. Then the CED scheme is applied to them. Additionally, the space and time complexity of these multipliers are compared against a number of systolic and/or semi-systolic multipliers previously published in the literature. Furthermore, the capability of error detection of each multiplier is evaluated by simulation-based fault injection. The results show that having better or

1.3 Thesis Outline 6

similar space and time overheads compared to a number of related previous work, the multipliers have generally a high error detection capability, e.g., the percentage of error detection of the scheme for the single and multiple stuck-at faults in a polynomial basis multiplier is 100%. Finally, we also comment on how RESO can be used for concurrent error correction to deal with transient faults.

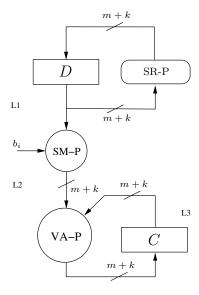

In Chapter 4, one parity based scheme to detect multiple-bit errors in polynomial basis multipliers is presented. In this scheme one input of the multiplier is divided into a number of parts and a parity bit is considered for each part. To obtain a realistic area and time overheads of the scheme, it is implemented in bit-serial and bit-parallel fashions on FPGAs. Also, the capability of the scheme is investigated using a theoretical analysis as well as a simulation-based fault injection. Having a high error detection capability, this scheme produces area and time overheads lower than dual modular redundant systems.

In Chapter 5, the parity based scheme presented in the previous chapter is extended to both inputs of the polynomial basis multiplier. This is because the errors on the second input cannot be detected, although, the error detection capability of the scheme, presented in previous chapter, is high, e.g., the percentage of error detection is 99.61% for eight partitions on the first input. This scheme is also implemented on FPGAs to determine the area and time overheads of the scheme. Moreover, the error detection capability of the scheme is evaluated by simulation-based fault injection. This scheme has slightly better percentage of error detection and slightly more area overhead compared to the previous scheme. In the second part of this chapter, both parity based schemes are extended to other bases, including dual, type I and type II normal bases.

In Chapter 6, a number of schemes based on linear codes are presented to detect errors in polynomial basis multipliers. In the first scheme one input of the multiplier is encoded by a generator polynomial. The correctness of the result is checked by decoding of the final and/or intermediate results of the multiplication. To resolve the problem of error detection on the second input of the multiplier, a second scheme is presented. In this scheme, both inputs of the multiplier are encoded by two different generator polynomials. Another scheme that combines the parity based scheme for the first input and the linear code based scheme for the second input is presented in this chapter. This scheme basically has a lower area overhead compared to the second scheme presented in this chapter, however, their error detection capabilities are almost the same. These scheme are also implemented on FPGAs and their error detection capability are evaluated by simulation-based fault injection.

Finally, summary and conclusions of the thesis as well as directions for further research are given in Chapter 7.

### 1.4 Research Contributions

Achieving an acceptable security level for hardware implementations of large digital systems specially with critical applications has received significant attention recently. Some of these digital systems use finite field arithmetic operations such as extension field multipliers. The major contributions of this thesis are the development of some schemes to concurrently detect and/or correct errors in such operations. Some specific contributions of the thesis are as follows:

- Concurrent error detection in binary extension field operations suitable for pipelined architectures and systolic arrays. These schemes use RESO (REcomputing with Shifted Operands) method for finite fields represented in polynomial, dual and optimal normal bases.

- Concurrent error detection in binary extension field multipliers for general bit-serial, digit-serial and/or bit-parallel implementations.

- Two of the schemes, SIMP and DIMP, are based on the parity codes and are for the finite fields represented using polynomial, dual and optimal normal bases.

- Three other schemes, SIE, DIE and hybrid, are based on the linear codes (scaling technique) and are for the finite fields represented using polynomial basis.

# Chapter 2

# Background

In this chapter, first finite fields are reviewed, secondly a number of arithmetic operations particularly multiplication algorithms are explained, and finally a brief introduction to fault tolerant systems is given.

### 2.1 Finite Fields

In this section, proofs of theorems and lemmas are omitted for brevity. For interested readers there are many good texts on algebra and finite fields such as [12, 30, 31, 42, 43, 46, 58].

### Basic Definitions and Properties

**Definition 2.1** A group is a set  $\mathbb{G}$  with a binary operation '\*' on  $\mathbb{G}$  if it satisfies the following conditions:

• The binary operation '\*' is associative, i.e.,

$$\forall a, b, c \in \mathbb{G}$$

$a * (b * c) = (a * b) * c$

• There is an identity element e in  $\mathbb{G}$  such that,

$$\forall a \in \mathbb{G} \quad a * e = e * a = a$$

• There is an inverse element for each element such that,

$$\forall a \in \mathbb{G}, \exists a^{-1} \in \mathbb{G} \quad a * a^{-1} = a^{-1} * a = e$$

The identity element of a group and the inverse of each element of a group are unique. Furthermore, a group is an Abelian or communicative group if '\*' also satisfies the following condition:

$$\forall a, b \in \mathbb{G} \quad a * b = b * a$$

**Definition 2.2** A set  $\mathbb{F}$  with two operations denoted by '+' and '.' is a field if it satisfies the following conditions:

- $(\mathbb{F}, +)$  is an Abelian group and 0 is its identity element.

- $(\mathbb{F}^*, .)$  is an Abelian group and 1 is its identity element where  $\mathbb{F}^*$  is the set of nonzero elements in  $\mathbb{F}$ .

- '.' is distributive over '+', i.e.,  $\forall a, b, c \in \mathbb{F}$

$$a.(b+c) = a.b + a.c$$

and

$$(b+c).a = b.a + c.a$$

**Definition 2.3** A set  $\mathbb{R}$  with two operations denoted by '+' and '.' is a ring if it satisfies all conditions of a field except the condition that each element should have

a multiplicative inverse. In other words, the elements of a ring may not have a multiplicative inverse.

**Definition 2.4** A field that contains a finite number of elements is called a finite field (also known as Galois field).

**Definition 2.5** The number of elements in a Galois field is called the order of the field and a Galois field with the order of q is denoted by GF(q).

**Definition 2.6** Let a be an element in GF(q). Then the smallest positive integer m is called characteristic of the field such that ma = 0.

**Theorem 2.1** The characteristic of any finite field is prime.

**Theorem 2.2** In a Galois field, the order of the field is a prime or a power of a prime.

**Lemma 2.1** Characteristic of  $GF(q) = \begin{cases} q & \text{if } q \text{ is prime;} \\ p & \text{if } q \text{ is a power of a prime } p. \end{cases}$

**Definition 2.7** The order of a nonzero element  $a \in GF(q)$  is the smallest positive integer n such that,

$$a^n \equiv 1$$

**Theorem 2.3** Let a be a nonzero element of GF(q). Then  $a^{q-1} \equiv 1$ .

Using Theorem 2, the inverse of any nonzero element a could be computed by  $a^{-1} \equiv a^{q-2}$ .

**Definition 2.8** In a finite field GF(q), a nonzero element a is primitive if its order is q-1.

**Definition 2.9** V is a vector space over F with multiplication operation '.':  $F \times V \to V$  if for all  $a, b \in F$  and  $v, w \in V$ :

- 1. (V, +) is a commutative group

- 2. a(v + w) = av + aw

- 3. (a+b)v = av + bv

- 4. (ab)v = a(bv)

- 5. 1v = v

Elements of F and V are called scalars and vectors, respectively. '+' is called vector addition and '.' is called scalar multiplication.

#### **Polynomials**

A polynomial over GF(p) is an expression of the following form:

$$F(x) = \sum_{i=0}^{n} a_i x^i = a_0 + a_1 x + \dots + a_n x^n$$

where  $a_i \in GF(p)$  and n, the degree of F(x), is a nonnegative integer. Polynomial F(x) is called monic if  $a_n = 1$ .

**Definition 2.10** A polynomial F(x) over GF(p) is said to be irreducible if it cannot be written as the product of some lower degree polynomials over GF(p).

**Definition 2.11** Suppose a polynomial F(x) over GF(p) which  $F(0) \neq 0$ . The order (or period) of F(x) is the least positive integer t such that  $F(x)|x^t - 1$ .

**Definition 2.12** Let F(x) be a polynomial of degree m over GF(p). Polynomial F(x) is said to be a primitive polynomial if its order is  $p^m - 1$ .

**Definition 2.13** A polynomial F(x) is said to be an all-ones polynomial (AOP) if all of its coefficients are one.

### Construction and Representation of $GF(p^m)$

To construct  $GF(p^m)$  the following theorem can be applied.

**Theorem 2.4** Let F(x) be an irreducible polynomial of degree m over GF(p). Then all polynomials over GF(p) of degree less than m form a finite field  $GF(p^m)$  of order  $p^m$  if addition and multiplication are performed modulo F(x).

F(x) is referred to as the field defining polynomial.

**Definition 2.14** Let F and G be two fields and  $F \subset G$ . Then F is called a subfield of G and G is called an extension field of F.

For example,  $GF(p^m)$  is an extension field of GF(p).

$GF(p^m)$  is a vector space of dimension m over GF(p). Thus, the basis of vector space  $GF(p^m)$  could be any set of m linearly independent elements, e.g.,  $\{x_0, x_1, \ldots x_{m-1}\}$ . A linear combination of these elements is as follows:

$$\mathcal{A} = a_0 x_0 + a_1 x_1 + \dots a_{m-1} x_{m-1}$$

where  $a_i \in GF(p)$ .

There are some well-known bases for representation of extension fields such as canonical (polynomial) basis, normal basis, dual basis and triangular basis. Below we introduce the first three bases.

**Definition 2.15** Let x be the root of an irreducible polynomial F(x) over GF(p) of degree m, i.e., F(x) = 0. Canonical (polynomial) basis is defined as the following set:

$$\{1, x, x^2, \dots x^{m-1}\}$$

Hereafter, this basis is called polynomial basis (PB).

**Definition 2.16** Let  $a \in GF(p^m)$ . The trace of a is:

$$\operatorname{Tr}(a) = \sum_{i=0}^{m-1} a^{p^i}.$$

The dual basis (DB) of the polynomial basis  $\{1, x, x^2, \dots x^{m-1}\}$  is a basis  $\{y_0, y_1, \dots, y_{m-1}\}$ , where  $y_i \in GF(2^m)$ , such that

$$\operatorname{Tr}(y_i x^j) = \begin{cases} 0, & i \neq j; \\ 1, & \text{otherwise.} \end{cases}$$

(2.1)

**Definition 2.17** A normal basis (NB) of  $GF(p^m)$  has the following form:

$$\{z, z^p, z^{p^2}, \dots z^{p^{m-1}}\}$$

where  $z \in GF(p^m)$ .

### 2.2 Field Arithmetic Operations

In this section, arithmetic operations except addition and subtraction which are considered to be trivial are briefly explained. Two arithmetic operations, i.e., multiplication and inversion over extension fields are discussed in the two following sections. It will be shown that the arithmetic operations such as inversion, division, exponentiation can be computed using repeated multiplications. We will use polynomial basis for representation of the elements of the binary extension field  $GF(2^m)$ .

### **2.2.1** Multiplication over $GF(2^m)$

#### General Bit-level Multiplications

Suppose that  $A, B \in GF(2^m)$  and F(x) is the modulus (defining polynomial of the field). Thus, given bits  $a_i, b_i \in GF(2)$ , we have:

$$A = \sum_{i=0}^{m-1} a_i x^i, \quad B = \sum_{i=0}^{m-1} b_i x^i$$

$$C = AB \mod F(x) = A \sum_{i=0}^{m-1} b_i x^i \mod F(x)$$

$$= \sum_{i=0}^{m-1} Ab_i x^i \mod F(x)$$

$$= (b_0 A + b_1 x A + \dots + b_{m-1} x^{m-1} A) \mod F(x)$$

(2.2)

According to (2.2), bit-level algorithm of multiplication from low bit to high bit is given in Algorithm 2.1.

### **Algorithm 2.1** Low-to-high bit-level multiplication in $GF(2^m)$ [31]

```

Input: A, B, F(x)

Output: C = AB \mod F(x)

D := A

C := 0

For i = 0 to m - 1 do \{

C := C + D.b_i

D := xD \mod F(x)

\}

```

Equation (2.2) can also be written as follows:

$$C = AB \mod F(x)$$

$$= A(b_{m-1}x^{m-1} + b_{m-2}x^{m-2} + \dots + b_0) \mod F(x)$$

$$= (\dots (Ab_{m-1}x + b_{m-2})x + \dots)x + Ab_0 \mod F(x)$$

$$= (\dots (Ab_{m-1}x \mod F(x) + b_{m-2})x \mod F(x) + \dots)x \mod F(x) + Ab_0$$

(2.3)

Based on (2.3), an algorithm for bit-level multiplication from high bit to low bit of element B is given in Algorithm 2.2.

### **Algorithm 2.2** High-to-low bit-level multiplication in $GF(2^m)$ [31]

```

Input: A, B, F(x)

Output: C = AB \mod F(x)

C := A.b_{m-1}

For i = m - 2 to 0 do {

C := xC \mod F(x)

C := C + A.b_i

}

```

An advantage of the second algorithm is that D, which is a register in hardware implementation, is not needed.

#### **Bit-Serial Multiplications**

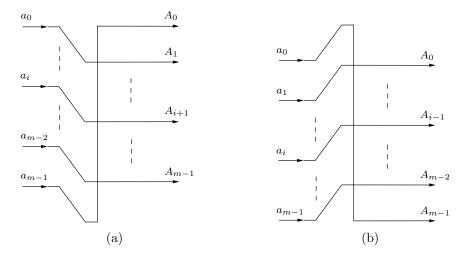

Let  $A \in GF(2^m)$  and F(x) be the defining polynomial. X = xA can be computed as:

$$X = xA = x \sum_{i=0}^{m-1} a_i x^i \mod F(x)$$

$$= \sum_{i=0}^{m-1} a_i x^{i+1} \mod F(x)$$

$$= \sum_{i=0}^{m-2} a_i x^{i+1} + a_{m-1} x^m \mod F(x)$$

$$= \sum_{i=0}^{m-2} a_i x^{i+1} + a_{m-1} \sum_{i=0}^{m-1} f_i x^i$$

(2.4)

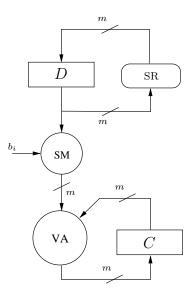

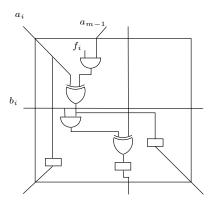

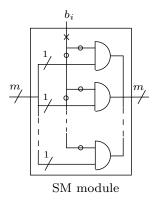

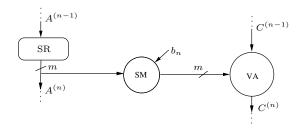

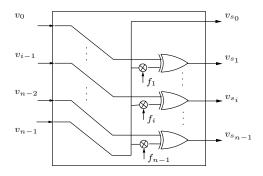

Figure 2.1: SR module

Figure 2.1 shows a module whose input and output are A and X, respectively. This module basically performs a shift operation and a reduction operation. Hence, it is hereafter referred to as Shift-and-Reduce or SR module.

Multiplication of  $A, B \in GF(2^m)$  can be written as:

$$C = AB = A(b_{m-1}x^{m-1} + b_{m-2}x^{m-2} + \dots + b_0)$$

$$= (b_{m-1}x^{m-1}A + b_{m-2}x^{m-2}A + \dots + b_0A)$$

$$= (b_{m-1}A^{(m-1)} + b_{m-2}A^{(m-2)} + \dots + b_0A^{(0)})$$

(2.5)

where  $A^{(0)} = A$  and  $A^{(i)} = xA^{(i-1)}$ .

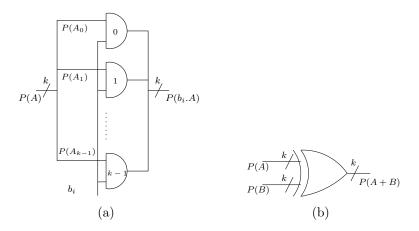

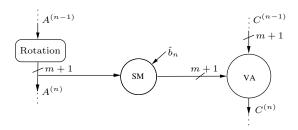

Since  $GF(2^m)$  is a vector space, in (2.5), '.' is a scalar multiplication and '+' is a vector addition [see Definition 2.9]. Additionally, bit  $b_i$  is the  $i^{th}$  coordinate of B. Figure 2.2 shows a low-to-high bit-serial multiplier where D is initialized with A. Scalar multiplication and vector addition of a bit-serial multiplier are bitwise-AND

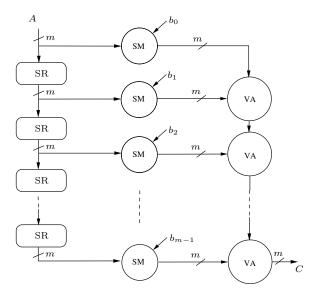

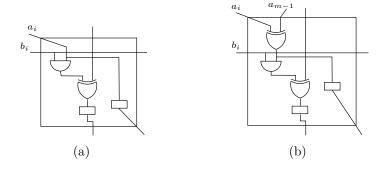

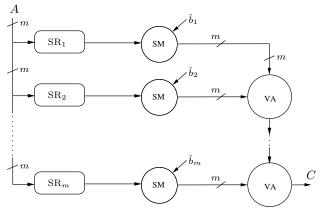

and bitwise-XOR, respectively. Modules that perform scalar multiplication and vector addition are hereafter referred to as SM module and VA module, respectively. These two modules and the SR module discussed earlier are the main components of a PB multiplier. In accordance with (2.5) and using these three main components, a bit-serial PB multiplier can be constructed as shown in Figure 2.2 (see [61] for a similar multiplier architecture).

Figure 2.2: Low-to-high bit-serial multiplication

#### **Bit-parallel Multiplications**

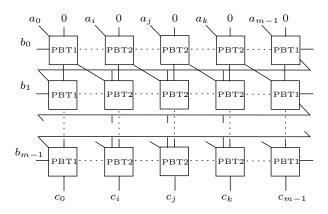

According to (2.5), we can implement multiplication in a bit-parallel fashion. Figure 2.3 shows a bit-parallel multiplication. A bit-parallel multiplication needs (m-1) SR modules, m scalar multiplications and (m-1) vector additions.

#### **Digit-Serial Multiplications**

Another method to implement a PB multiplier is to combine the above-mentioned implementations. In other words, instead of computing the multiplication of input

Figure 2.3: Bit-parallel multiplication

A by one bit of input B per clock cycle (like bit-serial implementations), one can multiply A by a number of bits of B (i.e., a digit of B). This implementation is referred to as digit-serial implementation.

### **2.2.2** Inversion over $GF(2^m)$

There are several algorithms for inversion [31] which are based on one of the following methods.

- 1. Repeated squaring-and-multiplications in extension field  $GF(2^m)$

- 2. Use of extended Euclidean algorithm over some subfield of GF(2)

- 3. Solution of a system of linear equations over some subfield of GF(2)

We consider the first two methods. The former is based on Theorem 2.3, such that  $\forall a \in GF(q=2^m)$ :

$$a^{q-1} = 1$$

$$a^{-1} = a^{q-2}$$

The latter is discussed below.

#### Extended Euclidean Algorithm (EEA) Based Inversion

Let  $A(x) \in GF(2^m)$  and F(x) be the defining polynomial of the field. We want to find B(x) such that,

$$A(x)B(x) = 1 \mod F(x)$$

.

Since gcd(F(x), A(x)) = 1, B(x) can be obtained using EEA (Algorithm 2.3):

$$A(x)B(x) + F(x)C(x) = 1$$

# Algorithm 2.3 Extended Euclidean algorithm [31]

```

Input: F(x) and A(x) \neq 0

Output: B(x)

Step1: R^{(-1)}(x) = F(x), R^{(0)}(x) = A(x)

U^{(-1)}(x) = 0, U^{(0)}(x) = 1

i = 0

Step2: do\{

i = i + 1

Q^{(i)}(x) = \lfloor R^{(i-2)}(x)/R^{(i-1)}(x) \rfloor

R^{(i)}(x) = R^{(i-2)}(x) - Q^{(i)}(x)R^{(i-1)}(x)

U^{(i)}(x) = U^{(i-2)}(x) - Q^{(i)}(x)U^{(i-1)}(x)

\} \text{while } (R^{(i)}(x) \neq 0)

Step3: B(x) = U^{(i-1)}(x)

```

It is worth mentioning that in addition to inversion, two other arithmetic operations, i.e., division and exponentiation, can be performed using repeated multiplications because:

$$\frac{A}{B} = A \times B^{-1},$$

$$A^{n} = \underbrace{A \times A \cdot \dots \times A}_{n},$$

where n is a non-negative integer.

# 2.3 Fault Tolerant Systems

#### 2.3.1 Faults

Faults can be investigated at different levels, including gate-level and architecture-level. Below we give brief descriptions of gate and architecture level faults.

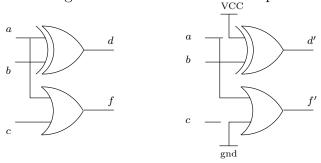

Gate-level faults can be categorized as open faults, short (bridging) faults, and stuck-at faults. An example for an open fault is a disconnected wire. The disconnected wire may keep its previous value. Figure 2.4 shows a circuit with an open fault which the gate output is disconnected. Assuming that the value of the circuit before disconnection was 1, the correct output (c) and the faulty output (c') for different values of the gate inputs are presented in Table 2.1. Clearly, the error can be modelled by a bit-flip  $(e_c = c \oplus c')$  in a higher level of abstraction such as architecture-level.

Figure 2.4: Open fault example b c c'

Table 2.1: Open fault table

| a | b | c | c' | $e_c$ |

|---|---|---|----|-------|

| 0 | 0 | 0 | 1  | 1     |

| 0 | 1 | 0 | 1  | 1     |

| 1 | 0 | 0 | 1  | 1     |

| 1 | 1 | 1 | 1  | 0     |

Similarly, Figure 2.5 shows two circuits, which one of them is fault free and the other one has two stuck-at faults. Table 2.2 presents the expected correct output values (d and f), the faulty output values (d' and f') and the multiple-bit flip errors that model the stuck-at faults  $(e_d \text{ and } e_f)$ .

Figure 2.5: Stuck-at fault example  $_{\rm VCC}$

Table 2.2: Stuck-at fault table

| a | b | c | d | f | d' | f' | $e_d$ | $e_f$ |

|---|---|---|---|---|----|----|-------|-------|

| 0 | 0 | 0 | 0 | 0 | 1  | 0  | 1     | 0     |

| 0 | 0 | 1 | 0 | 1 | 1  | 0  | 1     | 1     |

| 0 | 1 | 0 | 1 | 0 | 0  | 0  | 1     | 0     |

| 0 | 1 | 1 | 1 | 1 | 0  | 0  | 1     | 1     |

| 1 | 0 | 0 | 1 | 1 | 1  | 1  | 0     | 0     |

| 1 | 0 | 1 | 1 | 1 | 1  | 1  | 0     | 0     |

| 1 | 1 | 0 | 0 | 1 | 0  | 1  | 0     | 0     |

| 1 | 1 | 1 | 0 | 1 | 0  | 1  | 0     | 0     |

#### 2.3.2 Fault Tolerant Techniques

For having fault tolerance or detection capability, one can use some forms of redundancies. There are three common types of redundancies [51] used in practice:

1) Hardware redundancy, 2) Time redundancy and 3) Information redundancy.

An example for hardware redundancy is a dual modular redundant (DMR) system. In this system, two identical modules are functioning simultaneously and their results are compared. Any difference between the results indicates an error. A DMR has (more than) 100% hardware redundancy. On the other hand, one system with one module can perform the computations twice and then compare the results. This system has 100% time redundancy and clearly some hardware redundancies for storing the intermediate result and comparing the results. In the following section, some forms of information redundancies are briefly explained. For further information, references [1, 37, 42, 51] are recommended.

# 2.3.3 Information Redundancy

**Definition 2.18** A code is a set of rules by which some information or data is represented.

For example, a code can be 4-bit representation of each digit of a number which is called binary coded decimal (BCD).

**Definition 2.19** A collection of bits which is representing some information or data using a code is said to be a codeword. The bits are called digits if they are numbers. A binary code contains only 0 and 1 digits which are called bits.

**Definition 2.20** A codeword is valid if it satisfies all of the rules of the code.

For example, '1001' is a valid BCD , but '1100' is invalid. In the following a number of special codes are reviewed.

#### **Parity Codes**

The simplest form of a code is the parity code.

**Definition 2.21** Let  $A = (a_{k-1}, a_{k-2}, \dots, a_1, a_0)$  be a k-bit message. The single-bit parity code of A is  $A_C = (a_c, a_{k-1}, a_{k-2}, \dots, a_1, a_0)$  where  $a_c$  can be obtained as follows:

$$\begin{cases}

a_c = \sum_{i=0}^{n-1} a_i \mod 2; & \text{even parity} \\

a_c = \left(1 + \sum_{i=0}^{n-1} a_i\right) \mod 2; & \text{odd parity}

\end{cases}$$

(2.6)

For a hardware implementation of the above even (or odd) parity generator, k (or k+1) XOR gates are needed<sup>1</sup>.

The single-bit parity code can detect any single-bit error but it cannot correct it. Moreover, such codes can detect any odd number of erroneous bits, since they change an odd parity codeword to an even parity one and vice versa. Hereafter, parity is used instead of even parity for brevity.

#### **Arithmetic Codes**

One useful code especially for arithmetic operations are arithmetic codes [51]. The data are encoded before the operations are performed. The result should be a valid codeword, otherwise, an error is signalled.

Let b and c be the data and '\*' be the operation and A() be the encoding function. Then the arithmetic code must be invariant to the operation, i.e.,

$$A(b*c) = A(b)*A(c)$$

• The simplest arithmetic code is called AN code. It is constructed by multiplying a constant A by a data word N. AN codes are invariant to addition

$<sup>^{1}</sup>$ Precisely, for the odd parity generator, k XOR gates and one NOT gate are needed.

and subtraction, but, they are variant to multiplication. In case of binary codes, A should not be a power of 2. Let  $N = (a_{n-1}, a_{n-2}, \dots, a_1, a_0)$  be multiplied by  $A = 2^i$ . AN is:

$$(a_{n-1}, a_{n-2}, \cdots, a_1, a_0, 0, \cdots, 0)$$

where i zeroes appended to original N. Let any bit before the appended zeroes, i.e.,  $a_i$ 's, be flipped. Then the code cannot detect the fault, since it is still divisible by  $2^a$ .

One of the well-known AN codes is 3N code which can be efficiently constructed by addition of 2N and N. It increases the size of original message by 2 bits.

• Residue code is another type of arithmetic codes. For constructing a residue codeword, the original information is divided by a constant which is called modulus. Then the remainder, which is called the residue, is appended to the original information. This code is invariant to modular addition.

Let the size of modulus and original information be m bits and n bits, respectively. The size of the residue codeword is m + n bits.

• Inverse residue code is a modification of the residue code. Inverse residue is calculated as M - R, where M is the modulus and R is the residue of original information. The inverse residue codeword is constructed by appending inverse residue to the original information.

The advantage of such codes is their better tolerance in presence of repeated-use faults. A repeated-use fault is one that is encountered multiple times before the code is checked, since the hardware is used multiple times before checking [51].

#### **Duplication Codes**

In duplication codes, a codeword consists of completely duplicating of original information. The detection capability of such codes are the best. Since the information are assumed to be fault free if both parts are the same. The main disadvantage of such codes is its 100% informational overhead. But in many applications such as data transmission or memory, in addition to 100% informational overhead, there is a 100% redundancy in hardware and/or time. A variation of a basic duplication code is to complement the duplicated portion of the codeword. This is a major advantage when the original information and its duplicate must pass through the same way or must be processed by the same hardware.

# Chapter 3

# Concurrent Error Detection Using RESO

This chapter presents a number of schemes for detecting errors concurrently in polynomial, dual and normal bases arithmetic operations. The schemes presented in this chapter are based on recomputing with shifted operands (RESO) technique and are efficient for pipelined architectures such as systolic arrays. To investigate more on this scheme, one finite field semi-systolic multiplier is presented for each of the polynomial, dual, type I and type II optimal normal bases. Then the CED scheme is applied to them. Additionally, the space and time complexities of these multipliers are compared against a number of systolic and/or semi-systolic multipliers previously published in the literature. Furthermore, the capability of error detection of each multiplier is evaluated by simulation-based fault injection. The results show that having better or similar space and time overheads compared to a number of related previous work, the multipliers have generally a high error detection capability, e.g., the percentage of error detection of the scheme for the single and multiple stuck-at faults in a polynomial basis multiplier is 100%. Finally, we also comment on how RESO can be used for concurrent error correction to deal

3.1 RESO Method 28

with transient faults.

The organization of the remainder of this chapter is as follows. In Section 3.1, the RESO method is reviewed. The concurrent error detection strategy is presented in Section 3.2. General pipelined architectures, which are suitable for these schemes, along with an overhead analysis are given in Section 3.3. In Section 3.4, the CED scheme is investigated with more details for polynomial, dual and normal bases multipliers. The error detection capability of the scheme is then evaluated in Section 3.5. In Section 3.6, some comments on the concurrent error correction strategy are given. Finally, Section 3.7 gives a summary of the chapter.

This work also appeared in [5].

#### 3.1 RESO Method

REcomputing with Shifted Operands (RESO) is a technique for concurrent error detection (CED) in arithmetic and logic units introduced by Patel and Fung in [48,49]. This technique is based on time redundancy. Suppose x and f(x) are the input and output of a computation unit f, respectively. Also, suppose E and D are two functions such that D(f(E(x))) = f(x). Now, we store the result of the computation of f(x) (first step) in a register and compare it with the result of the computation of D(f(E(x))) (second step). Any difference between results of these two steps indicates an error. The functions E and D are referred to as encoding and decoding functions, respectively, and they can be usually chosen such that  $D = E^{-1}$ . It is worth mentioning that for conventional binary operands, E and D are simple shifts of operand bits and this is why it is referred to as RESO.

# 3.2 Concurrent Error Detection Strategy

Errors may be caused by different types of faults such as open faults, short (bridging) faults, and/or stuck-at faults. Furthermore, the faults can be transient or permanent. We assume that locations of these faults, occurred naturally or injected by an attacker, are random.

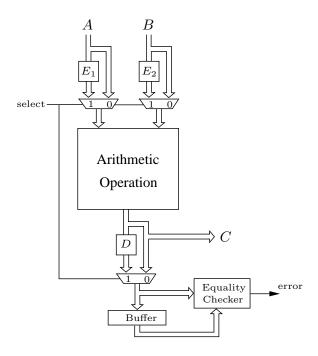

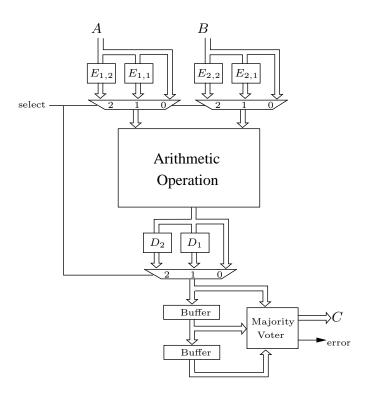

In this section, we use RESO method to concurrently detect errors in arithmetic operations over the field  $GF(2^m)$ . For the polynomial, normal and dual bases, the encoding and decoding functions are chosen in a way that the overhead costs (in terms of area and time) are fairly low. Additionally, in this chapter, the arithmetic operations addition/subtraction, multiplication, inversion, division, and exponentiation are considered. Figure 3.1 shows a general architecture of an operation with concurrent error detection. In the figure, two encoding functions of the inputs are  $E_1$  and  $E_2$  and the decoding function of the output is D. Clearly, for inversion the second input should not be considered. Also, for exponentiation the exponent is a non-negative integer number and is not an extension field element. Therefore, this input of exponentiation is not considered as well.

Let us assume that the arithmetic operation performs the f function. Then we have:

$$C = f(A, B).$$

Also, let  $A_{E_1} = E_1(A)$  and  $B_{E_2} = E_2(B)$ . Considering that C' is the result of the second computation after decoding, we have:

$$C' = D(f(A_{E_1}, B_{E_2})).$$

As a result,

error =

$$\begin{cases} 0 & \text{if } C = C', \\ 1 & \text{if } C \neq C'. \end{cases}$$

Figure 3.1: General architecture for the arithmetic operations with CED

In the following, the above-mentioned concurrent error detection strategy for each basis is investigated.

# 3.2.1 CED for Polynomial Basis (PB) Arithmetic Operations

Let us denote PB of  $GF(2^m)$  as  $1, x, \dots, x^{m-1}$ . A possible candidate for encoding and decoding functions in the PB representation of the elements of the field is multiplication by x or  $x^{-1}$ . Clearly, all arithmetic operations are modulo the field defining polynomial F(x). Particularly, elements  $x^m$  and  $x^{-1}$  modulo F(x) are as

follows:

$$x^{m} = 1 + \sum_{i=1}^{m-1} f_{i} x^{i} \mod F(x),$$

$$x^{-1} = x^{m-1} + \sum_{i=0}^{m-2} f_{i+1} x^{i} \mod F(x).$$

(3.1)

The multiplication of x and an arbitrary element A of  $GF(2^m)$  is performed as follows:

$$xA = \sum_{i=0}^{m-1} a_i x^{i+1} \mod F(x) = \sum_{i=0}^{m-2} a_i x^{i+1} + a_{m-1} x^m \mod F(x)$$

$$= (0, a_0, \dots, a_{m-3}, a_{m-2}) + a_{m-1} (1, f_1, \dots, f_{m-2}, f_{m-1}).$$

(3.2)

Similarly the multiplication of  $x^{-1}$  and A is performed as follows:

$$x^{-1}A = \sum_{i=0}^{m-1} a_i x^{i-1} \mod F(x) = a_0 x^{-1} + \sum_{i=1}^{m-1} a_i x^{i-1} \mod F(x)$$

$$= (a_1, a_2, \dots, a_{m-1}, 0) + a_0 (f_1, f_2, \dots, f_{m-1}, 1).$$

(3.3)

Hereafter, the former and the latter are referred to as (forward) scaling and inverse scaling, respectively. Additionally, both scalings are very inexpensive in hardware implementations. An overhead analysis will be given in Section 3.3.1.

Note that multiplication of an element with  $x^i$  or  $x^{-i}$  can be considered as i consecutive scalings or inverse scalings, respectively. In the following, encoding and decoding functions are determined for each operation. Also, we show the procedure of CED in each PB arithmetic operation, assuming that  $A, B, C \in GF(2^m)$ .

- 1. Addition/Subtraction:  $E_1 = x$ ,  $E_2 = x$ ,  $D = x^{-1}$ .

- (a) Compute A + B = C; Store in a register;

- (b) Compute Ax + Bx = (A + B)x = Cx; Inverse scaling; Compare this result with that of (a).

- 2. Multiplication:  $E_1 = x$ ,  $E_2 = x$ ,  $D = x^{-2}$ .

- (a) Compute  $A \times B = C$ ; Store in a register;

- (b) Compute  $Ax \times Bx = (A \times B)x^2 = Cx^2$ ; Two inverse scalings; Compare this result with that of (a).

- 3. Inversion:  $E_1 = x$ , D = x.

- (a) Compute  $\frac{1}{A} = C$ ; Store in a register;

- (b) Compute  $\frac{1}{Ax} = (\frac{1}{A})x^{-1} = Cx^{-1}$ ; Forward scaling; Compare this result with that of (a).

- 4. Division:  $E_1 = x$ ,  $E_2 = x^{-1}$ ,  $D = x^{-2}$ .

- (a) Compute  $\frac{A}{B} = C$ ; Store in a register;

- (b) Compute  $\frac{Ax}{Bx^{-1}} = \frac{A}{B}x^2 = Cx^2$ ; Two inverse scalings; Compare this result with that of (a).

- 5. Exponentiation:  $E_1 = x$ ,  $D = x^{-n}$ , where n is a non-negative integer.

- (a) Compute  $A^n = C$ ; Store in a register;

- (b) Compute  $(Ax)^n = A^n x^n = Cx^n$ ; *n* inverse scaling; Compare this result with that of (a).

For large n, to speed up the exponentiation, one can pre-compute and store  $x^{-n}$  for  $1 \le n \le 2^m - 1$  in some fault-tolerant manner.

Alternative encodings and decodings for multiplication and division are as follows:

- Multiplication:  $E_1 = x$ ,  $E_2 = x^{-1}$ , No decoding.

- 1. Compute  $A \times B = C$ ; Store in a register;

- 2. Compute  $Ax \times Bx^{-1} = (A \times B) = C$ ; Compare this result with that of (a).

- Division:  $E_1 = x$ ,  $E_2 = x$ , No decoding.

- 1. Compute  $\frac{A}{B} = C$ ; Store in a register;

- 2. Compute  $\frac{Ax}{Bx} = \frac{A}{B} = C$ ; Compare this result with that of (a).

Although this is more efficient for implementation, it may result in a lower error detection capability. For example, a permanent single-bit fault at the end of an arithmetic operation cannot be detected, since such faults change the results of both runs in a same manner and generates identical results even in the presence of the faults.

# 3.2.2 CED for Dual Basis (DB) Arithmetic Operations

Similar to PB arithmetic operations, a suitable candidate for encoding and decoding functions in DB representation of the elements of the field is multiplication of an element by x or  $x^{-1}$ . This multiplication is considered in Lemma 3.1.

**Lemma 3.1** Let  $A = (a'_0, a'_1, \dots, a'_{m-1}) \in GF(2^m)$  be represented in dual basis. Let  $F(x) = \sum_{i=0}^m f_i x^i$  be the field defining polynomial. Then the (forward) scaling and inverse scaling can be performed as follows:

$$xA = (a'_1, a'_2, \cdots, a'_{m-1}, \sum_{i=0}^{m-1} f_i a'_i)$$

$$x^{-1}A = (\sum_{i=0}^{m-1} f_{i+1} a'_i, a'_0, a'_1, \cdots, a'_{m-2})$$

(3.4)

**Proof** The proof for forward scaling can be found in [65]. Similarly, the inverse scaling can be proved as follows. Assume that the PB representation of A is  $(a_0, a_1, \dots, a_{m-1})$ . Then according to Section 2.1, we have:

$$A = \sum_{i=0}^{m-1} a_i x^i,$$

(PB representation)

$$A = \sum_{i=0}^{m-1} a'_i y_i.$$

(DB representation)

Moreover, according to [65], we have:

$$\operatorname{Tr}(x^j A) = a'_j.$$

Therefore, for  $1 \le j \le m-1$ , we have:

$$(x^{-1}A)'_{j} = \operatorname{Tr}\left(x^{-1}Ax^{j}\right) = \operatorname{Tr}\left(Ax^{j-1}\right)$$

$$= a'_{j-1}.$$

Also,

$$(x^{-1}A)'_0 = \operatorname{Tr}(Ax^{-1}) = \operatorname{Tr}\left(A\sum_{i=0}^{m-1} f_{i+1}x^i\right) = \sum_{i=0}^{m-1} f_{i+1}\operatorname{Tr}(Ax^i)$$

$$= \sum_{i=0}^{m-1} f_{i+1}a'_i.$$

Therefore,

$$x^{-1}A = (\sum_{i=0}^{m-1} f_{i+1}a'_i, a'_0, a'_1, \dots, a'_{m-2}).$$

Note that for low weight F(x), the hardware implementation of DB scalings requires only a few gates (see Section 3.3.2). Moreover, functions  $E_1$ ,  $E_2$  (if applicable), and D can be chosen same as those chosen for PB representation in Section 3.2.1 and similar CED procedure can be performed.

#### 3.2.3 CED for Normal Basis (NB) Arithmetic Operations

Let  $A = \sum_{i=0}^{m-1} a_i \alpha^{2^i}$  be the NB representation of A. Then considering that the arithmetic is performed in characteristic 2, we have:

$$A^{2} = \sum_{i=0}^{m-1} \left( \hat{a}_{i} \alpha^{2^{i}} \right)^{2} = \sum_{i=0}^{m-1} \hat{a}_{i} \alpha^{2^{i+1}}$$

$$= \left( \hat{a}_{m-1}, \hat{a}_{0}, \hat{a}_{1}, \dots, \hat{a}_{m-2} \right).$$

$$A^{\frac{1}{2}} = \sum_{i=0}^{m-1} \left( \hat{a}_{i} \alpha^{2^{i}} \right)^{\frac{1}{2}} = \sum_{i=0}^{m-1} \hat{a}_{i} \alpha^{2^{i-1}}$$

$$= \left( \hat{a}_{1}, \dots, \hat{a}_{m-2}, \hat{a}_{m-1}, \hat{a}_{0} \right).$$

$$(3.5)$$

The hardware implementations of NB squaring and taking the square root have no cost (see Section 3.3.3). Therefore, in NB arithmetic operations, proper choices for encoding and decoding functions are squaring and taking the square root. Moreover, the procedures of CED in NB arithmetic operations are more uniform since the encoding function(s) and the decoding function are always squaring and taking the square root, respectively. The CED procedures follow, assuming that  $A, B, C \in GF(2^m)$  and n is a non-negative integer.

#### 1. Addition/Subtraction:

- (a) Compute A + B = C; Store in a register;

- (b) Compute  $A^2 + B^2 = (A + B)^2 = C^2$ ; Take square root; Compare this result with that of (a).

#### 2. Multiplication:

- (a) Compute  $A \times B = C$ ; Store in a register;

- (b) Compute  $A^2 \times B^2 = (A \times B)^2 = C^2$ ; Take square root; Compare this result with that of (a).

#### 3. Inversion:

- (a) Compute  $\frac{1}{A} = C$ ; Store in a register;

- (b) Compute  $\frac{1}{A^2} = (\frac{1}{A})^2 = C^2$ ; Take square root; Compare this result with that of (a).

#### 4. Division:

- (a) Compute  $\frac{A}{B} = C$ ; Store in a register;

- (b) Compute  $\frac{A^2}{B^2} = \left(\frac{A}{B}\right)^2 = C^2$ ; Take square root; Compare this result with that of (a).

#### 5. Exponentiation:

- (a) Compute  $A^n = C$ ; Store in a register;

- (b) Compute  $(A^2)^n = (A^n)^2 = C^2$ ; Take square root; Compare this result with that of (a).

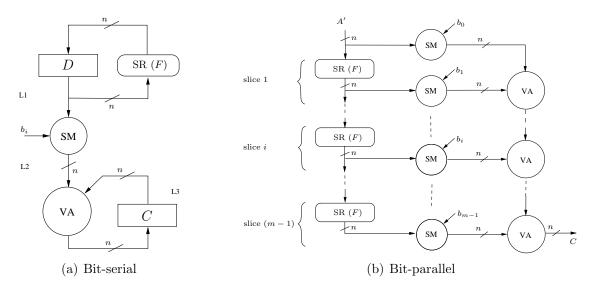

# 3.3 Pipeline Architecture and Overhead Analysis

The proposed CED scheme is based on time redundancy. A straightforward implementation causes more than 100% time redundancy which may not be desirable. An efficient architecture that can reduce the time overhead significantly is a pipeline architecture. Additionally, this architecture has a moderate area overhead. An example for the pipelined architecture is the systolic array, which is used for high performance arithmetic operations. As shown in Figure 3.2(a), one buffer is added to the end of the pipeline architecture to store the result of the (first) computation of the arithmetic operation. Then the result of the second computation after decoding will be compared against the content of the last buffer of the pipeline. Another possibility is to start performing the operation with encoded inputs first

and then perform the normal computation. In this case, a decoder should be placed after the added buffer as shown in Figure 3.2(b).

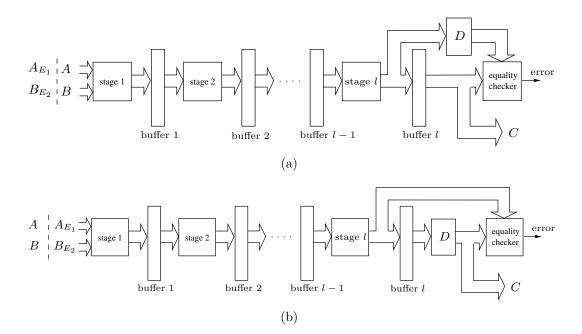

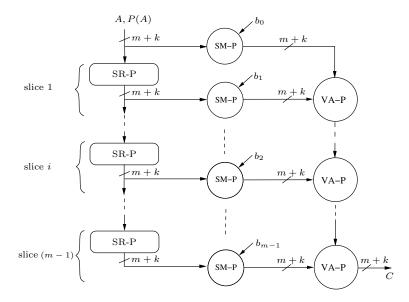

Figure 3.2: General pipelined architecture of an arithmetic operation with the proposed CED

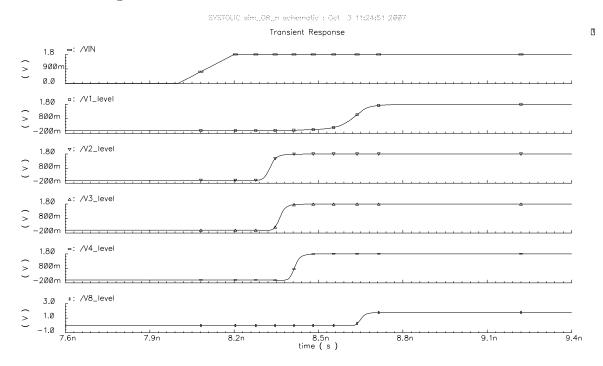

Suppose that the number of pipeline stages is l. Let the propagation delays of the encoding function, the decoding function, the  $i^{th}$  stage of the pipeline (including a buffer), the buffer, the equality checker, and one XOR gate be  $t_e$ ,  $t_d$ ,  $t_i$ ,  $t_b$ ,  $t_c$ , and  $t_X$ , respectively. Let  $t'_{clk}$  and  $t_{clk}$  be the clock period of the pipelined arithmetic operation with and without CED, respectively. Clearly,  $t_{clk} \geq \max\{t_i\}$  for  $1 \leq i \leq l$ . Also, in practice,  $t_{clk} \geq t_X$ . For each pipeline architecture of Figure 3.2,  $t'_{clk}$ , the clock period and latency overheads are given in Table 3.1. One can choose one of the above-mentioned architectures which has a smaller latency overhead.

It is worth mentioning that in some pipeline architectures such as systolic arrays, the delay of the equality checker  $(t_c)$  can be larger than other delays mentioned in

| Architecture | $t_{clk}^{\prime}$                                                                        | Clock period               | Latency                                |

|--------------|-------------------------------------------------------------------------------------------|----------------------------|----------------------------------------|

|              |                                                                                           | overhead $(\Delta_t)$      | overhead $(\Gamma_t)$                  |

| (a)          | $\geq \operatorname{Max} \{t_e + t_1, \operatorname{Max}\{t_i\}, t_l - t_b + t_d + t_c\}$ | $t'_{clk} - t_{clk}$       | $l \times \Delta_{t_{(a)}} + t'_{clk}$ |

| (b)          | $\geq \max\{t_e + t_1, \max\{t_i\}, t_l - t_b + t_c, t_d + t_c\}$                         | $t_{clk}^{\prime}-t_{clk}$ | $l \times \Delta_{t_{(b)}} + t'_{clk}$ |

Table 3.1: The time overheads for the different pipelined architectures

the second column of Table 3.1 under  $t'_{clk}$ . In this case, one may be able to reduce  $t_c$  using a suitable method such as pipelining the checker. This will be addressed with more details in Section 3.4.4.

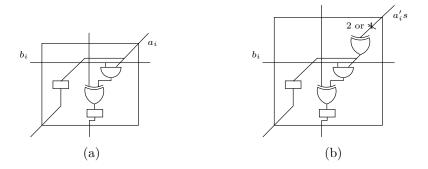

#### 3.3.1 Overheads in PB Operations

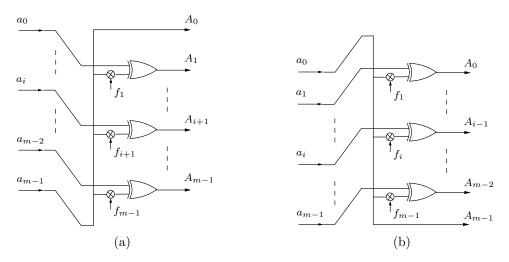

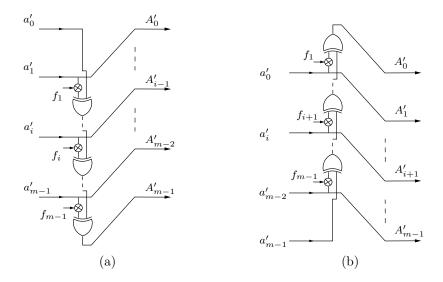

The hardware implementations of the PB scaling or inverse scaling are very inexpensive since they need a cyclic shift to the right or left, which is free of cost in hardware, and  $\omega - 2$  XOR gates, where  $\omega$  is the Hamming weight of F(x). Figure 3.3 shows the implementations of both scalings. As shown in the figure, the propagation delay for one PB scaling or inverse scaling is  $t_X$ , since there is one level of XOR gates in the implementation.

Figure 3.3: (a) Scaling and (b) inverse scaling in PB operations

As mentioned before, the multiplication of a finite field element with  $x^i$  or  $x^{-i}$

can be implemented by i scalings or inverse scalings, respectively. Therefore, the maximum number of XOR gates required for the implementation is  $i(\omega - 2)$ .

To implement a PB arithmetic operation with CED, we need two encoding functions at maximum. Each of them consists of one scaling or inverse scaling. Additionally, we need one decoding function that consists of two scalings or inverse scalings at maximum, except for exponentiation. Therefore,  $4(\omega - 2)$  XOR gates are needed for encoding and decoding functions for a PB arithmetic operation other than exponentiation. We also have:

$$t_e \approx t_X,$$

$$t_d \le 2t_X.$$

#### 3.3.2 Overheads in DB Operations

The hardware implementations of the DB scalings need a cyclic shift to right or left and  $\omega - 2$  XOR gates, where  $\omega$  is the Hamming weight of F(x) (see Figure 3.4). As shown in the figure, the propagation delay for one DB scaling or inverse scaling is  $(\omega - 2)t_X$  due to the propagation delay of the least significant bit of a scaling or the most significant bit of an inverse scaling.

Similar to PB arithmetic operations, for a DB arithmetic operation other than exponentiation,  $4(\omega-2)$  XOR gates are needed for encoding and decoding functions at maximum. We also have:

$$t_e \approx (\omega - 2)t_X,$$

$t_d < 2(\omega - 2)t_X.$

# 3.3.3 Overheads in NB Operations

Squaring and taking the square root of an element represented in NB needs just a cyclic shift to right or left (see Figure 3.5).

Figure 3.4: (a) Scaling and (b) inverse scaling in DB operations

Figure 3.5: (a) Squaring and (b) taking the square root in NB operations

Therefore, squaring and taking the square root have no area and time overhead in a hardware implementation and we have:

$$t_e = t_d = 0.$$

The area overheads for pipeline implementations of PB, DB and NB  $GF(2^m)$

arithmetic operations with the proposed CED are summarized in Table 3.2. It is worth mentioning that the added buffer is m bits long. Also, m XOR gates and one m-input OR gate are needed in the equality checker unit. Note that for all practical values of m, either a trinomial ( $\omega = 3$ ) or a pentanomial ( $\omega = 5$ ) can be found as the field defining polynomial [59].

|                       |              | $PB^1$          | $\mathrm{DB^1}$ | NB |

|-----------------------|--------------|-----------------|-----------------|----|

| Maximum area overhead | m-bit Buffer | 1               | 1               | 1  |

|                       | 2-input XOR  | $(m+4\omega-8)$ | $(m+4\omega-8)$ | m  |

|                       | m-input OR   | 1               | 1               | 1  |

Table 3.2: The area overheads of PB, DB and NB arithmetic operations with the proposed CED

# 3.4 A Closer Look at Polynomial, Dual and Normal Bases Multipliers with CED

In this section, two semi-systolic multipliers for PB and DB bases and two such multipliers for NB basis are presented. Then the time and area complexities of each of them with or without CED are given.

# 3.4.1 A Systolic PB Multiplier with CED

Let  $A, B, C \in GF(2^m)$ . Then the result of their PB multiplication is as follows:

$$C = A.B \mod F(x)$$