## Constraint Programming Techniques for Optimal Instruction Scheduling

by

Abid Muslim Malik

A thesis presented to the University of Waterloo in fulfillment of the thesis requirement for the degree of Doctor of Philosophy in Computer Science

Waterloo, Ontario, Canada, 2008 © Abid M. Malik 2008

#### AUTHOR'S DECLARATION

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

Abid Muslim Malik

#### Abstract

Modern processors have multiple pipelined functional units and can issue more than one instruction per clock cycle. This puts great pressure on the instruction scheduling phase in a compiler to expose maximum instruction level parallelism. Basic blocks and superblocks are commonly used regions of code in a program for instruction scheduling. Instruction scheduling coupled with register allocation is also a well studied problem to produce better machine code. Scheduling basic blocks and superblocks optimally with or with out register allocation is NPcomplete, and is done sub-optimally in production compilers using heuristic approaches. In this thesis, I present a constraint programming approach to the superblock and basic block instruction scheduling problems for both idealized and realistic architectures. Basic block scheduling with register allocation with no spilling allowed is also considered. My models for both basic block and superblock scheduling are optimal and fast enough to be incorporated into production compilers. I experimentally evaluated my optimal schedulers on the SPEC 2000 integer and floating point benchmarks. On this benchmark suite, the optimal schedulers were very robust and scaled to the largest basic blocks and superblocks. Depending on the architectural model, between 99.991% to 99.999% of all basic blocks and superblocks were solved to optimality. The schedulers were able to routinely solve the largest blocks, including blocks with up to 2600 instructions. My results compare favorably to the best previous optimal approaches, which are based on integer programming and enumeration. My approach for basic block scheduling without allowing spilling was good enough to solve 97.496% of all basic blocks in the SPEC 2000 benchmark. The approach was able to solve basic blocks as large as 50 instructions for both idealized and realistic architectures within reasonable time limits. Again, my results compare favorably to recent work on optimal integrated code generation, which is based on integer programming.

#### Acknowledgments

First, I would like to thank my supervisor, Peter van Beek, for his sincere guidance, mentoring and support throughout my work as a graduate student at the University of Waterloo. I would like to thank my examination committee members Jose Nelson Amaral, Peter Buhr, Gordon Cormack and Todd Veldhuizen for their very useful suggestions on my work. Special thanks to Jim McInnes and Marin Litoiu from the IBM Canada for their support during my Ph.D work. Thanks to Tyrel Russell and Michael Chase for their contribution in the work.

A big thank you to my wife, Jouweeriea, for encouraging and supporting me in my research and also helping me to balance between school and other aspects of my life.

I would like to thank my mother Zohra, my brothers Adil, Tariq, Zahid and Shahid, my nieces Saba and Maha, my nephews Ali and Ahmad and my sister Farah for their constant support.

I would like to thank a very special person, my two year old son Abdullah, for providing happiness in the last two years of my Ph.D work with his cute smiles.

This work was supported financially by IBM CAS and IBM Ph.D fellowships.

Dedicated to my wife Jouweeriea Abid and my son Abdullah Abid.

# Contents

| 1        | Intr | roduction                                                 | 1  |

|----------|------|-----------------------------------------------------------|----|

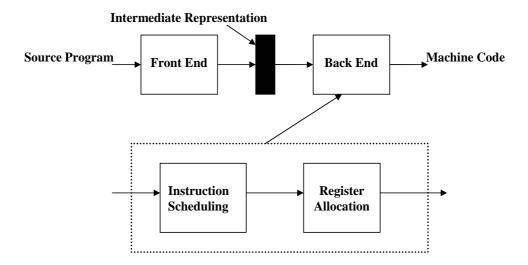

|          | 1.1  | Compilation phase                                         | 1  |

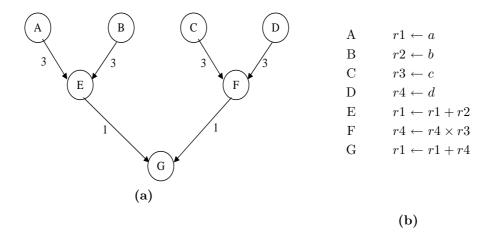

|          | 1.2  | Instruction scheduling                                    | 1  |

|          | 1.3  | Importance of the work                                    | 5  |

|          | 1.4  | Main motivation behind the work                           | 6  |

|          | 1.5  | Contributions                                             | 6  |

|          | 1.6  | Origin of the thesis                                      | 7  |

|          | 1.7  | Organization of the thesis                                | 8  |

| <b>2</b> | Bac  | kground                                                   | 9  |

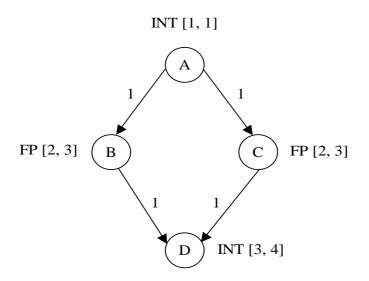

|          | 2.1  | Fundamental constraints                                   | 9  |

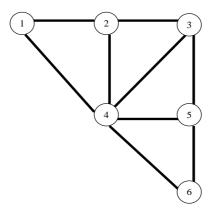

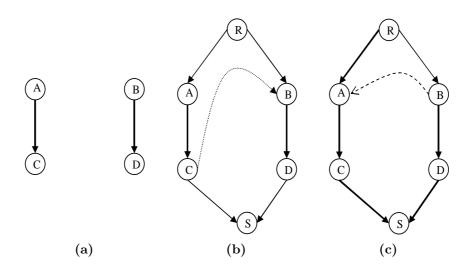

|          |      | 2.1.1 Data dependency constraints                         | 9  |

|          |      | 2.1.2 Control constraints                                 | 10 |

|          |      | 2.1.3 Resource constraints                                | 11 |

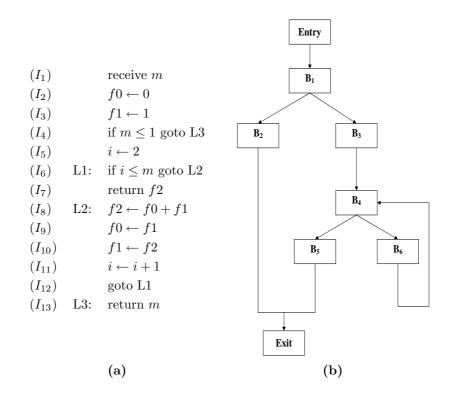

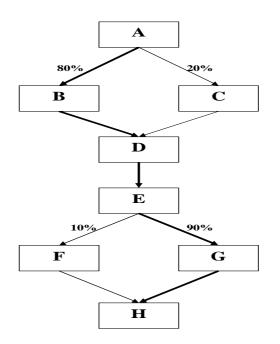

|          | 2.2  | Instruction scheduling regions                            | 11 |

|          | 2.3  | Target machine architecture                               | 15 |

|          | 2.4  | Basic block scheduling                                    | 17 |

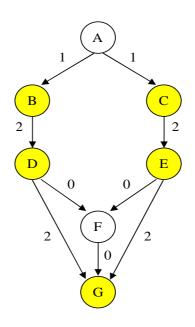

|          | 2.5  | Superblock scheduling                                     | 18 |

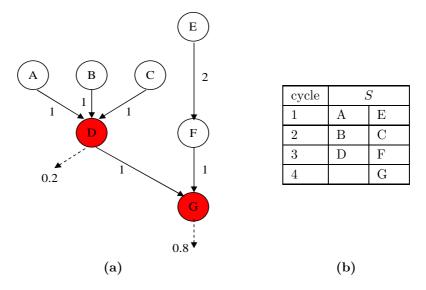

|          | 2.6  | List scheduling                                           | 20 |

|          |      | 2.6.1 Common scheduling heuristics                        | 20 |

|          | 2.7  | Instruction scheduling under register pressure constraint | 23 |

|          | 2.8  | Constraint programming                                    | 26 |

|          | 2.9  | Summary                                                   | 29 |

|          |      |                                                           |    |

| 3 | Bas | ic Blo | ck Scheduling for Multi-Issue Processors                                                | 30 |

|---|-----|--------|-----------------------------------------------------------------------------------------|----|

|   | 3.1 | Relate | ed work                                                                                 | 30 |

|   |     | 3.1.1  | Approaches for optimal solutions                                                        | 30 |

|   | 3.2 | Const  | raint programming model for basic block scheduling $\ldots \ldots \ldots \ldots \ldots$ | 33 |

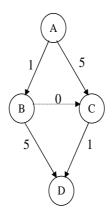

|   |     | 3.2.1  | Latency constraints                                                                     | 33 |

|   |     | 3.2.2  | Resource constraints                                                                    | 35 |

|   |     | 3.2.3  | Distance constraints                                                                    | 35 |

|   |     | 3.2.4  | Predecessor and successor constraints                                                   | 37 |

|   |     | 3.2.5  | Safe pruning constraint                                                                 | 38 |

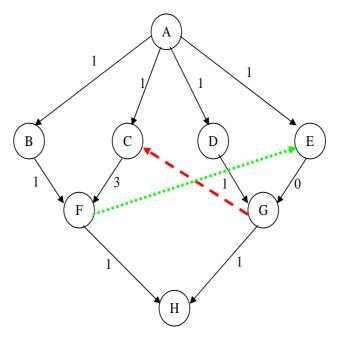

|   |     | 3.2.6  | Dominance constraints                                                                   | 40 |

|   | 3.3 | Addit  | ional constraints for realistic architectures                                           | 43 |

|   |     | 3.3.1  | Issue width constraint                                                                  | 43 |

|   |     | 3.3.2  | Non-fully pipelined processor constraint                                                | 43 |

|   |     | 3.3.3  | Serializing instruction constraint                                                      | 45 |

|   | 3.4 | Solvin | g an instance                                                                           | 46 |

|   | 3.5 | Exper  | imental evaluation                                                                      | 47 |

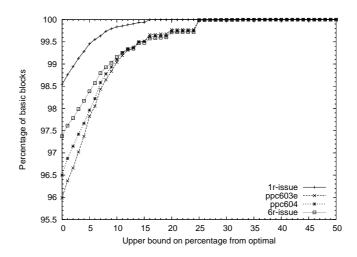

|   |     | 3.5.1  | Experiments for idealized architectural models                                          | 48 |

|   |     | 3.5.2  | Experiments for realistic architectural models                                          | 54 |

|   | 3.6 | Summ   | nary                                                                                    | 55 |

| 4 | Sup | erbloc | k Scheduling for Multi-Issue Processors                                                 | 61 |

|   | 4.1 | Relate | ed work                                                                                 | 61 |

|   |     | 4.1.1  | Scheduling heuristics                                                                   | 61 |

|   |     | 4.1.2  | Approaches for optimal solutions                                                        | 62 |

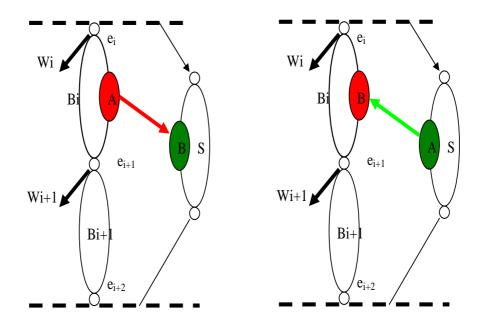

|   | 4.2 | Const  | raint programming model for superblock scheduling                                       | 64 |

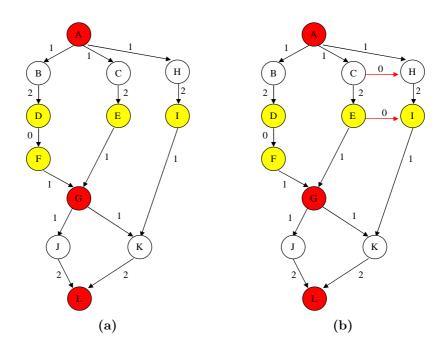

|   |     | 4.2.1  | Dominance constraints                                                                   | 64 |

|   |     | 4.2.2  | Upper bound distance constraints                                                        | 68 |

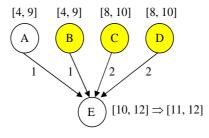

|   |     | 4.2.3  | Improved lower and upper bounds for cost variables                                      | 70 |

|   | 4.3 | Solvin | g an instance                                                                           | 73 |

|   |     |        |                                                                                         |    |

|   | 4.4    | Experi   | mental evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 76  |

|---|--------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

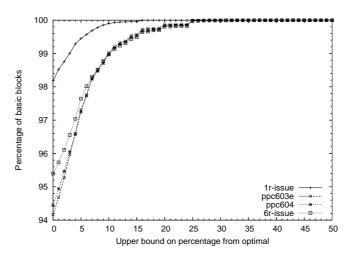

|   |        | 4.4.1    | Experiments for idealized architectural models $\hfill \ldots \hfill \ldots$ | . 76  |

|   |        | 4.4.2    | Experiments for realistic architectural models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 82  |

|   | 4.5    | Summ     | ary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 94  |

| 5 | Bas    | ic Bloc  | ck Scheduling without Spilling for Multi-Issue Processors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 95    |

|   | 5.1    | Introd   | uction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 95  |

|   | 5.2    | Relate   | d work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 97  |

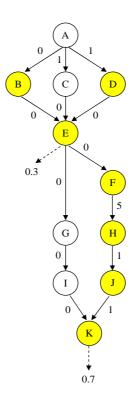

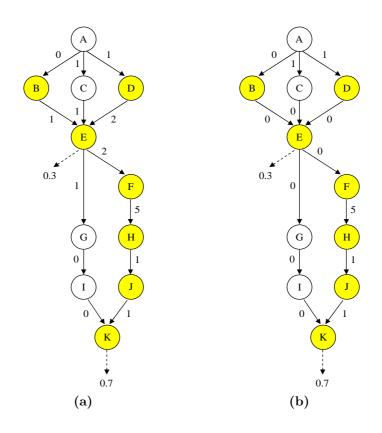

|   | 5.3    | Minim    | um register instruction sequencing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 100 |

|   |        | 5.3.1    | Properties of a lineage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 101 |

|   |        | 5.3.2    | Heuristic for lineage formation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 102 |

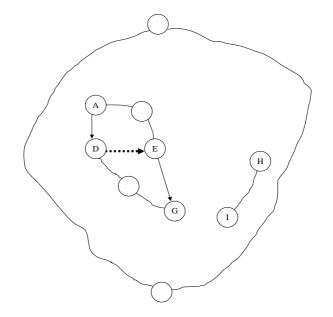

|   |        | 5.3.3    | Lineage interference graph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 104 |

|   |        | 5.3.4    | Instruction scheduling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 105 |

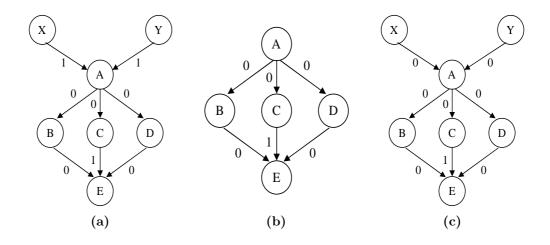

|   | 5.4    | My sol   | lution for the problem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 106 |

|   | 5.5    | Search   | ing for a solution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 111 |

|   | 5.6    | Experi   | mental evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 115 |

|   |        | 5.6.1    | Experiments for realistic architectural models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 116 |

|   | 5.7    | Summ     | ary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 123 |

| 6 | Cor    | nclusion | a and Future Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 124   |

|   | 6.1    | Conclu   | sion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 124 |

|   | 6.2    | Applic   | ations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 126 |

|   | 6.3    | Future   | Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 126 |