# Thin-Film Transistor Integration for Biomedical Imaging and AMOLED Displays

by

G. Reza Chaji

A thesis

presented to the University of Waterloo

in fulfillment of the

thesis requirement for the degree of

Doctor of Philosophy

in

Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2008

© G. Reza Chaji 2008

## **AUTHOR'S DECLARATION**

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### **Abstract**

Thin film transistor (TFT) backplanes are being continuously researched for new applications such as active-matrix organic light emitting diode (AMOLED) displays, sensors, and x-ray imagers. However, the circuits implemented in presently available fabrication technologies including poly silicon (poly-Si), hydrogenated amorphous silicon (a-Si:H), and organic semiconductor, are prone to spatial and/or temporal non-uniformities.

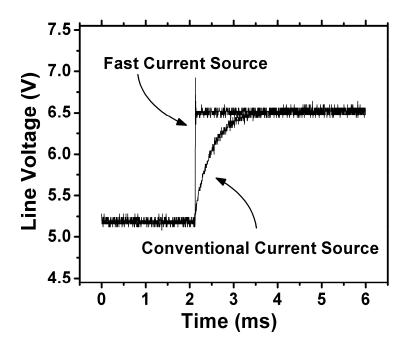

While current-programmed active matrix (AM) can tolerate mismatches and non-uniformity caused by aging, the long settling time is a significant limitation. Consequently, acceleration schemes are needed and are proposed to reduce the settling time to 20 µs. This technique is used in the development of a pixel circuit and system for biomedical imager and sensor. Here, a metal-insulator-semiconductor (MIS) capacitor is adopted for adjustment and boost of the circuit gain. Thus, the new pixel architecture supports multi-modality imaging for a wide range of applications with various input signal intensities. Also, for applications with lower current levels, a fast current-mode line driver is developed based on positive feedback which controls the effect of the parasitic capacitance. The measured settling time of a conventional current source is around 2 ms for a 100-nA input current and 200-pF parasitic capacitance whereas it is less than 4 µs for the driver presented here.

For displays needed in mobile devices such as cell phones and DVD players, another new driving scheme is devised that provides for a high temporal stability, low-power consumption, high tolerance of temperature variations, and high resolution. The performance of the new driving scheme is demonstrated in a 9-inch fabricated display intended for DVD players. Also, a multi-modal imager pixel circuit is developed using this technique to provide

for gain-adjustment capability. Here, the readout operation is not destructive, enabling the use of low-cost readout circuitry and noise reduction techniques.

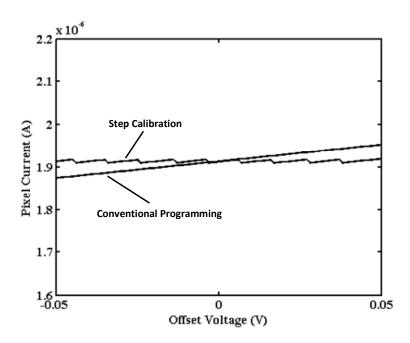

In addition, a highly stable and reliable driving scheme, based on step calibration is introduced for high precision displays and imagers. This scheme takes advantage of the slow aging of the electronics in the backplane to simplify the drive electronics. The other attractive features of this newly developed driving scheme are its simplicity, low-power consumption, and fast programming critical for implementation of large-area and high-resolution active matrix arrays for high precision.

#### Acknowledgements

I would like to thank Professor Arokia Nathan for his generosity in sharing his time, knowledge, and experience during our valuable discussions. Also, I am grateful to him for his encouragement, support, and guidance during the course of my studies, particularly during more challenging times. Also, I want to express my gratitude to the committee members: Prof. Ching Tang, Prof. Manoj Sachdev, Prof. James Barby, Prof. J.D. Martin, and Prof. Sherman Shen.

I am always grateful to my wife, Malihe, for her invaluable kindness, support, love, and inspiration. This work would be far from completion without her encouragement which has enabled me to literally work day and night. I also, would like to thank my parents, Mohammad Chaji and Kobra Khorashadi, for their endless love and support. In addition, I am thankful to my in-laws parents, Moslem Fakhimi and Fatemeh Chaji, for their encouragement and trust.

I was lucky to work at a highly professional yet friendly group, Giga-to-Nano Laboratories. This work has been accomplished with the technical support of the members of this group. I am obliged to all my colleagues, particularly, Dr. Denis Striakhilev for fabricating my circuits and our valuable discussions, Dr. Shahin Ashtiani for our insightful discussion and significant collaboration, Dr. Peyman Servati for assisting in setting up the simulation environment and our insightful discussions, Mohammad Esmaillie Rad for coaching me in the fabrication process, Dr. Majid Gharghi for the inspiring technical and non-technical discussions, Nader Safavian for our insightful discussion and collaboration, Stefan Alexander and Clement NG for helping me in testing and evaluating the circuits, and

Richard Barber for providing a pleasant and professional environment in the Giga-to-Nano Lab. Also, I would like to thanks my friends who have made my life a more joyful experience in Waterloo: Dr. Kambiz Khodaiary, Dr. Daryoosh Saeedkia, Mazeiar Salehi, Dr. Ali Naderian, Arash Fomani, Maryam Moradi, Dr. Issac Chan, Javid Jaffari, and many others.

I am indebted to the professors who taught me invaluable knowladge during their courses.

I am extremely grateful to my supervisor during my studies at the University of Tehran, Prof. S. Mehdi Fakhraie, for his endless kindness, inspiration, and support.

Additionally, I want to thank the University of Waterloo administration for providing me with the opportunity to pursue my Ph.D. studies. Particularly, I would like to express my thanks to Wendy Boles, Lisa Hendels, and Annette Dietrich, of ECE Graduate Office.

I would like to acknowledge the support of Natural Science and Engineering Research Council (NSERC) of Canada, Ontario Center of Excellence (OCE), and Ontario Graduate Scholarship (OGS). Also, I am grateful to Canada Micro System (CMC) and Ignis Innovation Inc. for assisting me in further developing my research.

# **Dedication**

To my lovely wife and kind parents

# **Table of Contents**

| Abstract                                        | iii      |

|-------------------------------------------------|----------|

| Acknowledgements                                | v        |

| Dedication                                      | vii      |

| Table of Contents                               | viii     |

| List of Figures.                                | xi       |

| List of Tables                                  | XVi      |

| Chapter 1 Introduction                          | 1        |

| 1.1 Organic Light Emitting Displays             | 1        |

| 1.2 Flat-Panel Biomedical Imagers               | <i>.</i> |

| 1.3 Backplane Technologies                      | 9        |

| 1.4 Thesis Outline                              | 10       |

| Chapter 2 Specifications and Considerations     | 13       |

| 2.1 Temporal and Spatial Non-Uniformity         | 13       |

| 2.2 Compensation Schemes                        | 16       |

| 2.2.1 Current Driving Scheme                    | 16       |

| 2.2.2 Voltage Driving Scheme                    | 24       |

| 2.3 Design Considerations for AMOLED Displays   | 34       |

| 2.3.1 Lifetime and Yield                        | 34       |

| 2.3.2 Differential Aging and Mura               | 36       |

| 2.3.3 Power Consumption                         | 37       |

| 2.3.4 Aperture Ratio                            | 37       |

| 2.3.5 IR Drop and Ground Bouncing               | 37       |

| 2.3.6 Implementation Cost                       | 38       |

| 2.4 Design Considerations for Flat Panel Imager | 39       |

| 2.4.1 Input Referred Noise and Dynamic Range    | 39       |

| 2.4.2 Implementation Cost                                  | 41  |

|------------------------------------------------------------|-----|

| 2.5 Summery                                                | 41  |

| Chapter 3 Hybrid Voltage-Current Programming               | 43  |

| 3.1 Multi-Modal Biomedical Imaging Pixel Circuit           | 45  |

| 3.2 Multi-Modal Biomedical Sensor Array                    | 49  |

| 3.2.1 Peripheral Circuitries                               | 51  |

| 3.2.2 Measurement Results                                  | 55  |

| 3.2.3 Improved Dynamic Rage                                | 60  |

| 3.2.4 Noise Analysis of CBVP Pixel Circuit                 | 61  |

| 3.3 CBVP AMOLED Pixel Circuit                              | 64  |

| 3.4 Summary                                                | 70  |

| Chapter 4 Enhanced-Settling Current Programming            | 72  |

| 4.1 Positive Feedback                                      | 72  |

| 4.2 Stability and Noise Analysis                           | 75  |

| 4.3 Measurement Results and Discussion                     | 79  |

| 4.4 Self-Calibration of the Current Source                 | 82  |

| 4.5 Summary                                                | 85  |

| Chapter 5 Charge-Based Driving Scheme                      | 86  |

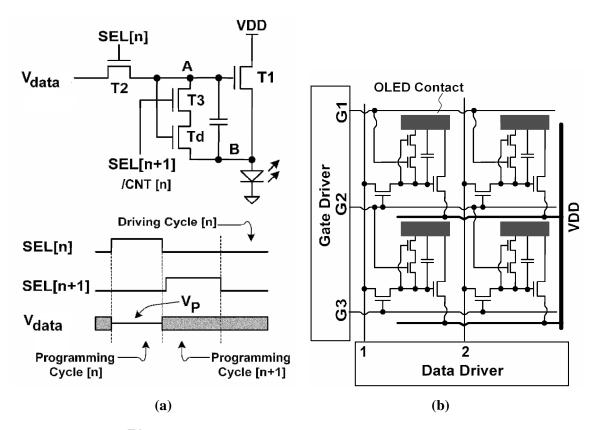

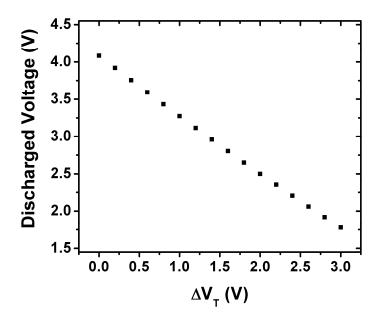

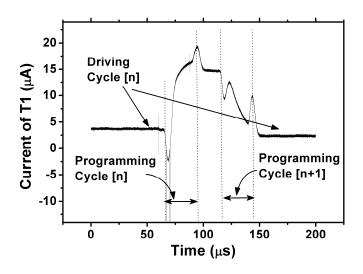

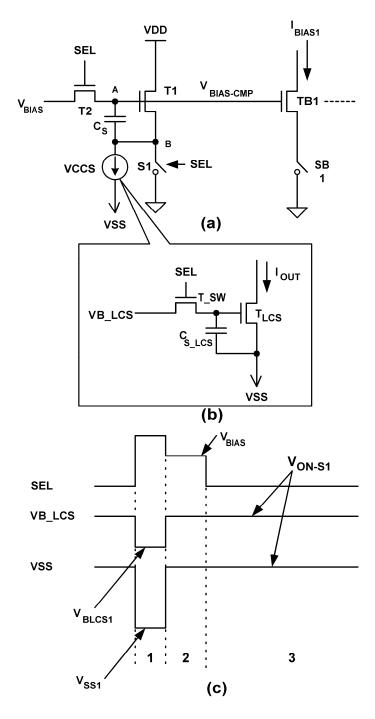

| 5.1 Advance Mobile Technology (AdMo <sup>TM</sup> )        | 87  |

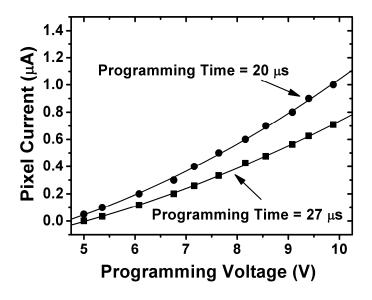

| 5.1.1 Measurement Results                                  | 88  |

| 5.1.2 Implementation of the Relaxation Technique           | 92  |

| 5.1.3 9-Inch AMOLED Display                                | 94  |

| 5.2 Real-Time Biomedical Imaging Pixel Circuit             | 100 |

| 5.2.1 Noise Analysis of Charge-Based Pixel Circuit         | 103 |

| 5.3 Summary                                                | 105 |

| Chapter 6 High Resolution Architectures                    | 107 |

| 6.1 Time Dependent Charge Injection and Clock Feed-Through | 107 |

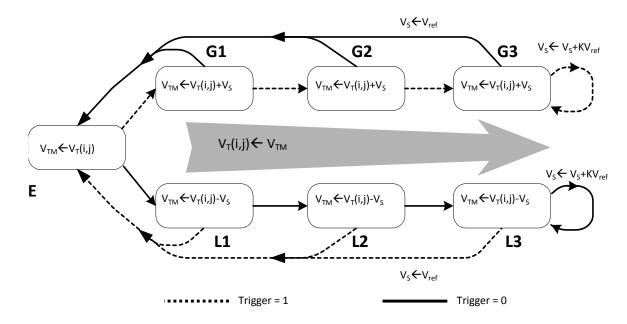

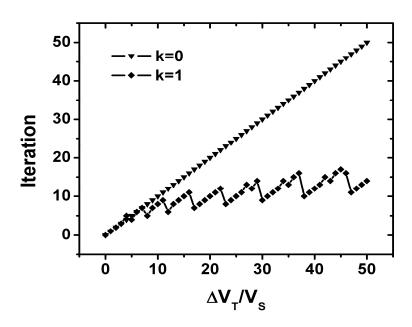

| 6.2 Successive Calibration                                 | 113 |

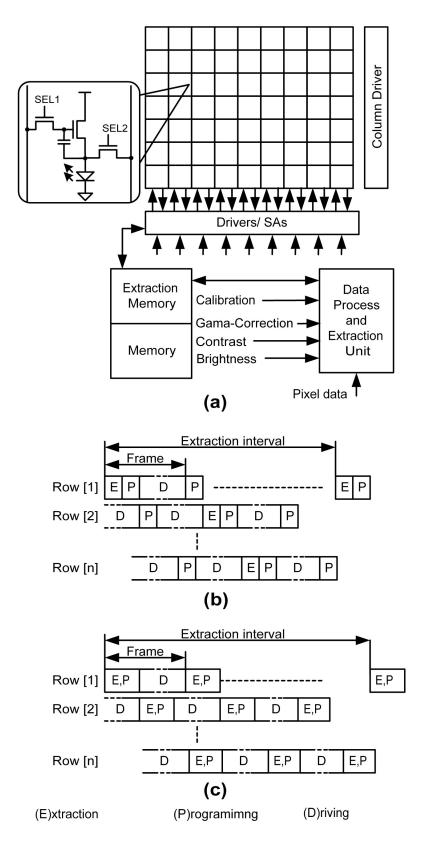

| 6.3 Arrays Structure and Timing                            | 120 |

| 6.3.1 Blanking-time extraction                             | 120 |

| 6.3.2 Simultaneous extraction                              | 122 |

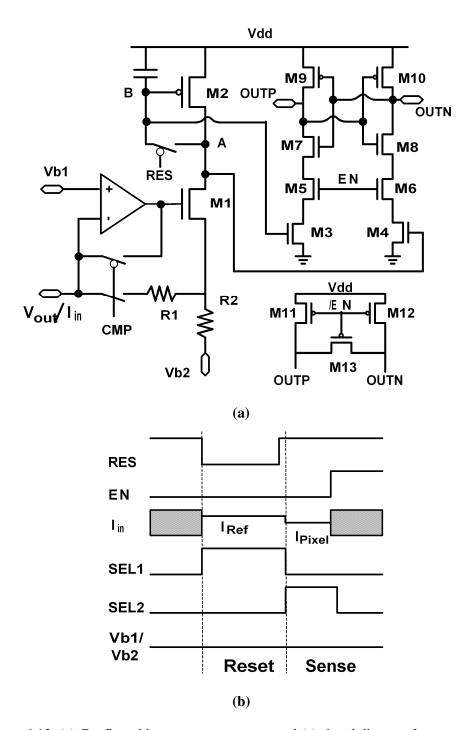

| 6.4 Configurable Current Comparator                        | 122 |

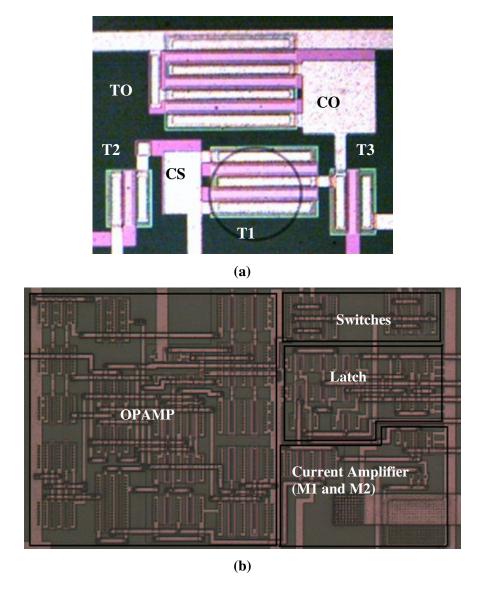

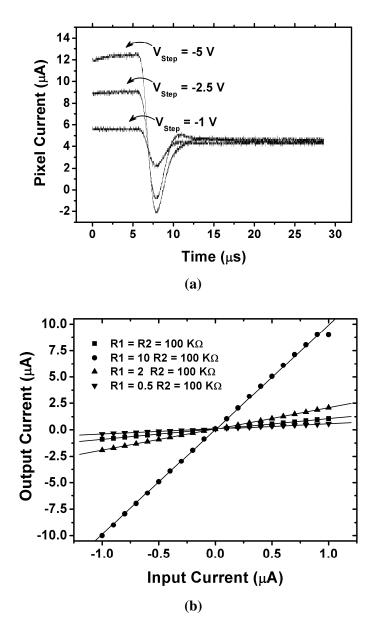

| 6.5 Measurement Results and Discussions                           | 125 |

|-------------------------------------------------------------------|-----|

| 6.6 Summary                                                       | 129 |

| Chapter 7 Conclusion                                              | 130 |

| Appendix A: Enhanced Voltage Driving Schemes                      | 134 |

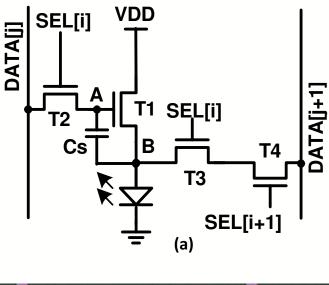

| A. 1 Interleaved Addressing Scheme                                | 134 |

| A.1. 1 3-TFT Pixel Circuit.                                       | 135 |

| Appendix B: Short Term Stress Driving Scheme                      | 142 |

| B. 1 Stability Analysis of Short-Term Stressed TFTs               | 142 |

| B. 2 Stable Circuit Design.                                       | 144 |

| Appendix C: OLED Electrical Calibration                           | 149 |

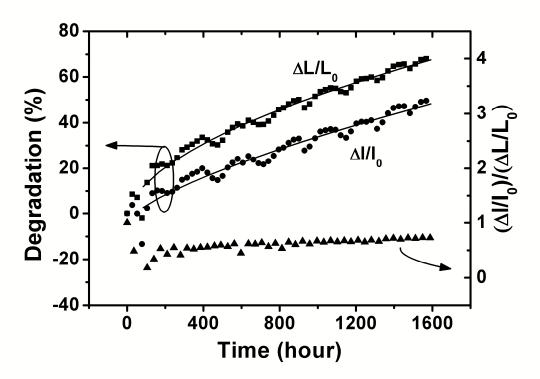

| C. 1 Interdependence Between Electrical and Luminance Degradation | 149 |

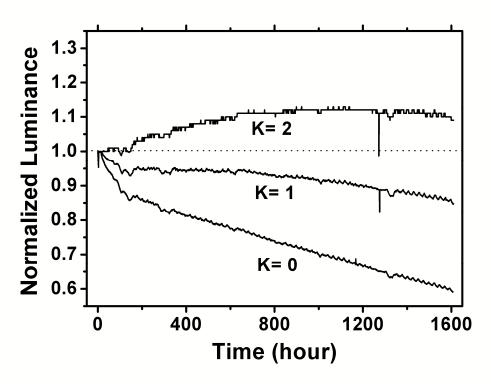

| C. 2 Electrical Compensation of OLED Degradation                  | 150 |

| C. 3 Pixel Circuit for OLED Compensation.                         | 151 |

| Bibliography                                                      | 154 |

# **List of Figures**

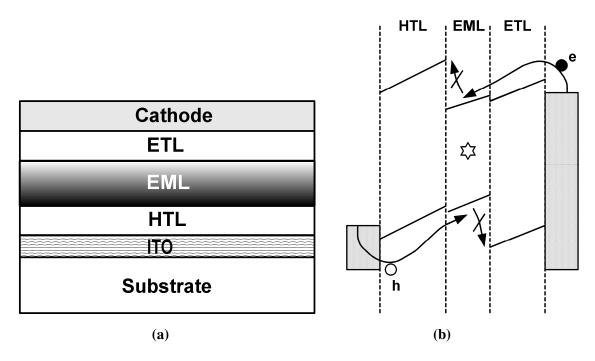

| Figure 1.1: (a) Multi-layer OLED stack structure and (b) OLED banding diagram [8, 10]2                          |

|-----------------------------------------------------------------------------------------------------------------|

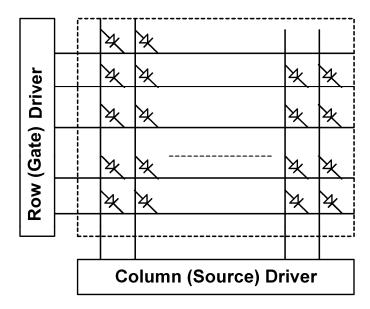

| Figure 1.2: Passive matrix OLED display structure [16].                                                         |

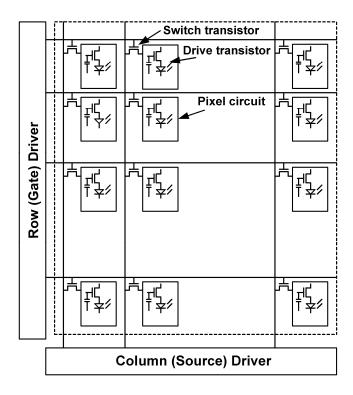

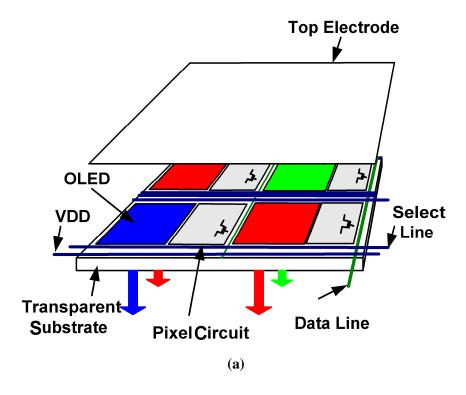

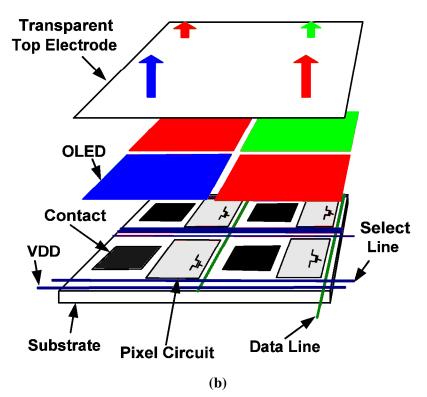

| Figure 1.3: Active matrix OLED (AMOLED) display structure                                                       |

| Figure 1.4: Bottom and top emission AMOLED pixel structure [19, 20]5                                            |

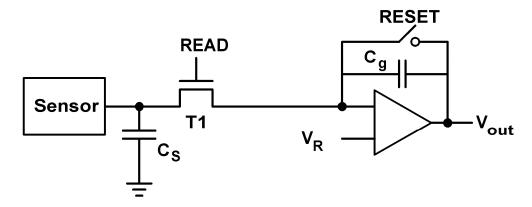

| Figure 1.5: PPS imager pixel circuit [1, 2]6                                                                    |

| Figure 1.6: 3-TFT APS imager pixel circuit [3]                                                                  |

| Figure 1.7: Hybrid active-passive imager pixel circuit [23]                                                     |

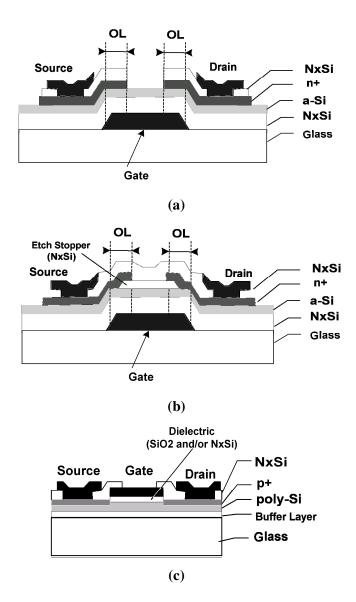

| Figure 2.1: Different TFT structures: (a) bi-layer inverted staggered, (b) tri-layer inverted staggered,        |

| and (c) coplanar                                                                                                |

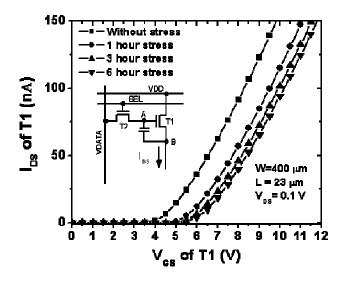

| Figure 2.2: Biased induced $V_T$ -shift (stress condition: $V_{GS} = 10 \text{ V}$ , $V_{DS} = 0.1 \text{ V}$ ) |

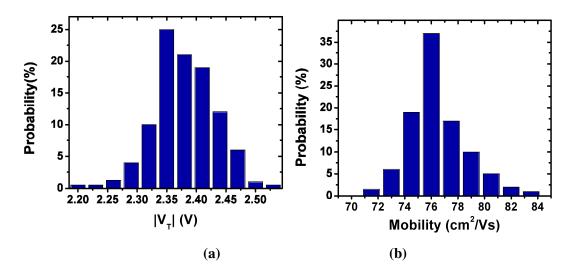

| Figure 2.3: (a) $V_T$ and (b) mobility variation in poly-Si TFTs (adapted from [32])15                          |

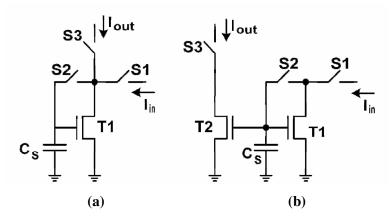

| Figure 2.4: Current programmed pixel circuits; (a) current cell and (b) current mirror                          |

| Figure 2.5: Current programmed pixel circuit (CPPC) for (a) AMOLED displays (adapted from [50])                 |

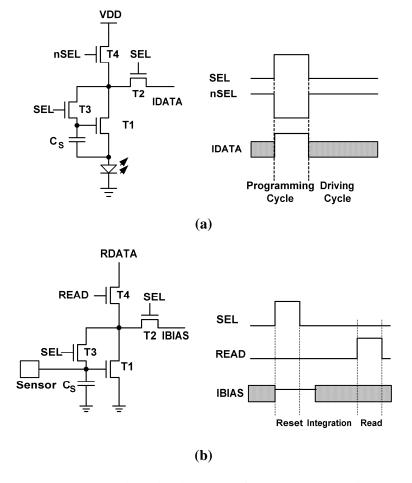

| and (b) flat-panel imagers (adapted from [51]).                                                                 |

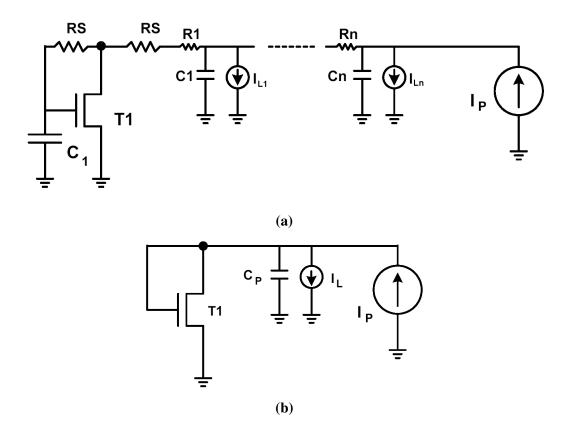

| Figure 2.6: (a) Line model for a column during the programming cycle and (b) its simplified                     |

| equivalent                                                                                                      |

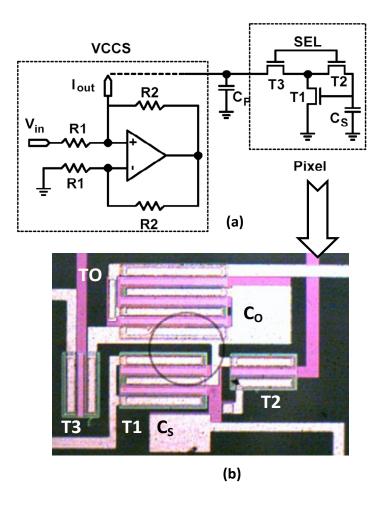

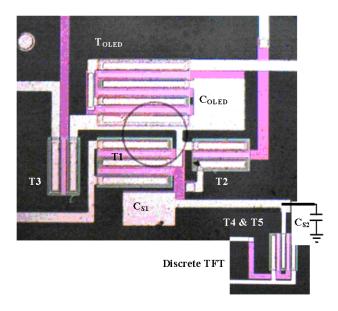

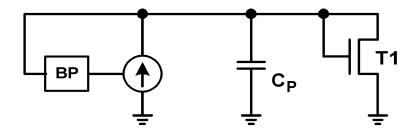

| Figure 2.7: (a) Discrete VCCS and (b) photomicrograph of fabricated current cell in amorphous                   |

| silicon technology                                                                                              |

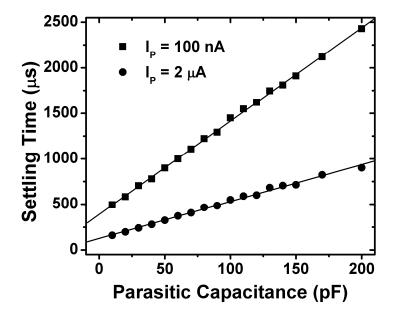

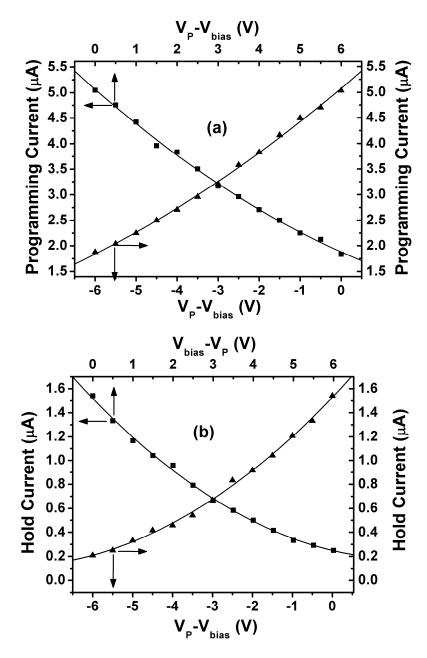

| Figure 2.8: Measured settling time as a function of parasitic capacitance for large and small                   |

| programming currents                                                                                            |

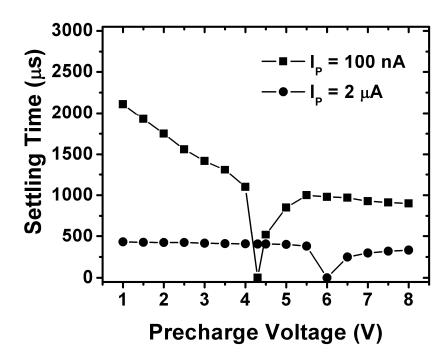

| Figure 2.9: As in Figure 2.8, but settling time is as a function of the pre-charge voltage21                    |

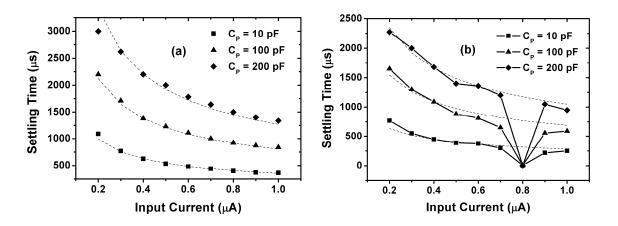

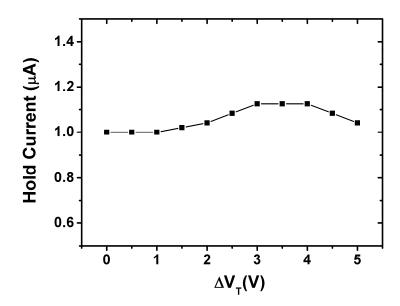

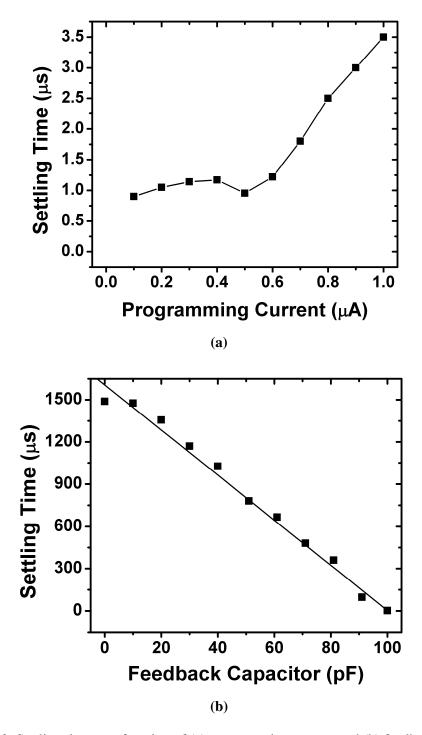

| Figure 2.10: Settling time as a function of the programming current for different parasitic                     |

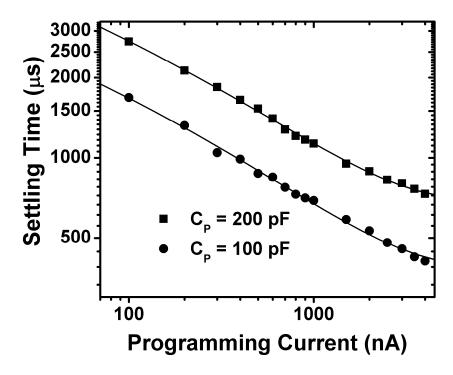

| capacitances                                                                                                    |

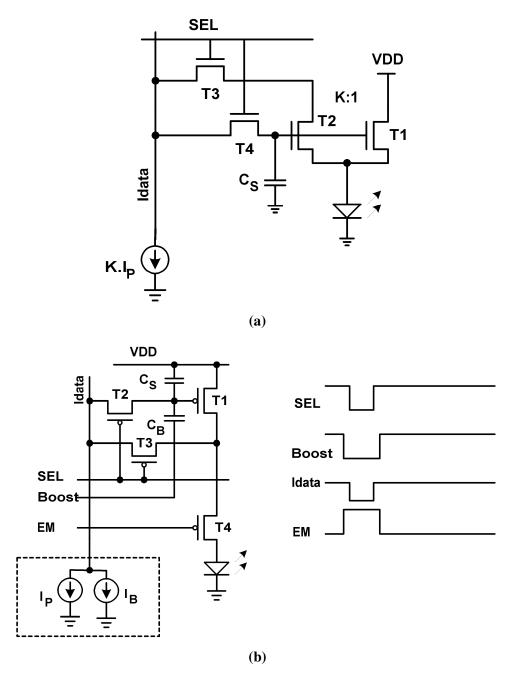

| Figure 2.11: Acceleration driving scheme: (a) scaling (adapted from [14]) and (b) additive (adapted             |

| from [53])                                                                                                      |

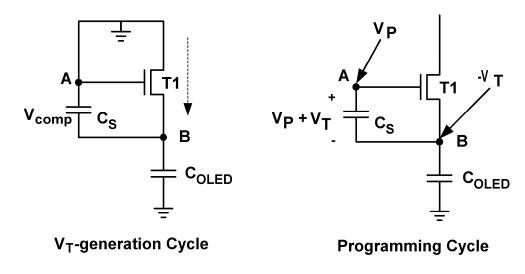

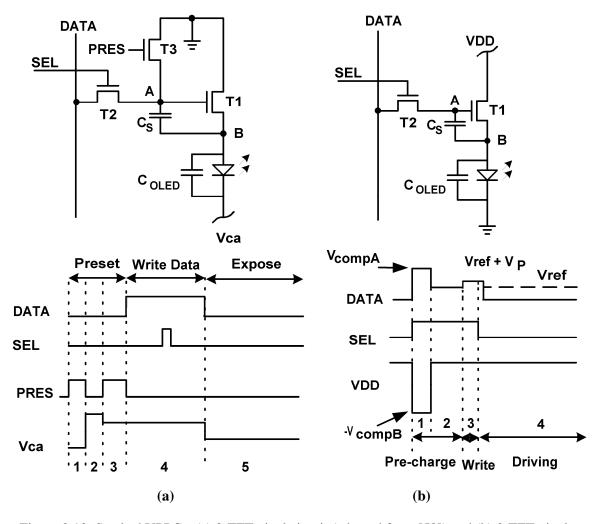

| Figure 2.12: Stacked VPPC configurations during different operating cycles                                      |

| Figure 2.13: Stacked VPPCs; (a) 3-TFT pixel circuit (adapted from [59]) and (b) 2-TFT pixel circuit             |

| (adapted from [60])                                                                                             |

| Figure 2.14: Parallel-compensation VPPC configurations during different operating cycles27                      |

| Figure 2.15: Parallel-compensation VPPCs: (a) 4-TFT pixel circuit (adapted from [61]) and (b) 5-TFT             |

| pixel circuit (adapted from [62])                                                                               |

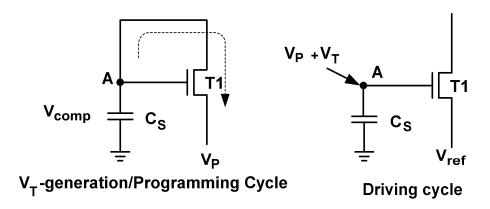

| Figure 2.16: Bootstrapped VPPCs during different operating cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 29  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 2.17: Bootstrapped VPPCs; (a) p-channel pixel circuit (adapted from [63]) and (b) n-channel pixel circuit (adapted | ıel |

| pixel circuit (adapted from [64]).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 29  |

| Figure 2.18: Mirror VPPCs; (a) p-channel pixel circuit (adapted from [65]), (b) complementary pi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | xel |

| circuit (adapted from [66]).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 30  |

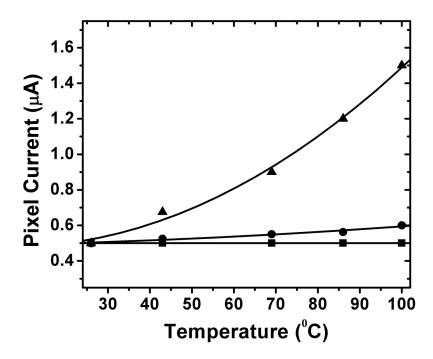

| Figure 2.19: Temperature stability measurement results for stacked VPPC (circles for $C_{OLED} = 6$ pl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | F   |

| and squares for $C_{OLED} = 8 \text{ pF}$ ) and conventional (triangles) driving schemes [68]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 32  |

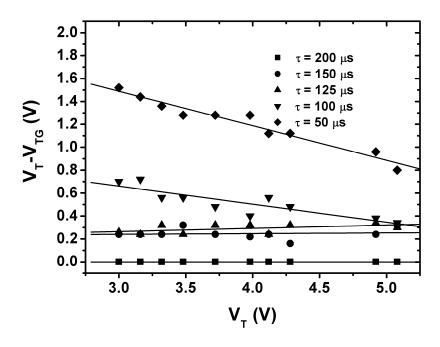

| Figure 2.20: Effect of limited timing budget on V <sub>T</sub> generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 33  |

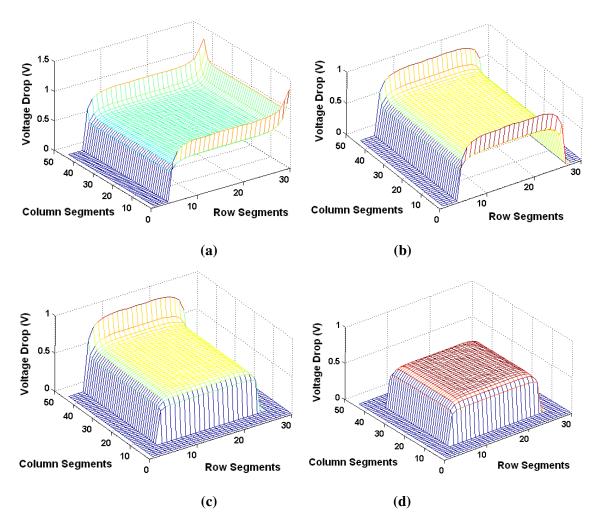

| Figure 2.21: Voltage gradient across the common electrode based on different sides connected to t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | the |

| voltage source: (a) one side, (b) two sides, (c) three sides and (d) four sides.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 38  |

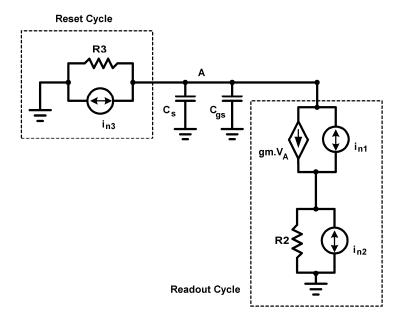

| Figure 2.22: Noise model for 3-TFT APS imager pixel circuit [3].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 40  |

| Figure 3.1: Settling time of current programming as a function of initial voltage: (a) $V_0 = 0$ V and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | (b) |

| $V_0 = 4 \text{ V}.$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 43  |

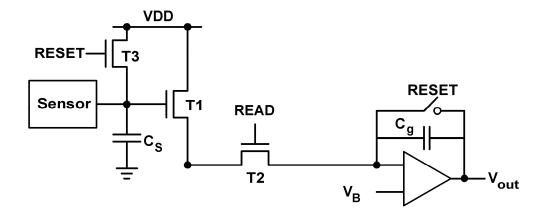

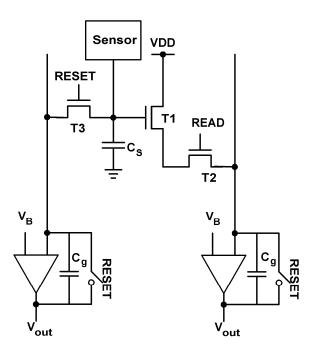

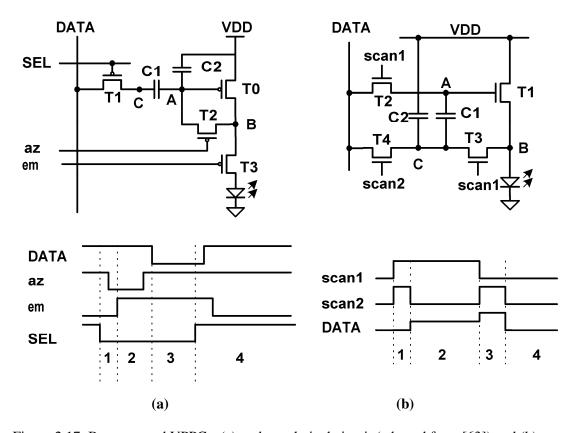

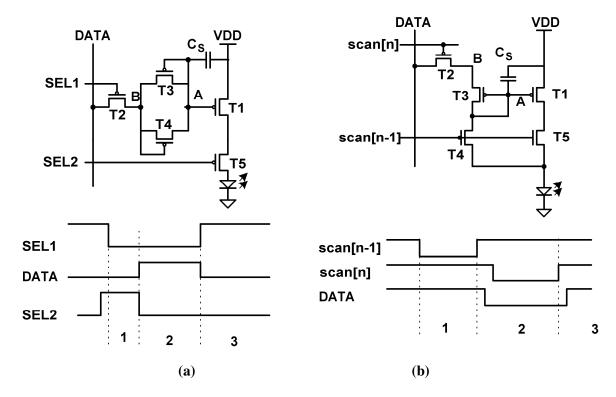

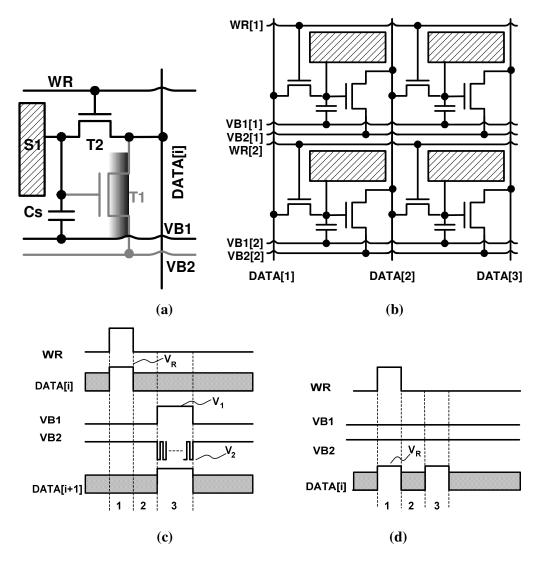

| Figure 3.2: 2-TFT hybrid active-passive pixel sensor circuits: (a) 2-TFT hybrid pixel circuit and (b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | b)  |

| its corresponding array structure along with (c) signal diagrams for active readout (low intensity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

| sensor signals) and (d) passive readout (high intensity sensor signals) mode signal diagram. The g                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ray |

| components are used only in the active readout mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 44  |

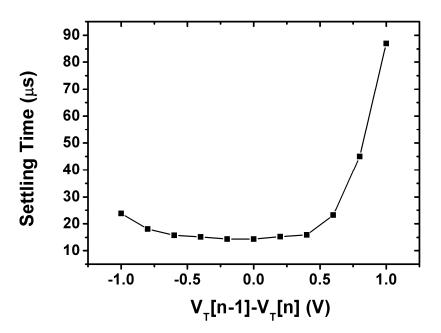

| Figure 3.3: Settling time of CBVP pixel circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 45  |

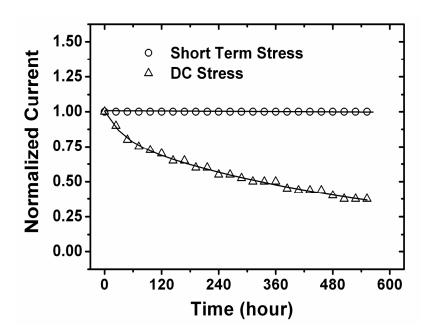

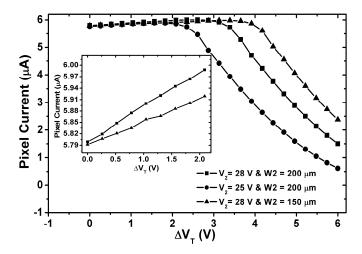

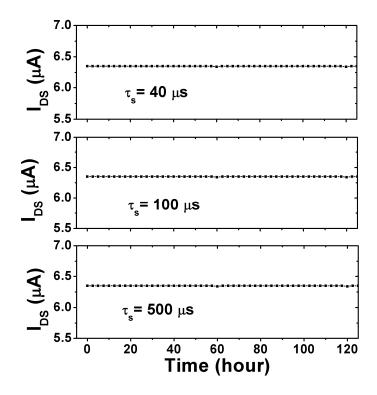

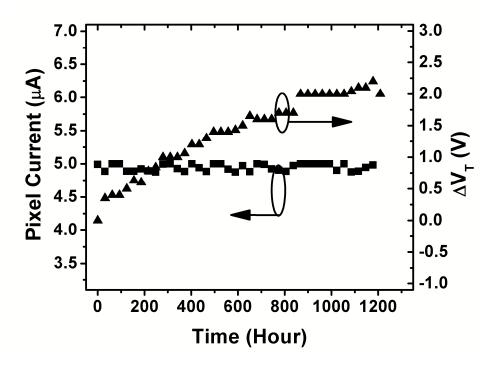

| Figure 3.4: Stability of the pixel current (here, voltage programming is used for DC biasing)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 46  |

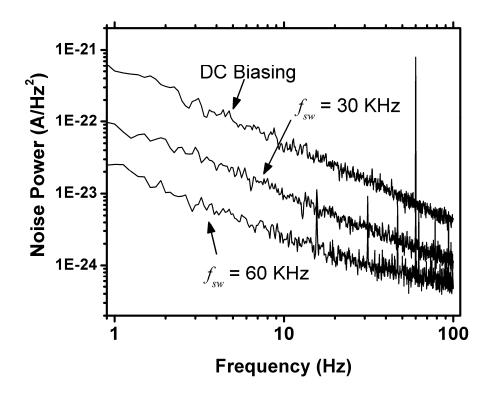

| Figure 3.5: Pixel output current noise using different biasing techniques.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 47  |

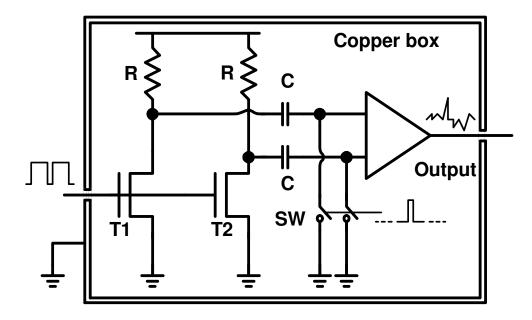

| Figure 3.6: Noins measurement setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 48  |

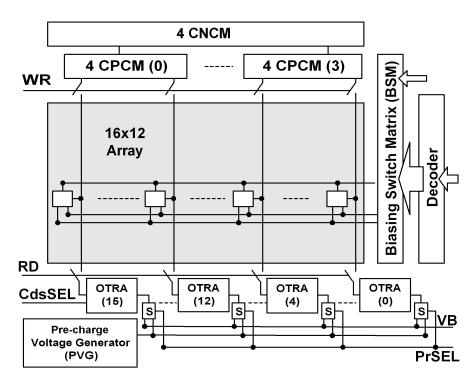

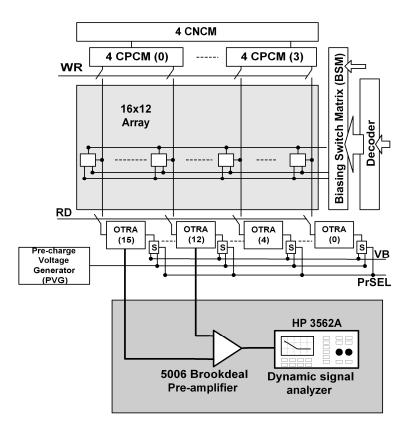

| Figure 3.7: Block diagram of the micro-array biosensor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 50  |

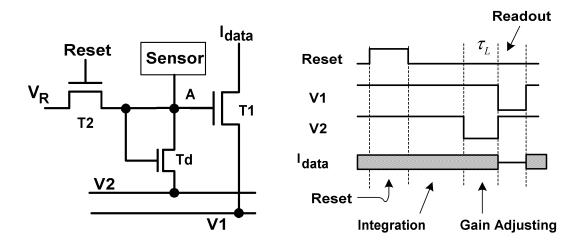

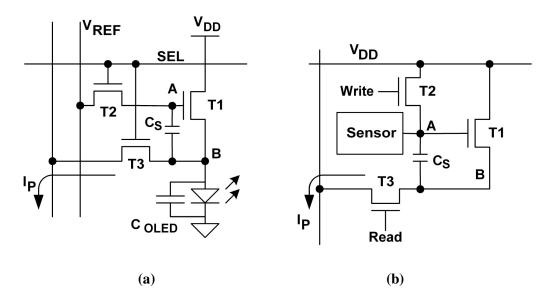

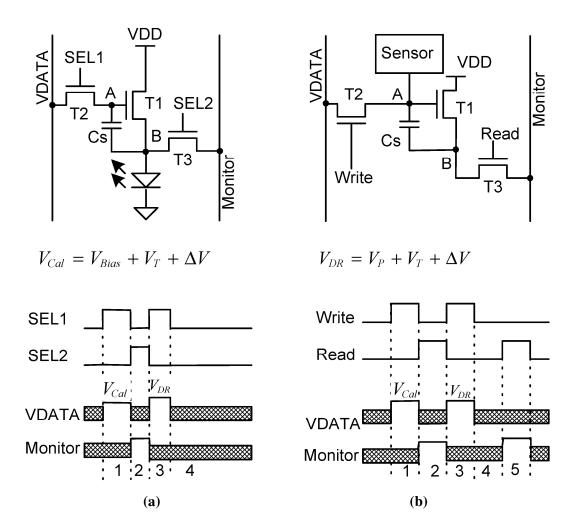

| Figure 3.8: Pixel circuit and corresponding signal diagram for different detection modes (* for sor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ne  |

| detection modes such as voltammetry a time variant voltage should be applied to $V_{\text{ref}}$ )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 51  |

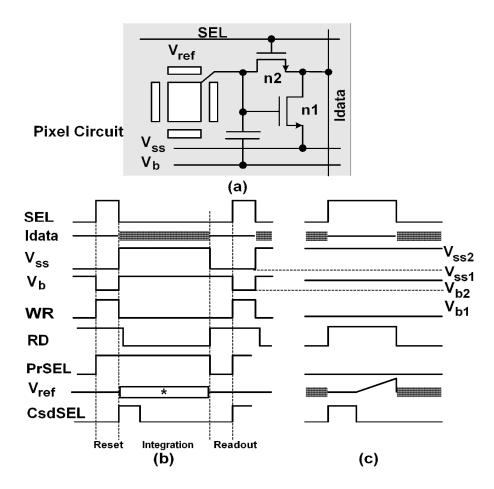

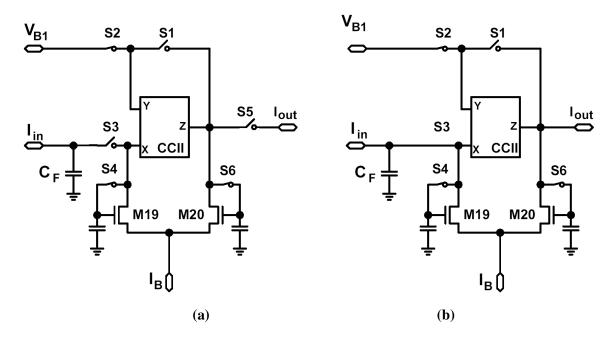

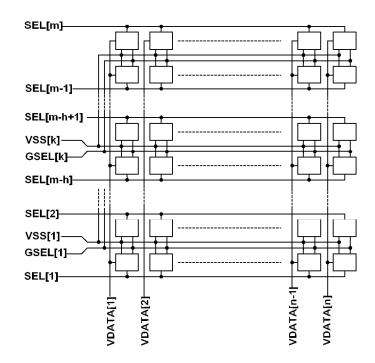

| Figure 3.9: Biasing switch matrix (BSM) circuit diagram.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 52  |

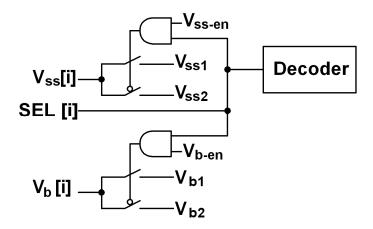

| Figure 3.10: (a) NMOS and (b) PMOS calibrated current sources.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 52  |

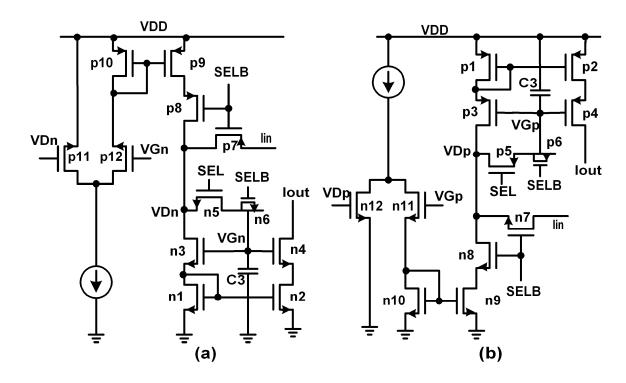

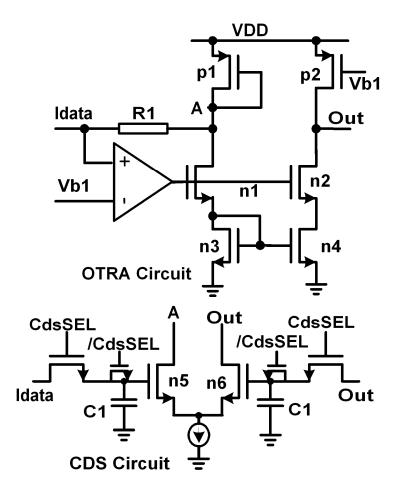

| Figure 3.11: OTRA circuit diagram.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 53  |

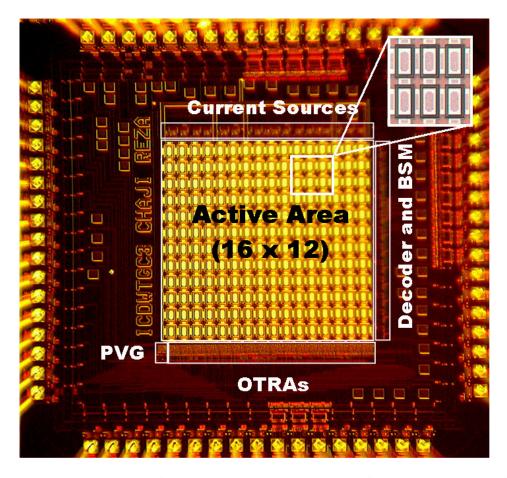

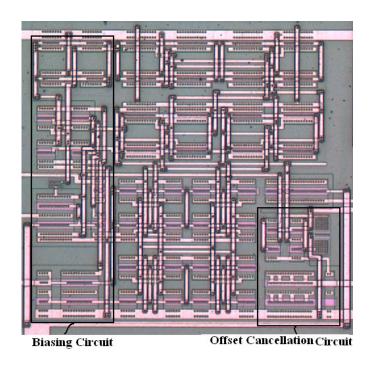

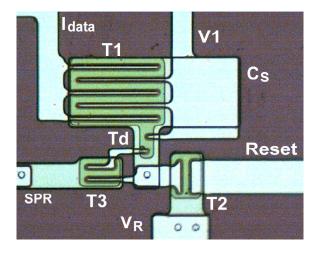

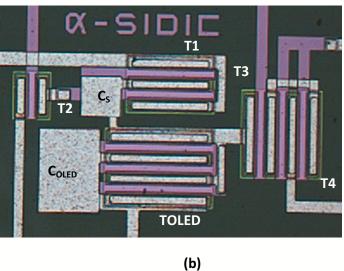

| Figure 3.12: Photomicrograph of the micro-sensor and a 3x2 magnified pixel pads surrounded by                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

| reference pads.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 54  |

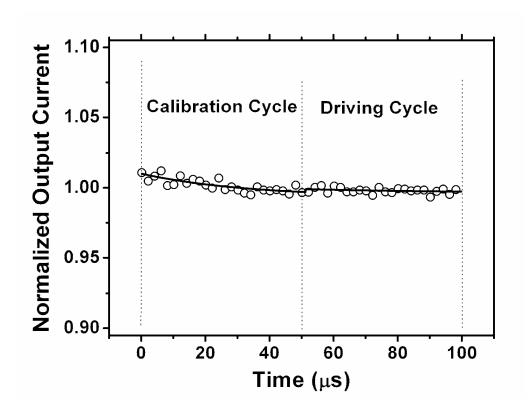

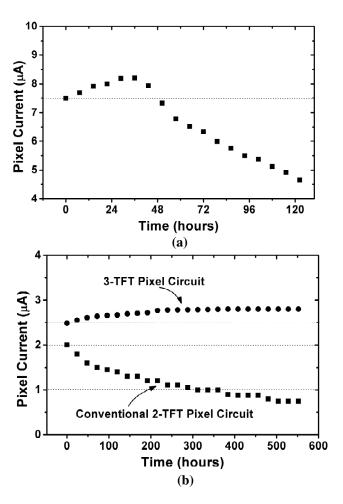

| Figure 3.13: Current stability measurement for the calibrated current sources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 56  |

| Figure 3.14: Noise measurement setup used for the biomedical sensor array                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 57  |

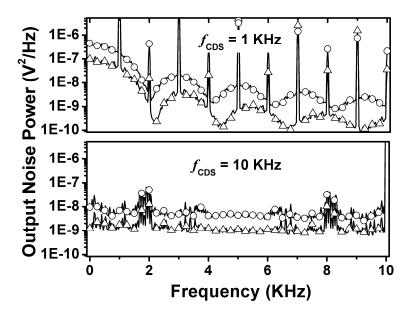

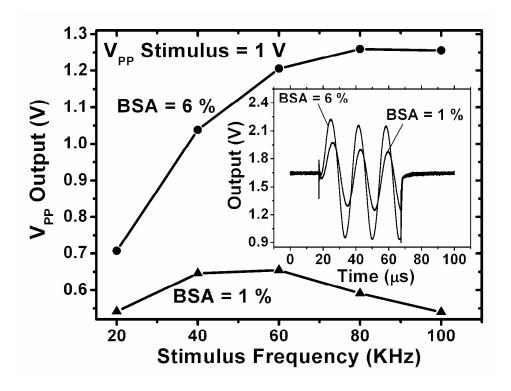

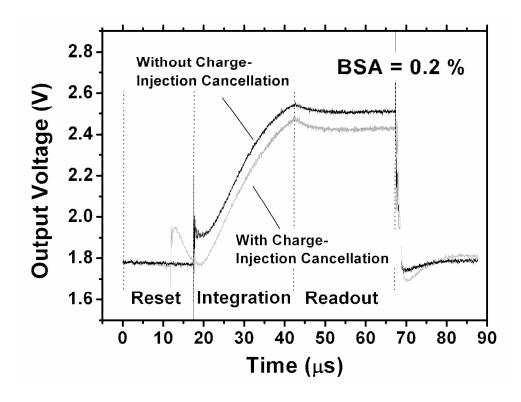

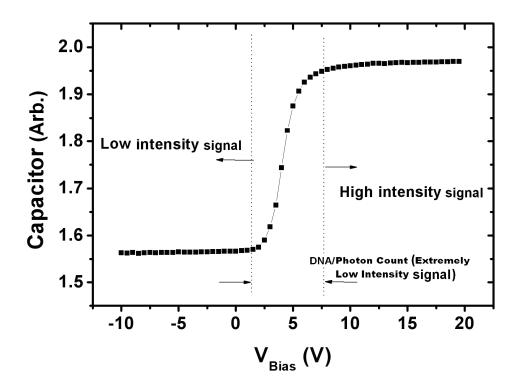

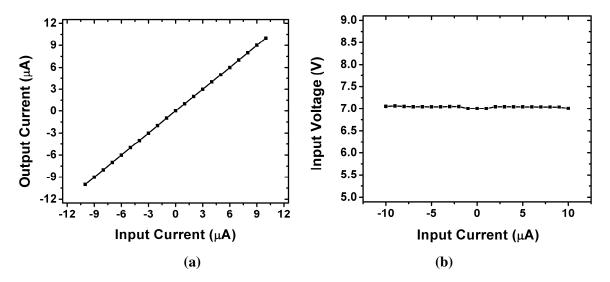

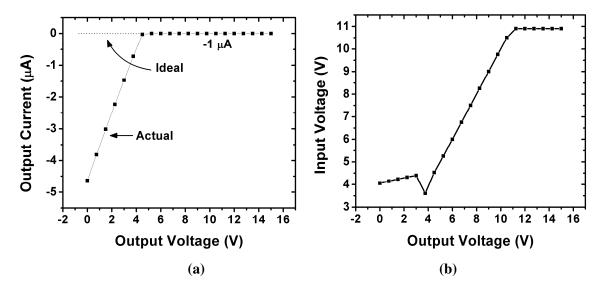

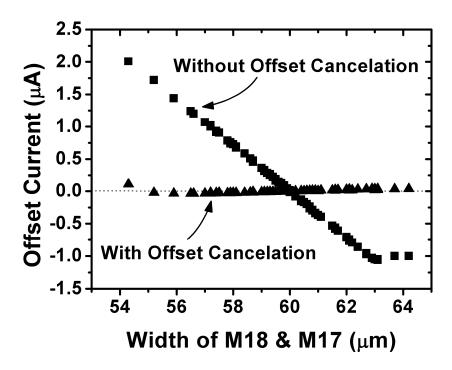

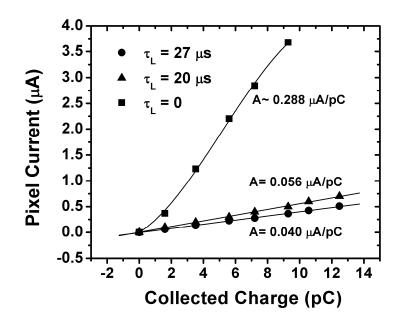

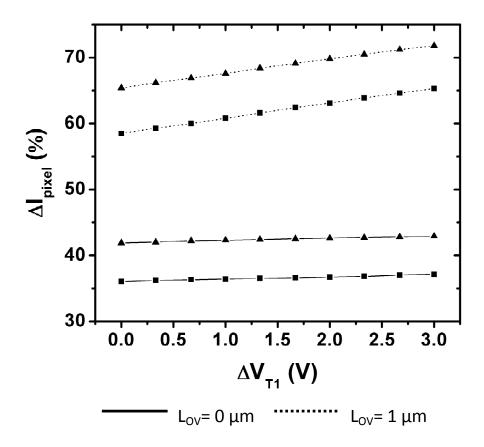

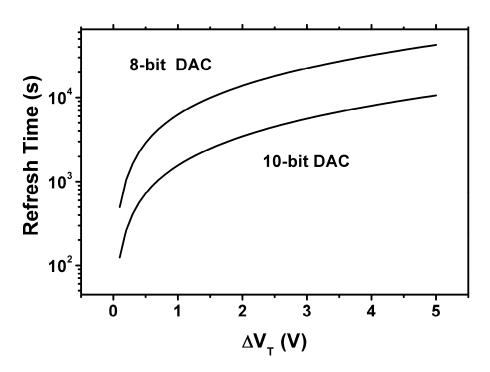

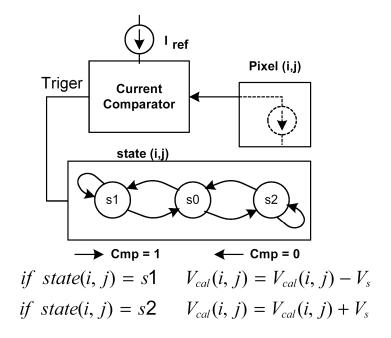

| Figure 3.15: Measured noise performance of the micro-array with different noise reduction techniques      |

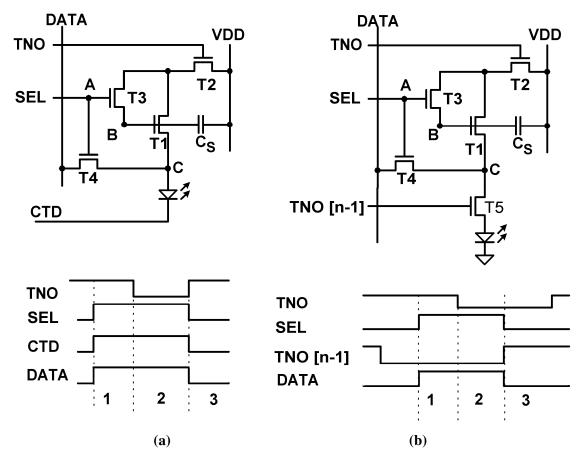

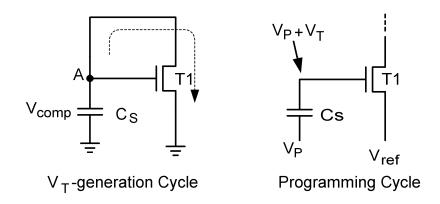

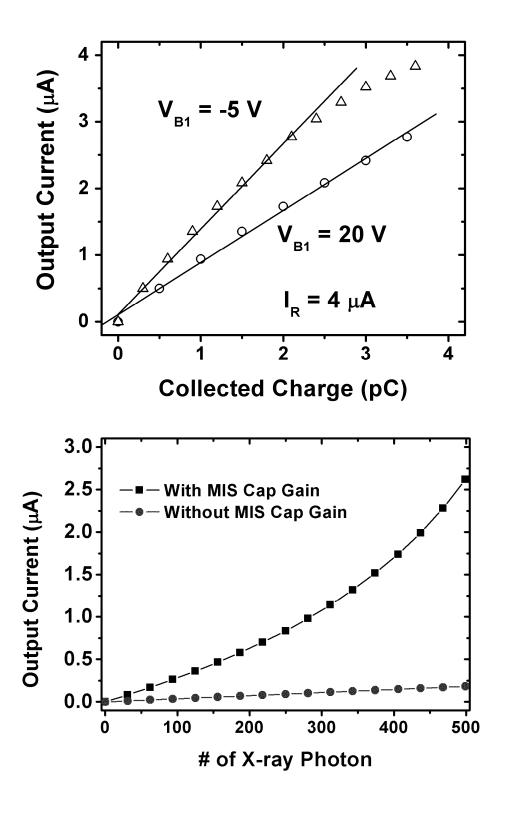

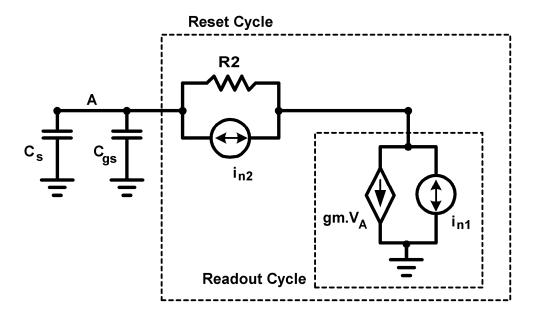

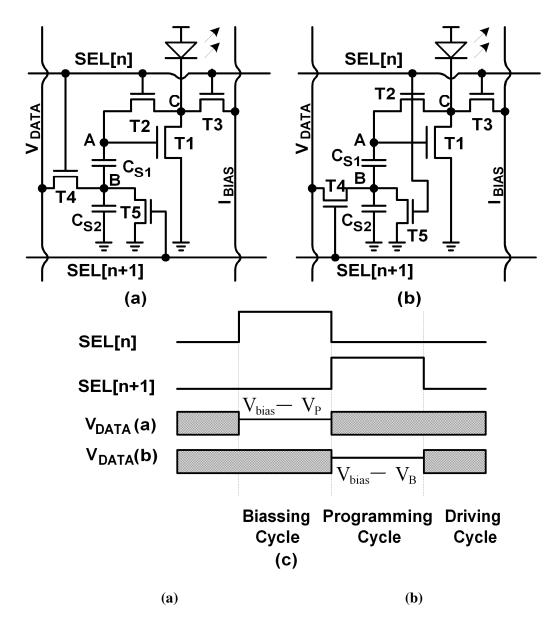

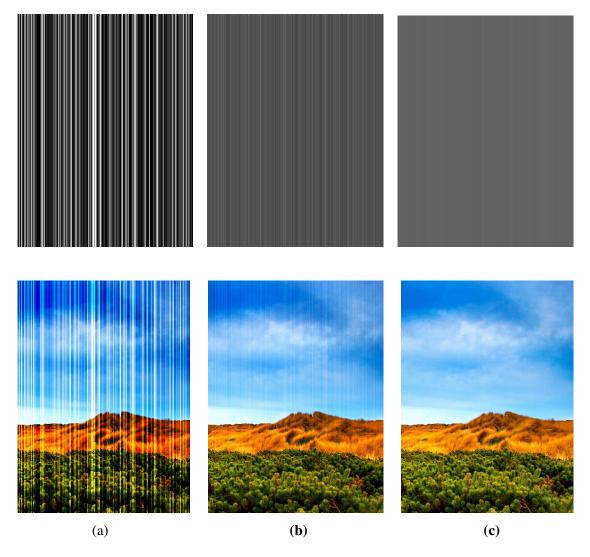

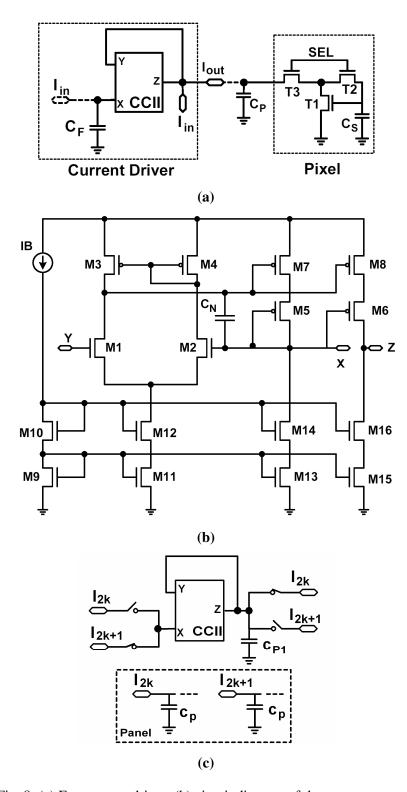

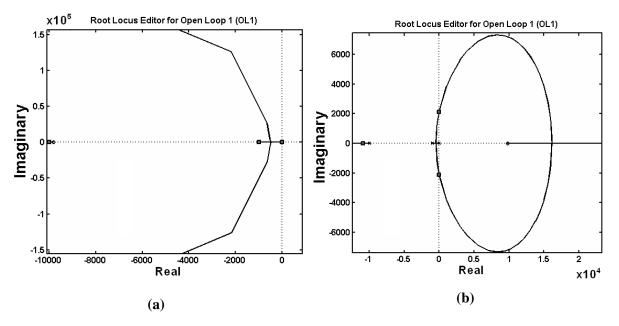

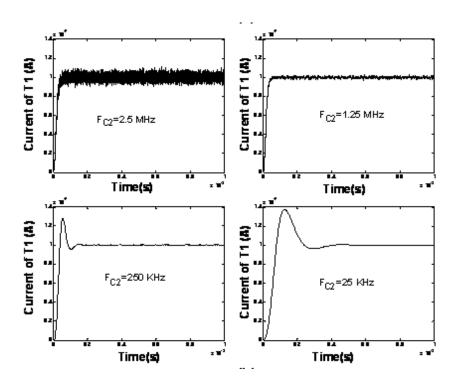

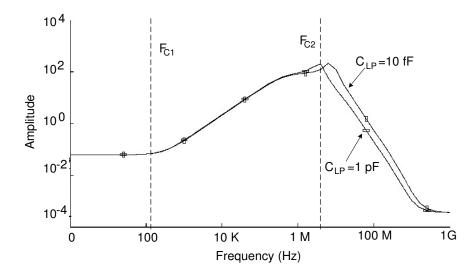

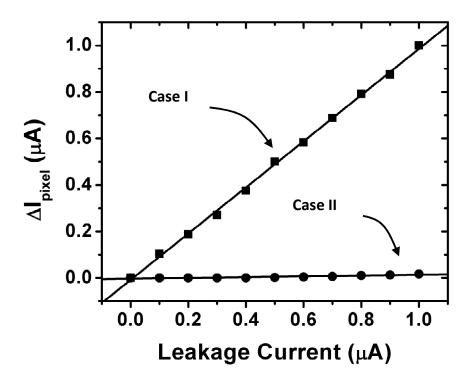

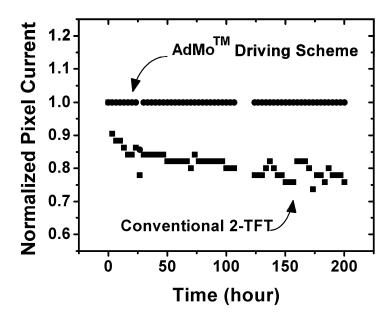

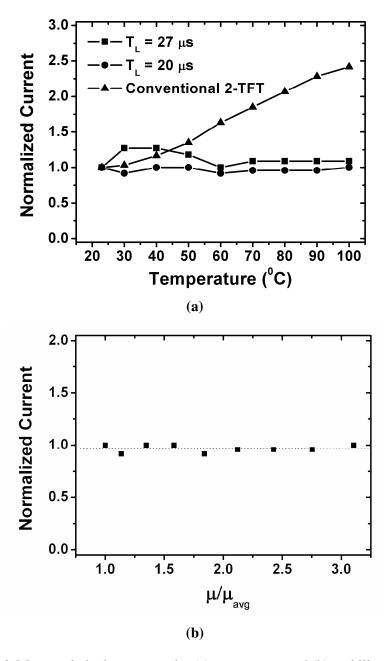

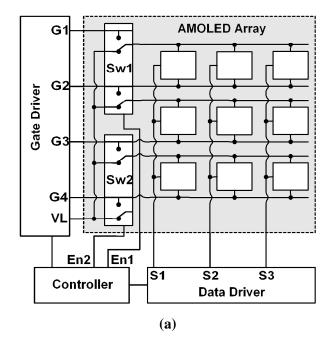

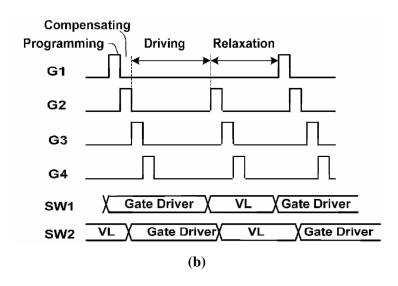

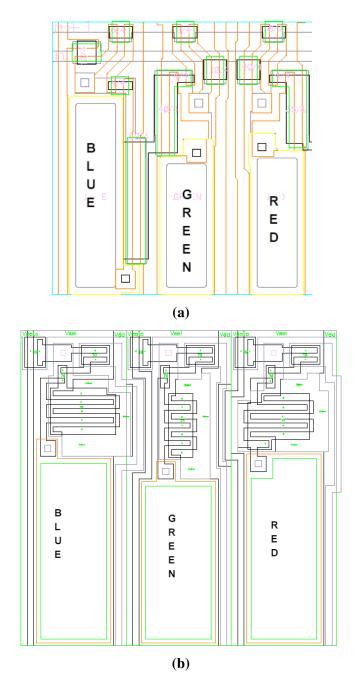

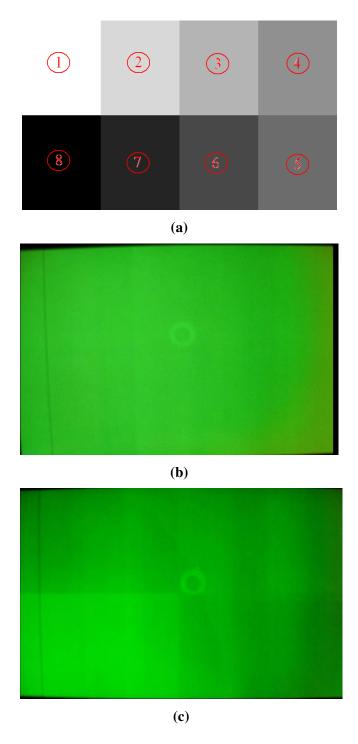

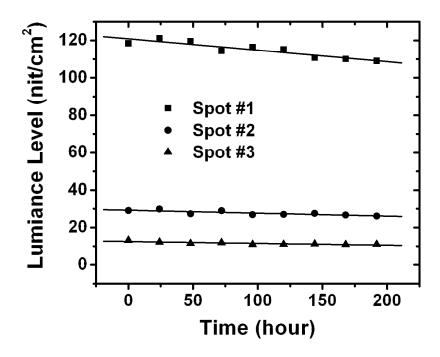

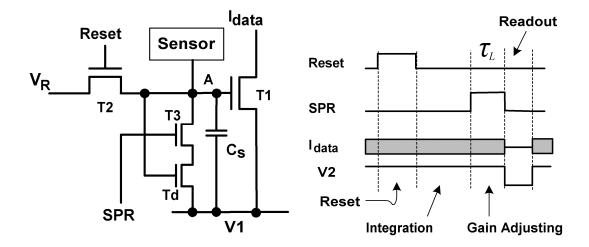

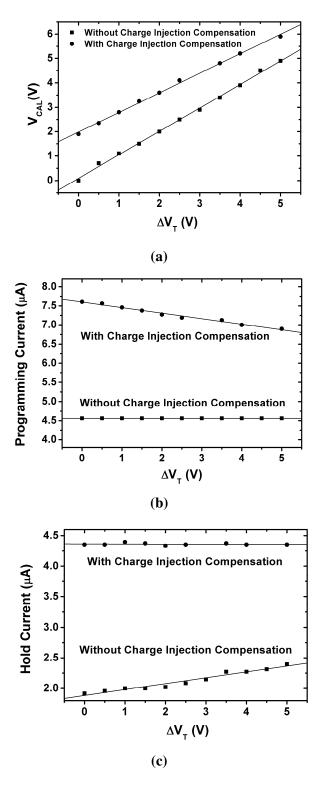

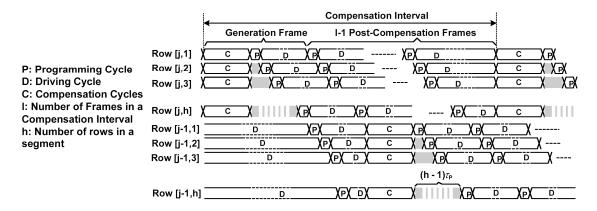

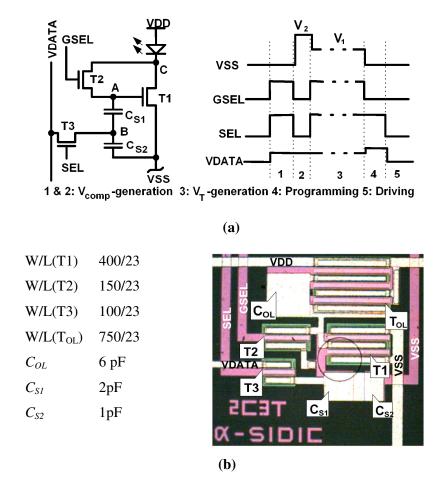

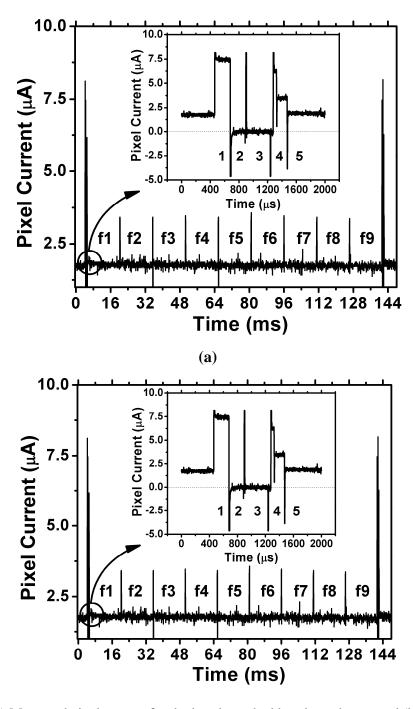

|-----------------------------------------------------------------------------------------------------------|