# Transparent Oxide Semiconductors: Fabrication, Properties, and Applications

by

Kai Wang

A thesis

presented to the University of Waterloo

in fulfillment of the

thesis requirement for the degree of

Doctor of Philosophy

in

Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2008

© Kai Wang 2008

# **AUTHOR'S DECLARATION**

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### **Abstract**

Transparent oxide semiconductors (TOSs) are materials that exhibit electrical conduction and optical transparency. The traditional applications of these materials are transparent conducting oxides in flat-panel displays, light-emitting diodes, solar cells, and imaging sensors. Recently, significant research has been driven to extend state-of-the-art applications such as thin-film transistors (TFTs). A new and rapidly developing field is emerging, called transparent electronics. This thesis advances transparent electronics through developing a new technique to fabricate TOSs and demonstrating their applications to active semiconductor devices such as diodes and TFTs.

Ion beam assisted evaporation (IBAE) is used to deposit two common TOSs: zinc oxide (ZnO) and indium oxide (In<sub>2</sub>O<sub>3</sub>). The detailed material study is carried out through various characterization of their electrical properties, chemical composition, optical properties, crystal structure, intrinsic stress, topology, and morphology, as well as an investigation of thin-film property as a function of the deposition parameters: ion flux and energy, and deposition rate. The study proves that IBAE technique provides the capability for fabricating TOSs with controllable properties.

By utilizing the newly developed semiconducting ZnO, p-NiO/i-ZnO/n-ITO and n-ITO/i-ZnO/p-NiO heterostructure photodiodes with a low leakage are proposed and assessed. Analysis of their current-voltage characteristics and current transient behaviour reveals that the dominant source of leakage current stems from the deep defect states in the intrinsic zinc oxide layer, where its dynamic response at low signal levels is limited by the charge trapping. The exploration of the photoconduction mechanism and spectral response confirms that such photodiodes are potentially

applicable for ultraviolet (UV) sensors. The comparative study of both device structures provides further insights into the leakage current mechanisms, p-i interface properties, and quantum efficiency.

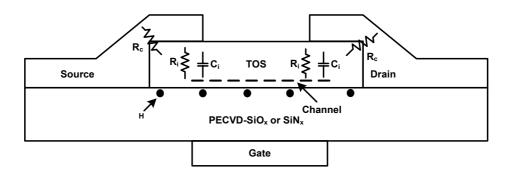

Secondly, with the novel semiconducting In<sub>2</sub>O<sub>3</sub>, TFTs are fabricated and evaluated. The device performance is optimized by addressing the source/drain contact issue, lowering the intrinsic channel resistance, and improving the dielectric/channel interface. The best n-channel TFT has a high field-effect mobility of ~30 cm<sup>2</sup>/Vs, a high current ON/OFF ratio of ~10<sup>8</sup>, and a sub-threshold slope of 2.0 V/decade. More important, high-performance indium oxide TFTs here are integrated with the silicon dioxide and silicon nitride gate dielectrics by conventional plasma-enhanced chemical vapour deposition, which makes indium oxide TFT a competitive alternative for next generation TFTs to meet the technical requirements for flat-panel displays, large area imager arrays, and radio frequency identification tags. The stability study shows that indium oxide TFTs are highly stable with a very small threshold voltage shift under both a long-term constant voltage and long-term current stress. The dynamic behaviour indicates factors that affect the operation speed of such TFTs. A descriptive model is proposed to link the material properties and the processing issues with the device performance to facilitate further research and development of TOS TFTs.

The research described in this thesis is one of the first investigations of the fabrication of TOSs by the IBAE and their applications to a variety of thin-film devices, particularly UV sensors and TFTs.

## **Acknowledgements**

I would like to express my sincere thanks to my advisor, Dr. Arokia Nathan for his vision, supervision and guidance. He has supported me throughout my doctoral program and often encouraged me to dig deeper into my research. Words cannot express my gratitude to him.

I am indebted to my mentor, Dr. Yuriy Vygranenko for training me in equipment usage, device fabrication and characterization, and analysis. This work would not have been completed without his direction and help.

Many thanks go to Flora Li and Hyun Jung Lee for their advice and fruitful discussion on device physics during countless coffee breaks. I am grateful to my colleagues, Reza Chaji and Afrin Sultana, for their help with the stress tests, Hassan El-Gohary for his assistance in rapid thermal annealing, and Richard Barber and Robert Mullins for their equipment trouble-shooting. Thanks are also given to many other colleagues: Mohammad R. Esmaeili Rad, Maryam Moradi, Dr. Majid Gharghi, Dr. Isaac Chan, Dr. Yichun Luo, former group members Dr. Dennis Striakhilev, Dr. Sheng Tao, Dr. Jeff Chang, Dr. Jackson Lai, Dr. Kyung Ho Kim, Saeed Fathololoumi, and my officemate, Arash Fomani.

I also want to thank some professors and staff from the department: Dr. Andrei Sazonov, Dr. Siva Sivoththaman, Dr. Hany Aziz, Dr. Dayan Ban, Dr. M. P. Anantrum, Dr. Sherman Shen, Annette Dietrich, Wendy Boles, Lisa Hendel, Karen Schooley, and Eliza Ho for their help.

Special thanks to Gloria Ichim for her endless encouragement and support. I am grateful to my landlady, Maria Alice Seviora and her family, Lakhena Sam, Donna

Armborst, Uncle Dexu Sun and his family, my roommate, Yunwei Dong, and my good friends: Raymond Zhu, Wei Li and Xiaoling Ling, Dr. Shude Xiao, Yanqiao Zhang, Dr. Xiaogang Li and his family, Dr. Humphrey Rutagemwa, Dr. Henghua Deng, Fanlong Ning and Yi Zhou for their encouragement and friendship during my years in Canada. I appreciate Jing Fu for her listening to my stories and sharing laughter which I needed most.

Lastly and most important, my everlasting gratitude goes to my father, Min Wang and my mother, Shumin Yang, for their continuous and unconditional support and love.

This thesis is dedicated to them.

# **Table of Contents**

| AUTHOR'S DECLARATION                                        | ii  |

|-------------------------------------------------------------|-----|

| Abstract                                                    | iii |

| Acknowledgements                                            | V   |

| Table of Contents                                           | vii |

| List of Figures                                             | X   |

| List of Tables                                              | xiv |

| Chapter 1 Introduction                                      | 1   |

| 1.1 Overview of TOSs                                        | 1   |

| 1.2 Two Common TOSs: In <sub>2</sub> O <sub>3</sub> and ZnO | 4   |

| 1.2.1 Crystal Structure                                     |     |

| 1.2.2 Electronic Structure                                  |     |

| 1.3 Transparent Electronics                                 | 8   |

| 1.3.1 Research Challenges                                   | 9   |

| 1.4 Organization of the Thesis                              | 11  |

| Chapter 2 Fabrication Technique                             | 13  |

| 2.1 Introduction                                            | 13  |

| 2.2 Ion Beam Assisted Evaporation                           | 14  |

| 2.2.1 Schematic Configuration of the IBAE system            | 14  |

| 2.2.2 Reactive IBAE                                         | 15  |

| 2.2.3 Oxygen Ion Source                                     | 17  |

| 2.3 Deposition Parameters                                   | 18  |

| Chapter 3 Material Study                                    | 20  |

| 3.1 Zinc Oxide                           | 20 |

|------------------------------------------|----|

| 3.1.1 Introduction                       | 20 |

| 3.1.2 Deposition Rate                    | 20 |

| 3.1.3 Electrical Properties              | 22 |

| 3.1.4 Optical Properties                 | 25 |

| 3.1.5 Crystal Structure                  | 30 |

| 3.2 Indium Oxide                         | 31 |

| 3.2.1 Electrical Properties              | 31 |

| 3.2.2 Compositional Analysis             | 34 |

| 3.2.3 Optical Properties                 | 36 |

| 3.2.4 Crystal Structure                  | 40 |

| 3.2.5 Intrinsic Stress                   | 41 |

| 3.2.6 Topology                           | 43 |

| 3.2.7 Morphology                         | 47 |

| 3.3 Summary                              | 48 |

| Chapter 4 ZnO-based UV Sensors           | 49 |

| 4.1 Introduction                         | 49 |

| 4.2 Device Fabrication and Processing    | 51 |

| 4.3 Device Characterization and Analysis | 52 |

| 4.3.1 Current-Voltage Characteristics    | 52 |

| 4.3.2 Leakage Current Mechanisms         | 53 |

| 4.3.3 Forward-Bias Analysis              | 59 |

| 4.3.4 Photocurrent Transient             | 61 |

| 4.3.5 Spectral Response and Linearity    | 62 |

| 4.3.6 Photoconduction Mechanisms         | 65 |

| 4.4 Summary                              | 67 |

| Chapter 5 Indium Oxide TFTs              | 69 |

| 5.1 Introduction                                    | 69  |

|-----------------------------------------------------|-----|

| 5.2 TFTs with a Silicon Dioxide Gate Dielectric     | 69  |

| 5.2.1 First-Run Indium Oxide TFTs                   | 69  |

| 5.2.2 Problem Identification and Proposed Solutions | 73  |

| 5.2.3 TFTs with the Improved Device Performance     | 74  |

| 5.3 TFTs with a Silicon Nitride Gate Dielectric     | 80  |

| 5.4 Threshold Voltage Stability                     | 84  |

| 5.4.1 Stability under Constant Voltage Stress       | 84  |

| 5.4.2 Stability under Current Stress                | 88  |

| 5.5 Dynamic Characteristics                         | 91  |

| 5.6 Summary                                         | 94  |

| Chapter 6 Conclusions and Contributions             | 96  |

| Appendix TFT Parameter Extraction                   | 98  |

| References                                          | 100 |

# **List of Figures**

| Figure 1.1: Schematic illustration of atomic arrangement in crystalline In <sub>2</sub> O <sub>3</sub> | 5   |

|--------------------------------------------------------------------------------------------------------|-----|

| Figure 1.2: Wurtzite structure of ZnO lattice                                                          | 6   |

| Figure 2.1: Schematic structure of a typical IBAE system                                               | 15  |

| Figure 2.2: IBAE system used in this research                                                          | 16  |

| Figure 2.3: Main chamber during deposition                                                             | 17  |

| Figure 2.4: Schematic diagram of oxygen ion source.                                                    | 18  |

| Figure 3.1: Deposition rate calibrated in terms of the discharge current                               | 21  |

| Figure 3.2: Deposition rate calibrated in terms of the discharge voltage                               | 22  |

| Figure 3.3: Resistivity of the ZnO films as a function of the discharge current                        | 23  |

| Figure 3.4: Resistivity of the ZnO films as a function of the discharge voltage                        | 24  |

| Figure 3.5: Transmittance spectra of the 100 nm ZnO films deposited at different                       |     |

| discharge currents                                                                                     | 25  |

| Figure 3.6: Transmittance spectra of the ZnO films deposited at different discharge                    | ;   |

| voltages                                                                                               | 26  |

| Figure 3.7: Variation of the refractive index with the wavelength of the ZnO films                     |     |

| deposited at different discharge currents                                                              | 27  |

| Figure 3.8: Dependence of the refractive index on the wavelength of the ZnO films                      | ;   |

| deposited at different discharge voltages                                                              | 28  |

| Figure 3.9: Representative absorption curves of the ZnO films deposited at the                         |     |

| discharge of 2.45 A and 1.85 A for the optical bandgap extraction                                      | 29  |

| Figure 3.10: XRD patterns of the semiconducting ZnO film                                               | 30  |

| Figure 3.11: Dependence of the resistivity of the indium oxide films on the deposit                    | ion |

| rate                                                                                                   | 32  |

| Figure 3.12: Variation of the resistivity of the indium oxide films with the discharg                  | e;e |

| current                                                                                                | 33  |

| Figure 3.13: XPS spectra of (a) In 3d and (b) O 1s of the indium oxide films                           |     |

| deposited at two different discharge currents of 0.5 A and 2.0 A                                       | 34  |

| Figure 3.14: Transmittance spectra of the indium oxide films deposited at different                    |     |

| deposition rates                                                                                       | 36  |

| Figure 3.15: Transmittance spectra of the indium oxide films deposited at different                    |     |

| discharge currents                                                                                     | 37  |

| Figure 3.16: Representative absorption curves of the indium oxides deposited at the                |

|----------------------------------------------------------------------------------------------------|

| discharge currents of 0.5 A and 2.0 A for the optical bandgap extraction38                         |

| Figure 3.17: Refractive index of the indium oxides fabricated at two different                     |

| discharge currents                                                                                 |

| Figure 3.18: Refractive index of the indium oxides deposited at two different                      |

| deposition rates                                                                                   |

| Figure 3.19: XRD patterns of the indium oxide films deposited at different discharge               |

| currents: 0.5 A, 1.5 A, and 2.0 A                                                                  |

| Figure 3.20: Intrinsic stress of the indium oxide films as a function of the deposition            |

| rate                                                                                               |

| Figure 3.21: Intrinsic stress of the indium oxide films as a function of the discharge             |

| current                                                                                            |

| Figure 3.22: Topological image of the semiconducting indium oxide45                                |

| Figure 3.23: Representative surface profiles scanned in both the x- and y- directions              |

| for the semiconducting indium oxide                                                                |

| Figure 3.24: Topological image of the highly-conducting indium oxide46                             |

| Figure 3.25: Representative surface profiles scanned in both the x- and y- directions              |

| for the highly-conducting indium oxide                                                             |

| Figure 3.26: Cross-sectional SEM images of the semiconducting indium oxide film on                 |

| a single crystalline Si wafer                                                                      |

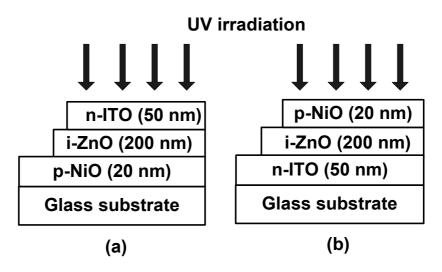

| Figure 4.1: Schematic diagram of the (a) p-i-n and (b) n-i-p heterostructures52                    |

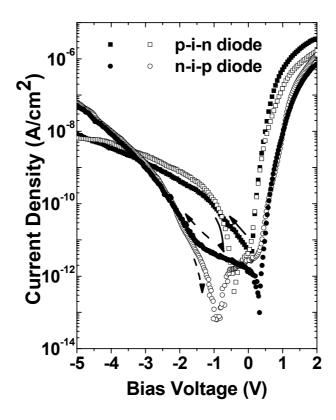

| Figure 4.2: Typical J-V characteristics of the ZnO-based p-i-n and n-i-p diodes53                  |

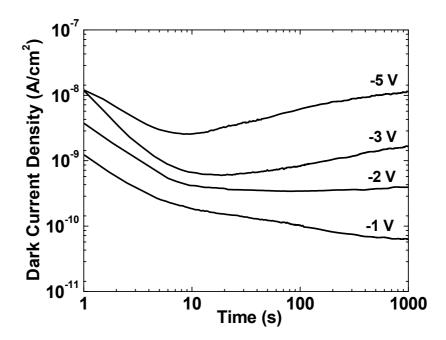

| Figure 4.3: Time dependence of the dark current at different bias voltages for the p-i-n           |

| diode                                                                                              |

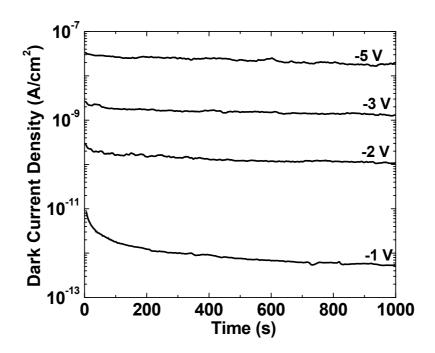

| Figure 4.4: Time dependence of the dark current at different bias voltages for the n-i-p           |

| diode55                                                                                            |

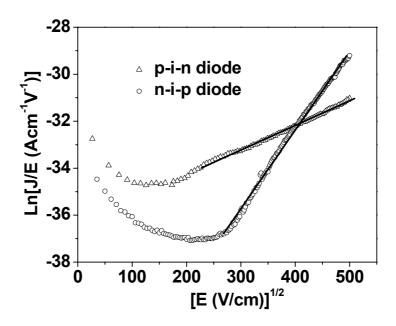

| Figure 4.5: Ln (J/E) as a function of $E^{1/2}$ , obeying the Poole-Frenkel model, accounts        |

| for the leakage current mechanism at a reverse bias higher than 1.5 V56                            |

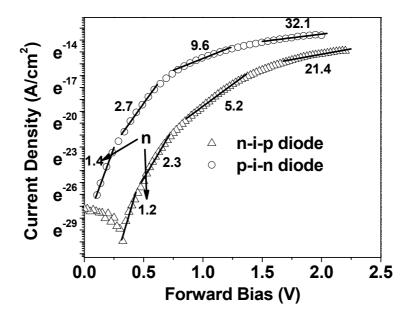

| Figure 4.6: Forward-bias ln(J)-V characteristics of the p-i-n and n-i-p diodes59                   |

| Figure 4.7: At higher biases, the current depends on V <sup>2</sup> , fitting well with the space- |

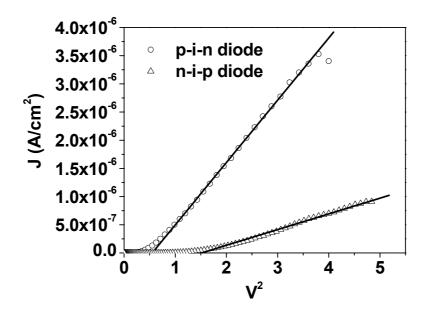

| charge-limited current model 60                                                                    |

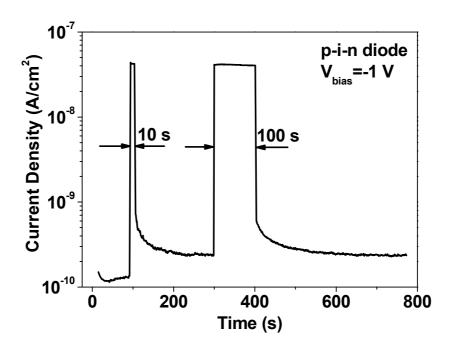

| Figure 4.8: Photocurrent transient of the p-i-n diode under the reverse bias of 1 V61              |

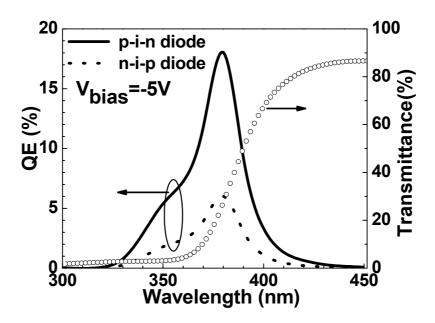

| Figure 4.9: Comparison of the quantum efficiency between the p-i-n and the n-i-p          |  |  |  |  |  |

|-------------------------------------------------------------------------------------------|--|--|--|--|--|

| diodes; transmittance spectrum of the ZnO intrinsic layer at wavelengths from 300 to      |  |  |  |  |  |

| 450 nm is also included                                                                   |  |  |  |  |  |

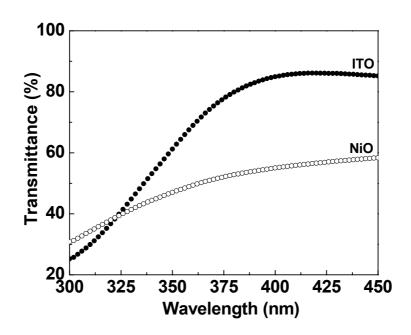

| Figure 4.10: Transmittance spectra of the 50 nm ITO and 20 nm NiO in the                  |  |  |  |  |  |

| wavelength range of 300 to 450 nm                                                         |  |  |  |  |  |

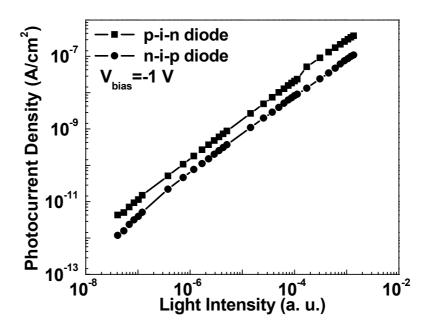

| Figure 4.11: Photocurrent density as a function of the light intensity for both the p-i-n |  |  |  |  |  |

| and n-i-p diodes65                                                                        |  |  |  |  |  |

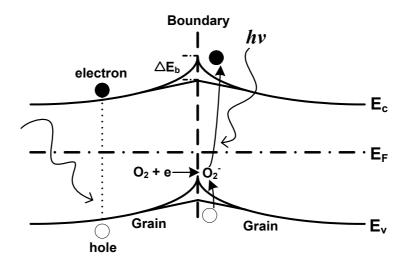

| Figure 4.12: Photoconduction mechanisms of the nanocrystalline ZnO thin film67            |  |  |  |  |  |

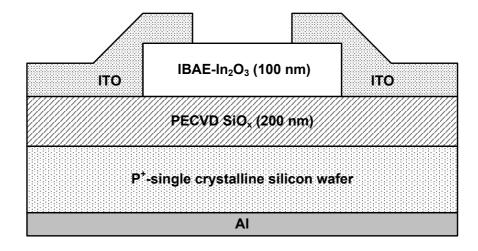

| Figure 5.1: Cross-sectional schematic diagram of the indium oxide TFT test structure      |  |  |  |  |  |

| 70                                                                                        |  |  |  |  |  |

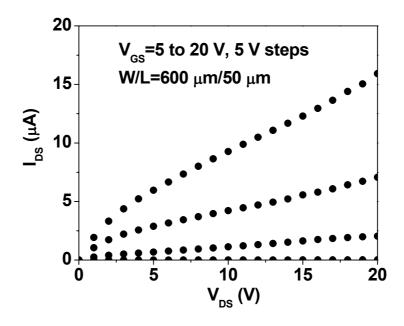

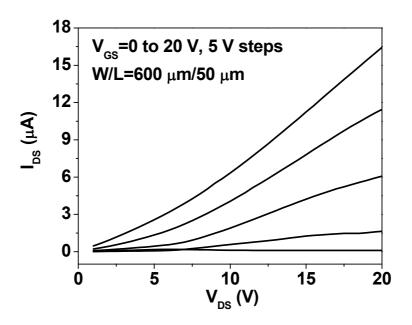

| Figure 5.2: Output characteristics of the first-run indium oxide TFT with the PECVD       |  |  |  |  |  |

| SiO <sub>x</sub> gate dielectric                                                          |  |  |  |  |  |

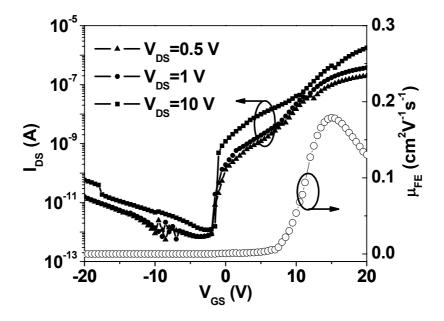

| Figure 5.3: Transfer characteristics and field-effect mobility dependence on the gate     |  |  |  |  |  |

| voltage of the first-run indium oxide TFT with the PECVD $SiO_x$ gate dielectric72        |  |  |  |  |  |

| Figure 5.4: (a) Schematic cross section of the fabricated bottom-gate indium oxide        |  |  |  |  |  |

| TFT with the PECVD $SiO_x$ dielectric and (b) micrograph of the fabricated TFT76          |  |  |  |  |  |

| Figure 5.5: Output characteristics of the indium oxide TFT with the PECVD $SiO_x$         |  |  |  |  |  |

| dielectric 77                                                                             |  |  |  |  |  |

| Figure 5.6: Transfer characteristics of the indium oxide TFT with the PECVD $SiO_x$       |  |  |  |  |  |

| dielectric; the field-effect mobility as a function of the gate bias is also included78   |  |  |  |  |  |

| Figure 5.7: Transfer characteristics of the indium oxide TFT with the 100 nm channel      |  |  |  |  |  |

| layer                                                                                     |  |  |  |  |  |

| Figure 5.8: Output characteristics of the first-run indium oxide TFT with the PECVD       |  |  |  |  |  |

| SiN <sub>x</sub> gate dielectric                                                          |  |  |  |  |  |

| Figure 5.9: Transfer characteristics of the first-run indium oxide TFT with the           |  |  |  |  |  |

| PECVD SiN <sub>x</sub> dielectric                                                         |  |  |  |  |  |

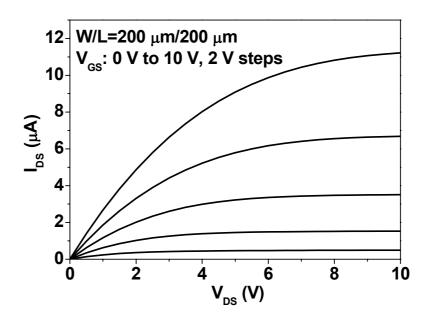

| Figure 5.10: Output characteristics of the second-run indium oxide TFT with the           |  |  |  |  |  |

| PECVD SiN <sub>x</sub> dielectric 82                                                      |  |  |  |  |  |

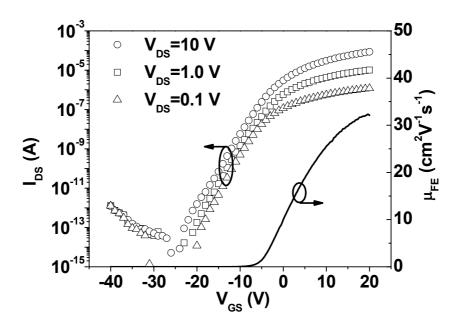

| Figure 5.11: Transfer characteristics of the second-run indium oxide TFT with the         |  |  |  |  |  |

| PECVD SiN <sub>x</sub> dielectric83                                                       |  |  |  |  |  |

| Figure 5.12: Threshold voltage of the indium oxide TFT with the PECVD $SiO_x$             |  |  |  |  |  |

| dielectric as a function of the stress time                                               |  |  |  |  |  |

| Figure 5.13: Shift in transfer characteristics of the TFT due to a stress gate bias of 30    |

|----------------------------------------------------------------------------------------------|

| V for different stress time86                                                                |

| Figure 5.14: Transfer characteristics of the indium oxide TFT measured before stress,        |

| after 6000 s stress, after 24 hr relaxation, and after 80°C baking for 24 hours (stress      |

| voltage: 30 V)                                                                               |

| Figure 5.15: Threshold voltage shift of the indium oxide TFT with the PECVD SiO <sub>x</sub> |

| gate dielectric under constant current stress                                                |

| Figure 5.16: Threshold voltage shift of the indium oxide TFT under the current stress        |

| with relaxation90                                                                            |

| Figure 5.17: Set up for the dynamic behaviour test                                           |

| Figure 5.18: Switching waveform of the TFT with the 100 nm indium oxide channel              |

| layer92                                                                                      |

| Figure 5.19: Switching waveform of the indium oxide TFT with the 30 nm channel               |

| layer93                                                                                      |

| Figure 5.20: Summarized factors which affect the performance of TOS TFTs with                |

| PECVD dielectrics95                                                                          |

# **List of Tables**

| Table 1.1: Candidates for HMCs with the electronic configuration | 2  |

|------------------------------------------------------------------|----|

| Table 1.2: Critical parameters of HMCs and TOSs [1]              | 3  |

| Table 1.3: Comparison of available TFT technologies              | 9  |

| Table 2.1: Deposition parameters of the IBAE technique           | 19 |

# **Chapter 1**

# Introduction

Metal oxides are very interesting materials which can behave as insulators, superconductors, and semiconductors. Some of them exhibit electrical conductivity and visible transparency such as transparent oxide semiconductors (TOSs). Traditionally, the semiconductors such as indium-tin oxide (ITO), doped tin oxide (SnO<sub>2</sub>:F; SnO<sub>2</sub>:Sb), and doped zinc oxide (ZnO:Al; ZnO:Ga; ZnO:In) are widely used as transparent conducting oxides (TCOs) in flat-panel displays, light-emitting diodes, solar cells, and imagers [2]. Recently, thin-film transistors (TFTs) based on TOSs have attracted a great deal of attention.

This thesis addresses materials, processing, and devices regarding TOSs with a focus on diodes and TFTs. The purpose of this chapter, in particular, is to review this group of materials, focusing on ZnO and In<sub>2</sub>O<sub>3</sub>, to describe the challenges of the emerging transparent electronics.

#### 1.1 Overview of TOSs

This section contains a brief introduction of TOSs from fundamental material physics to industrial applications, a review of two well-known TOSs: ZnO and In<sub>2</sub>O<sub>3</sub>, including their crystal and electronic structures, and the research challenges in the field of transparent electronics.

TOSs are a series of metal oxides, composed of heavy metal cations (HMCs) with an outside shell electronic configuration of (n-1)d<sup>10</sup>ns<sup>0</sup> (n>4) and oxygen anions [3].

In terms of this definition, the candidates of HMCs to form TOSs can be sorted out from the chemical periodic table and their electronic configurations are in Table 1.1.

Table 1.1: Candidates for HMCs with the electronic configuration

| Cu                                   | Zn                       | Ga                                                                    | Ge                                                                    | As                                                   |

|--------------------------------------|--------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------|------------------------------------------------------|

| $[Ar]3d^{10}4s^{1}$                  | $[Ar]3d^{10}4s^2$        | $[Ar]3d^{10}4s^24p^1$                                                 | $[Ar]3d^{10}4s^24p^2$                                                 | [Ar]3d <sup>10</sup> 4s <sup>2</sup> 4p <sup>3</sup> |

| Ag                                   | Cd                       | In                                                                    | Sn                                                                    | Sb                                                   |

| [Kr]4d <sup>10</sup> 5s <sup>1</sup> | $[Kr]4d^{10}5s^2$        | [Kr]4d <sup>10</sup> 5s <sup>2</sup> 5p <sup>1</sup>                  | $[Kr]4d^{10}5s^25p^2$                                                 | [Kr]4d <sup>10</sup> 5s <sup>2</sup> 5p <sup>3</sup> |

| Au                                   | Hg                       | T1                                                                    | Pb                                                                    | Bi                                                   |

| $[Xe]4f^{14}5d^{10}6s^{1}$           | $[Xe]4f^{14}5d^{10}6s^2$ | [Xe]4f <sup>14</sup> 5d <sup>10</sup> 6s <sup>2</sup> 5p <sup>1</sup> | [Xe]4f <sup>14</sup> 5d <sup>10</sup> 6s <sup>2</sup> 5p <sup>2</sup> | $[Xe]4f^{14}5d^{10}6s^{2}6p^{3}$                     |

[Ar]:  $1s^22s^22p^63s^23p^6$

[Kr]:  $1s^22s^22p^63s^23p^63d^{10}4s^24p^6$

$[Xe]: 1s^2 2s^2 2p^6 3s^2 3p^6 3d^{10} 4s^2 4p^6 4d^{10} 5s^2 5p^6$

TOSs have wide bandgaps in which the ns orbitals of the HMCs primarily constitute the bottom part of the conduction band and the oxygen 2p orbitals form the top of the valence band. Uniquely, the spatial spreading of the outside ns orbitals with a spherical symmetry in the HMCs is much larger than that in light metal cations such as aluminium, leading to a wider conduction band. Since the carrier mobility is proportional to the width of the conduction band, TOSs are electrically active and differ from light metal oxides such as MgO and Al<sub>2</sub>O<sub>3</sub> which are typical insulators. The metal ion radius, metal and oxygen bond length and angle are among the critical parameters that determine the carrier mobility of these oxide semiconductors. Table 1.2 lists these critical parameters of the common HMCs and TOSs, and their ns orbital overlap integrals [1].

Table 1.2: Critical parameters of HMCs and TOSs [1]

| НМС   | TOS                                     | ion radius<br>(pm) | M-O length<br>(Å) | M-O-M<br>angle  | Overlap |

|-------|-----------------------------------------|--------------------|-------------------|-----------------|---------|

| Zn 4s | ZnO                                     | 1.16               | 1.976             | 108.20          | 0.6045  |

| Ga 4s | $\beta$ -Ga <sub>2</sub> O <sub>3</sub> | 0.88               | 1.978             | $100.4^{\circ}$ | 0.4632  |

| Ge 4s | $GeO_2$                                 | 0.71               | 1.738             | $130.0^{\circ}$ | 0.2848  |

| Cd 5s | CdO                                     | 1.25               | 2.348             | $90.0^{\circ}$  | 0.6905  |

| In 5s | $In_2O_3$                               | 0.95               | 2.180             | $98.2^{\circ}$  | 0.5613  |

| Sn 5s | $SnO_2$                                 | 0.77               | 2.052             | $101.9^{\circ}$ | 0.4523  |

As seen from this table, the Zn-Zn 4s and the In-In 5s orbitals have large overlap integrals compared with the other HMCs. As a result, ZnO and  $In_2O_3$  should have a high carrier mobility. This has already been proven by Hall-effect measurements: single crystalline n-type ZnO has a Hall mobility of around 200 cm<sup>2</sup>/Vs, and single crystalline n-type  $In_2O_3$  has a Hall mobility as high as  $\sim 160$  cm<sup>2</sup>/Vs [1]. Moreover, the large ns-ns orbital overlap makes the mobility less sensitive to any angular variation or bond stretching in the M-O-M bonds; that is, the mobility of TOSs is immune to the structural disorder because of such ionic bonding. Thus, amorphous TOSs still display a considerable carrier mobility comparable to their crystalline counterparts. This characteristic cannot be found in other types of semiconductor materials. For instance, the mobility of polycrystalline silicon (covalent bonding) is  $2\sim3$  orders of magnitude higher than that of amorphous silicon (a-Si:H).

#### 1.2 Two Common TOSs: In<sub>2</sub>O<sub>3</sub> and ZnO

As discussed in the previous section, both  $In_2O_3$  and ZnO are non-toxic and have relatively large overlap integrals, leading to a high mobility that is desirable for device applications. In this section, an introduction of these two vital TOSs is given.

#### 1.2.1 Crystal Structure

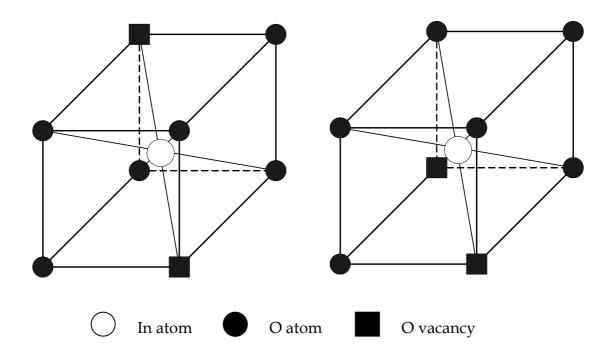

In<sub>2</sub>O<sub>3</sub> has a bixbyite crystal structure that is inherently a cubic-type rare earth, vacancy-defect oxide. Bixbyite has an 80 atom unit cell with the Ia3 space group and a 1 nm lattice constant in an arrangement, based on the stacking of the MO<sub>6</sub> coordination groups [2]. The bixbyite structure is similar to that of fluorite and has a face-centred cubic array of indium atoms with all the tetrahedral interstitial positions filled with oxygen atoms. The primary difference between fluorite and bixbyite is the MO<sub>8</sub> coordination units in the bixbyite structure (the oxygen position is on the corners of a cube and the indium atom is located at the centre of the cube) are replaced by units with oxygen atoms missing from either the body or the face diagonally as depicted in Figure 1.1. The removal of two oxygen atoms from the MO<sub>8</sub> to form the MO<sub>6</sub> coordination units forces the displacement of the indium from the centre of the cube. Thus, indium is distributed in two nonequivalent sites with one-quarter of the indium atoms positioned at the centre of a trigonally distorted oxygen octahedron (diagonally missing O), and the remaining three-quarters positioned at the centre of a more distorted and less symmetric octahedron that results from the removal of two oxygen atoms from the same face of the octahedron. The resulting MO<sub>6</sub> coordination units are then stacked such that one-quarter of the oxygen atoms are missing from each {100} plane in the fluorite structure [4].

Figure 1.1: Schematic illustration of atomic arrangement in crystalline In<sub>2</sub>O<sub>3</sub>

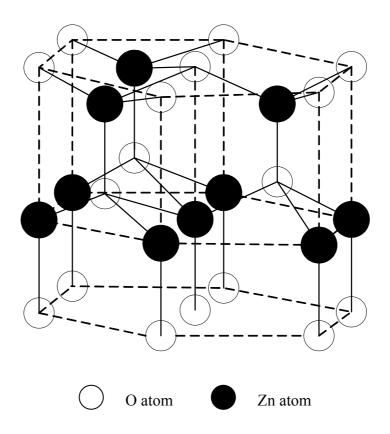

Zinc oxide crystallizes in the hexagonal wurtzite lattice in Figure 1.2. The zinc atoms are nearly in the position of hexagonal close packing. Each oxygen atom lies within a tetrahedral group of four zinc atoms, which are in the same direction along the hexagonal axis. ZnO lattice has space group  $P6_3$ mc, with the lattice constants of a = b = 3.24 Å, c = 5.19 Å [2]. Three of the oxygen atoms in the distorted ZnO<sub>4</sub> tetrahedron are placed in one close-packed ab plane, whereas the fourth oxygen atom is located in the adjacent plane. As a result, the structure contains an array of vertical Zn-O vectors along the c axis, resulting in a classical polar structure.

Figure 1.2: Wurtzite structure of ZnO lattice

#### 1.2.2 Electronic Structure

$In_2O_3$  has a cubic bixbyite structure in which  $O^{2-}$  ions occupy, in an ordered manner, three-quarters of the tetrahedral interstices of a faced-centered-cubic  $In^{3+}$ -ion array. Consequently,  $In_2O_3$  should consist of a filled  $O^{2-}$ :2p valence band that is primarily oxygen 2p in character [5]. The In: 3d core lies below the valence band edge  $(E_v)$ . The conduction band is the In: 5s band with an band edge  $(E_c)$  approximately 3.75 eV above  $E_v$ . As discussed in Section 1.2.1,  $In_2O_3$  is usually oxygen-deficient. At high oxygen vacancy concentration, an oxygen vacancy band forms and overlaps  $E_c$  at the bottom of the conduction band such that  $In_2O_3$  becomes a degenerated semiconductor [6]. Hereby, the oxygen vacancies act as doubly ionized donors and contribute a

maximum of two electrons to the conduction band. Electrons can also be generated by doping tin into indium oxide to form tin-doped In<sub>2</sub>O<sub>3</sub>. Since indium has a valence of three, the tin substitution results in an n-type doping by providing an extra electron to the conduction band to preserve the overall charge neutrality.

The second semiconductor of interest is ZnO. The electronic structure of ZnO has been calculated by many researchers. The lowest two valence bands correspond to the O<sup>2</sup>: 2s core-like states. The next six valence bands correlate to the O<sup>2</sup>: 2p bonding states. The first two conduction band states are strongly localized on zinc and correspond to the unoccupied Zn<sup>2+</sup>: 4s levels. The higher conduction bands are freeelectron-like. The fundamental bandgap, calculated by using band structure models, is ~3.4 eV at room temperature [2]. The undoped ZnO is slightly an n-type wide and a direct bandgap semiconductor. The n-type conduction is attributed to the deviation from the stoichiometry. The free carriers are created from the self-donors, associated with the oxygen vacancies and/or interstitial zinc [7, 8]. The donor levels are also produced by the incorporation of foreign atoms such as hydrogen, indium, aluminium, and gallium. It is necessary to fabricate both p-type and n-type ZnO in order to realize bipolar devices from ZnO. However, wide bandgap semiconductors generally have an asymmetric doping problem; that is they can be easily doped to either an n-type or a p-type, but not both. For example, ZnO is easily doped to an n-type with a very high carrier density and low resistance by group III elements [9]. However, p-type doped ZnO is very difficult to achieve [10]. Group V elements such as nitrogen have been considered as acceptor dopants.

## 1.3 Transparent Electronics

In 2003, the invention of the first transparent TFTs with ZnO as channels, marked the birth of transparent electronics [11-13]. Immediately, transparent electronics represented by transparent TFTs becomes one of the most nascent and attractive research areas in thin-film electronics. Continuous efforts have been made to fabricate TFTs with many TOSs including zinc oxide [14, 15], tin oxide [16], indium oxide [17-19], as well as binary or ternary oxide compounds such as zinc-tin oxide [20, 21], zinc-indium oxide [22], zinc-indium-tin oxide [23], and indium-gallium-zinc oxide [24-27]. The field-effect mobility of these TFTs is generally in the range of 10~30 cm²/Vs. Compared with their silicon and organic counterparts, TOS TFTs have much higher field-effect mobility, leading to a higher drain current density which is well suited for current-driven organic light-emitting diode (OLED) displays. Furthermore, low temperature process renders TOS TFTs compatible with future generation of large area electronics that require flexible substrates [24].

Table 1.3 summarizes the available TFT technologies. Compared with amorphous silicon and organic TFTs, TOS TFTs demonstrate the potential for better device characteristics in terms of mobility, leakage current, processing temperature, and transparency as a bonus. With the continuous research and development efforts, TOS TFT technology is believed to be an attractive alternative to existing TFT technologies.

Table 1.3: Comparison of available TFT technologies

| Tuote 1.5. Comparison         | Poly-Si     | uc-Si TFT | a-Si:H    | Organic TFT | TOS TFT   |

|-------------------------------|-------------|-----------|-----------|-------------|-----------|

|                               | TFT         |           | TFT       |             |           |

| Circuit Type                  | CMOS        | NMOS      | NMOS      | PMOS        | NMOS      |

| <b>Device Performance</b>     |             |           |           |             |           |

| -Mobility                     | Good        | Good      | Poor      | Poor        | Good      |

| -Leakage Current              | Medium      | High      | Low       | Medium      | Low       |

| -Uniformity                   | Poor        | Good      | Good      | Good        | Good      |

| -Stability                    | Good        | NA        | Poor      | Poor        | NA        |

| Cost                          | High        | Low       | Low       | Very low    | Medium    |

| <b>Processing Temperature</b> | High        | Low       | Low       | Very low    | Very low  |

| Flexible Substrate            | Alternative | Promising | Promising | Promising   | Promising |

| Transparent                   | No          | No        | No        | Can be      | Can be    |

Besides the research on TOS TFTs, some work has been conducted in TOS-based thin-film diodes. The primary application is for ultraviolet (UV) sensors. Wide bandgap semiconductors, including GaN, ZnS, and SiC are commonly used to form solar-blind UV sensors [28]. However, the integration of these devices with CMOS circuits is a complex technological issue. UV sensors based on oxide semiconductors such as ZnO can overcome this obstacle and offer significant advantages in terms of fabrication cost and processing simplicity [29].

## 1.3.1 Research Challenges

The advancement of transparent electronics largely depends on an in-depth understanding of oxide semiconductor physics and chemistry, material and device processing issues, and more important, device physics. In this section, several challenges in transparent electronics are addressed and some of them are the focus of this thesis work.

As discussed previously, most TFTs use ZnO-based oxide semiconductors as channel materials. Very few attempts have been made to fabricate singular indium oxide TFTs. However, the indium oxide TFTs exhibit the highest field-effect mobility of  $\sim 180 \text{ cm}^2/\text{Vs}$ , one order of magnitude higher than the other TOS competitors, and looks promising for TFT applications [18].

The reason for the unpopularity of In<sub>2</sub>O<sub>3</sub> TFT research is mainly due to the challenge of producing semiconducting indium oxides. Conventional sputtering techniques have been employed as an appropriate technology to prepare most oxide semiconductors including ZnO, SnO<sub>2</sub>, and other multi-component oxides such as In-Ga-Zn-O. However, it is difficult to deposit semiconducting indium oxide with a low background carrier concentration. Since as a doubly-charged donor, oxygen vacancy doping in indium oxide is more efficient than that in Zn- and Sn-oxide systems [2], it becomes difficult to effectively control the oxygen vacancies in indium oxides and thereby the free carrier density. Consequently, new techniques are pivotal to prepare semiconducting indium oxides for active devices.

Apart from this, a gate dielectric with a low defect density, a high break down voltage, and a highly packed density is another vital factor to achieve high-performance TOS TFTs. To date, a few gate dielectrics have been used in TOS TFTs, including thermally grown SiO<sub>2</sub> [12, 22], sputtered SiO<sub>2</sub> [30], laser-ablated Y<sub>2</sub>O<sub>3</sub> [24], e-beam evaporated Al<sub>2</sub>O<sub>3</sub> [31], atomic layer deposited Al<sub>2</sub>O<sub>3</sub> and hafnium oxide [32], Al<sub>2</sub>O<sub>3</sub> and TiO<sub>2</sub> superlattices [14, 20], and self-assembled organic polymers [18]. The most commonly-used gate dielectrics in modern TFTs, SiO<sub>x</sub> and SiN<sub>x</sub>, deposited by plasma-enhanced chemical vapour deposition (PECVD) are not that popular in TOS

TFTs and the viability of PECVD dielectrics in TOS TFTs remains unproven. There are very few reports on the fabrication of TOS TFTs with PECVD-derived gate dielectrics. Presley et al. have reported indium-gallium oxide TFT circuits with PECVD SiO<sub>x</sub> [33]. Carcia et al. have conducted a comparative study of zinc oxide TFTs with PECVD SiO<sub>x</sub> and SiN<sub>x</sub> dielectrics [34]. Recently, it has been demonstrated at the University of Waterloo, the stable indium oxide TFTs with a PECVD SiO<sub>x</sub> gate dielectric [19]. However, to our knowledge, high-mobility TOS TFTs with PECVD dielectrics have not been reported.

Besides device performance, two other concerns: device stability and dynamic characteristics, have also not well addressed for these TFTs. Even though some preliminary studies on oxide TFTs has been conducted by several groups [19, 35, 36], information on these two issues is sparse and a more detailed study is necessary. Thus, one part of this thesis is dedicated to device stability and dynamic behaviour.

With regards to TOS-based diodes, one serious problem is the imperfection and interfacial defects which cause a very high leakage current. Therefore, the task is to fabricate TOS-based diodes with a decreasing leakage current. In addition to this, an investigation of leakage mechanism in TOS-based diodes is also required.

# 1.4 Organization of the Thesis

This section describes the organization of this thesis. First, Chapter 2 is a discussion of IBAE as the fabrication technique in this research. After the introduction of the deposition system, some key deposition parameters are described.

In Chapter 3, a detailed material study for both ZnO and In<sub>2</sub>O<sub>3</sub> is conducted. The electrical properties, chemical composition, optical properties, crystal structure, intrinsic stress, topology, and morphology, are measured in order to fully examine the material properties by the IBAE.

Thin-film devices are demonstrated by employing optimized semiconducting oxide thin films. In Chapter 4, ZnO-based heterostructure diodes are fabricated and characterized. The device analysis including current-voltage characteristics, current transients, leakage current, and spectral response, is followed.

Chapter 5 details indium oxide TFTs with gate dielectrics by PECVD. The device analysis includes transfer and output characteristics, device stability, and dynamic behaviour.

Lastly, Chapter 6 concludes this thesis and summarizes its contribution to the field of transparent electronics.

# **Chapter 2**

# **Fabrication Technique**

This chapter describes the fabrication technique for developing TOSs. After a brief introduction of the IBAE technique, the schematic structure of the system is presented. Since the ion source is a very important unit in such a system, one section is devoted to the working principle of the ion source. In the last section, a discussion of the deposition parameters is given.

# 2.1 Introduction

IBAE deals with the use of energetic ions to assist the growth of thin films. It combines a traditional evaporation technique with an independent ion source, providing more capability in thin-film growth and processing.

Generally, the bombardment of a growing film with energetic particles has been recognized to produce significant modification such as improved adhesion, densification, texture, grain size, crystallinity, and morphology in thin-film properties [37]. Here, the energetic particles refer to those with kinetic energies that are typical of ion beam assistance processing; that is from a few tens to approximately one thousand electron volts (eV). For the purpose of substrate pretreatment or precleaning, a few tens of eV is enough to remove most of the physical and chemical adsorbed contaminants and moisture. Regarding the assistance of thin-film growth, a kinetic energy as much as one thousand eV is suitable and avoids plasma damaging and etching. Since most particles are ions and radicals, throughout this thesis, the term,

ion, is used for the impinging particles that assist thin-film growth. However, it is noteworthy that ion refers to two particles: ions and radicals. An independent ion source also offers the possibility of realizing reactive evaporation. For instance, in the preparation of oxides, an oxygen ion source can provide reactive oxygen ions during the oxide growth. Compared with a conventional reactive evaporation, immersed in an oxygen atmosphere, reactive IBAE is more feasible for low temperature deposition and more effective control in the stoichiometry.

## 2.2 Ion Beam Assisted Evaporation

The IBAE technique can be realized in several experimental configurations. In general, it consists of an independent ion source and a traditional evaporator. The ion source can be in different types such as Kaufman-type ion source, End-Hall ion source, and plasma-based ion source [38]. Evaporation can be carried out either by the resistive heating of a crucible or more efficiently, by the electron beam (e-beam) bombardment of a bulk solid.

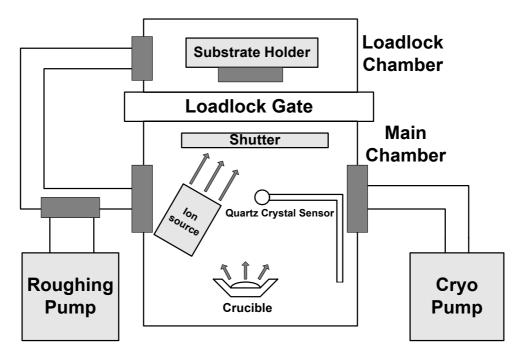

# 2.2.1 Schematic Configuration of the IBAE system

A typical IBAE system is illustrated schematically in Figure 2.1. It consists of dual chambers: the main vacuum chamber and the loadlock chamber. An evaporator and ion source are housed in the main chamber. The roughing pump and cryopump serve the system with a base pressure down to  $\sim 10^{-6}$  torr. The gas introduced into the system generates a desirable range of working pressure of approximately  $10^{-3}\sim 10^{-4}$  torr. The loadlock chamber separates the sample holder and main chamber by a loadlock gate

to facilitate an efficient pumping to attain the base pressure. The equipped quartz crystal sensor is used to in-situ monitor the thickness and evaporation rate during film growth. In some systems, the Faraday cup is employed to measure the ion beam flux and energy simultaneously. An independent ion source allows the independent control of the ion type, energy, and flux, which ultimately provides the capability to deposit different kinds of materials.

Figure 2.1: Schematic structure of a typical IBAE system

#### 2.2.2 Reactive IBAE

Thanks to more reliable ion sources, reactive IBAE technique is developing rapidly in thin-film fabrication, particularly in the low temperature deposition of oxides and nitrides. A high portion of ion beam processing deals with an inert gas such as Ar, He, and Ne. The ion effects are mainly physical. In a traditional reactive evaporation, oxygen or nitrogen gas is introduced into the vacuum chamber. It can be less efficient,

since the oxygen or nitrogen is in the form of atom, not as radical and reactive as oxygen or nitrogen plasma. Reactive ion assisted evaporation, however, uses oxygen or nitrogen ions as reactants and it is a technique that is emerging for the fabrication of many oxide or nitride compounds at low temperatures.

The system adopted in this research includes a typical e-beam evaporator and an independent oxygen ion source. The distance between the substrate and evaporation source is fixed at 35 cm. The oxygen ion source module is located 20 cm below the substrate with an incident angle of 60°. The water-cooling coils surrounding the sample holder maintains a substrate temperature below 40°C, principally coming from the oxygen plasma heating during deposition. Figure 2.2 and Figure 2.3 are photographs of the IBAE system and the main chamber during deposition.

Figure 2.2: IBAE system used in this research

Figure 2.3: Main chamber during deposition

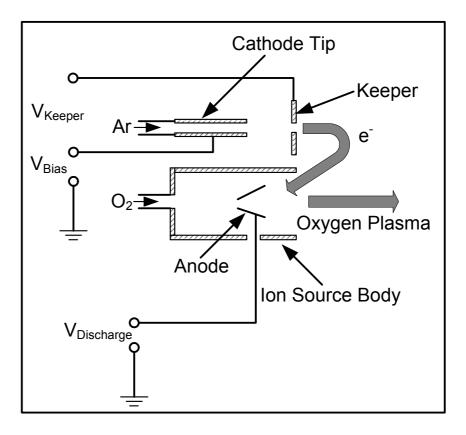

## 2.2.3 Oxygen Ion Source

The ion source plays a very important role in the reactive IBAE. Several commercially-available ion sources exist for different applications. The most commonly-used ion sources include the Kaufman-type ion source, End-Hall ion source, and filament-less ion source. The difference between each ion source lies in the mechanism and set-up of its plasma generator. The oxygen ion source in our IBAE system is the Kaufman-type ion source. Figure 2.4 is a schematic diagram of the oxygen ion source. The module includes a hollow cathode electron source, where the keeper tube generates a high voltage between the cathode tip and the keeper to ionize the Ar gas. The keeper first initiates the discharge of the Ar gas into the hollow cathode electron source. Once the bias voltage is applied, electrons flow toward the anode, but are prevented from flowing directly to the positive anode by the magnetic

field. The electrons bombard the oxygen gas to create the oxygen ions. They are then accelerated by the discharge voltage and reach the substrate.

Figure 2.4: Schematic diagram of oxygen ion source

# 2.3 Deposition Parameters

The deposition rate, ion beam energy and flux, dynamic pressure, and substrate temperature are among the deposition parameters, determining the film properties. Table 2.1 gives the deposition parameters of the IBAE technique used in this research.

Since the material properties such as resistivity and transparency correlate to the composition of the films, the ratio between the ion flux and arrival atoms from the evaporation source becomes the most important factor in the reactive IBAE.

Therefore, in the material development, the idea is to control the film properties by simply modifying the oxygen ion beam flux, ion beam energy, and metal evaporation.

Table 2.1: Deposition parameters of the IBAE technique

| Parameters            | Typical Range                 | Comments                                                                                                            |

|-----------------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Deposition Rate       | $0.5 \sim 4 \text{ Å/s}$      | It varies with the metal evaporation and oxygen ion flux.                                                           |

| Discharge Current     | 0.5 ~ 3.0 A                   | It is proportional to the ion flux with a density ranging from 0.025 mA/cm <sup>2</sup> to 0.1 mA/cm <sup>2</sup> . |

| Discharge Voltage     | 80 ~ 180 V                    | It is proportional to the ion beam energy with a range of 50 to 130 electron volts.                                 |

| Substrate Temperature | $30 \sim 40^{\circ} \text{C}$ | It is due to plasma heating during deposition.                                                                      |

| Dynamic Pressure      | 0.1 ∼ 1 mTorr                 | It is adjusted with a flow rate of $O_2$ (5 ~ 20 sccm); The flow rate of Ar stays at 10 sccm during deposition.     |

# **Chapter 3**

# **Material Study**

This chapter describes the preparation, characterization, and optimization of TOSs. Two widely-used TOSs are fabricated. One is ZnO and the other is  $In_2O_3$ . The correlations between deposition conditions and thin-film properties are also investigated.

#### 3.1 Zinc Oxide

#### 3.1.1 Introduction

Zinc oxide thin films are deposited by the reactive IBAE [39]. A high-purity zinc metal is chosen as the evaporation source, and the oxygen reactants are introduced in the forms of oxygen ions, generated by the oxygen ion source. The discharge voltage and current of the ion source are proportional to the oxygen ion energy and flux, respectively. The electrical and optical properties of IBAE-derived ZnO thin films are examined in the following sections.

## 3.1.2 Deposition Rate

In the reactive IBAE, the deposition rate depends on the number of arrival atoms and their migration on the substrate. The arrival mass and migration are determined by the evaporation rate of zinc, the oxygen ion flux, and the oxygen ion energy. The IBAE system has a deposition controller and quartz crystal sensor to set the deposition rate

while the actual evaporation is monitored. The measured deposition rate can differ from the set deposition rate. Therefore, the first thing that should be done is to calibrate the deposition rate before each deposition.

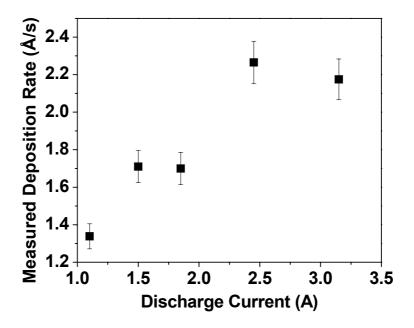

Figure 3.1: Deposition rate calibrated in terms of the discharge current

Figure 3.1 denotes the calibration of the deposition rate in terms of the discharge current. The measured deposition rate varies slightly from the deposition rate (1.5 Å/s) set in the deposition controller. The measured deposition rate increases with the discharge current, which is reasonable because the greater the ion beam flux, the greater the film growth.

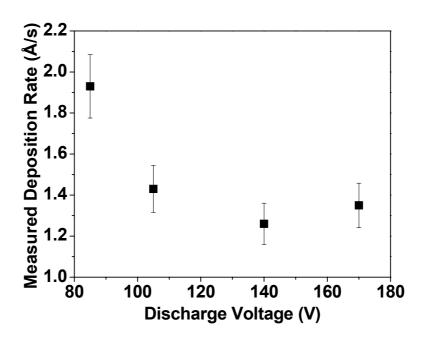

Figure 3.2: Deposition rate calibrated in terms of the discharge voltage

Similarly, the deposition rate is also calibrated in relation to the discharge voltage, which is proportional to the ion beam energy as observed in Figure 3.2. The set deposition rate is 1.5 Å/s. Here, the measured deposition rate decreases with the discharge voltage due to the atom peening effects which high-energy ions usually display [38]. Therefore, a low or modest discharge voltage is preferred in order to avoid any plasma damaging during deposition.

## 3.1.3 Electrical Properties

Since the primary goal of this chapter is to develop semiconducting ZnO thin films for active device applications, the first priority is to study the electrical properties: the resistivity of IBAE-derived ZnO thin films and the dependence of resistivity on the deposition parameters.

The ZnO films are deposited on Corning 1737 glass substrates for resistivity evaluation. All the films have a thickness of approximately 100 nm. The resistivity measurements are performed by sputtering Molybdenum (Mo) on the top of the ZnO films through a shadow mask on which the electrode patterns are defined by different widths and lengths. The resistivity of ZnO films is then extracted from the current-voltage curves by microprobing the electrodes.

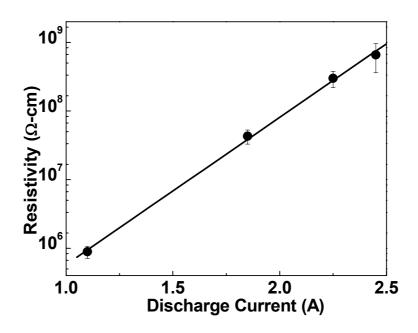

Figure 3.3: Resistivity of the ZnO films as a function of the discharge current

Figure 3.3 illustrates the dependence of the ZnO resistivity on the discharge current. The deposition rate and discharge voltage are maintained at the constants of 1.5 Å/s and 120 V, respectively. By increasing the discharge current, the resistivity of the ZnO films increases from  $9\times10^5$   $\Omega$ -cm to  $7\times10^8$   $\Omega$ -cm. Since the discharge current is proportional to the ion beam flux, the oxygen vacancy concentration inside ZnO films also rises with the discharge current.

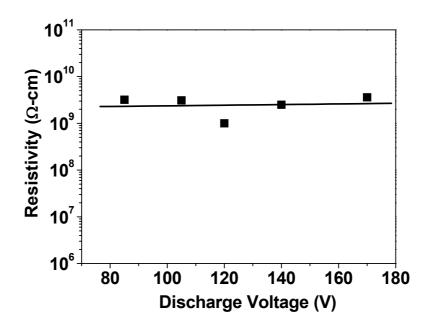

Figure 3.4 depicts the resistivity of the ZnO films as a function of the discharge voltage. The deposition rate and discharge current are fixed at 1.5 Å/s and 2.5 Å, respectively. The resistivity does not change when the discharge voltage is in the range of 80 V to 180 V, suggesting that the discharge voltage is not a determining parameter, in particular, for the resistivity.

Figure 3.4: Resistivity of the ZnO films as a function of the discharge voltage

Active semiconductor devices such as TFTs require semiconducting films with a low background carrier concentration and high carrier mobility. The experimental results in this thesis indicate that by simply modifying the discharge current, it is possible to achieve semiconducting ZnO thin films with a resistivity ranging from  $10^6$   $\Omega$ -cm to  $10^8$   $\Omega$ -cm that is appropriate for device applications. To avoid high-energy ion damage, a modest discharge voltage of  $100\sim120$  V should be chosen for the following semiconducting film deposition.

### 3.1.4 Optical Properties

In this section, the optical properties of the IBAE-derived ZnO thin films are investigated. After the optical transmittance and optical constants of the ZnO films are measured, the optical bandgaps of the ZnO thin films are extracted from an absorption model. The optical transmittance is measured by a Shimadzu UV/Vis spectrometer (UV-2501PC) in a wavelength range of 300 to 800 nm with a measurement resolution of 1 nm. The film thickness for the transmittance measurements is around 100 nm.

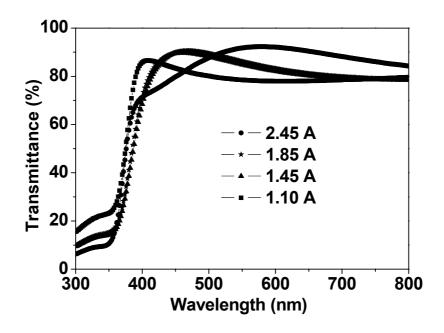

Figure 3.5: Transmittance spectra of the 100 nm ZnO films deposited at different discharge currents

Figure 3.5 plots the transmittance spectra of the 100 nm ZnO thin films, deposited at different discharge currents. The discharge voltage and deposition rate are set at 120 V and 1.5 Å/s, respectively. Figure 3.6 displays the transmittance of the 100 nm

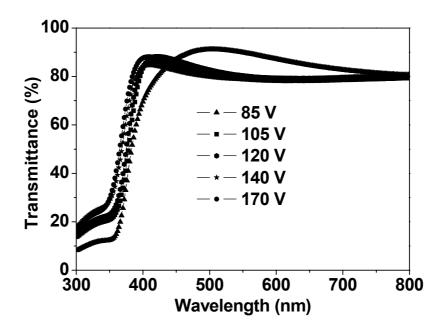

ZnO films, deposited at different discharge voltages. The deposition rate and discharge current are kept constants at 1.5 Å/s and 2.25 A, respectively.

Figure 3.6: Transmittance spectra of the ZnO films deposited at different discharge voltages

In the visible region, with a wavelength ranging from 400 to 700 nm, all the ZnO films are highly transparent with an average transmittance of more than 85%, and the transmittance spectra are not very dependent on either the discharge current or the discharge voltage.

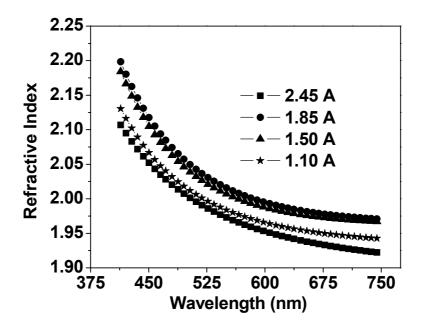

Another optical parameter, refractive index (n) as a function of the visible wavelength, is also evaluated. The refractive index is measured by a spectroscopic ellipsometer, produced by J. A. Woollam Co.. The value of n should slightly increases with the decrease of the wavelength in the visible region due to dispersion effects [2].

The best fit for the refractive index as a function of the wavelength is to use the following three-term Cauchy equation [29]:

$$n(\lambda) = A + \frac{B}{\lambda^2} + \frac{C}{\lambda^4},\tag{3-1}$$

where A, B, and C are parameters that fits the Cauchy model.

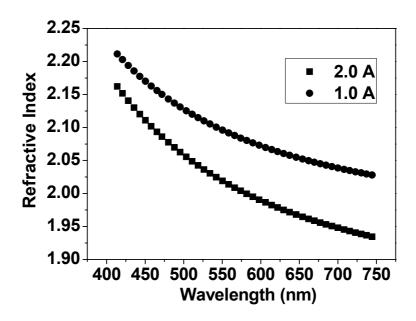

Figure 3.7: Variation of the refractive index with the wavelength of the ZnO films deposited at different discharge currents

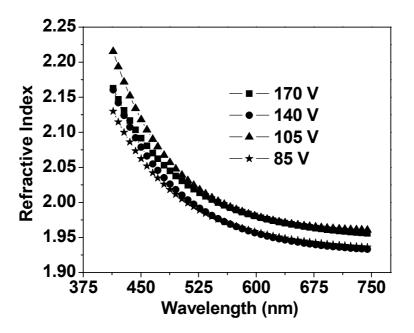

Figure 3.7 presents the variation of the refractive index with the wavelength of the ZnO films, deposited at different discharge currents with a fixed deposition rate of 1.5 Å/s and a discharge voltage of 120 V. Figure 3.8 gives the refractive index as a function of the wavelength of the ZnO deposited at different discharge voltages, whereas the deposition rate and discharge current are selected as 1.5 Å/s and 2.25 A, respectively. As observed, the refractive index depends very little on the discharge

current or discharge voltage. The index ranges from 1.90 to 2.20 in the visible region, which is consistent with the results in the literature, and is close to the refractive index of the bulk ZnO [2]. In this wavelength range, the extinction coefficient can be negligible because all the films are highly transparent with very weak absorption.

Figure 3.8: Dependence of the refractive index on the wavelength of the ZnO films deposited at different discharge voltages

The optical bandgap of the ZnO films can be extracted according to the direct band-to-band transition model [2]:

$$(hv\alpha)^2 = \alpha_0(hv - E_{gap}), \qquad (3-2)$$

where hv is the photon energy,  $\alpha$  is the absorption coefficient,  $\alpha_0$  is approximately a constant that is independent of the photon energy, and  $E_{gap}$  is the optical bandgap.

The curve  $(hv\alpha)^2$ , in terms of hv extrapolated to zero, yields the value of  $E_{gap}$ .  $\alpha$  is obtained from the transmittance by the relation [2]:

$$T = (1 - R)^2 \exp(-\alpha t),$$

(3-3)

where T is the transmittance, R is the reflectance, and t is the film thickness. By assuming R << 1 in the absorption region of the ZnO films, the absorption coefficient is simplified to:

$$\alpha = \frac{1}{t} \ln(\frac{1}{T}). \tag{3-4}$$

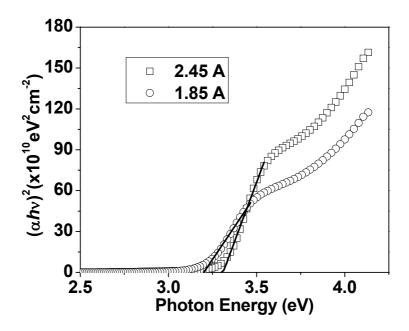

Figure 3.9: Representative absorption curves of the ZnO films deposited at the discharge of 2.45 A and 1.85 A for the optical bandgap extraction

Figure 3.9 sketches two representative absorption curves of the ZnO films for the optical bandgap extraction. The 100 nm films are deposited at a deposition rate of 1.5 Å/s and discharge voltage of 120 V, and the two discharge currents of 1.85 A and

2.45 A, respectively. The extracted optical bandgap is around 3.2 eV for the 1.85 A film and 3.3 eV for the 2.45 A film, both very close to those reported undoped ZnO films in the literature [2].

#### 3.1.5 Crystal Structure

The crystal structure of the deposited semiconducting ZnO film is obtained by performing x-ray diffraction (XRD) measurements with a Rigaku D/MAX 2000 x-ray diffractometer (Source: Cu K $\alpha_1$  with a wavelength of 1.54056 Å; Tube voltage: 50 kV; and Tube current: 40 mA).

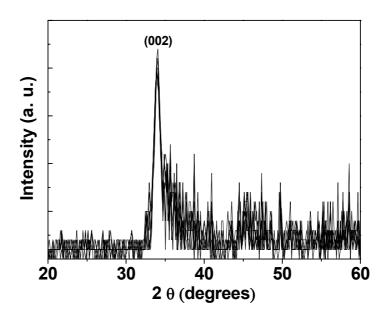

Figure 3.10: XRD patterns of the semiconducting ZnO film

Figure 3.10 reflects the XRD patterns with 2  $\theta$ , ranging from  $20^0$  to  $60^0$  of the semiconducting ZnO film, fabricated at a discharge current of 2.25 A, discharge voltage of 120 V, and deposition rate of 1.5 Å/s. Only the (002) peak at 2  $\theta \approx 34^0$  is

observed, identifying the formation of the ZnO film with a hexagonal structure and a preferred orientation with the c-axis perpendicular to the substrate. Calculated from the Scherrer formula:

$$D = \frac{K\lambda}{B_{1/2}\cos\theta},\tag{3-5}$$

in which D is the average grain size,  $\lambda$  is the wavelength of the incident x-ray, K is a numerical constant from 0.95  $\sim$  0.98,  $\theta$  is the Bragg angle, and  $B_{1/2}$  is the full-width half-maximum, the estimated average grain size is around 13 nm.

#### 3.2 Indium Oxide

Indium oxides are also fabricated by the reactive IBAE [40]. A high-purity indium is used as the evaporation source. The electrical properties are first characterized, followed by the chemical composition, optical properties, crystal structure, intrinsic stress, topology, and morphology.

## 3.2.1 Electrical Properties

In the reactive IBAE, in order to achieve semiconducting indium oxides for the active device applications, the oxygen vacancy concentration must be restrained as discussed in Section 1.2.2. Therefore, the indium and oxygen atom arrival ratio to the substrate are modified by adjusting two most important deposition parameters: deposition rate and oxygen ion flux.

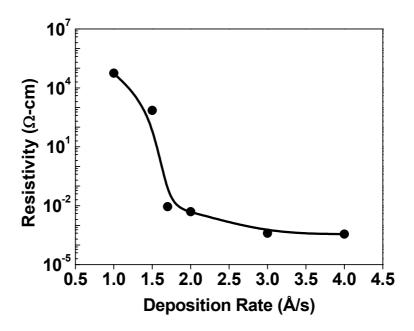

Figure 3.11: Dependence of the resistivity of the indium oxide films on the deposition rate

Figure 3.11 illustrates the dependence of the resistivity on the deposition rate. All the indium oxide films are deposited on Corning 1737 glass substrates with a thickness of ~100 nm. The discharge voltage and current of oxygen ion source are kept at 100 V and 1.0 A, respectively. As seen in Figure 3.11, the resistivity of the indium oxide films can be tuned from  $10^5~\Omega$ -cm down to  $10^{-4}~\Omega$ -cm by simply increasing the deposition rate. At a deposition rate higher than 3 Å/s, the resistivity approaches a stable value of  $5\times10^{-4}~\Omega$ -cm, on par with the current TCOs for flatpannel displays [2]. At lower deposition rates, the resistivity undergoes a sharp transition from the conducting (~  $10^{-2}~\Omega$ -cm) to the semiconducting states (~  $10^3~\Omega$ -cm), suggesting a critical oxygen vacancy concentration that causes a shift of the Fermi-energy level from close to the conduction band down to close to the midbandgap.

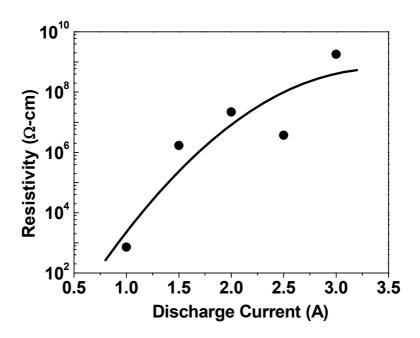

Figure 3.12: Variation of the resistivity of the indium oxide films with the discharge current

Figure 3.12 exhibits the variation of the resistivity of the indium oxide films with the discharge current. The deposition rate and discharge voltage are set at 1.5 Å/s and 100 V, respectively. In non-stoichiometric indium oxides, the oxygen vacancies act as doubly-charged donors [2]. Therefore, a small discharge current: that is less oxygen ions, tends to generate a high population of oxygen vacancies, and consequently, a low resistivity. In contrast, a large discharge current helps decrease the population of the oxygen vacancies, leading to an increased resistivity. Moreover, it is found that the resistivity of the indium oxide films can reach values as high as  $10^9 \,\Omega$ -cm, which is difficult to achieve with conventional sputtering or evaporation. Thus, the IBAE allows the engineering of the resistivity of indium oxides from metallic to insulating. Such a wide range of variation in the resistivity also indicates that the defect density

in these films is not that high, and the Fermi-energy level is not pinned, such that it can be shifted from the conduction band edge to close to the mid-bandgap.

#### 3.2.2 Compositional Analysis

To verify that the oxygen concentration inside the films changes with the deposition conditions and to identify how the concentration depends on the oxygen ion flux, x-ray photoelectron spectroscopy (XPS) measurements are performed in a multiple-technique ESCA microprobe system (VG ESCALab 250). In addition, XPS can be used to identify the chemical bonding states of the indium oxides.

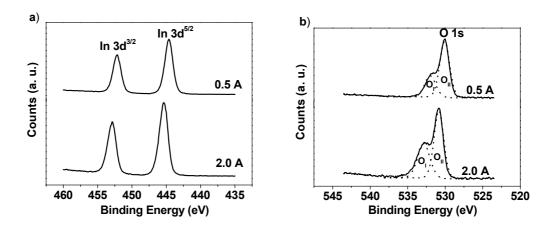

Figure 3.13: XPS spectra of (a) In 3d and (b) O 1s of the indium oxide films deposited at two different discharge currents of 0.5 A and 2.0 A

Figure 3.13 depicts the XPS spectra of In 3d and O 1s of the indium oxide films, deposited at the two different discharge currents of 0.5 A and 2.0 A for comparison. The binding energy of In 3d<sup>5/2</sup> and In 3d<sup>3/2</sup> is located at 444.6 eV and 452.2 eV for the 0.5 A film, similar to that of ITO reported elsewhere [5, 41]; and 445.3 eV and 452. 9 eV for the 2.0 A film. A shoulder peak appears adjacent the main peak of the O

1s spectra in both samples, as shown in Figure 3.13 (b). Two Gaussian functions with variable positions and intensities are used to deconvolute each spectrum, where the two resolved peaks in the O 1s spectrum are located at 530.1 eV and 531.9 eV for the 0.5 A film, and 530.8 eV and 532.7 eV for the 2.0 A film. Both the In 3d and O 1s spectra shift towards the lower binding energy by decreasing the oxygen ion flux. It is indicated that the oxygen bonding states depend more strongly on the discharge current compared with the In bonding states. Also from the XPS spectra, two types of  $\mathrm{O}^{2\text{-}}$  ions are distinguished:  $\mathrm{O}_{I}$  and  $\mathrm{O}_{II}.$  The main peak of  $\mathrm{O}_{II}$  is related to the O-In state, where the In atoms with the six closet O<sup>2-</sup> ions form the InO<sub>6</sub> octahedra. The subpeak of O<sub>1</sub> with a higher binding energy is associated with an O-In binding state in the oxygen-deficient region [5]. Consequently, O<sub>I</sub> is more sensitive to the loss of oxygen. Compared with the integrated areas of the In 3d<sup>5/2</sup> and O 1s peaks, the relative atomic ratio between indium and oxygen can be calculated. This ratio is 0.61 for the 0.5 A film and 0.53 for the 2.0 A film. Thus, by tuning the oxygen ion flux, the stoichiometry of indium and oxygen inside the film can be varied. The more oxygendeficient film is obtained at a smaller discharge current and the more oxygen-rich film is achieved at a larger discharge current, which is also in line with the resistivity results. For the TCO applications, the more oxygen-deficient film with a high conductivity is needed, whereas for the device applications, oxygen-rich films with a low electron density are desirable.

### 3.2.3 Optical Properties

The visible transmittance, the refractive index, and the extracted optical bandgap of indium oxides are presented. The measurements and extraction are similar to those for the ZnO films. The details are found in Section 3.1.4.

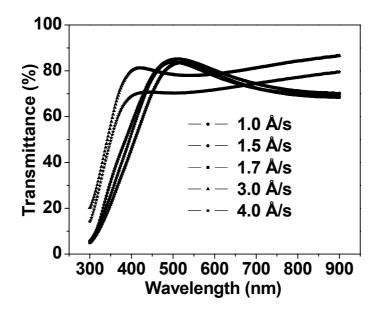

Figure 3.14: Transmittance spectra of the indium oxide films deposited at different deposition rates

Figure 3.14 shows the transmittance of the indium oxide films, deposited at different deposition rates. The discharge voltage and current are fixed at 100 V and 1.0 A, respectively. The film thickness is approximately 100 nm. The wavelength ranges from 300 to 900 nm. An average visible transmittance of more than 80 % is achieved for all the derived indium oxide films. The strong near-UV absorption is observed due to the band-to-band transition. Also, it is found that the transmittance spectra of the indium oxide films, fabricated at a higher deposition rate demonstrate

the blue shift: that is the transmittance spectrum shifts towards short wavelengths. This can be due to Burstein-Moss effect described as [2]:

$$E_g - E_{g0} = \frac{(\pi h)^2}{2m_r^*} (\frac{3N}{\pi})^{2/3}$$

(3-6)

where  $E_g$  is the optical bandgap,  $E_{g0}$  is the intrinsic optical band gap,  $m_r^*$  is the effective mass, and N is the free carrier density. The shift towards shorter wavelengths is caused by the increased free carrier density in the films with the deposition rates of 3 Å/s and 4 Å/s.

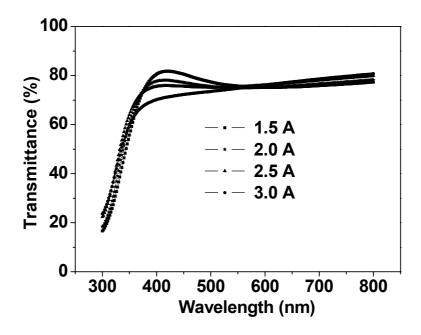

Figure 3.15: Transmittance spectra of the indium oxide films deposited at different discharge currents

Figure 3.15 illustrates the transmittance of the indium oxide films, deposited at different discharge currents. The deposition rate and discharge voltage are kept constants at 1.5 Å/s and 100 V, respectively. The thickness of all the deposited films

is approximately 100 nm. The transmittance varies little with the discharge current for the semiconducting indium oxides with an overall average visible transmittance of around 80%. The blue shift is not observed since the indium oxides, deposited under these conditions, are not degenerated and the free carrier density is not that high.

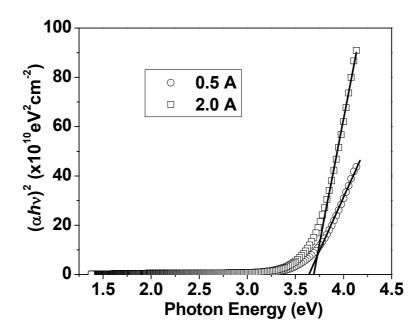

Figure 3.16: Representative absorption curves of the indium oxides deposited at the discharge currents of 0.5 A and 2.0 A for the optical bandgap extraction

Figure 3.16 conveys the direct optical bandgap extraction for the indium oxides, deposited at the discharge currents of 0.5 A and 2.0 A, while the deposition rate and discharge voltage remain at 1.5 Å/s and 100 V, respectively. The bandgap is retrieved from the transmittance data by extrapolating the linear part of the  $(\alpha hv)^2$  versus the photon energy hv plot to the absorption coefficient,  $\alpha = 0$ , as seen in Figure 3.16, yielding 3.6~3.7 eV for both the conducting and semiconducting indium oxides. This value is also close to that reported in the literature [2].

Figure 3.17: Refractive index of the indium oxides fabricated at two different discharge currents

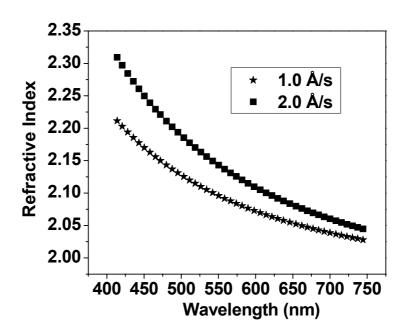

The refractive index in the relation to the wavelength curves of the indium oxides fabricated at two different discharge currents are shown in Figure 3.17. The deposition rate and discharge voltage are chosen as 1.0 Å/s and 100 V, respectively. Figure 3.18 presents the refractive index as a function of the wavelength of the indium oxides deposited at two different deposition rates. The discharge voltage and current are kept at 100 V and 1.0 A, respectively. The refractive index ranges from 2.30 to 1.95. The value slightly varies with the deposition conditions. Since the discharge current and deposition rate in the reactive IBAE affect the chemical composition of indium oxides, it is anticipated that the refractive index is dependent on the oxidation: that is more oxidized samples have the relatively smaller refractive index.

Figure 3.18: Refractive index of the indium oxides deposited at two different deposition rates

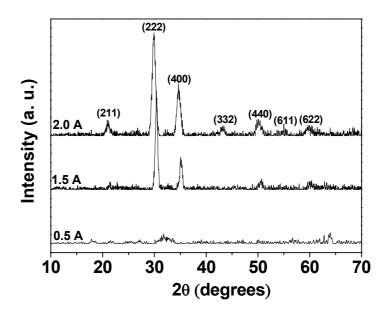

## 3.2.4 Crystal Structure

The crystal structure of the indium oxides are evaluated by the XRD technique performed by the same diffractometer described in Section 3.1.5. The structural order of the films is significantly dependent on the discharge current. Figure 3.19 signifies the XRD patterns of the indium oxide films, deposited at different discharge currents: 0.5 A, 1.5 A, and 2.0 A. The deposition rate and discharge voltage are kept constants at 1.5 Å/s and 100 V. The 1.5 A and 2.0 A films are polycrystalline with a dominant (222) orientation, whereas the 0.5 A film is amorphous in nature. As observed from the increased number of diffraction peaks, a large discharge current helps improve the structural ordering. The estimated grain size for the 2.0 A film is around 12 nm from the Scherrer formula.

Figure 3.19: XRD patterns of the indium oxide films deposited at different discharge currents: 0.5 A, 1.5 A, and 2.0 A

The reactive IBAE is proven a versatile technique that allows for modifying the crystal structure of the indium oxide films from amorphous to polycrystalline simply by adjusting the discharge current of the oxygen ion source.

#### 3.2.5 Intrinsic Stress

The obvious shift of the XRD peaks in Figure 3.19 is most likely caused by the intrinsic stress, generated from the growth process. To identify this, the intrinsic stress under different deposition conditions is measured. The stress measurements are performed by using a mechanical stress gauge from Ionic Systems. It is also crucial to study the film stress issue, especially for applications on flexible substrates. Excessive stress can cause the delamination of the film from the substrate. The film stress can be from thermal stress and intrinsic stress. The thermal stress arises from the difference

in the growth temperature and the thermal expansion coefficients between substrate and the grown film. The intrinsic stress is generated during the growth process varied with deposition technique and deposition conditions. Since all the films were grown at low temperature on water-cooled glass substrates ( $\sim 40^{\circ}$ C due to plasma heating during deposition), the thermal stress can be negligible, and therefore, the key stress would be intrinsic stress.

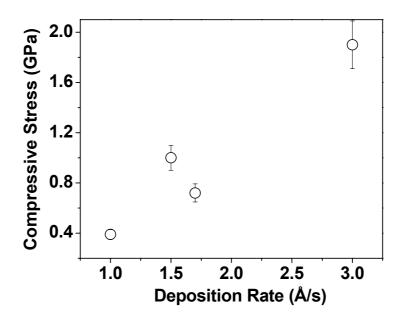

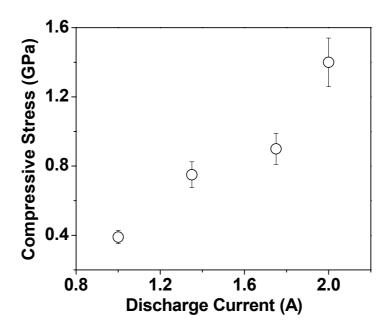

Figure 3.20: Intrinsic stress of the indium oxide films as a function of the deposition rate

Figure 3.20 displays the intrinsic stress of the indium oxide films as a function of the deposition rate. The discharge current and voltage are 1.0 A and 100 V. Figure 3.21 presents the dependence of the intrinsic stress on the discharge current, whereas the discharge voltage and deposition rate are kept constants at 100 V and 1.0 Å/s. Due to the atom peening effects [38], compressive stress generally occurs, when the

growing film is bombarded by ions with an energy of tens to hundreds of eV. In these figures, all the films have compressive stress ranging from 0.4 GPa to 1.8 GPa, slightly higher than that in the low-stress sputtered ITO films. The intrinsic stress increases with deposition rate and discharge current. This implies that the stress is proportional to the arrival mass, suggesting that a low deposition rate and low discharge current facilitates the realization of the low-stress films by the IBAE.

Figure 3.21: Intrinsic stress of the indium oxide films as a function of the discharge current

## 3.2.6 Topology

To examine the topology of the deposited films, the surface roughness is evaluated by a Veeco WYKO NT1100 optical profiler. The three surface roughness evaluation parameters are the average roughness, which is defined as the arithmetic mean or

average of the absolute distances of the surface points from the mean plane; the root mean square roughness, which is the root mean square of the surface departures from the mean plane within the sampling area; and the peak to valley roughness, which is defined as the sum of the largest peak height value and the largest valley depth from the mean plane within the sampling area.

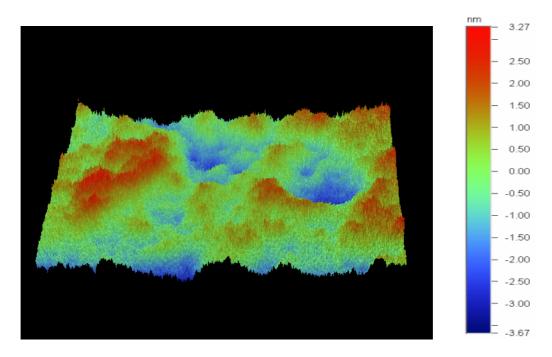

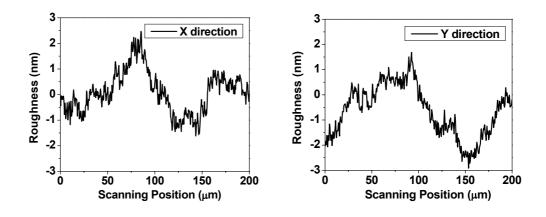

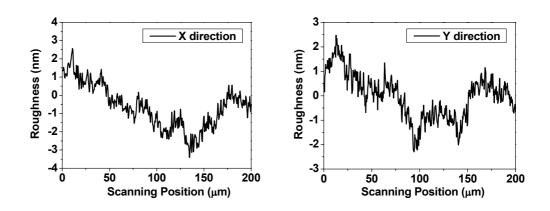

Figure 3.22 and Figure 3.23 show the image of the topology and representative surface profiles scanned in both the x- and y-directions. The 200-nm-thick film on a single crystalline silicon wafer is deposited at a discharge current of 2.0 A, discharge voltage of 100 V, and deposition rate of 1.5 Å/s. The calculated peak to valley roughness is around 4.0 nm for an area of 200  $\mu$ m×200  $\mu$ m. The calculated root mean square roughness and average roughness are  $\sim$  1.0 nm and  $\sim$  0.8 nm, respectively, comparable to those of the best ITO films by sputtering.

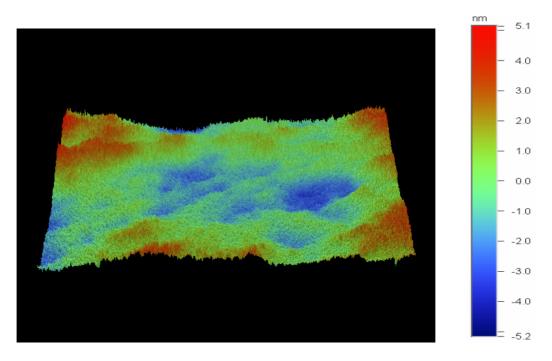

Figure 3.24 and Figure 3.25 are the image of the topology and the scanned surface profiles in both x- and y-directions for the 200 nm highly-conducting films, deposited at a rate of 3.0 Å/s. The discharge current is 1.0 A, and the discharge voltage is 100 V. The calculated peak to valley roughness is approximately 10.3 nm for the area of 200  $\mu m \times 200~\mu m$ . The calculated root mean square roughness and average roughness are  $\sim$  1.4 nm and  $\sim$  1.2 nm, respectively.

Figure 3.22: Topological image of the semiconducting indium oxide

Figure 3.23: Representative surface profiles scanned in both the x- and y- directions for the semiconducting indium oxide

Figure 3.24: Topological image of the highly-conducting indium oxide

Figure 3.25: Representative surface profiles scanned in both the x- and y- directions for the highly-conducting indium oxide

The IBAE-derived films are smoother and more uniform than those deposited by conventional evaporation, since the incident ions physically promote the migration of the atoms, which is one of the main physical effects of the IBAE technique [38].

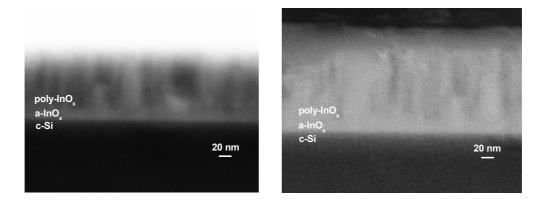

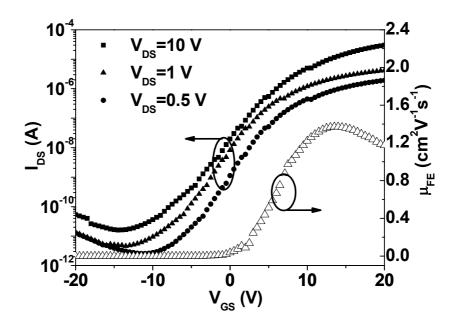

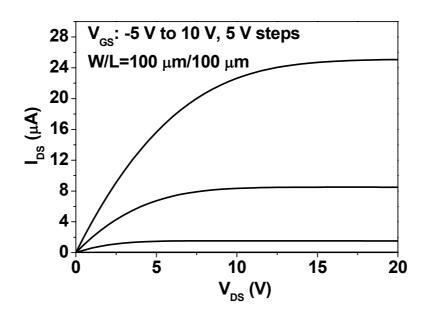

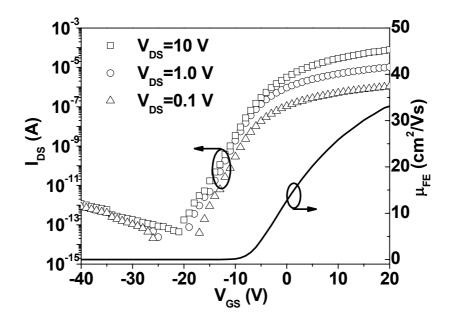

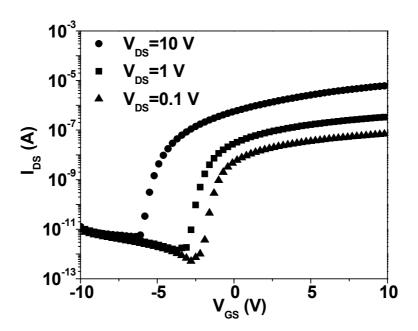

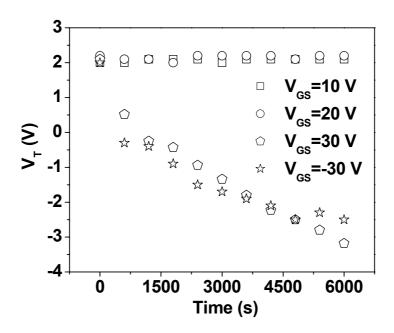

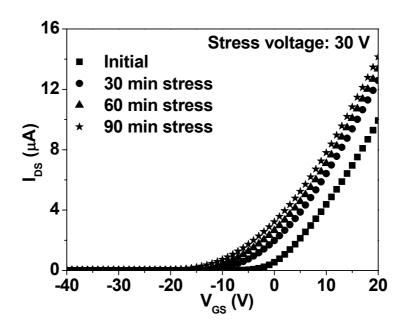

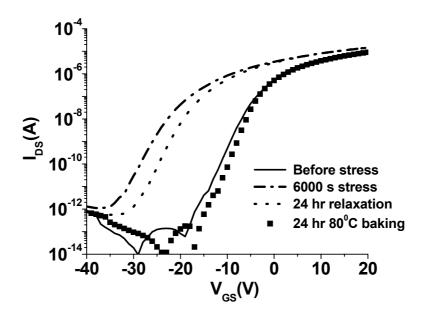

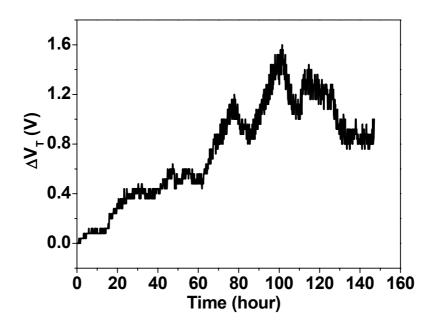

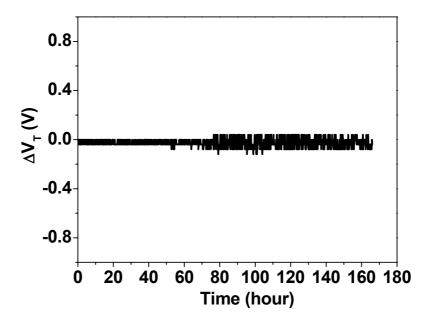

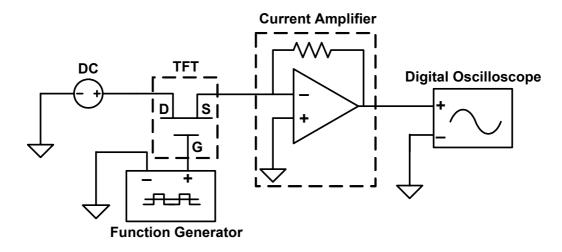

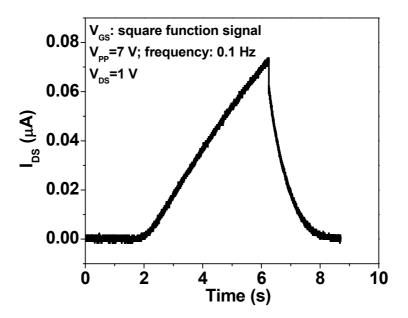

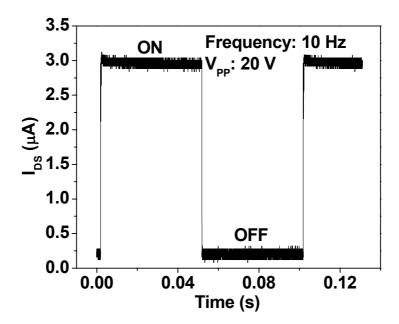

#### 3.2.7 Morphology