# Vertical Thin Film Transistors for Large Area Electronics

by

#### Maryam Moradi

A thesis

presented to the University of Waterloo

in fulfillment of the

thesis requirement for the degree of

Doctor of Philosophy

in

Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2008

© Maryam Moradi 2008

#### **AUTHOR'S DECLARATION**

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### **Abstract**

The prospect of producing nanometer channel-length thin film transistors (TFTs) for active matrix addressed pixelated arrays opens up new high-performance applications in which the most amenable device topology is the vertical thin film transistor (VTFT) in view of its small area. The previous attempts at fabricating VTFTs have yielded devices with a high drain leakage current, a low ON/OFF current ratio, and no saturation behaviour in the output current at high drain voltages, all induced by short channel effects. To overcome these adversities, particularly dominant as the channel length approaches the nano-scale regime, the reduction of the gate dielectric thickness is essential. However, the problems with scaling the gate dielectric thickness are the high gate leakage current and early dielectric breakdown of the insulator, deteriorating the device performance and reliability.

A novel ultra-thin  $SiN_x$  film suitable for the application as the gate dielectric of short channel TFTs and VTFTs is developed. The deposition is performed in a standard 13.56MHz PECVD system with silane and ammonia precursor gasses diluted in nitrogen. The deposited 50nm  $SiN_x$  films demonstrate excellent electrical characteristics in terms of a leakage current of 0.1 nA/cm<sup>2</sup> and a breakdown electric field of 5.6MV/cm.

Subsequently, the state of the art performances of 0.5um channel length VTFTs with 50 and 30nm thick  $SiN_x$  gate dielectrics are presented in this thesis. The transistors exhibit ON/OFF current ratios over  $10^9$ , the subthreshold slopes as sharp as 0.23 V/dec, and leakage currents in the fA range. More significantly, a high associated yield is obtained for the fabrication of these devices on 3-inch rigid substrates.

Finally, to illustrate the tremendous potential of the VTFT for the large area electronics, a 2.2-inch QVGA AMOLD display with in-pixel VTFT-based driver circuits is designed and fabricated. An outstanding value of 56% compared to the 30% produced by conventional technology is achieved as the aperture ratio of the display. Moreover, the initial measurement results reveal an excellent uniformity of the circuit elements.

#### Acknowledgments

I would like to express my gratitude and sincere appreciation to my supervisor, Prof. Arokia Nathan, for his support, guidance, and encouragement during my Ph.D. studies. Indeed, it is my honor to be his student and I would like to thank him for the opportunity to continue working with him despite his departure to the London Centre for Nanotechnology, UK.

I am grateful to Prof. Sigurd Wagner from Princeton University who accepted to serve as external to this thesis, and Prof. Ghassan Jabbour, Arizona State University, for interactions and stimulating discussions. I am also grateful to members of my PhD committee, Dr. Gareth Ingram, Prof. Vassili Karanassios, Prof. Andrei Sazonov, and Prof. Sherman Shen, for reading my thesis and providing invaluable comments.

Many thanks go to my colleagues and friends who helped me during my research. Special thanks goes to Dr. Isaac Chan who taught me how to fabricate my first vertical TFT, Dr. Denis Stryakhilev who always had time for numerous discussions, Mr. Saeed Fathololoumi, Dr. Moammad Esmaeili-Rad, Dr. Reze Chaji, Dr. Majid Gharghi, Dr. Flora Li, and Dr. Kai Wang. I am indebted to my wonderful friends Bahareh Sadeghimakki and Dr. Mojgan Daneshmand, who gave me hope and made me smile, even on the difficult days of my research, and, lastly, Mr. Richard Barber and Mr. Robert Mullins for keeping the clean room functional during my endless research. Special thanks go to the staff of the Department of Electrical and Computer Engineering at the University of Waterloo, in particular Ms. Wendy Boles, for being such a helpful and supportive person.

I have the utmost gratitude for my Dad and Mom for their endless guidance, encouragement, love, and patience. They taught me how to start with A, B, C and end up with a Ph.D. I would like to express my appreciation to my parents-in-law for all the support and encouragements during my PhD study. I must also thank my close family, Parisa, Mehdi, Amir, Sepideh, and Armin for always being there for me when I needed them.

Finally, I am forever grateful to my friend, my love, and my husband, Arash, who stood behind me during this journey. He taught me the basics of electronics and supported me at each step of my research. Certainly, this work would have been far from completion without him.

## **Table of Contents**

| List | of Table                 | es                                                  | viii          |

|------|--------------------------|-----------------------------------------------------|---------------|

| List | of Figur                 | res                                                 | ix            |

| Cha  | apter 1                  | Introduction                                        | 1             |

| 1.1  | Activ                    | ve Matrix Pixelated Arrays                          | 2             |

| 1.2  | Verti                    | ical Thin Film Transistors (VTFTs)                  | 6             |

| 1.3  | Objectives of the Thesis |                                                     |               |

| 1.4  | Thesi                    | is Organization                                     | 8             |

| 1.5  | References               |                                                     |               |

| Cha  | apter 2                  | Thin Film Transistors and Integration Con           | siderations12 |

| 2.1  | Later                    | ral TFTs                                            | 13            |

| 2.2  | Moti                     | vation for VTFTs                                    |               |

| 2.3  | Early                    | Works on VTFTs                                      | 19            |

| 2.4  | Devi                     | ce Fabrication                                      | 21            |

|      | 2.4.1                    | Deposition Techniques                               | 24            |

|      | 2.4.2                    | Etching Techniques                                  | 27            |

|      | 2.4                      | 2.1 Anisotropic Dry Etching                         | 29            |

|      | 2.4                      | -2.2 Masking Materials                              | 34            |

|      | 2.4.3                    | Thin Film Step Coverage                             | 36            |

| 2.5  | Prelin                   | minary Results                                      | 39            |

| 2.6  | Short                    | Short Channel Effects                               |               |

|      | 2.6.1                    | Back Gate Effect (BGE)                              | 43            |

|      | 2.6.2                    | Space Charge Limited Current (SCLC)                 | 43            |

|      | 2.6.3                    | Drain Induced Barrier Lowering (DIBL)               | 44            |

| 2.7  | Sumi                     | mary                                                | 45            |

| 2.8  | Refe                     | rences                                              | 47            |

| Ch   | anter 3                  | Silicon Nitride (SiN <sub>x</sub> ) Gate Dielectric | 51            |

| 3.1 | Conv                     | Conventional SiN <sub>x</sub>                        |     |

|-----|--------------------------|------------------------------------------------------|-----|

| 3.2 | Thickness Dependence     |                                                      | 54  |

|     | 3.2.1                    | Electrical Characteristics                           | 54  |

|     | 3.2.2                    | Physical Properties                                  | 56  |

| 3.3 | Verti                    | ical Topology                                        | 59  |

|     | 3.3.1                    | Electric Field Effects                               | 60  |

|     | 3.3.2                    | Material Inhomogeneity Effects                       | 62  |

| 3.4 | Dry 1                    | Etching Effects                                      | 63  |

| 3.5 | Sum                      | mary                                                 | 66  |

| 3.6 | Refe                     | rences                                               | 68  |

| Cha | apter 4                  | Thinning the SiN <sub>x</sub> Gate Dielectric        | 70  |

| 4.1 | Depo                     | osition of Ultra-Thin SiN <sub>x</sub>               | 71  |

|     | 4.1.1                    | Electrical Characteristics                           | 71  |

|     | 4.1.2                    | Physical Properties                                  | 76  |

|     | 4.1.3                    | Chemical Composition                                 | 78  |

|     | 4.1.4                    | Influence of Plasma Power Density                    | 81  |

|     | 4.1.5                    | Impact of N <sub>2</sub> Flow Ratio                  | 83  |

| 4.2 | Depo                     | osition with H <sub>2</sub> -Diluted Precursor Gases | 85  |

|     | 4.2.1                    | Electrical Characteristics                           | 86  |

|     | 4.2.2                    | Physical Properties                                  | 87  |

|     | 4.2.3                    | Chemical Composition                                 | 89  |

| 4.3 | Sum                      | mary                                                 | 91  |

| 4.4 | Refe                     | rences                                               | 93  |

| Cha | apter 5                  | VTFTs with Ultra-Thin Gate Dielectric                | 95  |

| 5.1 | Effec                    | ct of Gate Dielectric Scaling on a-Si:H VTFT         | 96  |

| 5.2 | Transport Mechanisms 10' |                                                      |     |

| 5.3 | OFF                      | Current and Subthreshold Slope                       | 108 |

| 5.4 | Nano                     | ocrystalline Silicon (nc-Si) VTFTs                   | 111 |

| 5.5 | Sum                      | mary                                                 | 121 |

| 5.6 | References                                 |     |

|-----|--------------------------------------------|-----|

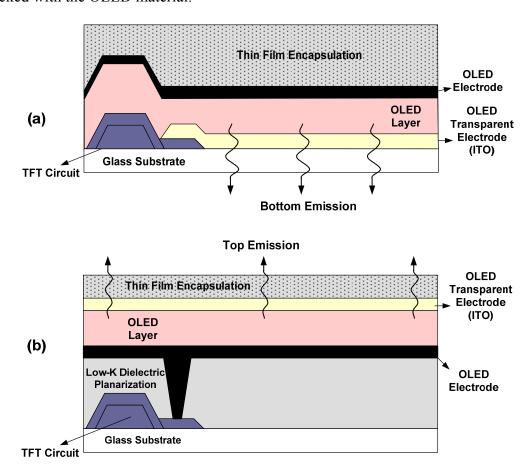

| Cha | apter 6 VTFT AMOLED Displays               | 126 |

| 6.1 | Organic Light Emitting Diode (OLED)        | 127 |

| 6.2 | 2-TFT AMOLED Driver Circuits               |     |

| 6.3 | VTFT for AMOLED                            | 129 |

| 6.4 | 2.2-inch AMOLED Display with 2-VTFT Driver | 130 |

|     | 6.4.1 Pixel Architecture                   | 130 |

|     | 6.4.2 Aperture Ratio                       |     |

| 6.5 | Display Fabrication                        | 133 |

| 6.6 | Summary                                    |     |

| 6.7 | References                                 |     |

| Cha | apter 7 Conclusions and Future Work        | 139 |

## **List of Tables**

| Table 2.1: Summary of the VTFT electrical and physical characteristics from literature | 21  |

|----------------------------------------------------------------------------------------|-----|

| Table 2.2: Summary of the deposition conditions for a-Si:H VTFT fabrication            | 25  |

| Table 2.3: Summary of the etching conditions in VTFT fabrication.                      | 28  |

|                                                                                        |     |

| Table 5.1: Summary of the 0.5 μm channel length a-Si:H VTFT performance                |     |

| parameters with different gate dielectric thicknesses                                  | 106 |

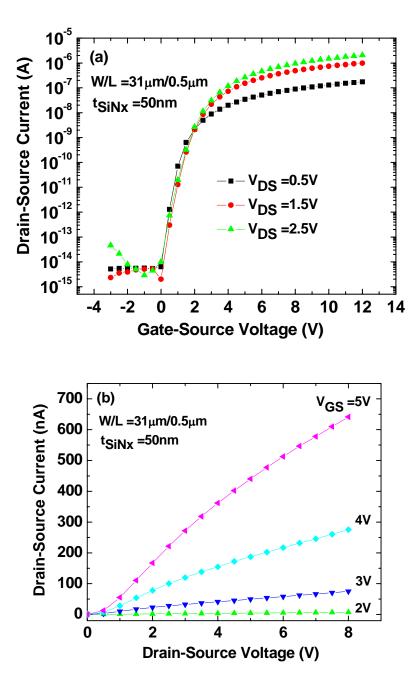

| Table 5.2: Extracted performance parameters of the 0.5 μm channel length nc-Si VTFT    |     |

| with 50nm new SiN <sub>x</sub> as the gate dielectric                                  | 117 |

## **List of Figures**

| Figure 1.1: (a) Samsung's 82-inch LCD TV [9] (b) flat-panel medical imager [10] (c)                                          |

|------------------------------------------------------------------------------------------------------------------------------|

| Sony's 11-inch AMOLED display [11]                                                                                           |

| Figure 1.2: Schematic of active matrix array.                                                                                |

| Figure 1.3: Basic circuit pixel for (a) AMLCD (b) AMOLED display                                                             |

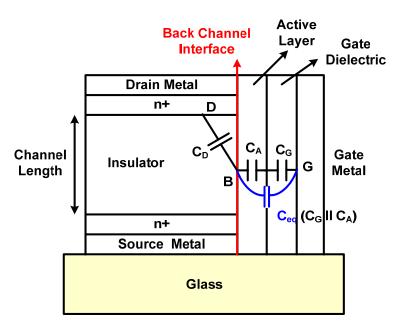

| Figure 1.4: Schematic cross section of the vertical TFT structure                                                            |

|                                                                                                                              |

| Figure 2.1: Fabrication sequence of an inverted staggered TFT (adapted from [7],                                             |

| [8])                                                                                                                         |

| Figure 2.2: (a) Transfer and (b) output characteristics of a lateral TFT (adapted from                                       |

| [11])                                                                                                                        |

| Figure 2.3: Schematic cross section of the (a) lateral (b) vertical TFT                                                      |

| Figure 2.4: Different topologies of the VTFT structure (adapted from [22] - [26])                                            |

| Figure 2.5: Fabrication sequence of the VTFT process (not to scale)                                                          |

| Figure 2.6: (a) MVS cluster PECVD equipment and (b) the chamber configuration                                                |

| Figure 2.7: (a) Isotropic and (b) anisotropic etching pattern                                                                |

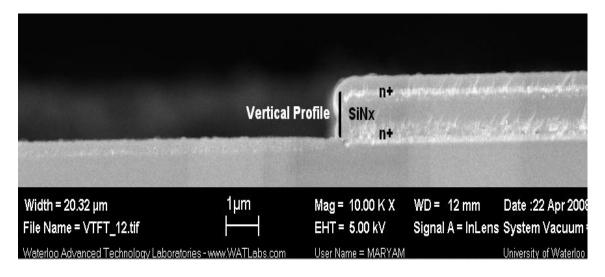

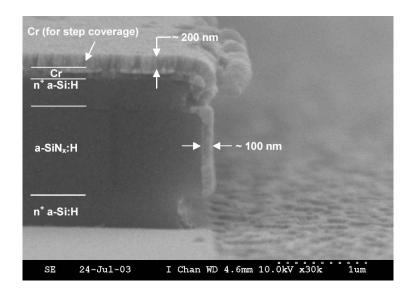

| Figure 2.8: (a) Cross-sectional SEM image of the fabricated VTFT and (b) schematic                                           |

| cross-section of the device showing the parasitic resistance near the drain contact                                          |

| (adapted from [27])                                                                                                          |

| Figure 2.9: n+/SiN <sub>x</sub> /n+ trilayer profile obtained after RIE etching by using CF <sub>4</sub> /H <sub>2</sub> gas |

| mixture and polymer removal process.                                                                                         |

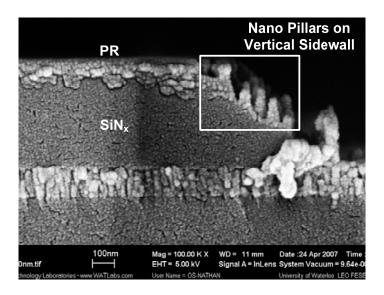

| Figure 2.10: SEM image of the slanted sidewall and the generated nano-pillar on its                                          |

| surface in the RIE etching of SiN <sub>x</sub> using a PR mask                                                               |

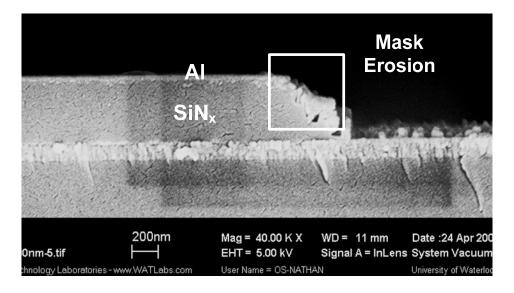

| Figure 2.11: SEM image of the slanted sidewall due to the mask erosion in RIE                                                |

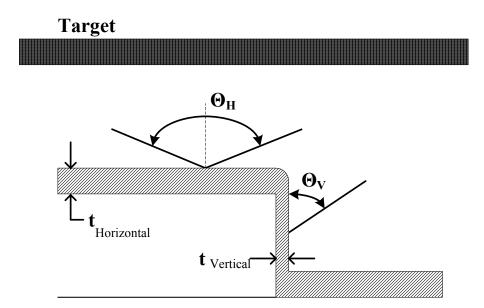

| Figure 2.12: Schematic illustrating the possible arriving angles for metal atom flux                                         |

| and the film coverage on a horizontal and a vertical surface                                                                 |

| Figure 2.13: Step coverage of sputter-deposited Cr metal film [27]                                                           |

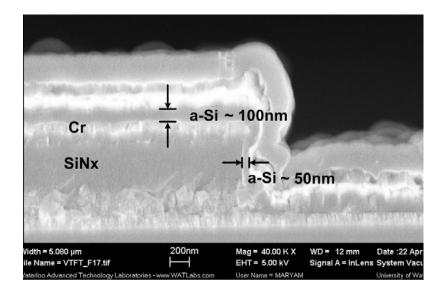

| Figure 2.14: Step coverage of the PECVD-deposited a-Si:H film                                                                |

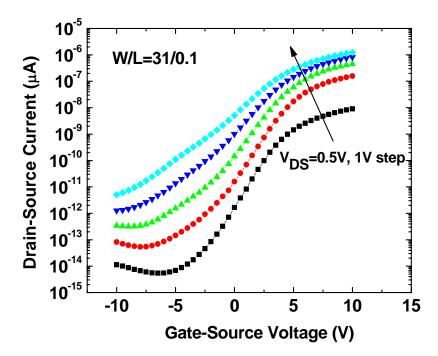

| Figure 2.15: Transfer characteristics of the a-Si:H VTFT with 0.1µm channel length                                           |

| at different drain voltages.                                                                                                 |

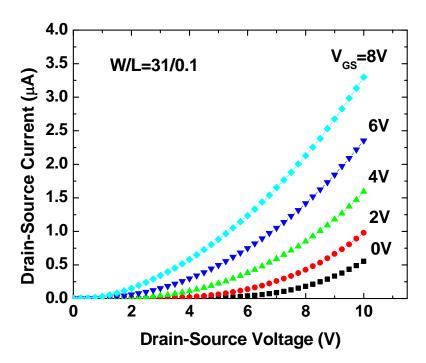

| Figure 2.16: $I_{DS}$ - $V_{DS}$ characteristics of the a-Si:H VTFT with 0.1 $\mu$ m channel length                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------|

| at different gate voltages                                                                                                                     |

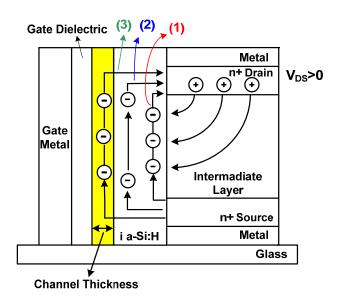

| Figure 2.17: Short channel effect in VTFTs (1) Back gate effect (2) Space charge                                                               |

| limited current and (3) Drain induced barrier lowering.                                                                                        |

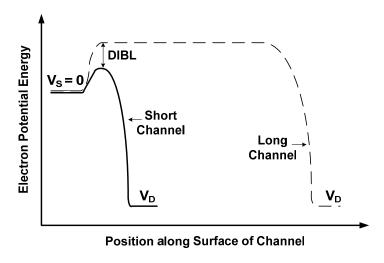

| Figure 2.18: DIBL in MOSFETs; potential distribution along the channel for a long                                                              |

| and short channel device (adapted from [44])                                                                                                   |

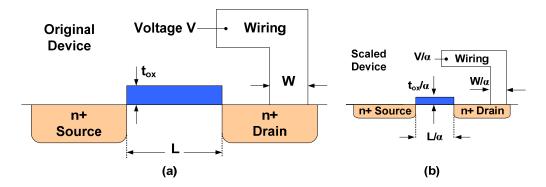

| Figure 2.19: Principle of scaling for MOS transistors and integrated circuits (adapted                                                         |

| from [47])                                                                                                                                     |

|                                                                                                                                                |

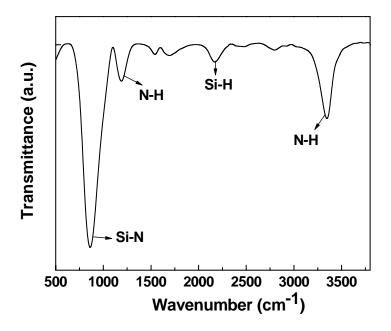

| Figure 3.1: FTIR spectra of the conventional silicon nitride.                                                                                  |

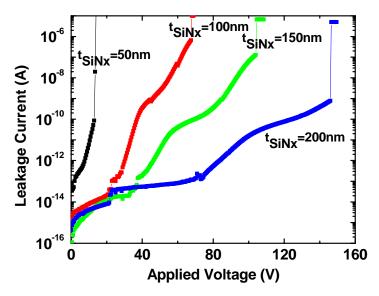

| Figure 3.2: Current-voltage characteristics of the SiN <sub>x</sub> films with different                                                       |

| thicknesses                                                                                                                                    |

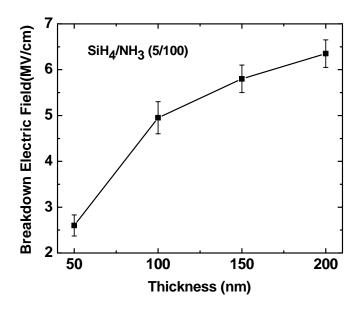

| Figure 3.3: Breakdown electric field as a function of silicon nitride thickness                                                                |

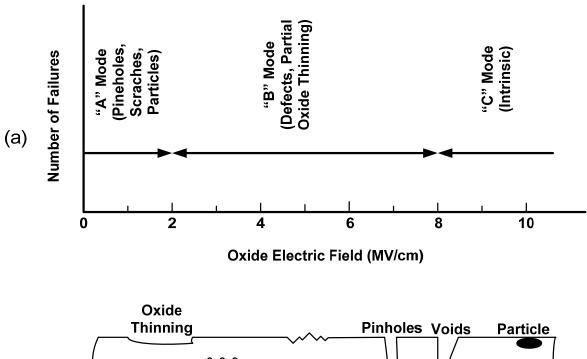

| Figure 3.4: (a) Oxide breakdown mode and (b) Oxide defects (adapted from [10])                                                                 |

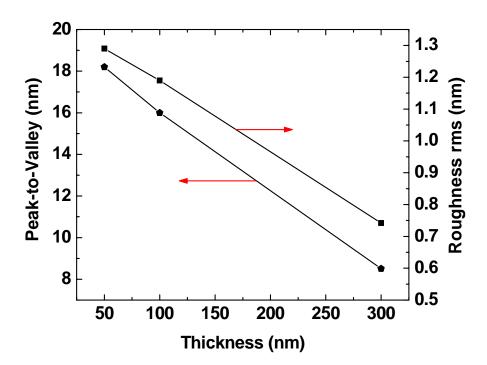

| Figure 3.5: Surface morphology of the SiN <sub>x</sub> layers as a function of film thickness                                                  |

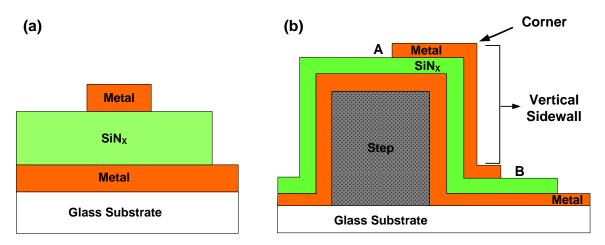

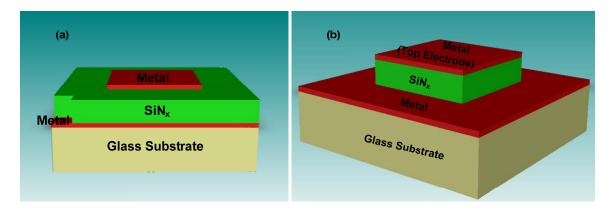

| Figure 3.6: Cross-section schematic of the (a) planar and (b) vertical structures used                                                         |

| in this study (not to scale)                                                                                                                   |

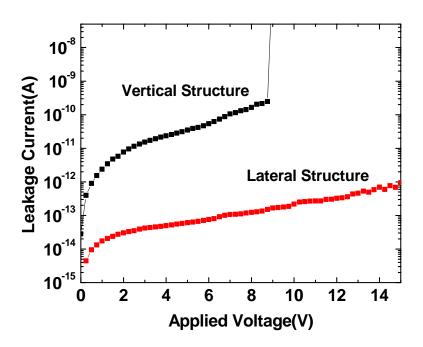

| Figure 3.7: Current-voltage characteristics of vertical and lateral structures                                                                 |

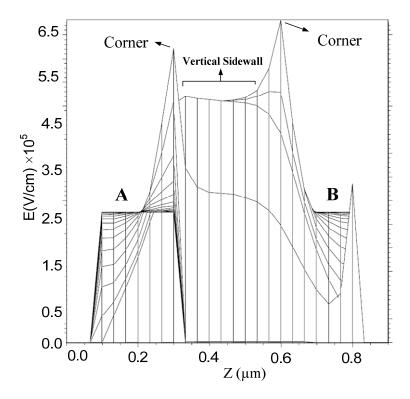

| Figure 3.8: Simulated electric field distribution of the vertical structure; the horizontal                                                    |

| axis corresponds to the distance from A to B shown in Figure 3.6 (b)                                                                           |

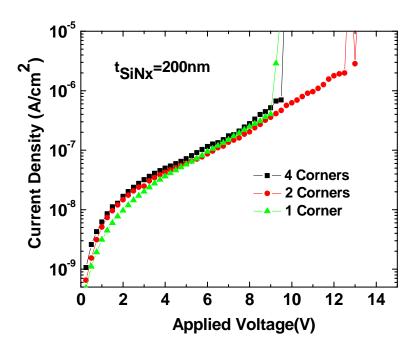

| Figure 3.9: Current density of the vertical structures with different numbers of                                                               |

| corners                                                                                                                                        |

| Figure 3.10: Schematic illustration of silicon nitride with (a) continues and (b)                                                              |

| patterned structures                                                                                                                           |

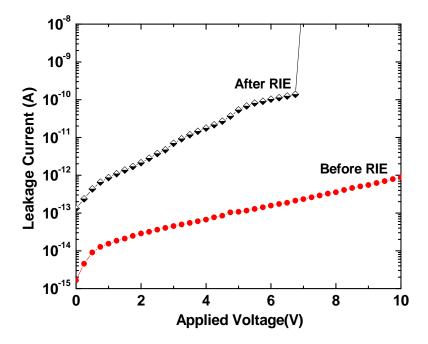

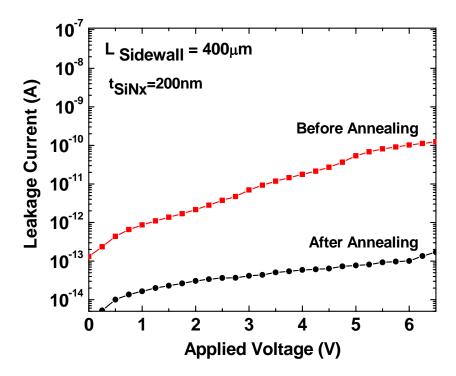

| Figure 3.11: Current-voltage characteristics of the continues and RIE-patterned SiN <sub>x</sub>                                               |

| Figure 3.12: Annealing effect on the leakage current after RIE patterning                                                                      |

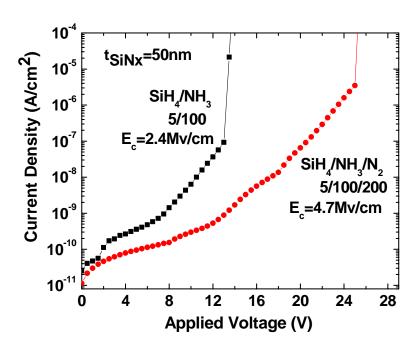

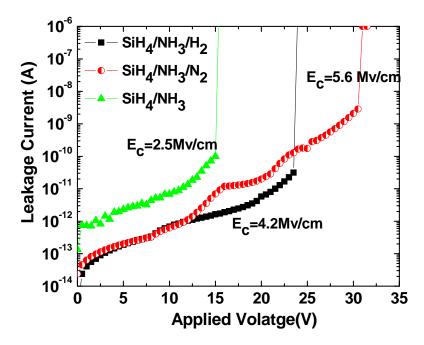

| Figure 4.1: Current-voltage characteristics and the breakdown field of a 50nm $SiN_x$                                                          |

| deposited with conventional (SiH <sub>4</sub> /NH <sub>3</sub> ) and a modified (SiH <sub>4</sub> /NH <sub>3</sub> /N <sub>2</sub> ) processes |

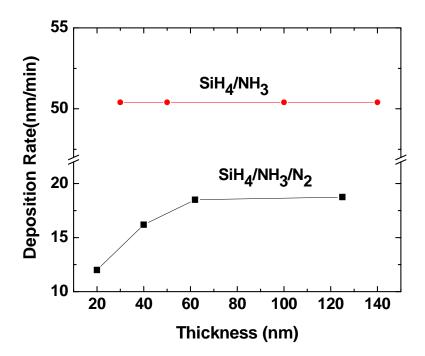

| Figure 4.2: Deposition rate as a function of the thickness for the silicon nitride films                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------|

| deposited with the conventional $(SiH_4/NH_3)$ and modified $(SiH_4/NH_3/N_2)$                                                              |

| processes                                                                                                                                   |

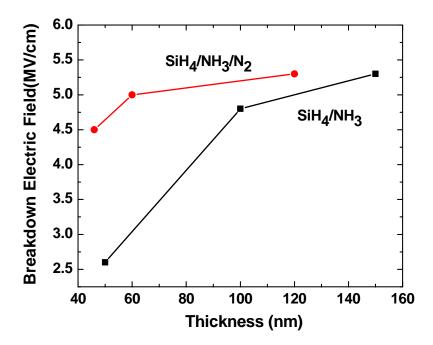

| Figure 4.3: The breakdown field as a function of thickness for the silicon nitride films                                                    |

| deposited with the conventional $(SiH_4/NH_3)$ and modified $(SiH_4/NH_3/N_2)$                                                              |

| processes                                                                                                                                   |

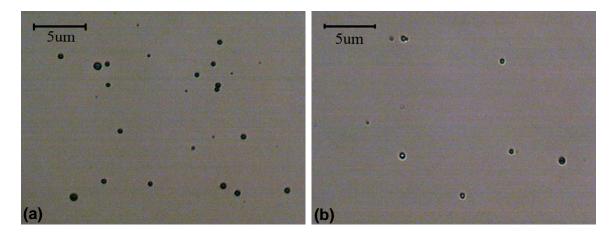

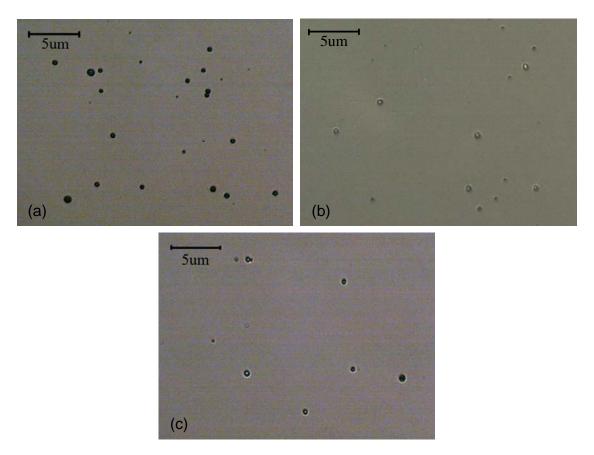

| Figure 4.4: Optical images illustrating the aerial pinhole density of the SiN <sub>x</sub> layers                                           |

| deposited by (a) SiH <sub>4</sub> /NH <sub>3</sub> and (b) SiH <sub>4</sub> /NH <sub>3</sub> /N <sub>2</sub> precursor gasses, respectively |

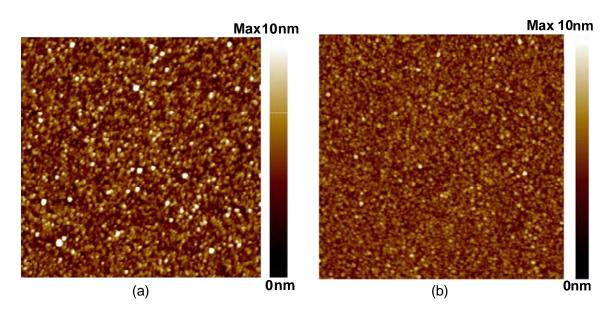

| Figure 4.5: AFM images of the surface morphology for the SiN <sub>x</sub> films deposited by                                                |

| (a) SiH <sub>4</sub> /NH <sub>3</sub> and (b) SiH <sub>4</sub> /NH <sub>3</sub> /N <sub>2</sub> gas mixtures                                |

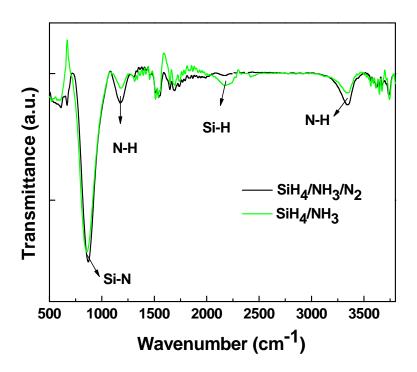

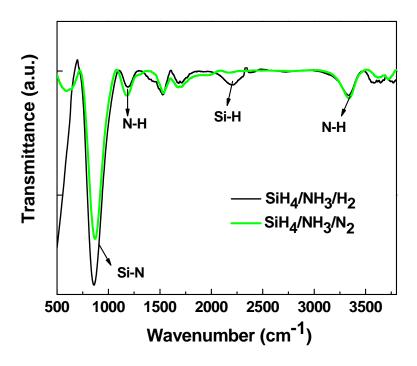

| Figure 4.6: FTIR spectra of the silicon nitride deposited with and without nitrogen                                                         |

| dilution of SiH <sub>4</sub> and NH <sub>3</sub> gasses.                                                                                    |

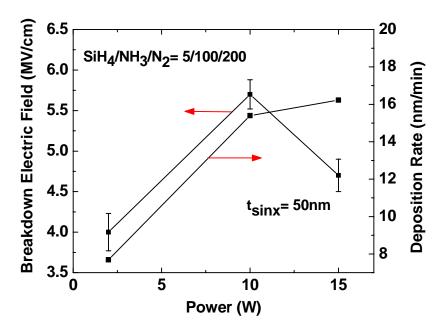

| Figure 4.7: Breakdown field and the deposition rate of the 50nm-thick silicon nitride                                                       |

| films as a function of the deposition power.                                                                                                |

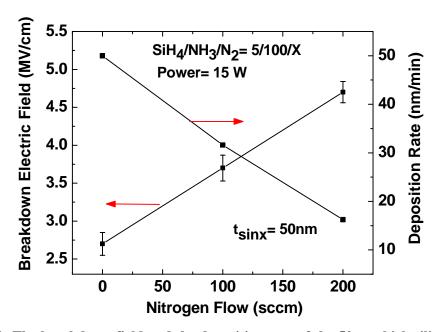

| Figure 4.8: The breakdown field and the deposition rate of the 50nm-thick silicon                                                           |

| nitride layer as a function of nitrogen flow.                                                                                               |

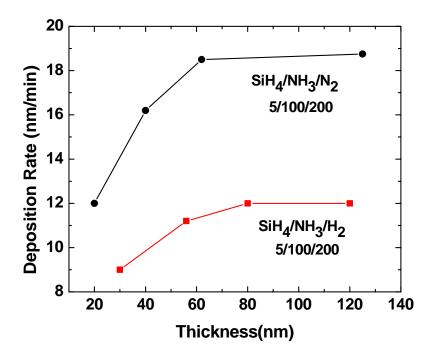

| Figure 4.9: Deposition rate as a function of thickness for the silicon nitride films                                                        |

| deposited with SiH <sub>4</sub> /NH <sub>3</sub> /H <sub>2</sub> and SiH <sub>4</sub> /NH <sub>3</sub> /N <sub>2</sub> gas mixtures.        |

| Figure 4.10: <i>I-V</i> characteristics of the 50nm silicon nitride deposited with different                                                |

| gas mixtures.                                                                                                                               |

| Figure 4.11: Optical images of the 50nm nitride layers deposited with (a) SiH <sub>4</sub> /NH <sub>3</sub>                                 |

| (5/100), (b) $SiH_4/NH_3/H_2$ (5/100/200), and (c) $SiH_4/NH_3/N_2$ (5/100/200) gases,                                                      |

| illustrating the populations of the pinholes in the film                                                                                    |

| Figure 4.12: FTIR spectra of the silicon nitride films deposited by SiH4/NH3/H2 and                                                         |

| SiH <sub>4</sub> /NH <sub>3</sub> /N <sub>2</sub> gas mixtures.                                                                             |

|                                                                                                                                             |

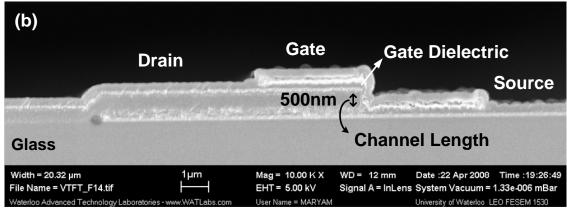

| Figure 5.1: (a) Cross-section schematic and (b) SEM image of the vertical thin film                                                         |

| transistor (VTFT)                                                                                                                           |

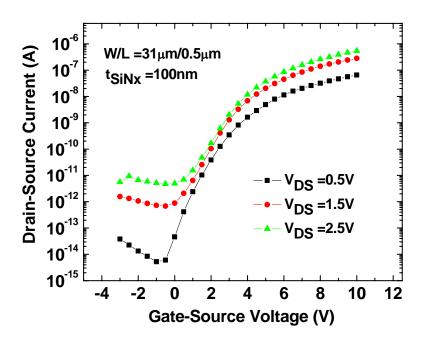

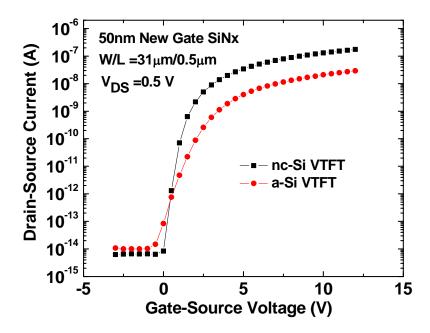

| Figure 5.2: $I_{DS}$ - $V_{GS}$ characteristics of the 0.5 $\mu$ m channel length VTFT employing                                            |

| 100nm conventional gate silicon nitride                                                                                                     |

| Figure 5.3: Output characteristics of the 0.5 μm channel length VTFT employin             |

|-------------------------------------------------------------------------------------------|

| 100nm conventional gate silicon nitride.                                                  |

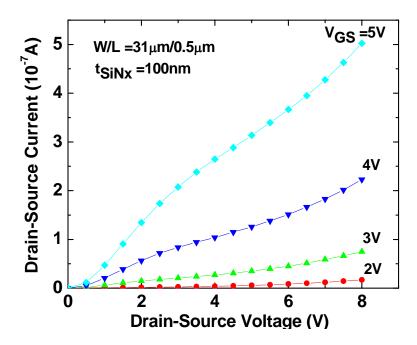

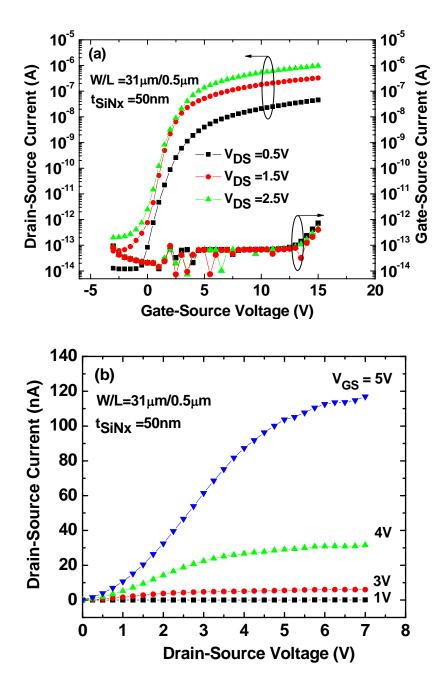

| Figure 5.4: (a) Output current and the gate leakage as a function of the gate voltage a   |

| different drain biases and (b) the output characteristics for a $0.5\mu m$ channel length |

| VTFT with 50nm silicon nitride as the gate dielectric.                                    |

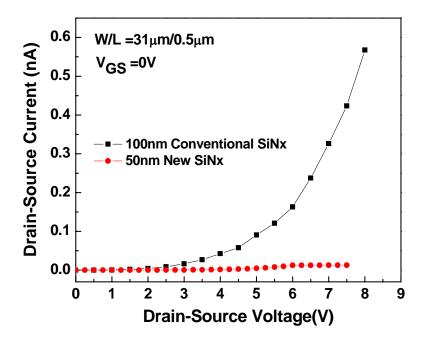

| Figure 5.5: $I_{DS}$ - $V_{DS}$ characteristics at $V_{GS} = 0$ V for the VTFT with 100nr |

| conventional and 50nm new SiN <sub>x</sub> gate dielectrics.                              |

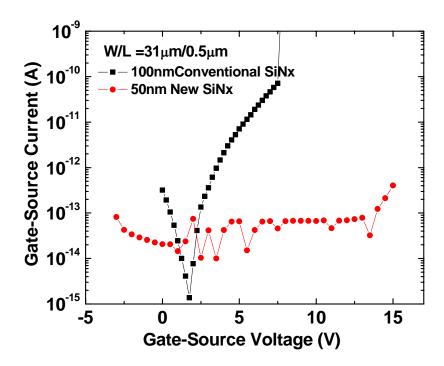

| Figure 5.6: Gate leakage current as a function of the gate voltage for the VTFTs wit      |

| 100nm conventional and 50nm new silicon nitride insulators                                |

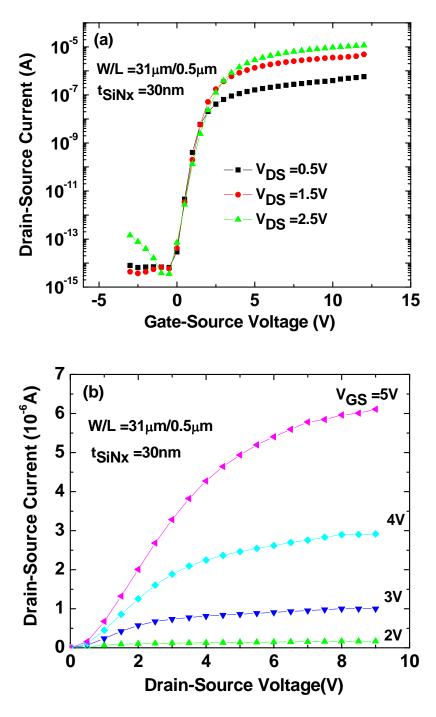

| Figure 5.7 (a) Transfer and (b) output characteristics of the 0.5 $\mu m$ channel lengt   |

| VTFT with 30 nm silicon nitride as the gate dielectric                                    |

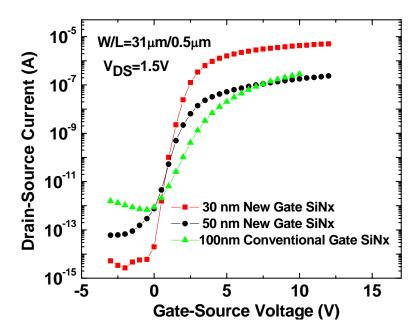

| Figure 5.8: Transfer characteristics of the VTFTs with gate dielectric thicknesses of     |

| 100nm, 50nm, and 30nm                                                                     |

| Figure 5.9 Schematic cross section of the VTFT structure illustrating the capacitive      |

| circuit elements                                                                          |

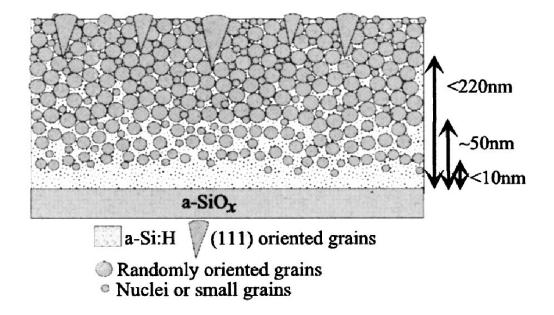

| Figure 5.10: Schematic cross-section of nc-Si film illustrating the evolution of          |

| material microstructure when the film thickness grows (adapted form [17])                 |

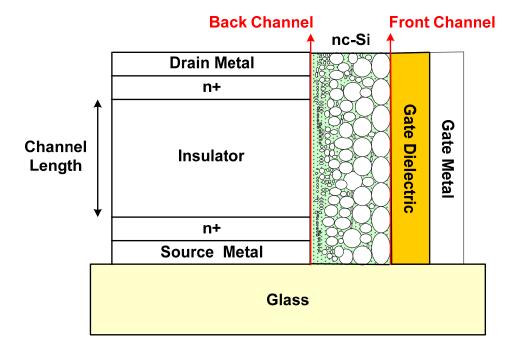

| Figure 5.11: Cross section schematic of the VTFT structure with nc-Si as the              |

| transistor active layer                                                                   |

| Figure 5.12: (a) Transfer and (b) output characteristics of the nc-Si VTFT with 50nr      |

| SiN <sub>x</sub> gate dielectric                                                          |

| Figure 5.13: Transfer characteristics of the a-Si:H and nc-Si VTFTs with 50nm new         |

| $SiN_x$ as the gate dielectric.                                                           |

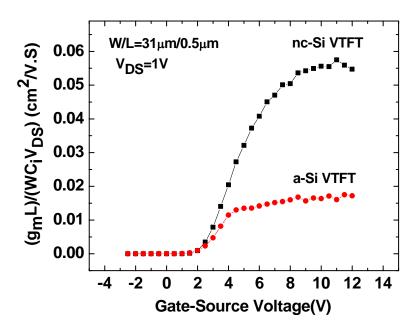

| Figure 5.14: Extracted field effect mobilities of the fabricated a-Si:H and nc-Si         |

| VTFTs; the $SiN_x$ gate dielectric thickness is 50nm for both devices                     |

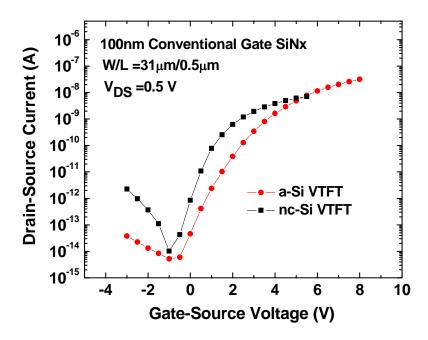

| Figure 5.15: Transfer characteristics of a-Si:H and nc-Si VTFTs with 100nr                |

|                                                                                           |

| conventional $SiN_x$ as the gate dielectric; no performance improvement is observed for   |

| Figure 6.2 Two different driver circuitry employed in a 2.2-inch QVGA AMOLED              |     |

|-------------------------------------------------------------------------------------------|-----|

| array                                                                                     | 133 |

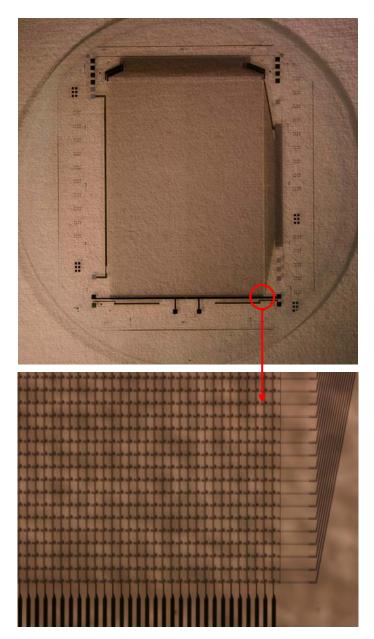

| Figure 6.3: Top view images of a fabricated VTFT array before the deposition of           |     |

| OLED                                                                                      | 134 |

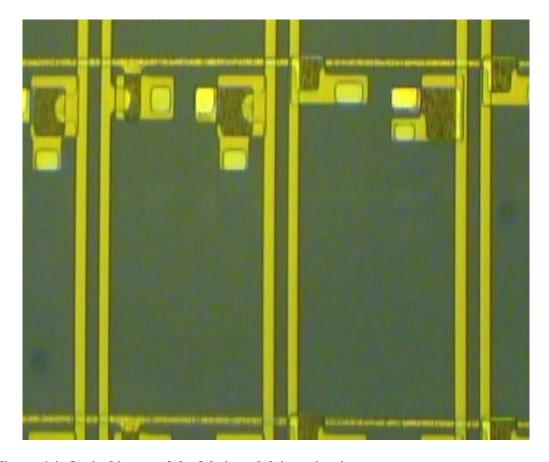

| Figure 6.4: Optical image of the fabricated driver circuits.                              | 135 |

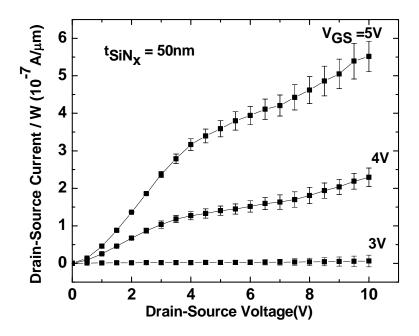

| Figure 6.5: Average normalized output characteristics of several devices across the       |     |

| fabricated AMOLED panel at different $V_{GS}$ biases. Error bars at each point illustrate |     |

| the maximum deviation                                                                     | 136 |

## Chapter 1

## Introduction

The enormous growth of microelectronics has greatly affected the modern-day lifestyle due to the availability of sophisticated hardware ranging from health and entertainment to communication and space products. In particular, the advancements in microelectronics have led to production of large area electronic circuits owing to the low-cost deposition of silicon-based thin films over large surfaces [1]. At present, the applications of large area electronics include flat panel displays, thin film solar cells, and x-ray imagers, which are collectively generating an ever-growing multi-billion dollar business [2].

The basic building block of large area electronics is the thin film transistor (TFT), which is employed as an active and/or switching element. To enhance the performance in terms of speed, resolution, or sensitivity, the dimensions of the TFT must be scaled down in a manner similar to the trend followed in the very large-scale integration (VLSI) industry [3]. However, critical issues related to the small geometrical dimensions of the transistor

channel, widely known as short channel effects, emerge thus limiting the performance and reliability of the TFT [4].

To overcome the problems, which deteriorate the functionality of the TFT especially when the channel length approaches the nano-scale regime, a proper choice for TFT configuration, structure, and topology are mandatory. Moreover, an in-depth material study and optimization of the various layers employed in the fabrication of the TFT is essential. This thesis specifically addresses these issues and presents device fabrication and material development for non-conventional TFT architectures suitable for high performance and high-resolution large area electronics.

### 1.1 Active Matrix Pixelated Arrays

The backplane electronics for any active matrix display or imager consists of an array of pixels and associated programming lines running in rows and columns [5]. The basic unit in each array is a pixel, and each pixel consists of a sensor or light-emitting device and one or more TFTs. Therefore, as the demand on the performance of the system increases, requirements on the TFT characteristics become more challenging to satisfy.

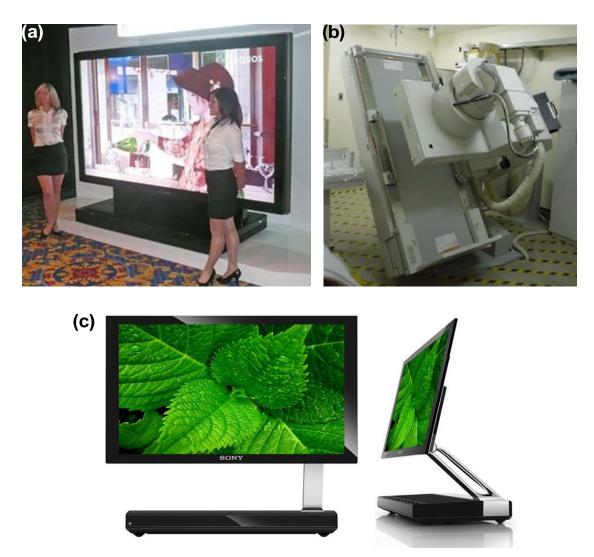

Among the different display technologies, the active matrix liquid crystal displays (AMLCD) is the most mature [6]. Figure 1.1 (a) illustrates an 82-inch AMLCD TV produced by Samsung Company. Another rapidly growing technology is the active matrix organic light emitting diode (AMOLED) display. OLED displays have gained significant attention because of their potentially faster response time, larger viewing angles (>150°), higher contrast, lower power consumption, and lighter weight compared to the AMLCD [7], [8]. Figure 1.1(c) shows the images of Sony's recently marketed 11-

inch AMOLED display. Other important application of active matrix arrays is in imaging particularly for modalities such as radiography and fluoroscopy (Figure 1.1(b)). High image quality, large area imaging capability, low storage cost, and computerized handling/storage of sensory information constitute the ever-growing demands, pushing the imaging technology to new limits.

Figure 1.1: (a) Samsung's 82-inch LCD TV [9], (b) flat-panel medical imager [10], and (c) Sony's 11-inch AMOLED display [11].

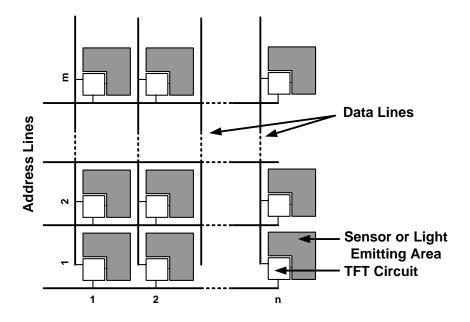

Despite the differences in the functionality of TFTs in the pixel, the architecture of all active matrix arrays is similar as illustrated in Figure 1.2. The address and data lines run

horizontally and vertically between the pixels and connect each pixel to external circuitry. Typically, the vertical lines provide the data and bias connections, and the horizontal address lines are connected to the gates of TFTs.

Figure 1.2: Schematic of active matrix array.

Depending on the function of the TFT in the circuit, the requirements on the performance specifications of the device vary. This, in turn, dictates the complexity and the cost of the fabrication process. The role of TFTs displays can be divided into two categories. For applications such as AMLCDs, the TFT acts as a switch. In AMOLED displays, the TFTs are used as linear integrated circuit elements, i.e. as switches, pass transistors, and drivers. As an example, the equivalent circuits for possible pixel architectures of an active matrix liquid crystal display (AMLCD) and an active matrix organic light emitting diode (AMOLED) display are depicted in Figure 1.3.

Figure 1.3: Basic circuit pixel for (a) AMLCD and (b) AMOLED display.

The history of the present TFT begins with the work of P. K. Weimer at RCA laboratories in 1962 [12]. From then on, TFTs have evolved in materials and structures to match different application requirements and this development is still going on.

Hydrogenated amorphous silicon (a-Si:H), nanocrystalline (nc)-, microcrystalline (μc)-, and poly-crystalline (poly)- Si are used as an active layer in the TFT depending on the application. Among the different family of materials, a-Si:H TFTs are popular for the large area electronics such as AMLCDs, AMOLED displays, and active matrix image sensors employed in document scanners and x-ray imagers. a-Si:H TFTs gain their reputation mainly due to the ability of low-cost high uniformity deposition over large areas (more than 1 meter in linear dimension) at low temperature (<300°C), which allows fabrication on a wide range of substrates. However, the most serious issue related to the present a-Si:H TFT is the operating speed due to low field effect mobility of electrons in the material (0.1-1 cm²/V-s) [13].

One feasible solution to increase the operation speed of the a-Si:H TFT is to reduce its channel length, since the switching time is proportional to the channel length. Short channel TFTs have a shorter transit time for carriers to cross the channel. However, in

conventional TFTs, shortening the channel length is limited by fabrication issues associated with lithography and etching. Thus, for high-resolution matrix addressing and high-density TFT integration applications, alternative TFT configurations have to be considered where shrinking of TFTs dimensions are not limited by the above issues.

The focus of this thesis is on reducing the dimensions of TFTs for active matrix addressed pixelated arrays in order to advance the performance of flat panel applications. The remaining part of this chapter includes a brief introduction of vertical thin film transistors and the objectives of the conducted research.

#### 1.2 Vertical Thin Film Transistors (VTFTs)

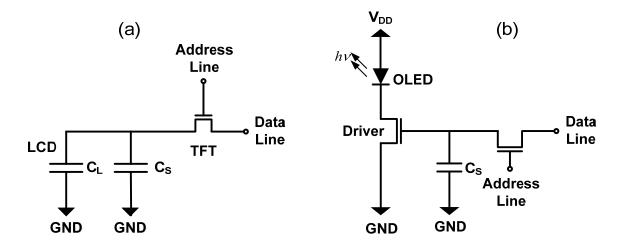

Figure 1.4 shows the simplified cross section of the vertical thin film transistors structure. The active channel in this device is deposited vertically and the channel length in the VTFT is defined by the intermediate  $SiN_x$  layer thickness between the drain and source islands. Therefore, the channel length can be accurately controlled and reduced down to nanometer-range by scaling the thickness of the insulator layer. Moreover, the area occupied by the TFT is not a function of the aspect ratio (W/L) [14]. Since the channel length (L) can be  $1\mu m$  or less, the channel width W can be reduced accordingly to maintain the same W/L ratio as in the lateral TFT, resulting in a further significant reduction in TFT size.

Figure 1.4: Schematic cross section of the vertical TFT structure.

Using small area transistors, the fill factor (defined as the ratio of light sensing area to the total pixel area) or aperture ratio (defined as the ratio of light emitting display area to the total pixel area), which determines the performance attributes in imagers or displays (such as dynamic range, brightness, contrast ratio, etc.), can be significantly enhanced. The VTFT offers an excellent platform due to its inherent structural characteristics of short channel length and small device area, enabling a new generation of low-cost, high-speed, and high-resolution applications. However, while the device holds great promise, there are severe issues related to its performance and reliability because of the scaled-down TFTs geometries. As the channel length shrinks, undesirable effects (so-called short channel effects), arise undermining the functionality of the TFTs. These adversities and the solution to alleviate their effects will be addressed in this thesis in detail.

## 1.3 Objectives of the Thesis

This doctoral study focuses on the fabrication of the vertical thin film transistors and the challenges related to the functionality and reliability of short channel lengths and small areas, in an attempt to make feasible high performance, high-resolution large area arrays.

The biggest challenge lies in dealing with short channel effects, which induce high drain leakage current, low on/off current ratio, and absence of the saturation behavior at high drain voltages. To overcome these adversities, which become prevail as the channel length approaches the nano-scale regime, reduction of the gate dielectric thickness is mandatory. However, the main problem that arises is the high gate leakage current and, more importantly, early dielectric breakdown, which undermines device reliability [15]. Hence an important goal of this thesis was to develop of an ultra thin silicon nitride insulator layer (SiN<sub>x</sub>) as the gate dielectric. We report here for the first time, SiN<sub>x</sub> with thicknesses as low as 30 nm, which has been employed as the VTFT gate dielectric providing the fabricated transistors with good performance and reliability.

## 1.4 Thesis Organization

A brief introduction to large area electronics and its applications is presented in Chapter 1. Here, different applications of TFTs serving as the building blocks of active matrix arrays are addressed. Lastly, the motivation for research on VTFTs and their potentially superior performance over conventional TFTs is discussed.

Chapter 2 reports the basics of lateral and vertical TFTs with a brief literature review. This chapter covers the detailed fabrication process of VTFTs and related issues. The challenges in formation of the vertical structure and associated process and solutions, in particular, deposition and etching techniques/conditions are discussed, along with initial electrical characteristics of the devices. Here, the underlying reasons for poor VTFT performance, particularly short channel effects, are reviewed.

Chapter 3 describes the impact of film thickness on leakage current and electrical breakdown of plasma enhanced chemical vapor deposited (PECVD) silicon nitride dielectrics. We consider  $SiN_x$  films of various thicknesses, in the range 50 to 300 nm, deposited on both planar and vertical sidewalls in resemblance to the structural topology of the vertical thin film transistor (VTFT). Both physical and electrical characteristics of the  $SiN_x$  with different thicknesses have been examined from the standpoint of performance characteristics and device reliability.

Chapter 5 focuses on development of sub-50 nm silicon nitride layers suitable for short channel TFTs. A systematic study on the relation between the material properties and the process conditions has been conducted to develop functional ultra-thin nitrides. The electrical, physical, and chemical properties of this nitride characterized using different techniques are reviewed in chapter 5.

Chapter 6 reports results of a-Si:H VTFTs fabricated using the ultra-thin  $SiN_x$  gate dielectric. VTFTs with different gate dielectric thickness are presented. The effect of the thin gate nitride on OFF current, ON current, and sub-threshold slope has been studied and compared VTFTs with conventional  $SiN_x$  gate dielectric. Also discussed is the impact of substituting the a-Si:H active layer with nc-Si on VTFT characteristics.

Chapter 7 discusses the applications of VTFTs in large area electronics. As a proof of concept, a 2.2-inch AMOLD array has been fabricated using optimized VTFTs as the building block for a two-transistor pixel circuit.

Chapter 8 concludes the thesis and outlines future work.

#### 1.5 References

- [1] L.E Antonuk, J. Boudry, J. Yorkston, E. J. Morton, W. Huang, and R.A. Street, "Development of thin-film flat-panel arrays for diagnostic and radiotherapy imaging," *Proc. of SPIE*, vol.1651, pp. 94-105, 1992.

- [2] [Online accessed Feb. 2008] "PARC Large-Area Electronics" Available from: http://www.parc.com/research/projects/lae/default.html

- [3] S. D. Brotherton, C. Glasse, C. Glaister, P. Green, F. Rohlfing, and J. R. Ayres, "High-Speed, short-channel polycrystalline silicon thin-film transistor," *Appl. Phys. Lett.*, vol. 84, no. 2, pp. 293-295, 2004.

- [4] C. D. Kim and M. Matsumura, "Short-channel amorphous-silicon thin film transistors," *IEEE Trans. Elec. Dev.*, vol. 43, no. 12, pp. 2172-2176, 1996.

- [5] H. Kawamoto, "The history of liquid-crystal displays," *Proc. IEEE*, vol. 90, no. 4, pp. 460-500, 2002.

- [6] C. R. Kagan and P. Andry, *Thin Film Transistors*. Marcel Dekker, New York, NY, 2003, Chapter 5.

- [7] S. K. Heeks, J. H. Burroughes, C. Town, S. Cina, N. Baynes, N. Athanassopoulou, and J. C. Carter, "Light-emitting polymers for full-color display applications," *J. Soc. Inf. Disp.*, vol. 10, no. 2, pp. 139-143, 2002.

- [8] R. M. Dawson and M. G. Kane, "Pursuit of active matrix organic light emitting diode displays," *Dig. Tech. Papers SID Int. Symp.*, vol. 31, no. 1, pp. 372-375, 2001.

- [9] [Online accessed Apr. 2008], "Samsung's 82-inch LCD TV" Available from: http://www.engadget.com/2005/03/07/samsungs-82-inch-lcd-tv.

- [10] [Online accessed Jun. 2008], "Fluoroscopy Wikipedia" Available from: http://en.wikipedia.org/wiki/Fluoroscopy.

- [11] [Online accessed Jun. 2008], "Sony OLED TV" Available from: www.SonyStyle.ca.

- [12] P. K. Weimer, "The TFT- a new thin film transistors", *Proc. IEEE*, vol. 50, no. 6, pp. 1462-1469, 1962.

- [13] R. A. Street, *Hydrogenated Amorphous Silicon*. Cambridge University Press, Cambridge, 1991.

- [14] A. Nathan, P. Servati, K.S. Karim, D. Stryakhilev, and A. Sazonov, "Thin film transistor integration on glass and plastic substrates in amorphous silicon technology," *IEE Proc. Circuits, Devices and Syst.*, vol. 150, no. 4, pp. 329-338, 2003.

- [15] M. Moradi, D. Stryakhilev, I. Chan, A. Nathan, N. I. Cho, and H. G. Nam, "Reliability of silicon nitride gate dielectric in vertical thin film transistors," *Proc. Mater. Res. Soc. Symp.*, vol. 989, p. A08-05, 2007.

## Chapter 2

## Thin Film Transistors and Integration

### **Considerations**

It is necessary to have a basic understanding of the thin film transistors (TFTs) since these devices serve as the building block of imagers or display panels. This chapter provides the reader with a concise description of both lateral and vertical TFTs. Following the introduction of the amorphous silicon TFT structure and its electrical characteristics, the motivation for the application of the vertical thin film transistors (VTFTs) is outlined. Then a brief literature review of VTFT is presented.

In this chapter the detailed fabrication process of the VTFT and the related issues are discussed. The challenges through the formation of the vertical structure and the developed processes and solutions are addressed. The details of the processing conditions for the deposition and etching techniques are reported along with the initial device

characteristics of VTFT constructed in University of Waterloo. At the end, the short channel effects will be introduced to explain the poor electrical behavior of the devices.

#### 2.1 Lateral TFTs

Lateral hydrogenated amorphous silicon (a-Si:H) TFTs are the most popular active devices used in current large area electronics [1]. The a-Si:H TFT was first demonstrated in 1981 by Spear and LeComber's research group [2], [3]. The reproducible device characteristics and simple low-cost fabrication process renders a-Si:H TFT-based circuits very attractive for large area electronics [4].

Although a variety of configurations can be used for producing a-Si:H TFT's, the most popular structure is the inverted-staggered structure [3], [5]. Most researchers employ an inverted staggered structure due to its performance that is better than a top-gate structure where the gate insulator is deposited on the a-Si:H. On the contrary, in and inverted staggered structure, the a-Si:H film is deposited on the gate dielectric layer in a single vacuum-pump down process. This sequence of deposition is one of the best methods to achieve a high interface quality. Therefore, the field effect mobility of the inverted staggered devices is typically about 30% higher than that for the staggered type [6].

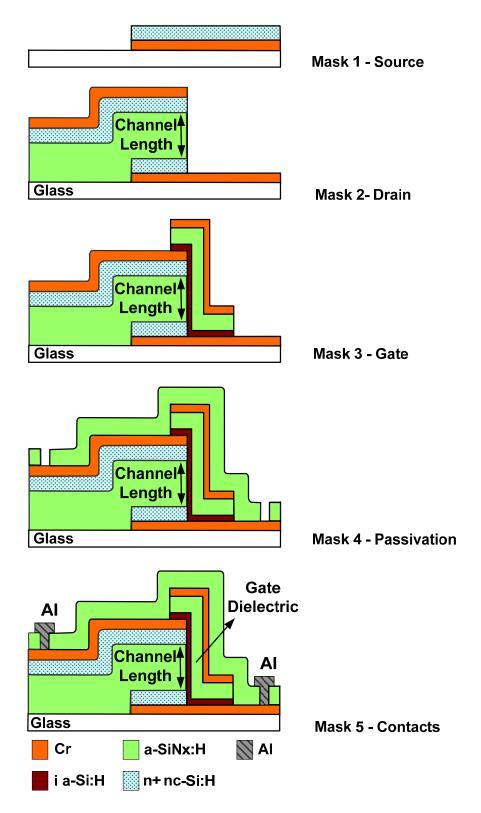

In amorphous silicon devices integrated circuit (a-SiDIC) laboratory at the University of Waterloo, the inverted staggered a-Si:H TFTs is fabricated using a five-mask process [7], [8]. As depicted in Figure 2.1, the fabrication process begins with the deposition of

100nm-Cr or Mo on the substrate to form the gate electrode of the device (Mask 1). The

next step is the deposition of silicon nitride (SiN<sub>x</sub>) as the gate insulator, a-Si:H as the

active channel, and a second SiN<sub>x</sub> film as the passivation layer in one vacuum-pump-

down cycle to minimize the density of defect states at the interfaces. Although other dielectric materials such as SiO<sub>2</sub> have been used, silicon nitride is by far the most recognized choice as the gate dielectric, giving a superior performance than that of other materials [9]. The three layers are deposited in a plasma enhanced chemical vapor deposition (PECVD) system with thicknesses of 250nm, 50nm, and 250nm for SiN<sub>x</sub>, a-Si:H and SiN<sub>x</sub> layers, respectively. Then, the passivation SiN<sub>x</sub> is patterned using mask 2 to define the source and drain regions. Next, a 300nm heavily-doped nano-crystalline (n<sup>+</sup> nc-Si:H) layer and a 250nm passivation silicon nitride film are deposited, and patterned with mask 3. Consequently, the mask 4 is employed to open the contact windows at the source and drain doped layer through the second SiNx passivation layer. Finally, the aluminum layer is deposited and patterned to form the contact metal pads.

Figure 2.1: Fabrication sequence of an inverted staggered TFT (adapted from [7], [8]).

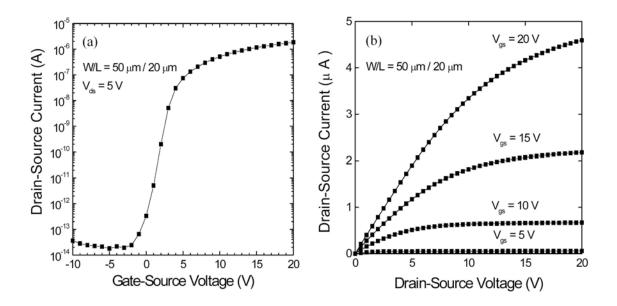

The transistor current-voltage characteristics of a device fabricated in the a-SiDIC laboratory are displayed in Figure 2.2. The TFT demonstrates an ON/OFF current ratio of around  $10^8$ , a good saturating behavior at the high drain voltages, and a low leakage current of ~10 fA at the drain-source voltage of -5V [10], [11]. No evidence of the current crowding at low drain-source voltages ( $V_{DS}$ ) indicates the good contact properties achieved through the application of the highly conductive n+ nc-Si:H source-drain contact layers.

Figure 2.2: (a) Transfer and (b) output characteristics of a lateral TFT (adapted from [11]).

#### 2.2 Motivation for VTFTs

VTFTs have the most appealing structure for high quality active matrix arrays due to the inherent short channel length of the transistor and the small area of the device. The evergrowing high quality panels require TFTs with dimensions as small as possible to preserve the aperture ratio or the fill factor. For example, in imagers, the pixel fill factor,

which represents the percentage of the photosensitive area to the entire pixel area, is a critical parameter that determines the image brightness, contrast ratio, dynamic range, and other factors of a high-quality image [12]. Although scaling the TFT size is possible, the reduction in the channel length and other dimensions of the conventional TFT is not possible without employing the expensive nano-lithography process. Therefore, for high resolution imaging or display applications, wherein an adequate fill factor must be preserved despite the pixel scaling or high-density TFT integration, an alternative TFT configuration is required in which the dimensions of the TFT is not limited by the fabrication issues associated with lithography or etching [13].

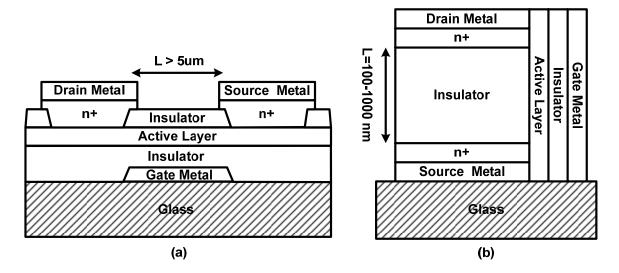

The most promising configuration of the TFT is the vertical structure where the channel length is defined independent of photolithographic patterning. Consequently, sub-micron channel-length VTFT is easily achieved without the need for a critical lithography process. In VTFTs, the channel length is defined by an intermediate dielectric layer, placed between the source and drain contact layers. Therefore, the channel length is accurately reduced down to sub-micron scales by controlling only the thickness of the intermediate dielectric layer.

The device structures for conventional inverted staggered TFTs and VTFTs are provided in Figure 2.3. From this figure, it can be concluded that a significant reduction in the device area can be obtained with the vertical TFT structure, since it does not spread laterally. Although the lateral TFT structure currently meets performance requirements, the device consumes a considerable portion of the pixel area, undermining the fill factor. For example, in digital mammography that requires a small pixel size to satisfy the spatial resolution requirement [14], the fill factor is reduced to 37% for the 50-µm pixel

pitch (Lp) arrays, with a lateral TFT area of 20 × 15  $\mu$ m<sup>2</sup> ( $L \times W$ ) and photoactive size ( $L_a$ ) of 35  $\mu$ m based on the 5- $\mu$ m lithography process according to:

$$f = \frac{L_a^2 - (L \times W)}{L_p^2}.$$

(2.1)

By employing VTFT with an area of  $5 \times 5 \mu m^2$  for the same pixel pitch, the fill factor increases to 48%. Moreover, it is possible to hide the VTFT under the signal lines to further boost the fill factor or aperture ratio. In Chapter 7, this architecture, which is used in the pixel drivers of an AMOLED display array, is explained.

Figure 2.3: Schematic cross section of the (a) lateral and (b) vertical TFT.

Low operational speed and low drive current are the other concerns of the present a-Si:H TFTs due to the low field effect mobility of the amorphous silicon. For instance, in AMOLED displays, the OLED emits light that is proportional to the passing current. Application of a high mobility poly-Si material seems to be a straightforward approach to increase the drive current and switching speed of TFTs. However, the fabrication of poly-Si TFTs usually requires extra processing steps such as excimer laser annealing (ELA) for crystallization of the deposited a-Si:H material that adds to the cost and complexity of

the production [15]. High leakage current and poor uniformity of the device characteristics are the other concerns involving the poly-Si TFTs that usually lower the throughput of the production line [16].

To attain a satisfactory speed, the transit time of the electrons across the channel of the TFT should be decreased. Scaling down the channel length (L) is an effective way to increase the switching speed of the TFT, since the time delay  $(t_d)$  of the TFT response to the input signal is proportional to  $L^2$ , expressed as follows [17]:

$$t_d \propto \frac{L^2}{\mu_{eff}} \tag{2.2}$$

Here,  $\mu_{eff}$  is the mobility of the electron in the active layer. Therefore, VTFTs can achieve a fast switching speed, since the channel length can be easily reduced to the nano-scale regime.

Furthermore, to increase the ON current of the transistors in both the linear and saturation regions, reducing the channel length is effective according to the following [3]:

$$I_{DS} = \frac{W}{L} \mu_{eff} C_i \left[ (V_{GS} - V_{Th}) V_{DS} - \frac{1}{2} V_{DS}^2 \right] \qquad V_{DS} < V_{GS} - V_{Th}$$

(2.3)

$$I_{Ds} = \frac{1}{2} \frac{W}{L} \mu_{eff} C_i (V_{GS} - V_{Th})^2 \qquad V_{DS} \ge V_{GS} - V_{Th}$$

(2.4)

In the previous equations, W,  $C_i$ ,  $V_{th}$ ,  $V_{GS}$ , and  $V_{DS}$  represent the channel width, gate capacitance, threshold voltage, gate-source voltage, and drain-source voltage, respectively.

Finally, the immediate benefit of this short channel, minimal size, and self-aligned structure, is the very low overlap gate capacitances. Consequently, a short turn-on time for the TFT and a read-out time for the signal detection are achieved [18].

### 2.3 Early Works on VTFTs

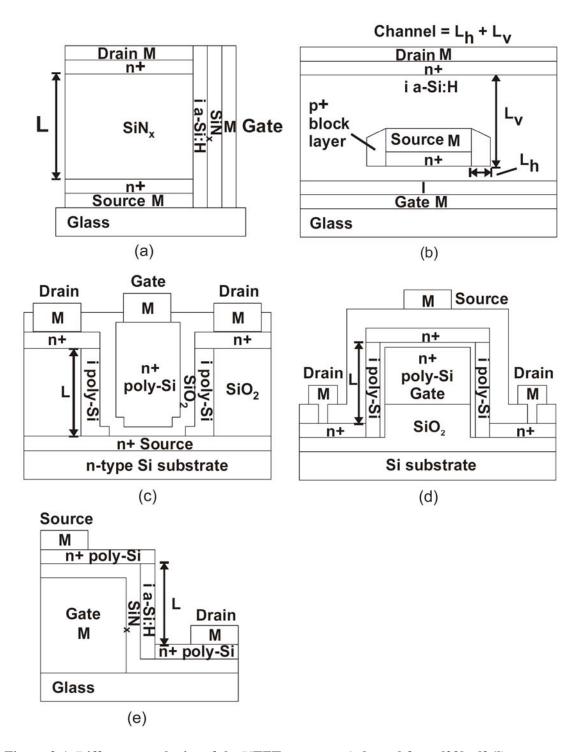

In 1984, the first vertical-type hydrogenated amorphous silicon (a-Si:H) VTFT was fabricated [19]. The channel length of the device was  $1\mu m$ , and demonstrated promising results that drew attention to its application potential in AMLCDs [19] [20]. In this device, as shown in Figure 2.4 (a), the gate electrode is at the right-hand side and the source and drain electrodes are the upper and lower metals. The channel is formed vertically at the gate  $SiN_x/a$ -Si:H interface, the channel length being defined by the thickness of the  $SiN_x$ , separating the drain-source region. The rationale for this structure is to provide an easy way to reduce the channel length L to the sub-micron scale in order to increase the switching speed of a-Si:H TFTs inversely proportional to  $L^2$ , according to (2.2) [19].

A conventional TFT limits in the reduction of the channel length, not by the device physics, but by the added complexity of the photolithography process for delineating the source and drain. Instead, in the vertical structure, the channel length is defined by the film thickness, which is controlled by the precise timing of the deposition process [21], [22]. The literature discusses various transistor topologies for VTFT, as seen in Figure 2.4; however, most of the designs are still in the experimental stage and are not defined as a standard VTFT process. The physical properties and electrical characteristics of these devices are summarized in Table 2.1 [22] - [26].

Figure 2.4: Different topologies of the VTFT structure (adapted from [22] - [26]).

Table 2.1: Summary of the VTFT electrical and physical characteristics from literature [22]-[26].

| TFT characteristics                 | Performance range                 | Comments                       |

|-------------------------------------|-----------------------------------|--------------------------------|

| Channel Length (L)                  | 0.5-1.5 μm                        |                                |

| W/L Ratio                           | 14~1000                           |                                |

| ON/OFF Current ratio                | $10^4 \sim 10^5$                  | At V <sub>D</sub> ≈ 5 V        |

| Leakage Current (I <sub>OFF</sub> ) | $10^{-6} \sim 10^{-10} \text{ A}$ | At V <sub>D</sub> ≈ 5 V        |

| Threshold Voltage $(V_T)$           | 1~3 V                             | At V <sub>D</sub> ≈ 5 V        |

| Subthreshold Slope (S)              | 1.25-4 V/dec                      |                                |

| Propagation Delay $(t_d)$           | 95 ns/stage                       | From a 7-stage ring oscillator |

The a-Si:H VTFT fabrication process, carried out in the a-SiDIC laboratory of University of Waterloo, includes five photolithography steps, initially developed by Dr. I. Chan [27]. The VTFTs are fabricated on a Corning 1737 glass substrate. The details of the fabrication process and issues related that will be addresses in the following sections.

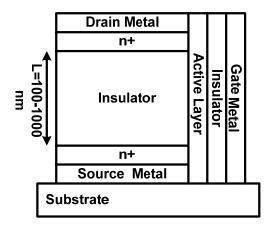

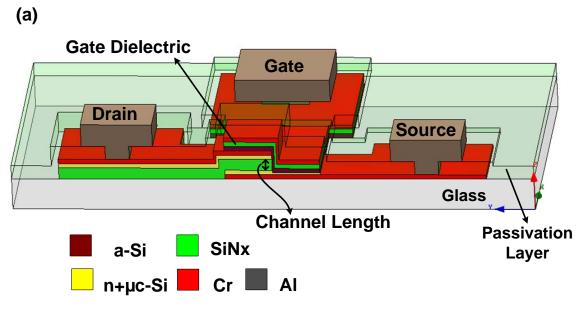

#### 2.4 Device Fabrication

The fabrication of the VTFT in the Giga-2-nano (G2n) laboratory is a five-mask process illustrated in Figure 2.5. First, a Cr layer with a thickness of 100nm is sputter deposited, followed by the deposition of  $n^+$  nc-Si:H layer and SiN<sub>x</sub> layer using PECVD with thicknesses of 300nm and 20nm, respectively. The last two layers are patterned in reactive ion etching (RIE) employing CF<sub>4</sub>/H<sub>2</sub> gas mixture, then Cr is wet-etched to form the source metal (Mask 1). The next step is related to the reverse deposition of SiN<sub>x</sub>/ $n^+$

nc-Si:H/Cr by applying the same conditions as the first step. The thicknesses of these three layers are 500nm, 300nm, and 100nm, respectively. Again, the top Cr is patterned (Mask 2) and wet-etched to form the drain metal. Now the patterned Cr layer is used as a mask for the layers underneath. Another RIE is conducted for dry-etching of the n<sup>+</sup> nc-Si:H/SiN<sub>x</sub> layers. This is the most critical step of the fabrication as defines the vertical sidewall of the device where channel lays. Any roughness or contamination, induced by the RIE etching process, deteriorates the VTFT performance.

The thickness of the intermediate nitride between the source and drain  $n^+$  films defines the channel length. It is note worthy that the  $n^+$  and  $SiN_x$  layers are self-aligned with the drain Cr. After this step, a-Si:H and  $SiN_x$  layers with thickness of 50nm and 250nm are deposited by PECVD in a single vacuum pump-down as the active and gate insulator layers, respectively. Then, Cr is deposited by sputtering, and patterned (Mask 3) as the gate metal and masking layer for the active and insulator films. The dry etch of these layers stops at the source and drain metal. Next, a  $SiN_x$  layer with a thickness of 250nm is deposited by PECVD to passivate the entire sample and patterned (Mask 4) to specify the contact vias. Lastly, to form the source, drain, and gate contact pads, a 1  $\mu$ m Al layer is sputter deposited and patterned (Mask 5).

Figure 2.5: Fabrication sequence of the VTFT process (not to scale).

In the fabrication of the VTFT, the formation of the vertical sidewall is the most critical part of the process determining the performance of the device. The vertical sidewall formation and the related challenges are detailed in the following sections. Before that, PECVD, which is the principal deposition method in the fabrication of VTFT, is reviewed to give the reader a concise information on the deposition steps.

## 2.4.1 Deposition Techniques

In this work, PEVCD is used for the deposition of silicon-based materials such as intrinsic Si, n- and/or p-doped Si, silicon nitride, and silicon oxide films. For the deposition of the chromium and aluminium metals, RF sputtering is employed. A summary of the deposition techniques and conditions for the a-Si:H VTFT fabrication is presented in Table 2.2.

A variety of plasma-assisted deposition methods for Si-based thin films have been reported including radio-frequency (RF) PECVD, direct current (DC) PECVD, very high frequency (VHF) PECVD, and electron cyclotron resonance (ECR) CVD. Among them, the 13.56 MHz RF PECVD is the industrial standard and is used in this doctoral research for the fabrication of the VTFT.

Table 2.2: Summary of the deposition conditions for a-Si:H VTFT fabrication.

| Film                   | Application                                                       | Deposition<br>Technique | Deposition Conditions                                                                                      |

|------------------------|-------------------------------------------------------------------|-------------------------|------------------------------------------------------------------------------------------------------------|

| a-Si:H                 | Active Layer                                                      | PECVD                   | 20 sccm (SiH <sub>4</sub> ), 2 W, 400 mTorr,<br>300 °C, ~ 9 nm/min                                         |

| n <sup>+</sup> nc-Si:H | Source and Drain                                                  | PECVD                   | SiH <sub>4</sub> /PH <sub>3</sub> /H <sub>2</sub> (1/1/250 seem), 10 W,<br>1900 mTorr, 300 °C, ~1.5 nm/min |

| SiN <sub>x</sub>       | Gate Dielectric, Passivation Layer, Intermediate Dielectric Layer | PECVD                   | NH <sub>3</sub> / SiH <sub>4</sub> (100/5), 2W, 400 mTorr,<br>300 °C, ~10 nm/min                           |

| Cr                     | Source, Drain, and<br>Gate Metal                                  | RF Sputtering           | Ar (30 sccm), 400 W, 5 mTorr, room temp.(22 °C), ~11 nm/min                                                |

| Al                     | Contact Pads                                                      | RF Sputtering           | Ar (30 seem), 400 W, 5 mTorr, room temp. (22 °C), ~12 nm/min                                               |

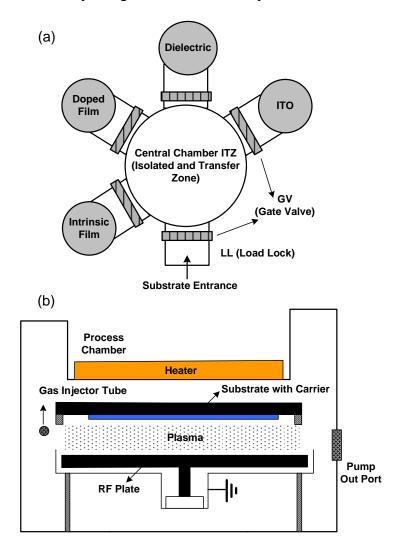

The cluster multi-chamber PECVD/Sputtering system, manufactured by MVSystems Inc., is employed for the deposition of the various thin film semiconductor materials [28]. A schematic top-view of the PECVD cluster multi-chamber system and chamber layout are displayed in Figure 2.6. The reactor consists of a gas inlet, a deposition reactor, an RF power system, and a gas outlet. Two parallel-plate electrodes with a size of  $6^{\circ\circ} \times 6^{\circ\circ}$  are separated by a specified distance in the reactor, where the top electrode is grounded and the bottom one is RF powered. The system consists of four isolated chambers for the deposition of intrinsic Si film, n- and/or p-doped Si film, dielectric film, and ITO films to prevent any cross-contamination. Here, the deposition method for the ITO films is RF sputtering, and for all the other materials, is RF PECVD. The central chamber is used to

transfer the substrate between the deposition chambers, and the substrate is loaded and unloaded via a load lock by using a robotic arm that operates in vacuum.

Figure 2.6: (a) MVS cluster PECVD equipment and (b) the chamber configuration.

The pumping system is composed of the combination of a corrosion resistant turbomolecular pump and a rotary vane pump. Prior to deposition, the background vacuum is

kept at a base pressure below 10<sup>-7</sup> Torr. The samples are placed on the ground electrode,

and the substrate temperature is controlled by a resistive heater. The plasma is created

between the two electrodes in the reactor, when the RF power is applied. The flow of

each gas and the chamber pressure are set by the mass flow controllers and a controllable

throttle valve, respectively. For the silicon-based materials, SiH<sub>4</sub> is used as the main source gas. The electrical and physical characteristics of the deposited film are dependent on the deposition conditions such as gas pressure, gas flow rate, deposition temperature, and RF power density.

## 2.4.2 Etching Techniques

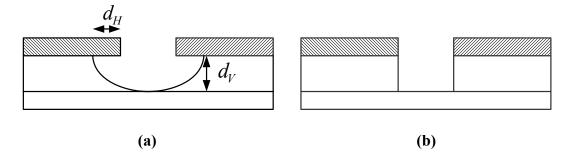

The goal of any etch process is to reproduce the image of a mask with a high degree of integrity. The characteristics of the etching process can be either isotropic or anisotropic. In an isotropic etching, the etch proceeds at the same rate for each direction, creating an undercut, equal to the film thickness beneath the mask. In anisotropic etching, the horizontal etch component is very small, resulting in a faithful pattern transfer, observed in Figure 2.7.

Figure 2.7: (a) Isotropic and (b) anisotropic etching pattern.

The degree of isotropic etching (IE) and anisotropic etching (AE) is defined as:

$$IE = \frac{d_H}{d_V} \tag{2.5}$$

and

$$AE = 1 - IE = \frac{(d_V - d_H)}{d_V}$$

(2.6)

where,  $d_H$  and  $d_V$  are the lateral and vertical etch rate, respectively. For the completely isotropic etching,  $d_H = d_V$  which translates into IE = 0.5, and for a fully anisotropic etching,  $d_H = 0$  or AE = 1.

Typically wet etching processes result in an isotropic profile of etching with some exceptions in the etching of crystalline materials where the etch rate depends on the crystalline orientation. However, in dry etching, it is possible to achieve anisotropic etching, since the etching can proceed by both physical sputtering and ion-assisted mechanisms. In the fabrication of the VTFT, RIE is used for the anisotropic etching of the Si-based layers. The summary of the etching conditions for the fabrication of the VTFTs is shown in Table 2.3.

**Table 2.3: Summary of the etching conditions in VTFT fabrication.**

| Film                   | Application                         | Etching<br>Technique | <b>Etching Conditions</b>                                                                                                                                         |

|------------------------|-------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| a-Si:H                 | Active Layer                        | RIE                  | CF <sub>4</sub> (20 sccm), Pr 10 mT, RIE 60W                                                                                                                      |

| n <sup>+</sup> nc-Si:H | Source and Drain                    | RIE                  | CF <sub>4</sub> /H <sub>2</sub> (17/3 sccm), Pr 10 mT, RIE<br>100W                                                                                                |

| SiN <sub>x</sub>       | Gate Dielectric, Passivation Layer, | RIE                  | CF <sub>4</sub> /H <sub>2</sub> (17/3 sccm), Pr 10 mT, RIE<br>100W                                                                                                |

| Cr                     | Source, Darin, and<br>Gate Metal    | Wet                  | (NH <sub>4</sub> ) <sub>2</sub> Ce(NO <sub>3</sub> ) <sub>6</sub> : 120g, CH <sub>3</sub> COOH:<br>100 cc, H <sub>2</sub> O: 500cc, 40°C, etch rate:<br>~40nm/min |

| Al                     | Contacts                            | Wet                  | H <sub>3</sub> PO4: 465cc, CH3COOH: 36cc,<br>HNO <sub>3</sub> : 18cc, H <sub>2</sub> O: 90cc, 30°C, etch<br>rate: ~40nm/min                                       |

## 2.4.2.1 Anisotropic Dry Etching

Dry etching employs an electrically generated plasma environment, consisting of energetic gas molecules, ions, and/or free radicals to remove the surface material from the wafer [29]. The term commonly applies to the following processes [29]:

- Plasma etching

- Reactive ion etching

- Ion milling

- Sputter etching

Reactive ion etching is based on a combination of the chemical activities of the reactive species, generated in the plasma, and the physical effects, caused by the ion bombardment. The impinging ions damage the surface, thereby increasing its reactivity. The primary processes, occurring in RIE can be summarized as follows:

- Active species generation

- Transport of plasma-generated reactant from the bulk of the plasma to the surface of the material being etched

- Adsorption step

- Reaction step

- Desorption of the volatile reaction products

- Pump-out of the volatile reaction products

In the fabrication of the VTFT, the formation of a vertical sidewall on the drain-source structure, consisting of a  $Cr/n^+$  nc-Si:H/SiN<sub>x</sub>/n<sup>+</sup> nc-Si:H/Cr multilayer, is the most critical step. The requirement for a vertical sidewall implies a precise self-alignment of the top Cr layer and the  $n^+/SiN_x/n^+$  trilayer. This self-alignment can be accomplished by reactive

ion etching of the trilayer using a wet etch patterned Cr layer as a masking layer. However, because of the different material composition of the  $n^+$  and  $SiN_x$  layers, any lateral etching of the stacked layers (given the unequal etch rates) leads to film misalignment, giving rise to a sidewall with zig-zag profile. This outcome can undermine the integrity of the subsequent channel layers deposited on the sidewall.

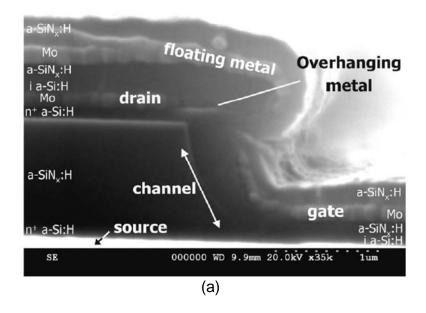

Figure 2.8 (a) is a cross-section SEM image of the fabricated device using a non-optimized dry etching process. It is evident that the channel profile is not vertical, a problem that arises because of the undercutting on the top part of the channel during the RIE etching. The channel lies on a slanted sidewall with a portion of the drain metal hanging over the channel. Because of the shadowing effect of the overhanging drain metal, the flux of the gate metal is possibly blocked from reaching the upper part of the channel region during the deposition process.

Hence, a high gate voltage is needed to enhance the conduction in the un-gated region. This part of the channel behaves as a high-resistance region between the n<sup>+</sup> drain and the gated channel (Figure 2.8 (b)). This issue causes poor subthreshold characteristics and a low ON current of the transistor [30],[31].

Figure 2.8: (a) Cross-sectional SEM image of the fabricated VTFT and (b) schematic cross-section of the device showing the parasitic resistance near the drain contact (adapted from [27]).

Therefore, the development of a dry-etching process for  $n^+/SiN_x/n^+$  trilayer that can provide a high degree of anisotropic etching is critical for the fabrication of the VTFT [21]. In this work, a gas mixture of  $CF_4/H_2$  is used to form the vertical sidewall of the channel. Fluorocarbon molecules in the ground state are inert towards the silicon, silicon oxide, and silicon nitride surfaces [32]. Etching starts only after the reaction gas has been

dissociated to ions in the plasma environment. The subsequent etching of Si in CF<sub>4</sub> plasma can be described according to the following chemical processes:

$$CF_4 \to 2F + CF_2 \tag{2.7}$$

$$Si + 4F \rightarrow SiF_4$$

(2.8)

$$Si + 2CF_2 \rightarrow SiF_4 + 2C$$

(2.9)

Typically, only the atomic fluorine and difluorocarbene react with silicon to form silicon tetrafluoride as a volatile product.

Even when there is no ion bombardment, the atomic fluorine reacts easily with silicon [32]. The reaction between the fluorine atoms and silicon is highly exothermic (negative heat of reaction) generating volatile products at room temperature. The ion bombardment increases the reaction rate between F and Si only slightly, therefore does not significantly affect the characteristics of the process. This is the reason behind the isotropical etching of silicon in most fluorine-based plasma systems.

The role of H<sub>2</sub> in CF<sub>4</sub> is to reduce the concentration of F atoms by forming HF, according to the following reactions:

$$H_2 \rightarrow 2H$$

(2.10)

$$H + F \rightarrow HF$$

(2.11)

These HF gas molecules are not reactive in a high vacuum environment. The experimental results also demonstrate that adding H<sub>2</sub> to a CF<sub>4</sub> glow discharge lowers the Si etch rate [33]. Fluorocarbon species are strongly chemisorbed on silicon surfaces, but react only slowly without ion bombardment. Consequently, the addition of hydrogen to the gasses reduces the density of the discharge fluorine ions and suppresses the plasma etching in favor of fluorocarbon polymerization as the F/C ratio drops,

$$nCF_2 \to [CF_2]_n \tag{2.12}$$

However, constant ion bombardment on the bottom surface sputters the polymer material from the surface of the material, which allows the etching to proceed in the vertical direction. The sidewalls, though, are not subjected to the ion bombardment and polymerization occurs on their surface, inhibiting further lateral etching [30], [34].

At high flux density and energy level, the impinging ions damage the surface layers and provide the possibility for reaction of the adsorbed fluorocarbon species with the substrate. If the substrate is silicon oxide, oxygen is available to form volatile carbon oxide with fluorocarbon compounds. Simultaneous to this chemical reaction, F is released to remove the Si atoms [32] as follows:

$$SiO_2 + 2CF_2 \rightarrow SiF_4 + 2CO \tag{2.13}$$

A similar mechanism is not available for silicon, and a carbon-rich film, called an inhibitor polymer, is formed on the sidewall, based on (2.12). The low sputter yield of the carbon materials then suppresses further Si removal. The characteristic of silicon nitride etching is between that of silicon and of silicon oxide [34]. Silicon nitride reacts faster with fluorine ions than oxide does due to the Si-N bonds being weaker than the Si-O bonds. Moreover, it is proposed that the silicon nitride reacts with the CF<sub>2</sub> species, since it is etched in CF<sub>4</sub>/H<sub>2</sub> at approximately the same rates of silicon oxide. This suggests the surface carbon may be removed as CN in analogy with equation (2.13).

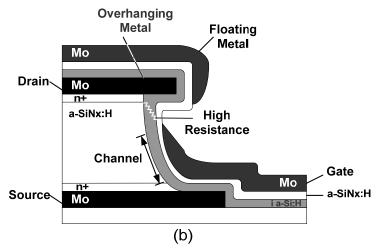

Figure 2.9 demonstrates a good alignment of the drain metal with the trilayer in CF<sub>4</sub>/H<sub>2</sub> (18%) gas mixture. Although this CF<sub>4</sub>/H<sub>2</sub> gas mixture can provide a vertical channel profile, an immediate concern is the potential effects of the inhibitor polymer on the device performance. This polymer might physically hinder the electrical contact between

the n<sup>+</sup> and the intrinsic a-Si:H layer. In addition, the polymer might act as a defect creation site at the back interface between the intrinsic a-Si:H and the sidewall of the trilayer, which can, in turn, lead to an increase in the leakage current of the TFT [27]. Therefore, it is necessary to remove this polymer film formed on the vertical sidewall of the sample. One possible approach is to immerse the wafer in a photoresist stripper solution with an ultrasonic activation to mechanically remove this polymer, followed by the exposure of the sample to an oxygen plasma.

Figure 2.9:  $n^+/SiN_x/n^+$  trilayer profile obtained after RIE etching by using  $CF_4/H_2$  gas mixture and polymer removal process.

#### 2.4.2.2 Masking Materials

During the dry etching of the n<sup>+</sup>/SiN / n<sup>+</sup> trilayer, it is crucial to choose a mask material that has no influence on the plasma chemistry and the etch result. The mask should be deposited without complicating the fabrication process. For instance, photoresist (PR) is the most common mask for patterning. However, the PR/Si selectivity is not high enough due to the presence of the fluorine and oxygen content in the plasma, which can react to

the carbon content of the PR. Moreover, during the etching of the Si, PR can be sputtered and redeposited on the silicon, where it's not protected with the mask. This phenomenon gives rise to the formation of the nano-pillar on the silicon surface. Figure 2.10 is the SEM image of the 500nm silicon nitride step structure with PR as the mask. It is evident that, the development of the fully vertical sidewall has failed by virtue of the nano-pillar formation.

Figure 2.10: SEM image of the slanted sidewall and the generated nano-pillar on its surface in the RIE etching of  $SiN_x$  using a PR mask.

Any metal can also be used as the mask, and at the same time, serve as the drain metal contact. However, the mask erosion is an undesirable phenomenon that deteriorates the etching profile. In general, if the mask is retarded or etched during the process, the trench profile is influenced and the result is not fully vertical. Figure 2.11 shows the slanted sidewall of the a-Si:H with a height of 500nm, when Al is used as the mask. Al is an IC compatible metal; however, even impinging ions with a low energy (40eV) can attack the mask by means of sputtering the material. This effect roughens or etches the Si adjacent

to the A1 protected regions [35]. The erosion may be explained by the existence of eddy currents in aluminum [35].

Figure 2.11: SEM image of the slanted sidewall due to the mask erosion in RIE.

Among the different metals, Cr is an appropriate choice for the masking purpose in RIE processes. A 10 nm Cr layer as a mask is enough to etch over 400µm height of the Si, because of its low physical sputtering and low volatility of the fluoride compounds [35]. It is reported that Cr is not sputtered even at ion energies as high as 200eV. Figure 2.9 demonstrates that Cr is an appropriate masking material in the fabrication of VTFTs.

## 2.4.3 Thin Film Step Coverage

The step coverage of the active layer, gate dielectric, and the gate metal is the next critical issue in determining the device performance and success of the VTFT fabrication. Although the deposition process parameters have been optimized for lateral electronic devices, the plasma kinetics responsible for the step coverage of those films on a topographical surface are not well understood. To develop a clear understanding of thin

film step coverage, a new study on the material deposition for VTFT fabrication is required.