# Low Temperature RF MEMS Inductors Using Porous Anodic Alumina

by

Tania Brinda Oogarah

A thesis

presented to the University of Waterloo

in fulfillment of the

thesis requirement for the degree of

Master of Applied Science

in

Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2008

©Tania Brinda Oogarah 2008

#### **AUTHOR'S DECLARATION**

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

Tania Brinda Oogarah

#### **ABSTRACT**

In today's communication devices, the need for high performance inductors is increasing as they are extensively used in RF integrated circuits (RFICs). This need is even more pronounced for variable inductors as they are widely required in tunable filters, voltage controlled amplifiers (VCO) and low noise amplifiers (LNA). For RFICs, the main tuning elements are solid state varactors that are used in conjunction with invariable inductors. However, they have limited linearity, high resistive losses, and low self resonant frequencies. This emphasizes the need for developing another tuning element that can be fabricated monolithically with ICs and can offer high range of tuning.

Due to the ease of CMOS integration and low cost silicon based IC fabrication, the inductors currently used are a major source of energy loss, therefore driving the overall quality factor and performance of the chip down. During the last decade there has been an increase in research in RF MicroelectroMechanical Systems (RF MEMS) to develop high quality on chip tunable RF components. MEMS capacitors were initially proposed to substitute the existing varactors, however they can not be easily integrated on top of CMOS circuits. RF MEMS variable inductors have recently attracted attention as a better alternative.

The research presented here explores using porous anodic alumina (PAA) in CMOS and MEMS fabrication. Due to its low cost and low temperature processing, PAA is an excellent candidate for silicon system integration.

At first, PAA is explored as an isolation layer between the inductor and the lossy silicon substrate. Simulations show that although the dielectric constant of the PAA is tunable, the stress produced by the required thicker layers is problematic.

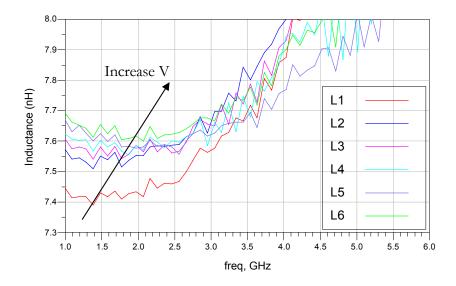

Nevertheless, the use of PAA as a MEMS material shows much more promise. Tunable RF MEMS inductors based on bimorph sandwich layer of aluminum PAA and aluminum are fabricated and tested. A tuning range of 31% is achieved for an inductance variation of 5.8 nH to 7.6 nH at 3 GHz.

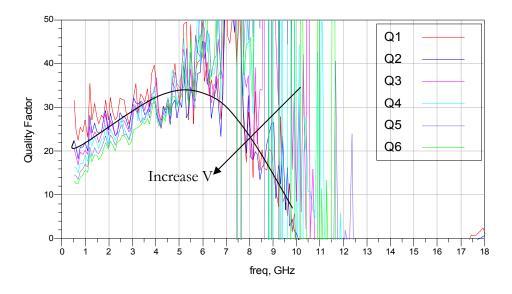

To further improve the Q, bimorph layers of gold and PAA are fabricated on Alumina substrates. A lower tuning range is produced; however the quality factor performance is greatly improved. A peak Q of over 30 with a demonstrated 3% tuning range is presented.

Depending on the need for either high performance or tunability, two types of tunable RF MEMS inductors are presented. Although PAA shows promise as a mechanical material for MEMS, the processing parameters (mainly stress and loss tangent) need to be improved if used as an isolation layer. To our knowledge, this is the first time this material has been proposed and successfully used as a structural material for MEMS devices and CMOS processes.

#### ACKNOWLEDGMENTS

First and foremost, I would like to thank my professor and advisor Professor Raafat Mansour, who bravely decided to take a chance on a lowly physicist and transform her into a true RF engineer. It was a bit like My Fair Lady, but without the dancing, music and silly ending. Thank you so much for your support and extreme patience. It was a true honor working with you.

Like all great musicals and movies, there is an amazing supporting cast filled with the occasional odd character or two. Without its charismatic leader, Bill Jolley, the Centre for Integrated RF Engineering (CIRFE) group would skip along without any plot or direction. Thank you Bill for making me laugh and letting me vent without a concern for my sailor's mouth. I am also thankful to Roger Grant for the hours of insightful advice and feedback.

And although I was a hotshot in the cleanroom, I am eternally grateful for all the RF help that was swung my way. A huge thank you goes out to my great advisors, Mojgan Daneshmand, Paul Laforge and Siamak Fouladi. I never would have made it without each and every single one of you. If I manage to remember a single thing about RF engineering, I am deeply in your debt.

To my post grad student angels, Stella Chang and Winter Yan who over coffee and emails let me know that there really was a light at the end of the tunnel. And for all those times I teased you during your thesis writing...trust me, I will never doubt you again.

# **DEDICATION**

To my parents, Suresh and Bernadette Oogarah,

Thank you for making me who am I today. Your love and guidance are without a doubt a god send.

To my husband Eric,

Without you, there would be none of this. Thank you for your support, your patience, and your love.

# TABLE OF CONTENTS

| List of Figures                                                        | ix |

|------------------------------------------------------------------------|----|

| Chapter 1                                                              | 1  |

| 1.1 INTRODUCTION AND MOTIVATION                                        | 1  |

| 1.2 THESIS ORGANIZATION.                                               |    |

| Chapter 2                                                              | 4  |

| 2.1 HISTORY OF POROUS ANODIC ALUMINA                                   | 4  |

| APPLICATIONS OF POROUS ANODIC ALUMINA                                  |    |

| 2.1.1 Nanotechnology applications                                      |    |

| 2.1.2 Humidity sensors and biosensors                                  |    |

| 2.1.3 RF applications                                                  |    |

| 2.2 Previous work on Inductors and Silicon                             |    |

| 2.2.1 Model                                                            |    |

| 2.2.1.1 Inductance                                                     |    |

| 2.2.1.2 Metal losses                                                   |    |

| 2.2.1.3 Capacitance Losses                                             |    |

| 2.2.1.4 Substrate losses                                               |    |

| 2.2.1.5 Parameter Extraction                                           |    |

| 2.2.2 Previous Work                                                    |    |

| 2.2.2.1 Conventional RFIC Inductors.                                   |    |

| 2.2.2.2 RF MEMS Inductors using Bulk or Surface Micromachining         |    |

| Chapter3                                                               | 29 |

| 3.1 POROUS ANODIC ALUMINA FORMATION                                    | 29 |

| 3.2 FILM CHARACTERIZATION                                              | 36 |

| 3.2.1 Surface Roughness of PAA Film                                    |    |

| 3.2.2 Maximum deflection                                               |    |

| 3.2.3 Dielectric Constant and Stress of PAA Films                      | 44 |

| 3.2.3.1 Capacitance-Voltage (CV) Characterization                      |    |

| 3.2.3.2 Ellipsometry                                                   |    |

| 3.3 FILM FABRICATION AND SETUP                                         | 50 |

| Chapter 4                                                              | 54 |

| 4.1 Planar Inductors                                                   | 56 |

| 4.1.1 Simulation.                                                      | 56 |

| 4.1.2. Device Fabrication                                              | 58 |

| 4.1.3 Results and Discussion                                           | 59 |

| 4.2 TUNABLE RF MEMS INDUCTORS USING AN ALUMINUM, PAA AND ALUMINUM SAND |    |

| SILICON WAFERS.                                                        |    |

| 4.2.1 Design                                                           |    |

| 4.2.2 Device Fabrication                                               |    |

| 4.2.3 Results and Discussion                                           |    |

| 4.2.3.1 Parameter Extraction                                           |    |

| 4.2.3.2 Measurement Results                                            |    |

| 4.2 High O Turkari e DE MEMC Inductors                                 | 70 |

| 4.3.1 Design                                                                                                       | 79  |

|--------------------------------------------------------------------------------------------------------------------|-----|

| 4.3.2 Device Fabrication                                                                                           | 80  |

| Chapter 5                                                                                                          | 87  |

| 5.1 Conclusions                                                                                                    |     |

| 5.2 Future Work                                                                                                    | 88  |

| Glossary                                                                                                           | 89  |

| Appendix                                                                                                           | 92  |

| Appendix A Fabrication Process for RF MEMS Tunable Inductors based on the Aluminum/PAA/Aluminum Sandwich Structure | 92  |

| Appendix B Deembedding Techniques with Y Matrices                                                                  | 104 |

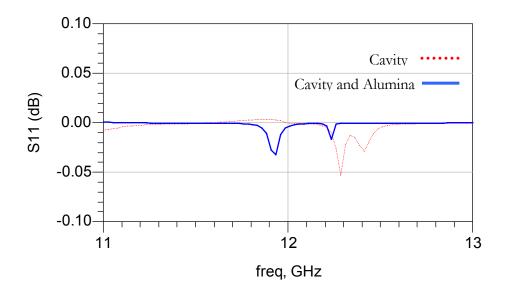

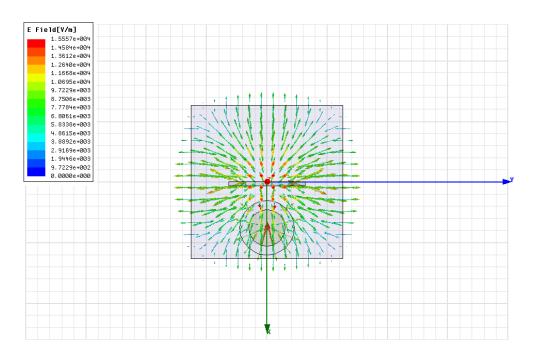

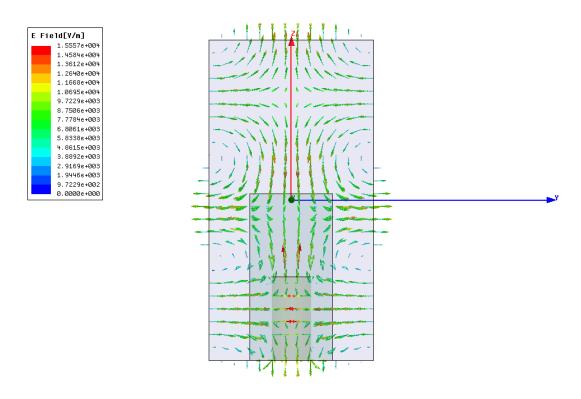

| Appendix C Simulations for Finding the Dielectric Constant of PAA using a Wave Loaded with a Known Dielectric Slab |     |

| Bibliography                                                                                                       | 111 |

|                                                                                                                    |     |

# LIST OF FIGURES

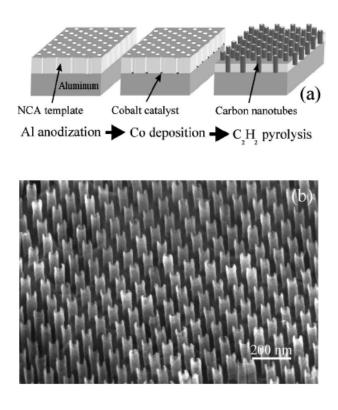

| Figure 1: (a) Fabrication Process (b) SEM of CNT using PAA as a template [9]                                 | 6  |

|--------------------------------------------------------------------------------------------------------------|----|

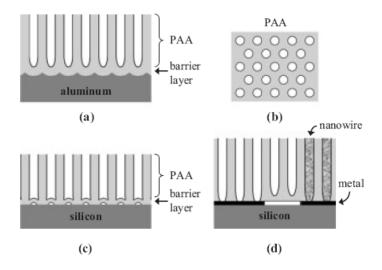

| Figure 2: Schematic representation of the process to making nanowires [12]                                   |    |

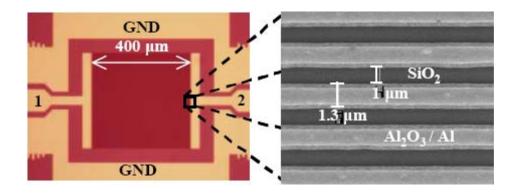

| Figure 3: (left) interdigitated capacitor, (right) SEM picture of fingers [13]                               |    |

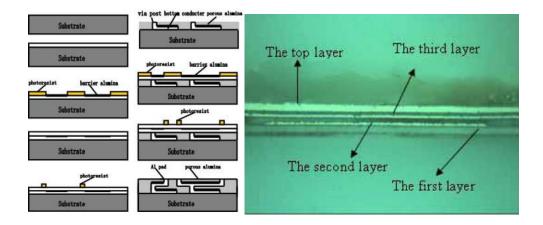

| Figure 4: (left) Schematic of aluminum anodization substrate process (right) image of four                   |    |

| layer substrate [22]                                                                                         | 9  |

| Figure 5: SEM cross-section micrograph of multilevel aluminum interconnections with the                      |    |

| interlevel porous alumina insulator [24].                                                                    | 9  |

| Figure 6: (top) Two Port Π model [14] (bottom) schematic of typical inductor                                 | 10 |

| Figure 7: Schematic of coil to demonstrate self and mutual inductance                                        | 13 |

| Figure 8: Loss mechanisms for Inductors                                                                      | 14 |

| Figure 9: Schematic representation of the parasitic capacitance between metal turns                          | 16 |

| Figure 10: Schematic representation of parasitic capacitance between the metal and                           |    |

| substrate                                                                                                    | 16 |

| Figure 11: Lumped physical model of a spiral inductor on silicon [18]                                        | 18 |

| Figure 12: Equivalent model with combined impedance of C <sub>ox</sub> , C <sub>si</sub> and R <sub>si</sub> | 20 |

| Figure 13: Patterned Ground Shield [18]                                                                      | 22 |

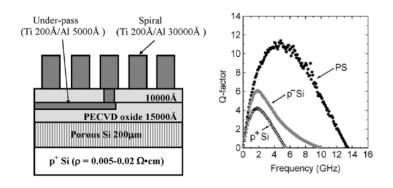

| Figure 14: (left) Cross section of device and (right) extracted Q factor for the inductor [21]               | 23 |

| Figure 15: (left) Schematic diagram of the planar inductor (right) Inductance and Q                          |    |

| performance as a function of the number of turns [25]                                                        |    |

| Figure 16: Metal loss-optimized inductor [26].                                                               | 24 |

| Figure 17: (left) Membrane suspended spiral inductor integrated with 0.7um CMOS                              |    |

| process (right) Schematic cross section of device [28].                                                      | 25 |

| Figure 18: (left) SEM micrograph of elevated inductor (right) Measured and modeled                           |    |

| performance of inductor [29]                                                                                 | 26 |

| Figure 19: (left) Self assembled out of plane spiral inductor (right) view of solder hinge                   |    |

| region after self assembly [30].                                                                             | 26 |

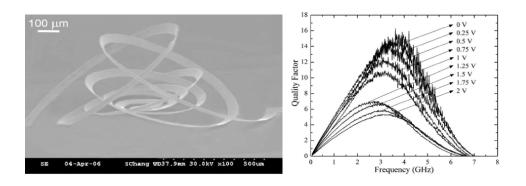

| Figure 20: (left) SEM micrograph of hinged Self Assembling Inductor (right) Q and L                          |    |

| performance [31].                                                                                            | 27 |

| Figure 21: (left) SEM micrograph of tunable inductor (right) measured inductance of the                      | •  |

| inner and outer coil [32].                                                                                   | 28 |

| Figure 22: (left) SEM micrograph of warped inductor (right) Quality factor performance                       | 20 |

|                                                                                                              | 28 |

| Figure 23: Schematic diagram of (left) barrier type alumina and (right) porous type                          | 20 |

| alumina.                                                                                                     |    |

| Figure 24: Anodic Cell                                                                                       | 30 |

| Figure 25: A typical experimental current time characteristic during a constant voltage                      | 27 |

| anodization                                                                                                  | 32 |

| Figure 26: Schematic diagram of the pore formation. (1) formation of barrier oxide over entire surface, (2) local field distributions caused by surface fluctuations (3) init |     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| stages of pore creation cause by dissolution (4) stable and steady pore growth                                                                                                |     |

| Figure 27: Schematic drawing of an idealized hexagonal PAA structure [36]                                                                                                     | 34  |

| Figure 28: SEM micrographs of PAA. (a) 0.3M sulfuric acid at 25V (b) 0.3M oxalic acid 40V (c) 10 wt% phosphoric acid at 160V. The pore diameters are 60, 95 a                 | at  |

| ` '                                                                                                                                                                           |     |

| 420nm respectively [9]                                                                                                                                                        |     |

| Figure 29: Surface Roughness of 1μm PAA (top) at 5x magnification                                                                                                             |     |

| Figure 30: Surface Roughness of 1µm PAA (top) at 10X magnification, (middle) 50                                                                                               |     |

| magnification, (bottom) 100X magnification                                                                                                                                    |     |

| Figure 31: Schematic of a bimorph cantilever beam [38]                                                                                                                        |     |

| Figure 32: Schematic of the bimorph cantilever beams                                                                                                                          |     |

| Figure 33: Fabrication steps for (left) aluminum/PAA and (right) gold/PAA bimor cantilever beams                                                                              |     |

| Figure 34: Micrograph of gold/PAA Bimorph Cantilever beams                                                                                                                    | 43  |

| Figure 35: Schematic cross section of Al/Alumina/p-Si capacitors [39]                                                                                                         |     |

| Figure 36: Residual stress as a function of porosity [42]                                                                                                                     |     |

| Figure 37: Anodization cell and laboratory wet bench setup                                                                                                                    |     |

| Figure 38: Anodization of aluminum film. Before anodization (left), half time anodization                                                                                     |     |

| (middle) fully anodized (right)                                                                                                                                               |     |

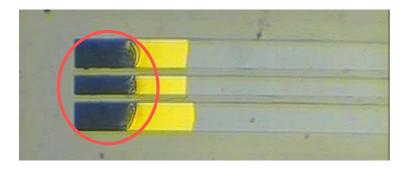

| Figure 39: Micrograph backside image of chromium/gold CPW line with PAA film above                                                                                            |     |

| The chromium became an oxide and eventually dissolved                                                                                                                         |     |

| Figure 40: Micrograph image showing the PAA film peeling off the gold structure                                                                                               |     |

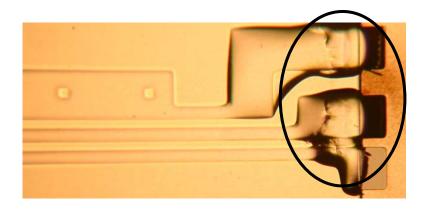

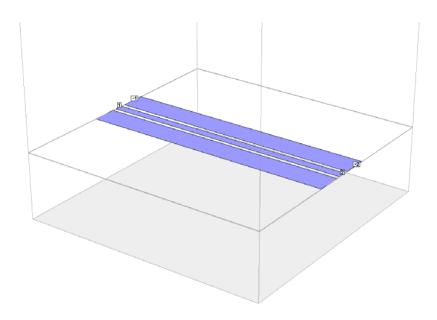

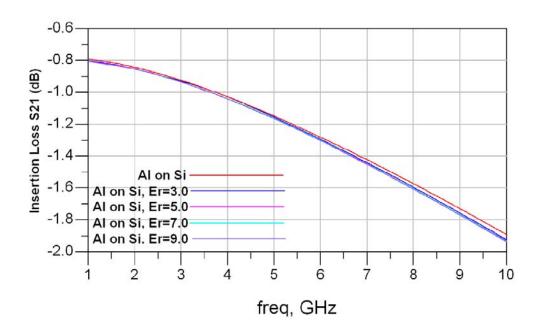

| Figure 41: Sonnet Simulation layout for CPW lines                                                                                                                             |     |

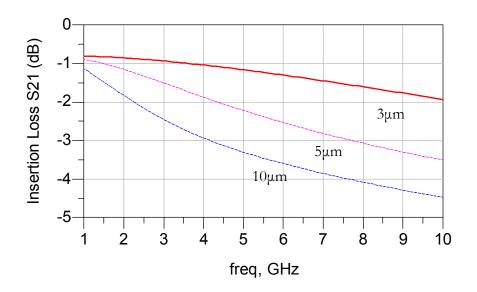

| Figure 42: Simulated insertion loss of CPW transmission lines with the e varying from 3                                                                                       |     |

| , 0                                                                                                                                                                           |     |

| to 9.0                                                                                                                                                                        |     |

| Figure 43: Simulated insertion loss of CPW transmission lines with varying the PA                                                                                             |     |

| thickness.                                                                                                                                                                    |     |

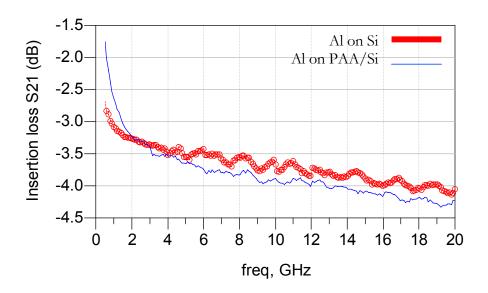

| Figure 44: The measured insertion loss of the fabricated CPW lines with and without PA                                                                                        |     |

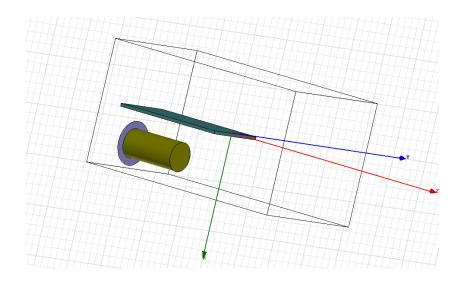

| isolation layer                                                                                                                                                               |     |

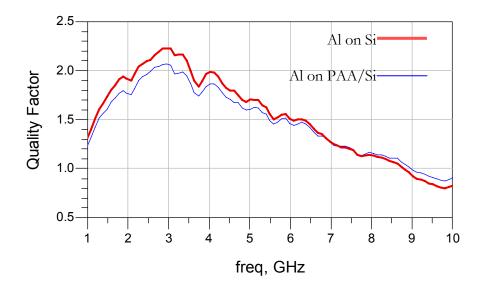

| Figure 45: Quality factor of planar inductors with and without PAA as an isolation lay                                                                                        |     |

| between Silicon                                                                                                                                                               |     |

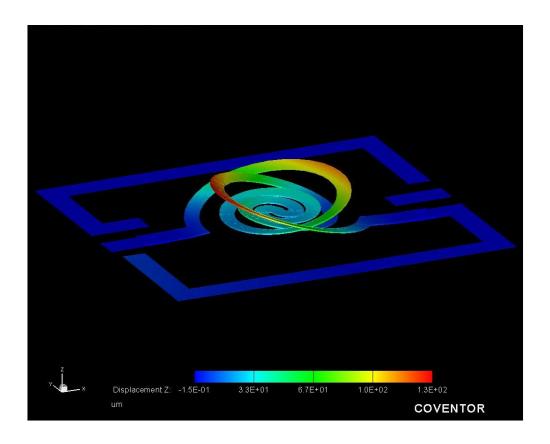

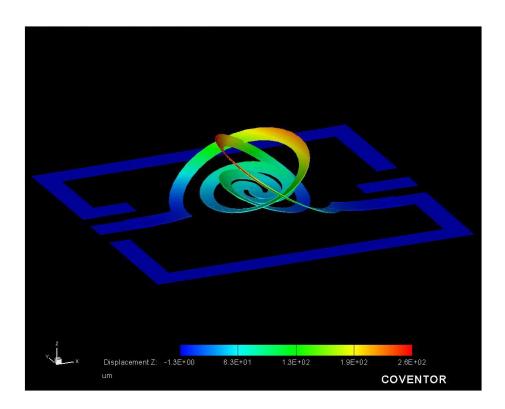

| Figure 46: Thermomechanical simulation performed using Coventor of the fabricat tunable RF MEMS inductor based on an aluminum/PAA/aluminum sandwi                             | ich |

| layer                                                                                                                                                                         |     |

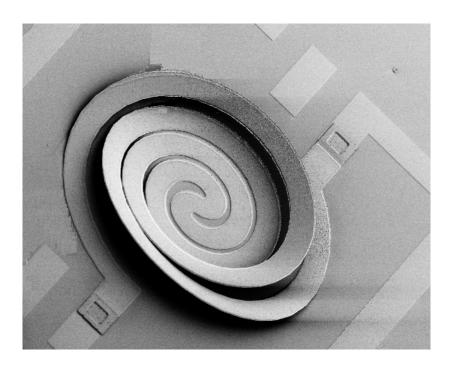

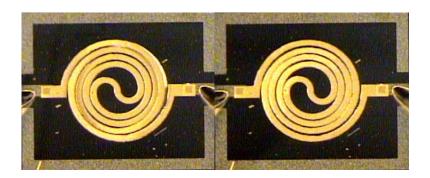

| Figure 47: SEM Micrograph at 120X of an RF MEMS Tunable Inductor based on t                                                                                                   |     |

| aluminum/PAA/aluminum sandwich structure                                                                                                                                      |     |

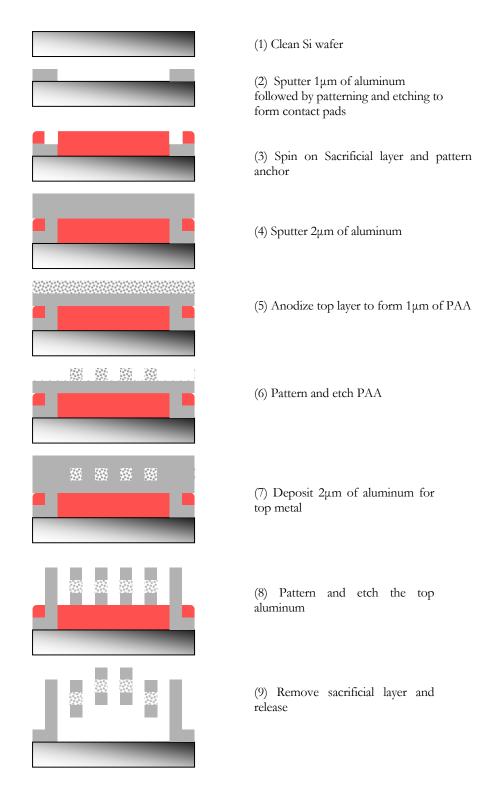

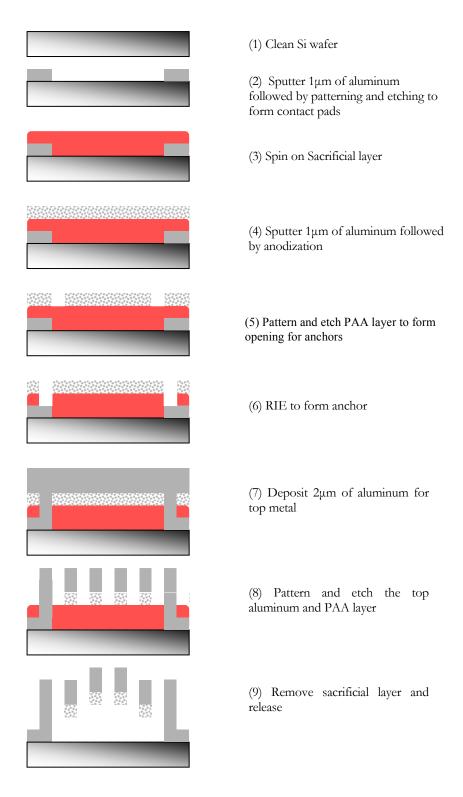

| Figure 48: Fabrication of tunable RF MEMS inductor based                                                                                                                      |     |

| aluminum/PAA/aluminum sandwich                                                                                                                                                |     |

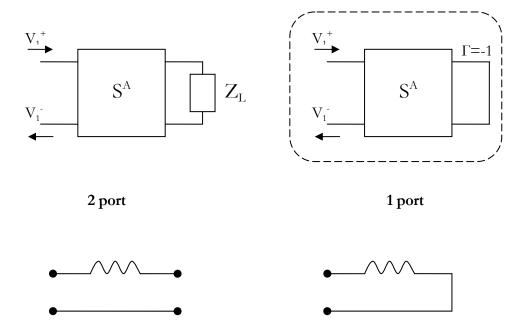

| Figure 49: Transforming 2 port to 1 port                                                                                                                                      | 67  |

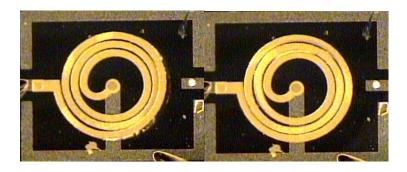

| Figure 50: Top view micrograph of a 1 port RF MEMS tunable inductor (left) :                                                                                                  |     |

| actuation (right) with 1.18V applied across the device                                                                                                                        | 69  |

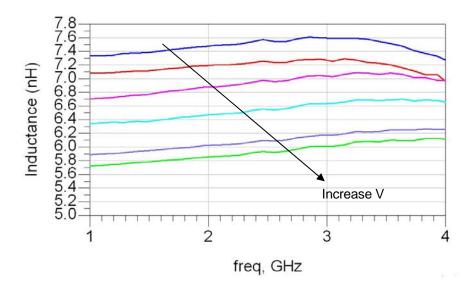

| Figure 51: Measured inductance of a fabricated 1 port RF MEMS tunable inductor based on the aluminum/PAA/aluminum sandwich structure, with 0 to 2V applied across the device.                               | . 70 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 52: Measured Q of a fabricated RF MEMS tunable inductor based on an aluminum/PAA/aluminum sandwich structure at 0 V.                                                                                 |      |

| Figure 53: Top view micrograph of a 2 port RF MEMS tunable inductor (left) no actuation (right) with 1.38V applied across the device                                                                        |      |

| Figure 54: Measured inductance of a fabricated 2 port RF MEMS tunable inductor based on the aluminum/PAA/aluminum sandwich structure, with 0 to 2V applied across the device                                | . 72 |

| Figure 55: Measured Q of a fabricated 2 port RF MEMS tunable inductor based on an aluminum/PAA/aluminum sandwich structure.                                                                                 | . 72 |

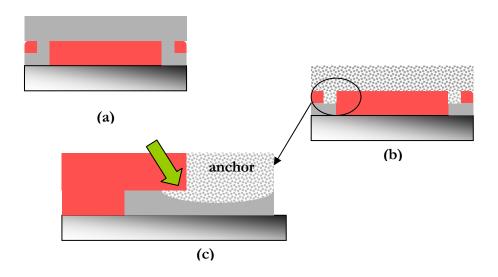

| Figure 56: Thermomechanical simulation performed using Coventor of the fabricated tunable RF MEMS inductor based on an aluminum/PAA layer                                                                   | .73  |

| Figure 57: Schematic diagram showing (a) Top aluminum film connected to the first metal layer through the anchors (b) Film is completely anodized (c) enlarged area of the anchor and contact pad interface | . 74 |

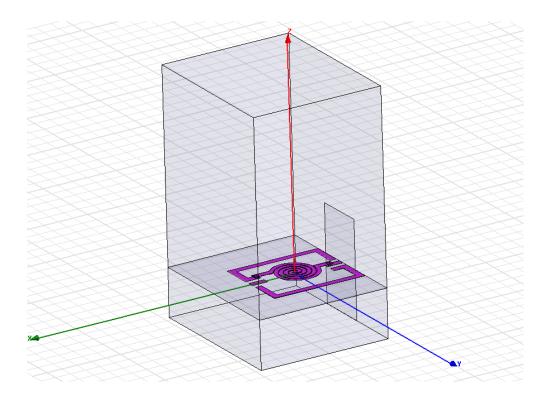

| Figure 58: Fabrication of tunable RF MEMS inductor based on PAA/aluminum                                                                                                                                    | 76   |

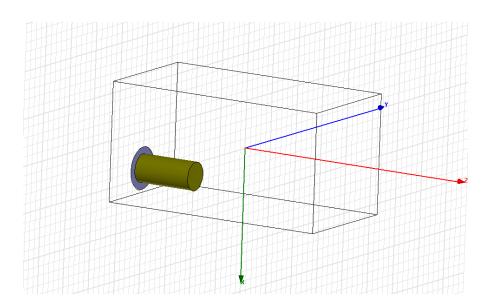

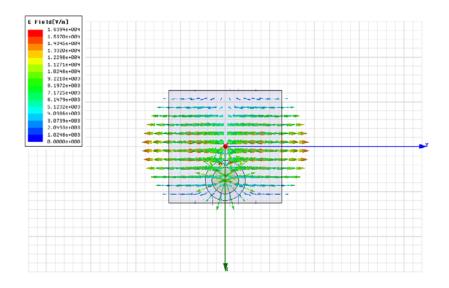

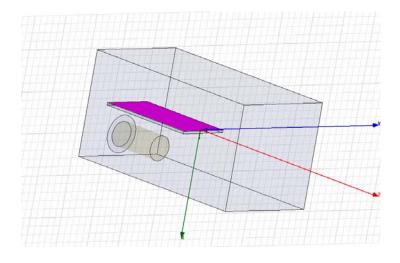

| Figure 59: HFSS Model of 1 port RF MEMS tunable inductor used in this thesis                                                                                                                                | .77  |

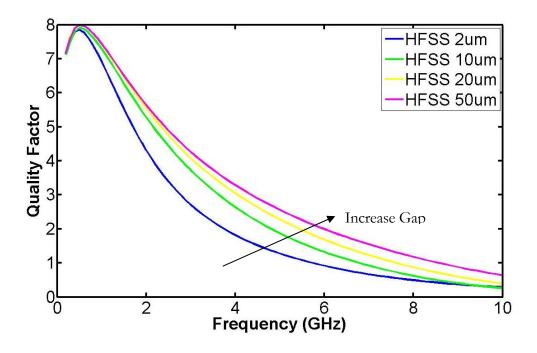

| Figure 60: Simulated Q factor of inductor with different air gap thicknesses                                                                                                                                | .78  |

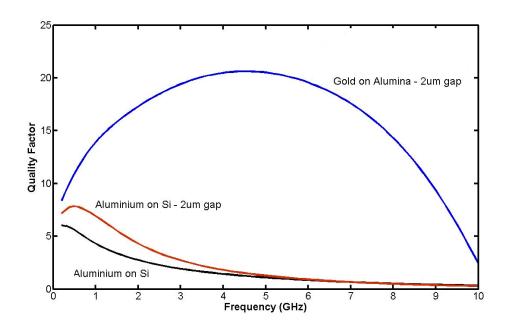

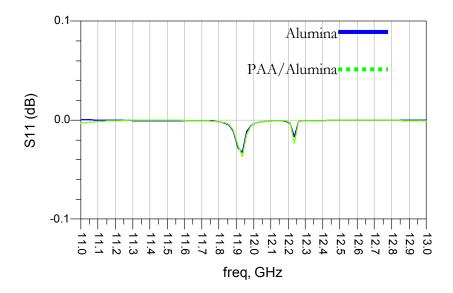

| Figure 61: HFSS simulations comparing aluminum on Silicon RF MEMS inductors and gold on Alumina RF MEMS inductors. The Q improves from 7 to 20                                                              |      |

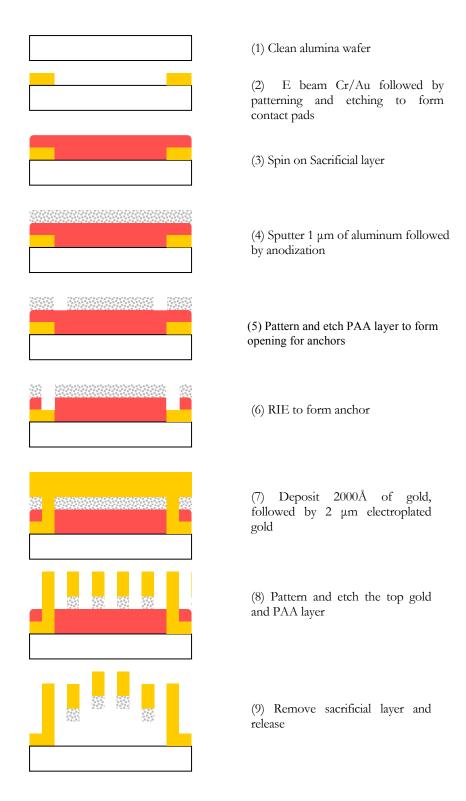

| Figure 62: Fabrication of tunable RF MEMS Inductor based on gold/PAA layers                                                                                                                                 | 82   |

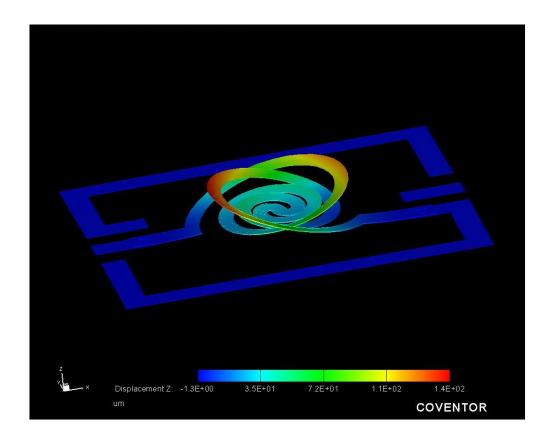

| Figure 63: Thermomechanical simulation performed using CoventorWare of a fabricated tunable RF MEMS Inductor based on the gold/PAA bilayer structure                                                        | . 83 |

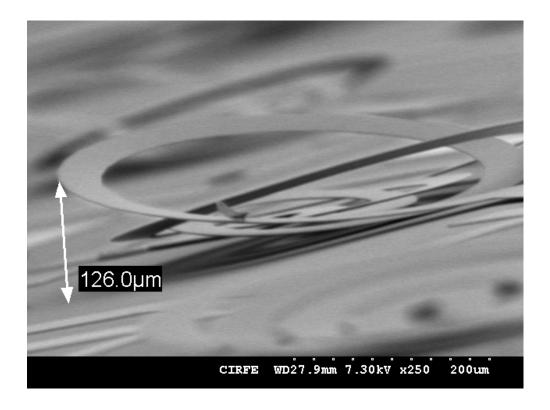

| Figure 64: SEM of tunable RF MEMS inductor based on gold/PAA structure. The outer coil reached a height of nearly 130µm and shows good agreement with the simulated structure.                              |      |

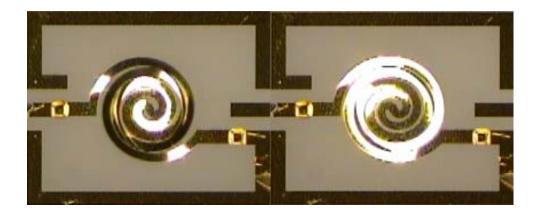

| Figure 65: Top view micrograph of a 1 port RF MEMS tunable inductor (left) no actuation (right) with 1.4V applied across the device                                                                         | . 85 |

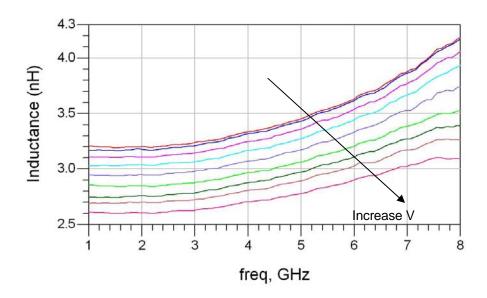

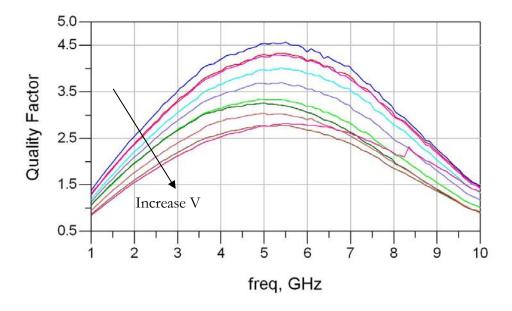

| Figure 66: Measured Q of a fabricated RF MEMS tunable inductor based on the gold/PAA bilayer with 0 to 1.6 V applied across the device                                                                      |      |

| Figure 67: Measured inductance of a fabricated RF MEMS tunable inductor with 0 to                                                                                                                           |      |

| 1.6V applied across the device.                                                                                                                                                                             | .86  |

#### 1.1 INTRODUCTION AND MOTIVATION

For today's wireless communication devices, the need for high performance components is a constant engineering issue. The global demand for wireless phones and other handheld devices is increasing, as evidenced by the sale of more than 1.15 billion phones in 2007, a 16% increase from last year [1]. In Canada alone, 1.6 million new wireless customers were added to the now 20.1 million users [2]. While the functionality and performance of these devices has improved, manufacturers and foundries are still looking for ways to reduce costs.

An important parameter in realizing high performance RF circuits is the quality factor (Q) of integrated passive devices such as low-noise amplifiers (LNA), voltage controlled-oscillators (VCO) and RF filters. Inductors used in these GHz wireless circuits (< 10 GHz) must display a high quality factor Q (ideally greater than 10), have a high self resonance frequency (above 10 GHz) and must have an inductance of 1-5 nH [3]. And while inductors play a major role in these devices, a low loss device has yet to be successfully integrated with Silicon ICs. The standard low cost silicon CMOS technologies have produced inductors limited to around a quality factor of 10, with self resonating frequencies in the range of 5-20 GHz [3]

To approach this issue, there are several factors that must be addressed in inductor performance. The inductance (L), the quality factor (Q) and the self-resonant frequency ( $f_{res}$ ). The following section will address these parameters.

By improving the quality of the inductor, the overall performance of many devices will follow suite. This is evidenced by enhanced phase noise performance and reduced power consumption in VCO. A better insertion loss allows for less power needed to compensate for loss in RF filters and a higher Q will improve the gain in LNA's.

While RF integrated circuits (RFICs) are produced by conventional si-CMOS processes [4], the performance of integral passive components is poor compared to those based on SiGe and GaAs [5]. However, the cost of silicon based CMOS processing is relatively lower and the main reason why they are still used today.

Recently, CMOS processing is becoming integrated with microelectromechanical systems (MEMS). Traditionally, the hybrid approach was used to integrate MEMS and CMOS chips on one substrate, connected by various wire bonds. However, this increases complexity in packaging and parasitic losses. A better approach is to build the MEMS device directly on the CMOS chip at the end or prior to the final processing steps. While this approach is beneficial, the thermal budget of additional fabrication steps must be restricted to prevent damage to the CMOS circuit [7].

The work done in this thesis will explore Porous Anodic Alumina as a novel low temperature, low cost material for RF MEMS inductors and show compatibility with standard CMOS processes. Porous Anodic Alumina will be integrated in the design and fabrication of a RF MEMS inductor. This will be shown by the following:

- 1. Fabrication and characterization of Porous Anodic Alumina as a low temperature MEMS material

- 2. Planar Inductors built on PAA isolation films on low resistive Silicon Substrates.

- 3. Bimorph RF MEMS Inductors integrating Porous Anodic Alumina will be fabricated. Porous Anodic Alumina compatibility with aluminum and gold will be demonstrated. The warped devices are tuned by applying a voltage across the terminal allowing the eventual flattening of the device. Thermomechanical and RF simulations show structural and electrical performance.

## 1.2 THESIS ORGANIZATION

The following chapter will provide a background on porous anodic alumina and its past and current applications. In addition, previous work on improving the performance of inductors will be presented.

This will be followed by the fabrication and characterization of the film. The next chapters will present porous anodic alumina as an isolation layer and structural layer. The modeling, fabrication and testing will be further discussed along with future improvements and conclusions.

## 2.1 HISTORY OF POROUS ANODIC ALUMINA

The anodization of aluminum is a decades old electrochemical synthesis that has its roots in corrosion resistance for the automotive industry and has developed over the years as a tried and true method to protect many household items from architectural windows and framing to household cookware [8].

In recent years, this chemistry has attracted much attention to those who work in the nanotechnology field [10-11]. Some of the research includes sensing, optics, biomedical implantation, or as "nanotemplates" for innovative structures such as carbon nanotubes (CNTs) and quantum dots [10-12].

The term "Anodized Aluminum" can also be referred to as Anodic Aluminum Oxide or (AAO), Porous Alumina, Anodic Alumina, or Porous Anodic Alumina (PAA). Due to the confusing amount of acronyms, it will be called Porous Anodic Alumina (PAA) henceforth in this thesis.

# Applications of Porous Anodic Alumina

## 2.1.1 Nanotechnology applications

Recently, the research on self organization in nanotechnology has gained momentum with the use of porous anodic alumina. 1D materials such as nanowires or carbon nanotubes have already shown great promise in applications for quantum devices [10]. By using PAA, researchers have been able to fabricate an inexpensive, high throughput and easily tunable template.

Anodized Porous Alumina has several advantages in the effort to produce Carbon Nanotubes (CNTs). Primarily, they offer consistently parallel pore channels, the ability to engineer varying pore diameters, are optically transparent in the visible spectrum and are resistant to most chemicals except for strong bases and acids [9].

CNTs in PAA have been explored by several groups [10, 11]. The potential applications in electrochemical devices, quantum wires and electrodes for rechargeable Li-batteries are just some of the numerous areas that have been explored.

Most importantly CNTs in PAA can withstand high temperatures, up to a 1000°C; this is more than sufficient to handle the high temperatures of Chemical Vapor Deposition (CVD), which is the most common method for synthesizing CNTs. As shown in Figure 1, CVD offers control over the length and diameter of the CNT. Once the deposition is completed, the PAA template is removed, releasing the tubes.

Figure 1: (a) Fabrication Process (b) SEM of CNT using PAA as a template [9]

In addition to CNTs, magnetic nanowires are attracting a growing interest for applications in magnetic storage. By using PAA, one can control the height and diameter of the magnetic wires [11]. The ability to create a dense array of magnetic wires will be a promising candidate for magnetic hard disks with a recording density of up to 1 terabit/in<sup>2</sup>.

Several types of metals and alloys have been successfully deposited or electroplated into nanowire structures [12] as seen in Figure 2.

Figure 2: Schematic representation of the process to making nanowires [12]

The optical properties of PAA have been well documented and the material has been utilized in both polarizers and electroluminescent devices [11]. The photoluminescent (PL) properties of PAA are further enhanced when they are filled with semiconductor composites such as CdS or ZnO. These optical nanowires are being utilized in polymer light emitting diodes (PLEDs) and optical displays.

## 2.1.2 Humidity sensors and biosensors

Due to its hydrophilic properties, PAA is currently used in micro humidity sensors that show good response and are easily fabricated. These devices are based on interdigitated electrodes that take advantage of the sensitive capacitance-humidity relationship [11].

Another interesting characteristic of PAA is its biological properties, and for years, PAA has been used in dental and bone implants due to its biocompatibility and ease of integration with medical implants.

Furthermore, these PAA membranes are now employed as electrochemical biosensors. The membrane acts as a support for enzymes and other biological materials. The sensors shown in Figure 3 have been used to monitor blood glucose levels and for DNA detection [13].

Figure 3: (left) interdigitated capacitor, (right) SEM picture of fingers [13]

# 2.1.3 RF applications

To date, for RF and microwave applications, PAA has been used mainly as an isolation layer in multilevel circuits. In [22] PAA was formed on a glass substrate to produce Multichip Module Deposited (MCM-D) substrates. In this process, they were able to fabricate several interconnecting layers of porous and barrier layers of PAA as shown in Figure 4. The measured resistance of the layer insulation dielectric layer was on the order of  $10^9 \,\Omega$ ·cm much, higher than porous Si [23] at  $10^6 \,\Omega$ ·cm.

Figure 4: (left) Schematic of aluminum anodization substrate process (right) image of four layer substrate [22].

To improve interconnect delays; PAA was used as a low dielectric material for isolation [24]. Here they introduced a CMOS compatible process where a multilayer system of Niobium and aluminum was used. By selectively anodizing areas, an interlevel alumina insulator was fabricated as shown in Figure 5. A dielectric constant of 4.4 and a breakdown voltage of more than 400 V were reported.

Figure 5: SEM cross-section micrograph of multilevel aluminum interconnections with the interlevel porous alumina insulator [24].

## 2.2 PREVIOUS WORK ON INDUCTORS AND SILICON

Before we can summarize the recent work on integrated inductors, it is important to understand the fundamental physics and issues when designing inductors.

#### 2.2.1 Model

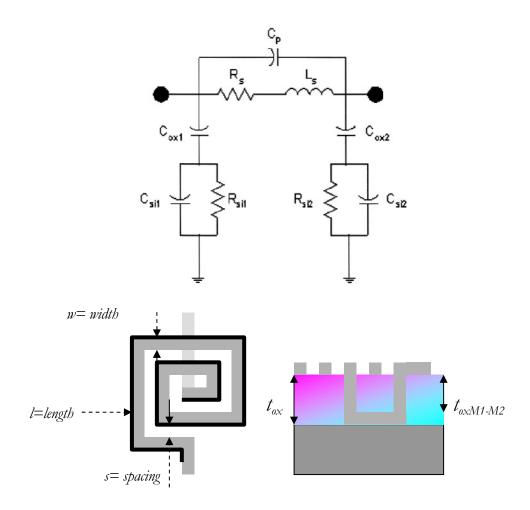

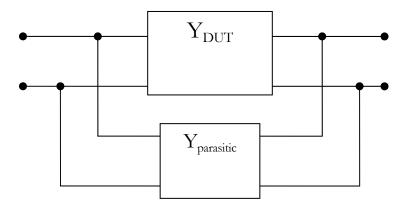

The most common lumped model is the  $\Pi$  model shown in Figure 6. While it is simple and can easily fit empirical data, it is useful for only a narrow frequency band [14].

Figure 6: (top) Two Port  $\Pi$  model [14] (bottom) schematic of typical inductor

The model is made up of ideal resistors, inductors and capacitors. These elements are summarized in Table 1.

|             | Equation                                     | Relation                                                                                                                                                                                                                                                                                                                                                                           |

|-------------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $C_p$       | $\frac{nw^2\varepsilon_{ox}}{t_{oxM_1-M_2}}$ | Capacitance between the underpass and overpass metal strips. This value is normally negligible. $n = \text{number of crossing between the coil and central lower connection}$ $w = \text{width}$ $\epsilon_{\text{ox}} = \text{oxide dielectric constant}$ $t_{\text{oxM1-M2}} = \text{oxide depth between the spiral tracks and its central interconnection}$                     |

| $L_{\rm s}$ | $n^2 \mu \frac{wt}{l}$                       | Inductance of the coil  n = number of turns  \( \mu = \text{ permeability of the metal} \)  w = width  t = depth of metal strip  l = length of spiral                                                                                                                                                                                                                              |

| $R_{\rm s}$ | $rac{ ho l}{w\delta [1-e^{t/\delta}]}$      | Inductor resistance. Accounting for ohmic losses due to the metal resistance, induced effects in the metallic conductor and magnetic induced currents in the substrate. $w = \text{width}$ $t = \text{depth of metal strip}$ $t = \text{length of spiral}$ $t = \text{spiral}$ |

| $C_{ox}$    | $\frac{lw\varepsilon_{ox}}{2t_{ox}}$         | Parasitic capacitance between metal of the coil and substrate $w = \text{width}$ , $l = \text{length of spiral}$ $t_{ax} = \text{depth of oxide}$ , $\epsilon_{ox} = \text{oxide dielectric constant}$                                                                                                                                                                             |

| $R_{si}$    | $\frac{2}{lwG_{sub}}$                        | Resistivity caused by the ohmic losses in the silicon substrate $G_{\text{sub}}$ = substrate conductance per unit area                                                                                                                                                                                                                                                             |

| $C_{si}$    | $\frac{lwC_{sub}}{2}$                        | Capacitance effect of the substrate due to the silicon substrate characteristics $C_{\text{sub}} = \text{substrate}$ capacitance per unit area                                                                                                                                                                                                                                     |

Table 1: Summary of equations and parameter effects in the  $\Pi$  model (Aguilera)

# 2.2.1.1 Inductance

There are two components that makeup the inductance of an inductor: self ( $L_{self}$ ) and mutual inductance (M).

The self inductance of a rectangular conductor as derived by Grover [15] is given by:

$$L_{self} = 2l \left\{ \ln \frac{2l}{w+t} + 0.5 + \frac{w+t}{3l} \right\}$$

(2.1)

Where  $L_{self}$  is measured in nH, and l is the length, w is the width and t is the thickness of the conductor in cm.

The mutual inductance is defined as the ratio between the flux generated by one circuit crossing another circuit. Mutual inductance is positive when the current in two parallel lines is in the same direction and negative when they run in the opposite direction. The mutual inductance is zero when two lines run orthogonal to each other. This is represented by:

$$M = 2lQ (2.2)$$

$$Q = \ln \left\{ \left( \frac{l}{GMD} \right) + \left[ 1 + \frac{l^2}{GMD^2} \right]^{1/2} \right\} - \left\{ 1 + \frac{GMD^2}{l^2} \right\}^{1/2} + \left[ \frac{GMD}{l} \right]$$

(2.3)

$$\ln GMD = \ln d - \frac{w^2}{12d^2} - \frac{w^4}{60d^4} - \frac{w^6}{168d^6} - \frac{w^8}{360d^8} - \dots$$

(2.4)

The GMD is the geometric average of the distance between two areas of the two conductors, where w and d represent the width and distance, center to center between the two conductors.

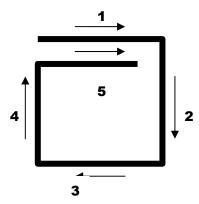

As an example, if we look at the inductor in Figure 7, we can summarize the total inductance given by Greenhouse [16] as:

$$L_{total} = \sum_{self} L_{self} + \sum_{self} M_{+} + \sum_{self} M_{-}$$

$$L_{total} = L_{1} + L_{2} + L_{3} + L_{4} + L_{5} + 2M_{1,5} - 2(M_{1,3} + M_{2,4} + M_{3,5})$$

(2.5)

Figure 7: Schematic of coil to demonstrate self and mutual inductance

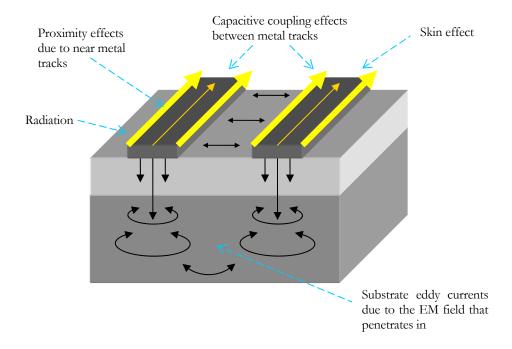

The  $\Pi$  model can give a better understanding of the inductor performance and pinpoint any integration challenges. From the equations in Table 1, it is obvious that the choice of substrate and metals can have a major influence on the performance. To improve upon the device, the path for any potential losses must be understood. These loss mechanisms are shown in Figure 8.

Figure 8: Loss mechanisms for Inductors

These losses and their physical origins will be explained below.

#### 2.2.1.2 Metal losses

Passive elements in CMOS make use of the many metallization layers. For example, a typical inductor is made up of one metal layer parallel to lower tracks of concentric turns, eventually making a full coil. The quality is determined by the conductivity of the metal. At

high frequencies, the current is no longer uniform due to skin and proximity effects. As you increase the frequency, the effective area which the current circulates is decreased. This in turn, increases the current density, creating losses due to the Joule effect [14].

Due to the geometry of the inductor, the alternating magnetic fields penetrate the conductor and create opposing electric fields. This increases the resistivity in the inner section of the inductor, so that the current will likely travel in the outer layer of the conductor. When the time varying magnetic field induces eddy currents in the conductor, this is called "the skin effect". When the time varying fields are produced by neighboring conductors and then influence the main conductor, this is called "the proximity effect".

An important factor that influences these eddy currents is the skin depth  $(\delta)$

$$S = \sqrt{\frac{\rho}{\pi \mu f}} \tag{2.6}$$

Where  $\rho$  is the resistivity,  $\mu$  is the permeability and f is the frequency. When the metal traces are thicker than the skin depth, the eddy current become negligible. For example, for aluminum with  $\sigma$ = 3.72 x 10<sup>7</sup> S/m, the skin depth is 1.84  $\mu$ m at 2 GHz and 0.824 $\mu$ m at 10 GHz [17]. For gold, with  $\sigma$ = 4.55 x 10<sup>7</sup> S/m the skin depth is 1.51  $\mu$ m at 2 GHz and 0.675 $\mu$ m at 10 GHz.

## 2.2.1.3 Capacitance Losses

As well as the resistance effects of the metal tracks, the capacitance between the metal tracks and the capacitance between the metal and the substrate must be examined.

The series capacitance  $C_s$  represents two types of capacitance at work: the first is among and between the metal tracks of the coil (Figure 9), and second is between the coil and the substrate below (Figure 10).

Figure 9: Schematic representation of the parasitic capacitance between metal turns

Figure 10: Schematic representation of parasitic capacitance between the metal and substrate.

The first parasitic capacitance loss between the metal turns arises from the metal/oxide/metal or in this thesis work, metal/air/metal structure. The crosstalk that occurs can be neglected [14]. The second loss is due to the metal inductor and the silicon

substrate, which acts as a large capacitor. Depending on the capacitance and frequency, some of this inductor energy will be stored in this structure therefore the inductor will begin to behave as a capacitor. This will occur at the resonant frequency ( $f_{res}$ ) and this phenomenon can easily be seen on a Smith chart.

#### 2.2.1.4 Substrate losses

The typical low cost silicon substrate is one the greatest sources of loss due to its high conductivity. The effects of this loss occur (i) between the metal layers and the conductive substrate (ii) by induced currents in the substrate due to the varying magnetic fields from the metal layers that penetrate the substrate.

The inductor generates a magnetic field that penetrates into the substrate. This induces a voltage difference, which then generates a current. The energy of the coil, and corresponding quality factor of the inductor decreases.

#### 2.2.1.5 Parameter Extraction

In order to verify the performance of the inductor design, the inductance (L), quality factor (Q) and resonant frequency ( $f_{res}$ ) must be calculated.

The quality factor is defined as the ratio between the maximum energy stored and the average power dissipated on a duty cycle, or:

$$Q = \frac{\omega W_{\text{max}}}{P_{\text{diss}}} = 2\pi \frac{energy\_stored}{energy\_loss\_in\_one\_oscillation\_cycle}$$

(2.7)

As stated earlier, the resonant frequency occurs when the inductor is in resonance with its parasitic capacitances. The device normally operates below this frequency. In this regime, by combining the terms from the one port  $\Pi$  model shown in Figure 11 [18] the quality factor becomes:

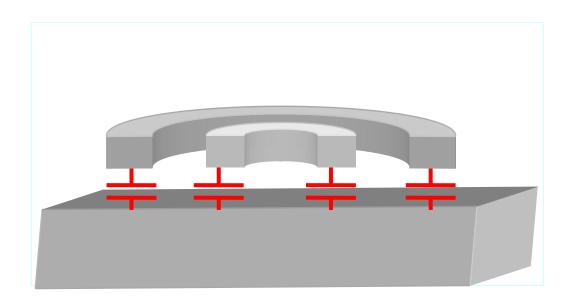

Figure 11: Lumped physical model of a spiral inductor on silicon [18]

$$Q = \left(\frac{\omega L_s}{R_s}\right) \cdot \left(\frac{R_p}{R_p + \left[\left(\frac{\omega L_s}{R_s}\right)^2 + 1\right] \cdot R_s}\right) \cdot \left(1 - \frac{R_s^2 C_o}{L_s} - \omega^2 L_s C_o\right)$$

(2.8)

The first term represents the stored magnetic energy and the ohmic losses in the conducting metal layer. The second term is the substrate loss factor representing the energy lost due to the silicon substrate. The last term is the self resonance factor describing the reduction in the quality factor due to the increase in the peak electric energy with frequency and the reduction of Q at the resonant frequency. Therefore by equating this last term to zero, one can calculate the self resonant frequency or:

$$f_o = \frac{1}{2\pi\sqrt{LC}} \tag{2.9}$$

From Equation (2.9), we see that the spiral inductor has both an inductance and capacitive behaviors.

$L_s$ ,  $R_s$ ,  $R_p$  and  $C_o$  ( $C_o = C_p + C_s$ ) represent the total inductance, the conductor losses, the substrate losses and the total capacitance.

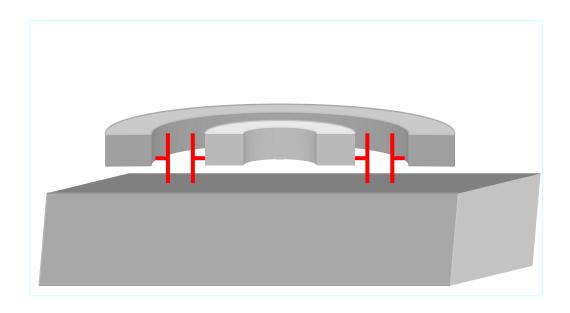

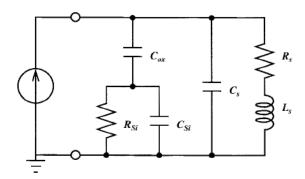

Both  $R_p$  and  $C_p$  which are frequency dependent represent the combined effects of  $C_{ox}$ ,  $C_{si}$  and  $R_{si}$  so that the general model is then simplified as shown in Figure 12. By making this substitution, the analysis of  $R_p$ 's effect on the Q and the extraction of the shunt parasitics from the measured S parameters are simplified.

Figure 12: Equivalent model with combined impedance of  $C_{\text{ox}}, C_{\text{si}}$  and  $R_{\text{si}}$

Then,

$$R_{p} = \frac{1}{\omega^{2} C_{ox}^{2} R_{si}} + \frac{R_{si} (C_{ox} + C_{si})^{2}}{C_{ox}^{2}}$$

(2.10)

and

$$C_{p} = C_{ox} \cdot \frac{1 + \omega^{2} (C_{ox} + C_{si}) C_{si} R_{si}^{2}}{1 + \omega^{2} (C_{ox} + C_{si})^{2} R_{si}^{2}}$$

(2.11)

The L and Q calculations from the S parameters will be further discussed in chapter 4.

#### 2.2.2 Previous Work

There have been several methods introduced in literature with a focus on improving the quality factor of Silicon CMOS based inductors. While silicon CMOS is an attractive high yield low cost production, the conductivity of the substrate remains a problem.

One fairly obvious solution would be to remove the silicon substrate entirely and switch to a more resistive substrate such as quartz, sapphire or high resistive silicon. Unfortunately, this method is not CMOS compatible and the required fabrication costs increase.

This section will summarize some of the most recent methods that have been proposed to improve inductor performance. The first approach is to tackle the substrate itself and explore ways to minimize the loss using standard CMOS planar processes. The second section will look at the MEMS approach using both bulk and micromachining methods.

#### 2.2.2.1 Conventional RFIC Inductors

When an inductor is fabricated on silicon, the substrate is lossy enough to allow the magnetic field of the inductor to penetrate and create eddy currents which work against the inductor. The usual conventional RFIC methods can be categorized as either (i) substrate insulation techniques, or (ii) layout optimization.

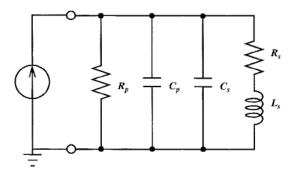

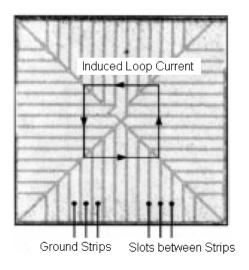

#### **Patterned Ground Plane**

In the patterned ground approach, metal slots, oriented perpendicularly to the spiral inductor are etched in the ground plane [18]. As shown in Figure 13, these act as an open circuit which impedes the path the of the eddy currents that are generated from the inductor. By using this method, the Q improved from 5.08 to 6.76 (33%) at 2 GHz on a 7.5 nH inductor. While this method is compatible with standard CMOS processes, this

does reduce the resonant frequency of the inductor, thereby reducing its operational performance.

Figure 13: Patterned Ground Shield [18]

#### Substrate isolation

In conventional RFIC, an oxide is used a dielectric isolation layer to separate the metal inductor and the lossy silicon substrate. However, good quality oxides require high deposition temperatures, while oxides at lower temperatures exhibit poorer quality and structural issues (such as porosity) [19]. Theoretically, a thicker oxide (50 µm or more) would prove better isolation, yet these thicker films have introduced stress issues. This stress is due to the difference in thermal expansion coefficients (CTE) between the silicon substrate and the oxide [20].

One proposed isolation material is porous silicon formed by electrochemical means. Films of  $54 \mu m$  to  $200 \mu m$  were fabricated and then sealed with a thick PECVD oxide film. This was done in order to seal the open exposed pores and allow for a smoother metal topology. Figure 14 shows a 4.6 nH spiral inductor fabricated on such layers. They show a quality factor of 11.4 at around 13.4 GHz; a nearly 50% increase compared to the same

inductor fabricated on bulk silicon alone [21]. One of the drawbacks of this material is the need to cover the porous silicon with a capping layer to seal it from the ambient. Otherwise, any subsequent layers will not be completely electrically isolated from the substrate.

Figure 14: (left) Cross section of device and (right) extracted Q factor for the inductor [21]

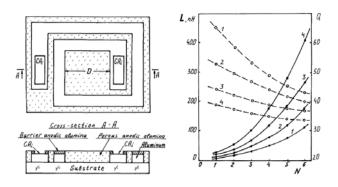

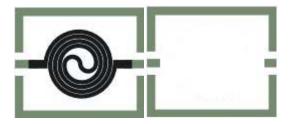

Since anodized aluminum has shown promise in planar interconnection systems for IC, planar inductors and capacitors were fabricated on glass substrates using PAA as an isolation spacer and barrier alumina as a capping layer [25]. A peak quality factor of 60 was reported for a 4 turn 400 nH inductor as shown in Figure 15. However, these low frequency (1 kHz-300 MHz) inductors had an area in the millimeter range (high footprint) and were fabricated on glass substrates, making these incompatible with CMOS processes.

Figure 15: (left) Schematic diagram of the planar inductor (right) Inductance and Q performance as a function of the number of turns [25].

#### **Layout Optimization**

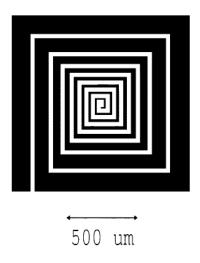

It was determined from [26] that the ohmic losses in a spiral inductor are predominant in the outer turns, while the magnetic losses predominate in the inner turns. An algorithm was used to vary the trace width of the metal from a small width in the inner turns, to larger widths at the outer turns. The layout optimized structure is shown in Figure 16. The Q of these inductors was greater than 40 for a 20 nH at 3.5 GHz, a 60% improvement with respect to the single width inductors operating at the same frequency.

Figure 16: Metal loss-optimized inductor [26].

# 2.2.2.2 RF MEMS Inductors using Bulk or Surface Micromachining

MEMS technology allows the inductors to be either suspended or levitated in air away from the silicon substrate. This increase in distance reduces the eddy current effects. The use of bulk and surface micromachining methods is presented.

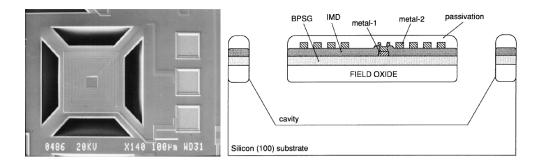

#### **Bulk Micromachining**

In bulk micromachining, the lossy silicon substrate is etched away from underneath the inductor using an anisotropic etchant such as KOH, TMAH or EDP. This allows the inductor to be suspended in mid air reducing the substrate losses and the capacitive coupling of the inductor/substrate. This membrane building technique is implemented in standard 2 µm CMOS processes by [27] and in 0.7 µm CMOS processes [28] as shown in Figure 17. While this technique improves the Q (22 at 270 MHz on a 115 nH inductor) and resonant frequency (100 MHz to 3 GHz) there is an issue of fragility, limitations to subsequent wafer processing and increased complexity in packaging.

Figure 17: (left) Membrane suspended spiral inductor integrated with 0.7um CMOS process (right) Schematic cross section of device [28].

#### **Surface Micromachining**

Though the previous techniques do improve the inductor performance, the remaining parasitic capacitance between the conductive metal and substrate poses limitations [5]. Another approach is to use surface micromachining to build elevated structures away from the substrate. Using a 3D photoresist mould, the structure is electroplated and eventually released as shown in Figure 18. This method resulted in a Q of 16.7 at 2.4 GHz on a 2.67 nH inductor [29]

Figure 18: (left) SEM micrograph of elevated inductor (right) Measured and modeled performance of inductor [29].

## Self Assembly

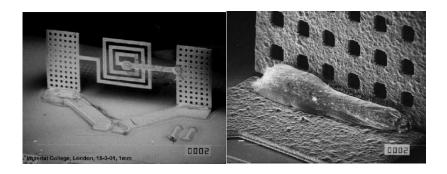

Another method of elevating the inductor from the substrate is to use self assembly techniques. These structures are fabricated using a planar batch process, but with an added meltable hinge pad placed at the substrate anchor and the released section of the device. Once the pads are melted, the surface tension force rotates the inductor out of the substrate plane. Figure 19 shows these out of plane inductors that are perpendicular to the substrate and have improved the Q from 4 at 0.5 GHz (released yet not self assembled), to a peak Q of 17 at 3.5 GHz for the same inductor when self assembled at a 90° angle [30].

Figure 19: (left) Self assembled out of plane spiral inductor (right) view of solder hinge region after self assembly [30].

#### **RF MEMS Tunable Inductor**

Only recently has there been any substantial work done on developing tunable inductors. The benefit of such devices provides optimization and added functionality to many RF components.

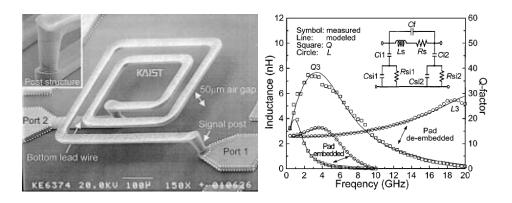

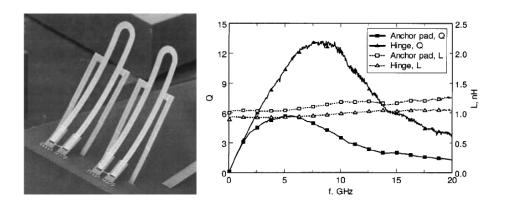

The first such device was proposed by Lubecke [31] who used the PolyMUMPS process to fabricate bimorph structures. The inductor bends away from the substrate by means of an interlayer stress caused by using two materials. In this process, polysilicon and chromium-gold metal layers are used as shown in Figure 20. These devices reached a peak Q of 13 at 9 GHz with an L of 1.2 nH.

Figure 20: (left) SEM micrograph of hinged Self Assembling Inductor (right) Q and L performance [31].

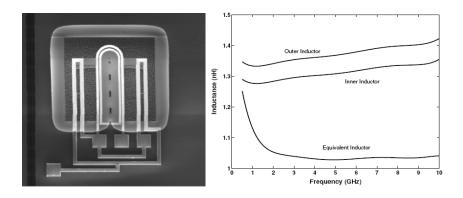

Another tunable inductor presented in [32] is based on the mutual coupling between two coils. In one state, the actuators displace the external coil, reducing the mutual coupling, and in the other state (rest), the coil remains in the closest position to the other coil, creating a higher mutual coupling. By changing the pitch, the coupling can increase or decrease with tuning based on thermal bimorph structures as seen in Figure 21. Similar to bulk micromachining methods, the substrate was removed by XeF2 etch. This device presented a tuning range of 30% with peak quality factor of almost 25 at 7 GHz.

Figure 21: (left) SEM micrograph of tunable inductor (right) measured inductance of the inner and outer coil [32].

More recently a tunable RF MEMS inductor based on amorphous silicon was presented [33]. The bimorph structure of amorphous silicon and aluminum shown in Figure 22 achieved a 32% tuning range with a peak quality factor reaching 15.

Figure 22: (left) SEM micrograph of warped inductor (right) Quality factor performance [33].

The design structure of the RF tunable inductors presented in this thesis is based on the work in [17]. In this work, we will show how PAA can be a lower cost and lower temperature alternative to many of the tunable inductors presented earlier.

### 3.1 POROUS ANODIC ALUMINA FORMATION

aluminum has the natural tendency to oxidize when exposed to the atmosphere. The thickness of this native oxide coating,  $Al_2O_3$ , can be in the submicron range and is generated to protect the metal surface from further reactions. The term "anodic oxidation" or anodization is defined by the electrolytic process or hydrolysis for producing thicker oxide coatings. The process of anodization further enhances the native oxide, creating a thicker, anti-corrosive layer.

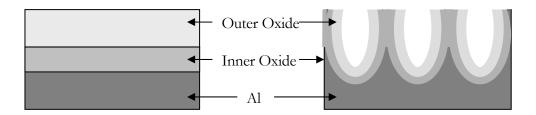

In Figure 23, the two types of anodic films that can be produced are shown: barrier and porous. Barrier type films are formed in insoluble electrolytes (5 < pH < 7) such as a neutral boric acid, ammonium borate, tartrate and ammonium tetraborate in ethylene glycol. To create porous films, slightly soluble electrolytes such as sulfuric, phosphoric, chromic and oxalic acids are used [34].

Both types of film consist of a high purity alumina inner oxide and an outer oxide layer composed of alumina with incorporated anions [35]. The inner oxide is adjacent to the oxide-metal interface, while the outer oxide is adjacent to the electrolyte-oxide interface.

Figure 23: Schematic diagram of (left) barrier type alumina and (right) porous type alumina.

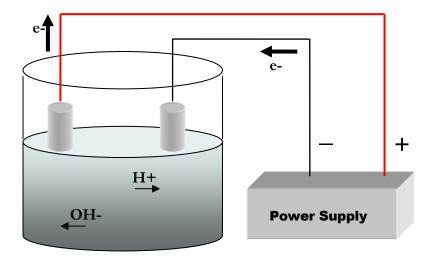

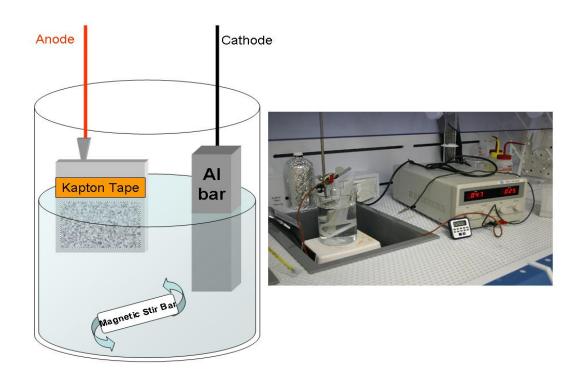

The general principle of electrolysis is as follows: In a bath containing a solution of either a dilute acid or a base (the electrolyte), a cathode of either platinum or any other metal that cannot be dissolved in the solution, is placed with an anode, in this case, aluminum. Figure 24 shows a common anodic cell setup. If one chooses the anode to be made of copper, it would dissolve in the solution and redeposit on the cathode (the basis of electroplating).

Figure 24: Anodic Cell

Once a voltage or current is applied and the circuit is closed, electrons are withdrawn from the positive terminal. The applied current sets up an electrostatic field in the native oxide. This allows the oxygen ions in the solution to be pulled through the film and react with the metal surface to form the aluminum oxide. At the cathode end, the electrons return to the solution where they react with the hydrogen ions. This causes the formation of hydrogen gas.

This reaction is defined by 3 equations.

Overall Reaction:

$$2Al + 3O_2 \rightarrow Al_2O_3 + 3H_2$$

(3.1)

Reaction at Anode:

$$2Al + 3O_2 \rightarrow Al_2O_3 + 6e$$

-

(3.2)

Reaction at Cathode:

$$6H + +6e \rightarrow 3H_2$$

(3.3)

The first reaction contributes most of the anodic current, while the remaining equations relate to the growth of the aluminum oxide film with hydrogen gas generated as a by product.

In electrochemistry, the Nernst equation describes the equilibrium reduction potential of a half cell in an electrochemical cell. Assuming there are no complex anions, the Nernst half cell reduction potential equation is:

$$E_{red} = E^{o} - \frac{RT}{zF} \ln(\frac{{}^{a} \operatorname{Re} \, duction}{{}^{a} Oxidation})$$

(3.4)

Where R is the universal gas constant, T is the absolute temperature in Kelvin, z is the charge number of the electrode reaction, and F is Faraday's constant.

Solving for equation (3.4), the potential E at the anode becomes:

$$E = -1.550 - 0.0591pH \tag{3.5}$$

Equation (3.5) shows that the reaction that occurs at the anode is thermodynamically dependent on the pH of the solution. By changing the pH, the pore size can vary.

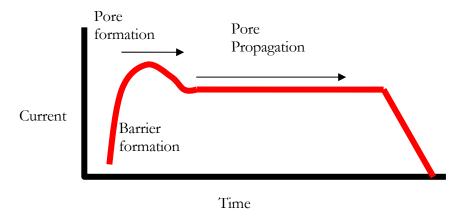

Figure 25 shows the typical voltage time characteristic during a constant voltage anodization. During the first few seconds, a barrier layer is formed on top of the aluminum film. As time continues, the pores begin to develop on top of the barrier layer. The diameters of the pores increase until they are crowded against each other. Once this competition is complete, the pore depths increase and propagate downward and a steady state current is reached. As the aluminum is consumed, the current drops to nearly zero and the anodization is complete.

Figure 25: A typical experimental current time characteristic during a constant voltage anodization

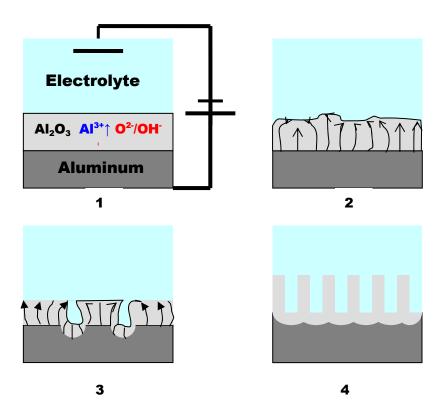

The pore formation is shown in Figure 26. Initially, a barrier of protective oxide covers the entire aluminum surface. Once the voltage is applied, an electric field is locally focused on the surface. This is followed by field enhanced dissolution of the formed oxide. Subsequently, the pores continue to grow until they begin to compete with each others surrounding areas. The pore growth will continue to expand in the vertical direction. This will continue until all of the conductive aluminum is consumed.

Figure 26: Schematic diagram of the pore formation. (1) formation of barrier oxide over entire surface, (2) local field distributions caused by surface fluctuations (3) initial stages of pore creation cause by dissolution (4) stable and steady pore growth

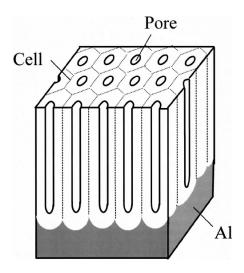

As aluminum is oxidized, the volume of the aluminum oxide also expands by roughly a factor of 1.4-1.6 of its original thickness. Since this process takes place over the entire metal/oxide interface, the newly created material can only expand in the vertical direction. The geometry of PAA can be described as a honeycomb structure with a high aspect ratio. The cells are shown in Figure 27 and are arranged in a hexagonal array of column-like pores. However, this array is non uniform and randomly spaced [36].

Figure 27: Schematic drawing of an idealized hexagonal PAA structure [36].

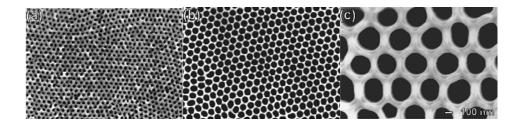

The pore and cell diameters are dependent on the choice of electrolyte and its pH value. Pore diameters ranging from 4 nm to over 400 nm as shown in Figure 28, have been fabricated [9, 37]. Some researchers have also been able to develop a more uniform and self organized packing system by using nano-imprinting or two step anodization.

Figure 28: SEM micrographs of PAA. (a) 0.3M sulfuric acid at 25V (b) 0.3M oxalic acid at 40V (c) 10 wt% phosphoric acid at 160V. The pore diameters are 60, 95 and 420nm respectively [9].

Generally, there are several process conditions that can affect the material and electrical properties of the film:

Choice of Electrolyte: Typical electrolyte solutions are dilute sulfuric acid, oxalic acid and

phosphoric acid. As the pH of the electrolyte increases, the applied voltage increases. a

circulating cooling bath is often incorporated into the experimental setup as this increase

in voltage will also increase the temperature of the solution.

Typically, electrolyte solutions containing sulfuric acid generate the smallest pore

diameters; on the order of 50-70 nm with phosphoric acid give a pore diameter of 420 nm

or higher.

By changing the pore size, the dielectric constant can be either as low as 1 (with a high

porosity), or as high as 10 (with a low, more dense porosity).

**Temperature:** Changing the temperature of the electrolyte solution will affect the stress

and surface roughness. During anodization, there is an excessive amount of heat that is

generated. Without adequate cooling, this heat will cause stress in the film and cracks will

develop, with the film eventually peeling and falling off of the underlying aluminum film.

**Voltage:** The applied voltage to the sample can change the desired pore diameter.

35

# 3.2 FILM CHARACTERIZATION

Once the anodization process was developed, the film characteristics, both physical and electrical were investigated and summarized. Some of these values are verified in this work, while others are referenced.

# 3.2.1 Surface Roughness of PAA Film

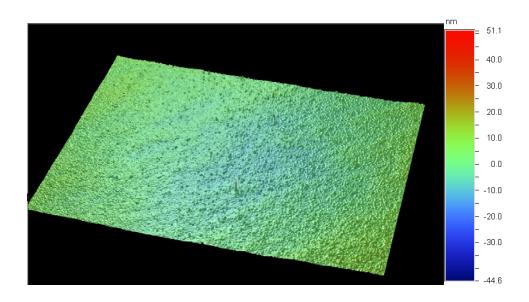

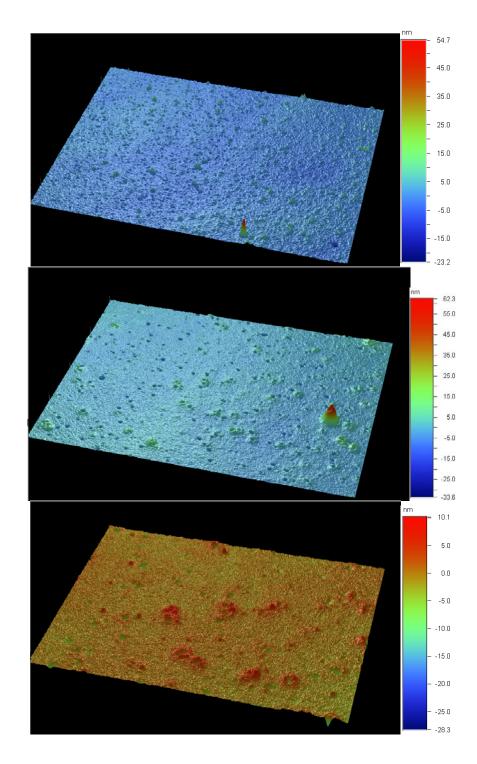

Films of 1  $\mu$ m and 2  $\mu$ m PAA were anodized on glass wafers. To measure the surface roughness of the film, a Veeco optical profiler was used to calculate the average roughness and is shown in Figure 29 and Figure 30.

Figure 29: Surface Roughness of  $1\mu m$  PAA (top) at 5x magnification

Figure 30: Surface Roughness of  $1\mu m$  PAA (top) at 10X magnification, (middle) 50X magnification, (bottom) 100X magnification

The profiler can measure the average roughness of the PAA film over a certain area. For a  $45 \times 59 \ \mu\text{m}^2$  area, the average roughness was 1.30 nm at 100X magnification. As seen in the middle and bottom of Figure 30, at these magnifications the pores of the PAA are clearly visible.

# 3.2.2 Maximum deflection

In order to verify PAA as a viable structural material for MEMS production, several test structures were fabricated. Bimorph cantilever beams of varying lengths were made and the deflection was measured.

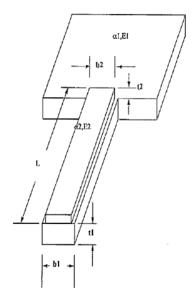

For a bimorph cantilever beam as in Figure 31, the radius of curvature can be calculated as [38]:

$$\frac{1}{r} = \frac{6b_1b_2E_1E_2t_1t_2(t_1+t_2)(\alpha_1-\alpha_2)\Delta T}{(b_1E_1t_1^2)^2 + (b_2E_2t_2^2)^2 + 2b_1b_2E_1E_2t_1t_2(2t_1^2 + 3t_1t_2 + 2t_2^2)}$$

(3.6)

Where b is the width, t is the thickness,  $\alpha$  is the coefficient of thermal expansion, E is Young's modulus and  $\Delta T$  is the temperature change. The subscript 1 and 2 refer to the top and bottom layers respectively.

Figure 31: Schematic of a bimorph cantilever beam [38].

Since the materials used in this thesis have a Young's moduli on the same magnitude, we can simplify the above equation to:

$$\frac{1}{r} = \frac{3\Delta\alpha\Delta T}{8t} \tag{3.7}$$

Where  $\Delta\alpha$  is the difference in the coefficient of thermal expansion and t is the total thickness of both layers in the beam.

The vertical tip deflection is

$$d = \frac{l^2}{2r} \tag{3.8}$$

Where l is the free deflection length. If l << r, then the equation for the deflection becomes:

$$d = \frac{3l^2 \Delta \alpha \Delta T}{16t} \tag{3.9}$$

From the above equation, we can see that in order to maximize the tip deflection, the  $\Delta\alpha$  and the  $\Delta T$  must be large. Using the structure in Figure 32, the tip deflection of various structures as a function of  $\Delta T$  was calculated.

Figure 32: Schematic of the bimorph cantilever beams

From the values listed in Table 2, it is obvious that a bimorph structure of aluminum and PAA will give a higher deflection than gold and PAA. However, the excellent conductivity properties of gold are attractive to many RF applications.

| Material | Coefficient of thermal | Maximum Tip deflection |  |

|----------|------------------------|------------------------|--|

|          | Expansion (1/K)        |                        |  |

| gold     | 14 x 10 <sup>-6</sup>  | 0.027 ΔΤ               |  |

| PAA      | 6.8 x 10 <sup>-6</sup> | ]                      |  |

| aluminum | 25 x 10 <sup>-6</sup>  | 0.068 ΔΤ               |  |

| PAA      | 6.8 x 10 <sup>-6</sup> |                        |  |

Table 2: Calculated tip deflection for bimorph cantilever beams

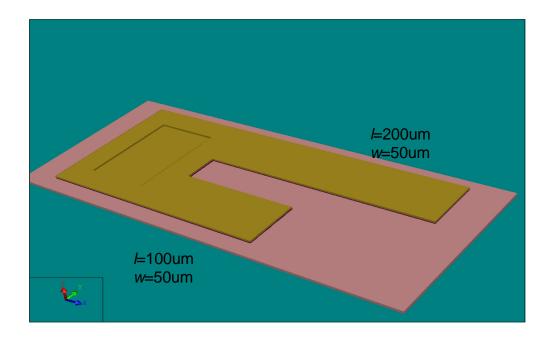

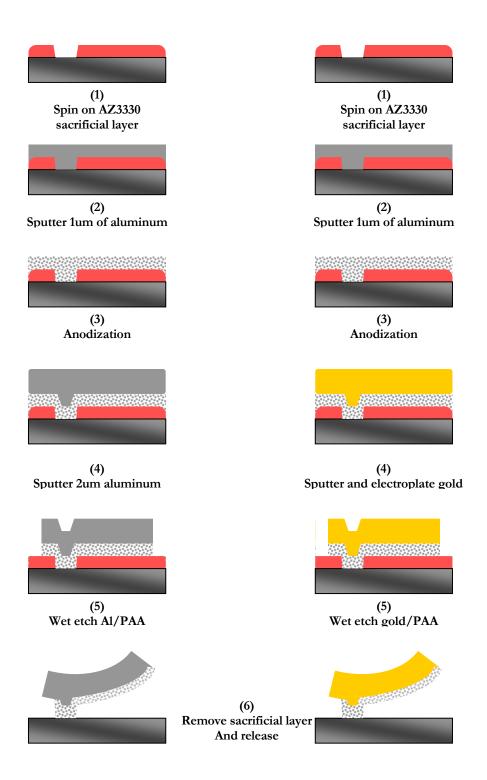

To verify these conditions, bimorph structures were fabricated in the process in Figure 33. After the p-type <100> 8-12  $\Omega$ ·cm silicon wafer was cleaned using a standard RCA-1 recipe, it was then coated with a 2  $\mu$ m photoresist sacrificial layer. The anchors were then patterned and after hard baking to prevent any further outgassing, 1 $\mu$ m of aluminum was sputtered. The maximum temperature inside the sputtering chamber reached almost 70°C. The aluminum film was then anodized in a 0.3M oxalic acid solution for 5 minutes or until the film became transparent. For the aluminum/PAA bimorph structures, another 2  $\mu$ m of aluminum was sputtered. For the gold/PAA bimorph structures, a thin 100 nm layer of gold was sputtered, followed by another 2  $\mu$ m of electroplated gold. The top layer for both substrates was patterned and etched, followed by the etching of the PAA. To remove the sacrificial layer, Reactive Ion Etching (RIE) was used to release the beams. Due to the residual stress in the layers, the beams are warped upwards after release.

Figure 33: Fabrication steps for (left) aluminum/PAA and (right) gold/PAA bimorph cantilever beams

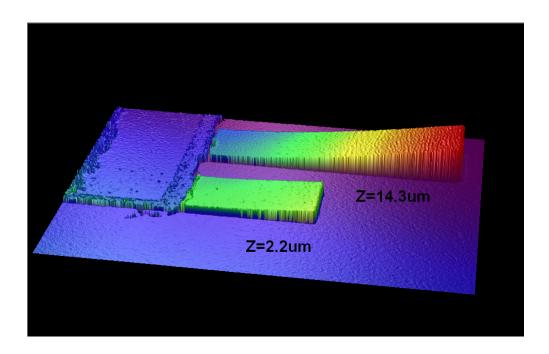

The tip deflection and curvature were measured using a Veeco optical profiler as shown in Figure 34. As was predicted earlier, the aluminum and PAA structures produced the highest deflection as shown in Table 3.

Figure 34: Micrograph of gold/PAA Bimorph Cantilever beams

| Structure    | Length (µm) | Maximum Tip     | Radius of Curvature |

|--------------|-------------|-----------------|---------------------|

|              |             | Deflection (µm) | (mm)                |

| gold/PAA     | 182.8       | 14.3            | 1.44                |

| aluminum/PAA | 186.1       | 19.1            | 1.69                |

Table 3: Optical Profiler measurements for fabricated bimorph cantilever beams

#### 3.2.3 Dielectric Constant and Stress of PAA Films

Although the chemical makeup of PAA is similar to the more common aluminum oxide, the structure is more of a porous nature than a crystalline arrangement. PAA is constructed of pillars of alumina with air filled pores. Due to this porosity, the dielectric constant of this material can be estimated as a mixture of  $\varepsilon_{Alumina}$ = 9.9 and  $\varepsilon_{Air}$ = 1.0. By varying the diameter of the pore cell, the dielectric constant of PAA can vary between these two values.

While there are several methods of measuring the dielectric constant, it is still one of the most difficult properties to accurately deduce. A summary of published dielectric constants is shown in Table 4. It is evident that by simply varying the anodization conditions, the dielectric constant is tunable to any specific application. The two most popular methods of calculating the dielectric constant are summarized below.

| Dielectric<br>Constant | Electrolyte                                | Voltage or<br>Current<br>Density | Thickness | Pore<br>Diameter<br>(nm) | Pore Spacing (nm) | Porosity | Method of<br>Measurement            | Source |

|------------------------|--------------------------------------------|----------------------------------|-----------|--------------------------|-------------------|----------|-------------------------------------|--------|

| 1.98-2.02              | 20% sulfuric acid                          | 15, 20, 30<br>mA/cm <sup>2</sup> | 0.2 μm    |                          |                   | 77%      | Capacitor-Voltage                   | [39]   |

| 7.2                    | 0.3M oxalic acid                           | 40V                              |           | 50                       | 100               | 23%      | unknown                             | [41]   |

| 4.4                    | 1 M sulfuric acid + 2 M<br>phosphoric acid | 10V                              | 0.5 μm    |                          |                   | 75%      | Ellipsometry                        | [24]   |

| 6.5                    | 10 wt% sulfuric acid                       | 20V                              | 100 nm    | 16                       |                   |          | Capacitor-Voltage                   | [48]   |

| 10.5                   | boric acid/ ammonium<br>hydroxide          | 1 mA/cm <sup>2</sup>             |           |                          |                   |          | Capacitor-Voltage  And Ellipsometry | [13]   |

Table 4: Summary of reported PAA

# 3.2.3.1 Capacitance-Voltage (CV) Characterization

In this method, metal-insulator-semiconductor (MIS) structures are fabricated to determine carrier density, threshold voltage and flatband voltage [39]. Since the capacitance  $C_0$  is determined by the properties of the dielectric or insulating layer, this device can be used to measure the dielectric constant of PAA by:

$$\varepsilon = \frac{C_o t_{ox}}{\varepsilon_o A} \tag{3.10}$$

Where  $C_o$  is the oxide capacitance (F),  $t_{ox}$  is the oxide thickness (m), and A is the area of the top contact (m<sup>2</sup>).

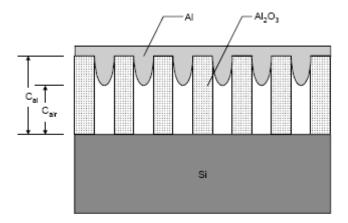

However, as Das et al. had shown, measured capacitance is combination of the capacitance of the air filled pores plus the capacitance of aluminum oxide, or

$$C_o = C_{air} + C_{alox} (3.11)$$

They found that as the pore size increase (larger volume of air filled holes versus aluminum oxide) would see a decrease in the overall dielectric constant. However, by widening the pore diameter, this allowed the top metal contact to partially fill the pores as seen in Figure 35.

Figure 35: Schematic cross section of Al/Alumina/p-Si capacitors [39]

This method was initially used to calculate the dielectric constant of the PAA in this work; however the results were found to be inconclusive.

# 3.2.3.2 Ellipsometry

A non destructive method that can be used to measure the dielectric constant is to use optical means. Ellipsometry is used to study thin films on solid substrates. By measuring the reflected elliptically polarized light, the film thickness and index of refraction can be solved.

To date, the Maxwell-Garnett model is used to represent a good approximation of the complex structure of PAA [40]. If we assume that  $\varepsilon_{Alox}$ =9.9, then the effective dielectric constant is given by:

$$\varepsilon_{eff} = \frac{\varepsilon_{air} + 2\varepsilon_{Alox} + 2f(\varepsilon_{air} - \varepsilon_{Alox})}{\varepsilon_{air} + 2\varepsilon_{Alox} - f(\varepsilon_{air} - \varepsilon_{Alox})}$$

(3.12)

Where f is the filling fraction of air, in this case equal to the porosity p. The porosity p of the hexagonal cell structure is given by:

$$p = \frac{\pi}{2\sqrt{3}} \left(\frac{D}{D_{\text{int}}}\right)^2 \tag{3.13}$$

Table 5 shows the results of the above calculations and the measured results from the ellipsometer.

| Interpore<br>Distance<br>D <sub>int</sub> (nm) | Pore Diameter<br>D(nm) | Porosity | ε <sub>eff</sub><br>(Model) | ε <sub>eff</sub><br>(Ellipsometry) |

|------------------------------------------------|------------------------|----------|-----------------------------|------------------------------------|

| 100                                            | 50                     | 0.2267   | 7.27                        | 3.72                               |

Table 5: Results from Model and Ellipsometry Calculations

As shown, there is still a wide discrepancy from these measurements. However, since the PAA in this thesis has a low porosity, it is safe to assume that the effective dielectric constant that was calculated from the model is the most accurate. The dielectric constant measured from the model shows good agreement with the one reported by Delendrik [41] that used the same anodization conditions as in this work.

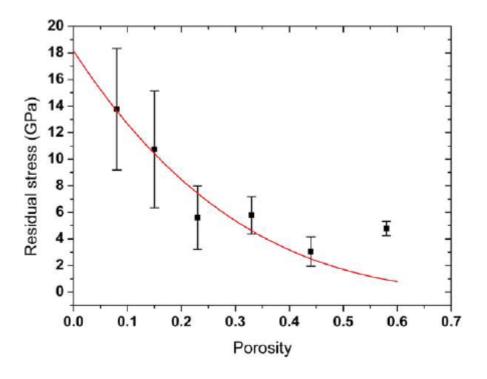

As with the dielectric constant, the value of the stress depends on the porosity of the PAA film. In [42], the mechanical properties and residual stress in PAA films are investigated using nano indentation tests. The relationship between the pore size and the porosity is shown in Table 6 and shows good agreement with the model previously presented. It was found that the Young's modulus and the hardness of the structure decreased as the size of the pores increased. This is expected since the composition of the material shifts from a solid to a more porous state. As seen in Figure 36, the residual stress decreases as the porosity increases. Based on the fabrication of the PAA film presented in this thesis, the

Young's modulus is 137-141 GPa [41, 42] and the residual stress is approximately 600 MPa.

| Hole diameter of specimens (nm) | Porosity (nm) |

|---------------------------------|---------------|

| 30                              | 8             |

| 40                              | 15            |

| 50                              | 23            |

| 60                              | 33            |

| 70                              | 44            |

| 80                              | 58            |

Table 6: Hole diameter and porosity

Figure 36: Residual stress as a function of porosity [42]

# 3.3 Film Fabrication and setup