# Verification of Pipelined Ciphers

by

## Chiu Hong Lam

A thesis

presented to the University of Waterloo

in fulfillment of the

thesis requirement for the degree of

Master of Applied Science

in

Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2008

© Chiu Hong Lam 2008

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### Abstract

The purpose of this thesis is to explore the formal verification technique of completion functions and equivalence checking by verifying two pipelined cryptographic circuits, KASUMI and WG ciphers.

Most of current methods of communications either involve a personal computer or a mobile phone. To ensure that the information is exchanged in a secure manner, encryption circuits are used to transform the information into an unintelligible form. To be highly secure, this type of circuits is generally designed such that it is hard to analyze. Due to this fact, it becomes hard to locate a design error in the verification of cryptographic circuits. Therefore, cryptographic circuits pose significant challenges in the area of formal verification.

Formal verification use mathematics to formulate correctness criteria of designs, to develop mathematical models of designs, and to verify designs against their correctness criteria.

The results of this work can extend the existing collection of verification methods as well as benefiting the area of cryptography. In this thesis, we implemented the KASUMI cipher in VHDL, and we applied the optimization technique of pipelining to create three additional implementations of KASUMI. We verified the three pipelined implementations of KASUMI with completion functions and equivalence checking. During the verification of KASUMI, we developed a methodology to handle the completion functions efficiently based on VHDL generic parameters. We implemented the WG cipher in VHDL, and we applied the optimization techniques of pipelining and hardware re-use to create an optimized implementation of WG. We verified the optimized implementation of WG with completion functions and equivalence checking. During the verification of WG, we developed the methodology of "skipping" that can decrease the number of verification obligations required to verify the correctness of a circuit. During the verification of WG, we developed a way of applying the completion functions approach such that it can deal with a circuit that has been optimized with hardware re-use.

#### Acknowledgements

I would like to thank my MASc supervisor, Dr. Mark Aagaard, for his guidance and support from the beginning to the end of this research. I would like to thank Dr. Guang Gong and Dr. Anwar Hasan for their suggestions that have improved the quality of this thesis. I would like to thank my fellow researchers at the Waterloo Formal Methods Group, Vlad Ciubotariu and Hazem Shehata, for their assistance in the submission of this thesis. Finally, I would like to thank Ontario Graduate Scholarship (OGS) program for their support in this research.

$To\ wing L$

# Contents

| Li | st of | Tables                                                   | viii |

|----|-------|----------------------------------------------------------|------|

| Li | st of | Figures                                                  | xi   |

| 1  | Intr  | roduction                                                | 1    |

|    | 1.1   | Overview of Background                                   | 2    |

|    | 1.2   | Thesis Outline                                           | 3    |

| 2  | Bac   | ekground Materials                                       | 4    |

|    | 2.1   | Burch-Dill Flushing                                      | 4    |

|    | 2.2   | Completion Functions                                     | 7    |

|    | 2.3   | The Basics of Cryptography                               | 11   |

|    | 2.4   | The KASUMI Cipher                                        | 12   |

|    | 2.5   | Algebraic Terminology for Finite Fields and Normal Basis | 15   |

|    | 2.6   | The Welch-Gong Cipher                                    | 16   |

| 3  | KA    | SUMI: Design, Optimizations and Verification             | 21   |

|    | 3.1   | The First Design                                         | 21   |

|    | 3.2   | Formulating The Specification                            | 22   |

|    | 3.3   | Pipelined Implementations                                | 26   |

|    | 3.4   | Verification Methodology                                 | 28   |

|    |       | 3.4.1 General Guidelines                                 | 28   |

|    |       | 3.4.2 Background of VHDL Features                        | 33   |

|   |     | 3.4.3   | Single Entity Environment                           | 34 |

|---|-----|---------|-----------------------------------------------------|----|

|   |     | 3.4.4   | Multiple Entities Environment                       | 35 |

|   | 3.5 | Verific | eation of KASUMI                                    | 38 |

| 4 | WG  | : Desi  | gn and Optimizations                                | 43 |

|   | 4.1 | The F   | first Design                                        | 43 |

|   |     | 4.1.1   | WG Core and Trace Function                          | 44 |

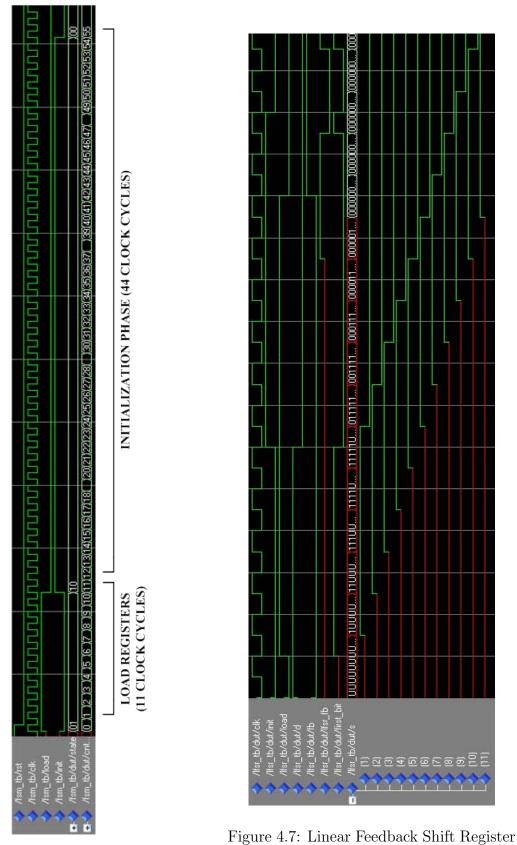

|   |     | 4.1.2   | Linear Feedback Shift Register                      | 46 |

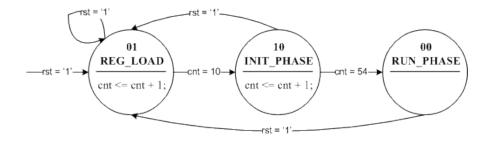

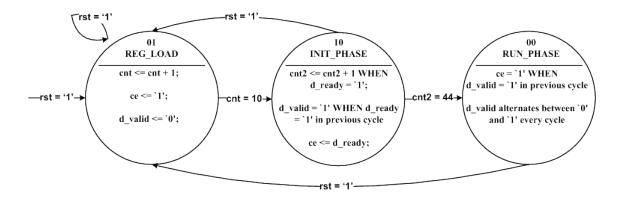

|   |     | 4.1.3   | Finite State Machine                                | 47 |

|   | 4.2 | Formu   | lating The Specification                            | 48 |

|   |     | 4.2.1   | Finite State Machine                                | 50 |

|   |     | 4.2.2   | Linear Feedback Shift Register                      | 50 |

|   |     | 4.2.3   | Trace Function and WG Core                          | 52 |

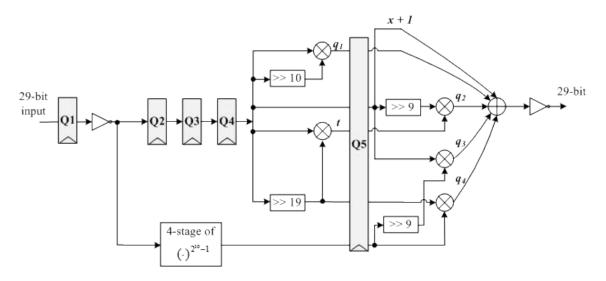

|   | 4.3 | The C   | Optimized Implementation                            | 53 |

|   |     | 4.3.1   | Pipelining                                          | 53 |

|   |     | 4.3.2   | Hardware Re-Use                                     | 55 |

|   |     | 4.3.3   | Control Circuitry Modifications                     | 64 |

|   | 4.4 | Relate  | ed Work                                             | 66 |

| 5 | WG  | : Veri  | fication                                            | 70 |

|   | 5.1 | The V   | VG Core                                             | 70 |

|   |     | 5.1.1   | First Verification: The Normal Basis Multiplier     | 71 |

|   |     | 5.1.2   | Second Verification: The $(\cdot)^{2^{10}-1}$ Block | 72 |

|   |     | 5.1.3   | Third Verification: The WG Core                     | 76 |

|   | 5.2 | The L   | inear Feedback Shift Register                       | 82 |

|   | 5.3 | The F   | inite State Machine                                 | 84 |

|   |     | 5.3.1   | Background of Model Checking                        | 84 |

|   |     | 5.3.2   | The Verification                                    | 85 |

|   | 5 1 | Dolata  | ad Work                                             | 00 |

| 6  | Conclusions and Future Work | 90 |

|----|-----------------------------|----|

| Re | eferences                   | 91 |

# List of Tables

| 4.1 | Signal Selected Based on load and init | 46 |

|-----|----------------------------------------|----|

| 5.1 | Semantics of Temporal Modal Operators  | 85 |

| 5.2 | First Set of Properties Verified       | 86 |

| 5.3 | Semantics of Additional Operators      | 86 |

| 5.4 | Second Set of Properties Verified      | 87 |

| 5.5 | Third Set of Properties Verified       | 87 |

# List of Figures

| 2.1  | Specification                                        | 5 |

|------|------------------------------------------------------|---|

| 2.2  | Pipelined Implementation                             | 5 |

| 2.3  | Difficulty in The Verification of Pipelined Circuits | 6 |

| 2.4  | Burch-Dill Flushing                                  | 8 |

| 2.5  | Flushing Example                                     | 8 |

| 2.6  | Completion Functions                                 | 9 |

| 2.7  | Completion Functions Example                         | 9 |

| 2.8  | Block Ciphers                                        | 2 |

| 2.9  | Stream Ciphers                                       | 2 |

| 2.10 | KASUMI Circuit                                       | 4 |

| 2.11 | FO Circuit                                           | 4 |

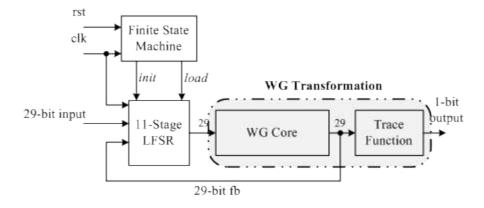

| 2.12 | WG Family Circuit Structure                          | 7 |

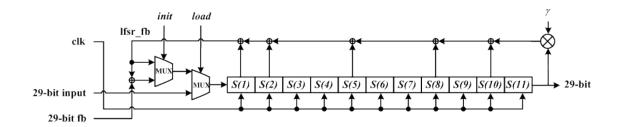

| 2.13 | LFSR Feedback Polynomial                             | 8 |

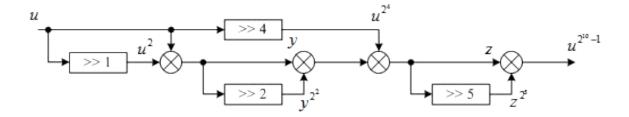

| 2.14 | Implementation of WG Transformation                  | 9 |

| 2.15 | Key Initialization Phase                             | 0 |

| 3.1  | FI Test Vectors Results                              | 3 |

| 3.2  | Fragments of Test Vectors from KASUMI Specification  | 4 |

| 3.3  | FO Test Vectors Results                              | 4 |

| 3.4  | FL Test Vectors Results                              | 4 |

| 3.5  | KASUMI Test Vectors Results                          | 5 |

| 3.6  | Registers Locations in KASUMI                        | 7 |

| 3.7  | Registers Locations in FO                              | 27 |

|------|--------------------------------------------------------|----|

| 3.8  | Area and Performance Results of Various KASUMI Designs | 29 |

| 3.9  | 2-Stage Pipeline Verification Structure                | 31 |

| 3.10 | First Verification Obligation                          | 31 |

| 3.11 | Second Verification Obligation                         | 32 |

| 3.12 | Third Verification Obligation                          | 32 |

| 3.13 | If-Generate Statement                                  | 33 |

| 3.14 | Generic Parameters                                     | 34 |

| 3.15 | Entity A: VHDL Code                                    | 36 |

| 3.16 | Contrived Entity A With Completion Functions           | 36 |

| 3.17 | Contrived Entity D                                     | 37 |

| 3.18 | Stage 8 Obligation                                     | 39 |

| 3.19 | Stage 7 Obligation                                     | 39 |

| 3.20 | Stage 1 Obligation                                     | 41 |

| 3.21 | Final Obligation                                       | 41 |

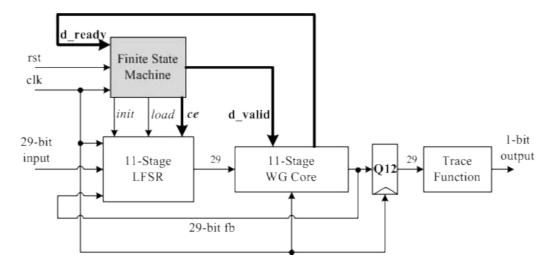

| 4.1  | WG Implementation Block Diagram                        | 44 |

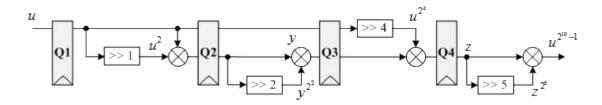

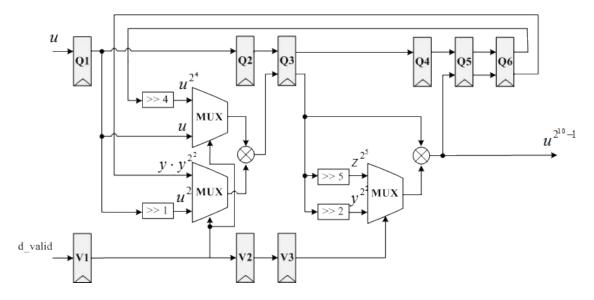

| 4.2  | Implementation of $(\cdot)^{2^{10}-1}$                 | 45 |

| 4.3  | Linear Feedback Shift Register Implementation          | 46 |

| 4.4  | Finite State Machine Implementation                    | 47 |

| 4.5  | Fragments of Test Vectors from WG Paper                | 49 |

| 4.6  | Finite State Machine Simulation Results                | 51 |

| 4.7  | Linear Feedback Shift Register Simulation Results      | 51 |

| 4.8  | Trace Function Simulation Results                      | 52 |

| 4.9  | WG Test Vectors Results                                | 53 |

| 4.10 | 4-Stage Implementation of $(\cdot)^{2^{10}-1}$         | 54 |

| 4.11 | 5-Stage Implementation of WG Core                      | 54 |

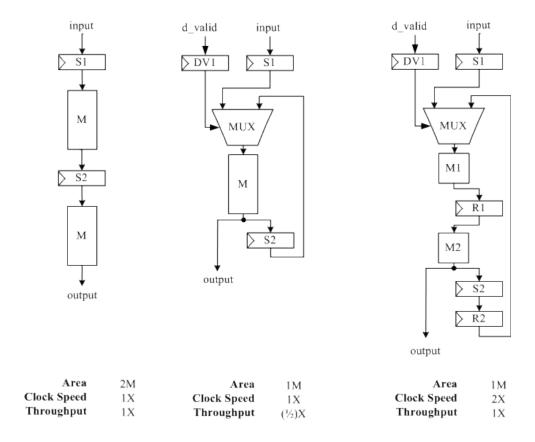

| 4.12 | Initial Pipeline                                       | 56 |

| 4.13 | Pipeline with Re-Use                                   | 56 |

| 4.14 | Pipeline with Re-Use and Superpipelining                                       | 56 |

|------|--------------------------------------------------------------------------------|----|

| 4.15 | Timing Diagram of Pipeline with Re-Use and Superpipelining                     | 57 |

| 4.16 | 9-stage Implementation of $(\cdot)^{2^{10}-1}$ with Re-Use                     | 58 |

| 4.17 | Timing Diagram of 9-stage Implementation of $(\cdot)^{2^{10}-1}$ with Re-Use . | 59 |

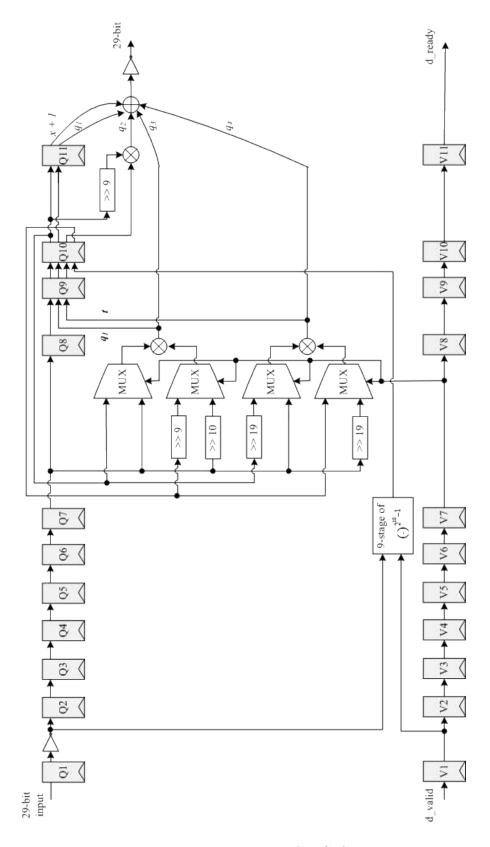

| 4.18 | 11-stage Implementation of WG Core with Re-Use                                 | 61 |

| 4.19 | Timing Diagram of 11-stage Implementation of WG Core with Re-Use $$            | 62 |

| 4.20 | Optimized Implementation Block Diagram of WG                                   | 64 |

| 4.21 | Modified Finite State Machine Implementation                                   | 65 |

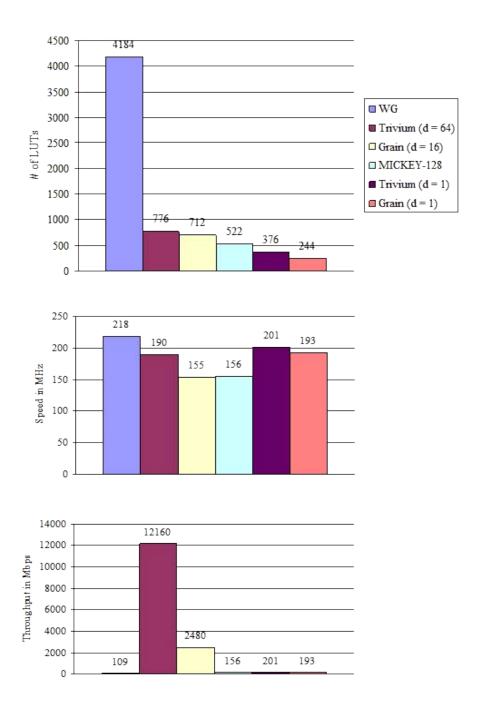

| 4.22 | Area and Performance Results of Various Stream Ciphers                         | 68 |

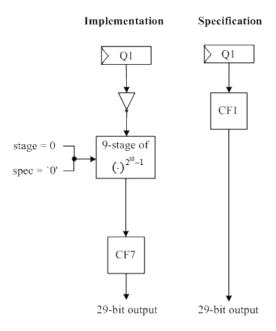

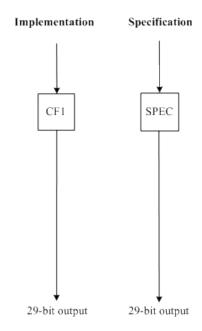

| 5.1  | Multiplier: $1^{st}$ Obligation                                                | 71 |

| 5.2  | Multiplier: $2^{nd}$ Obligation                                                | 71 |

| 5.3  | Multiplier: Final Obligation                                                   | 72 |

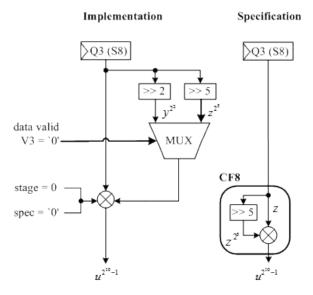

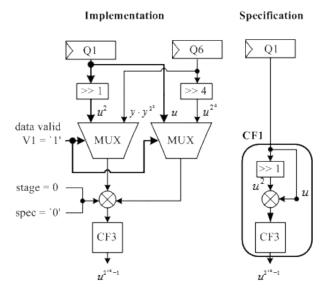

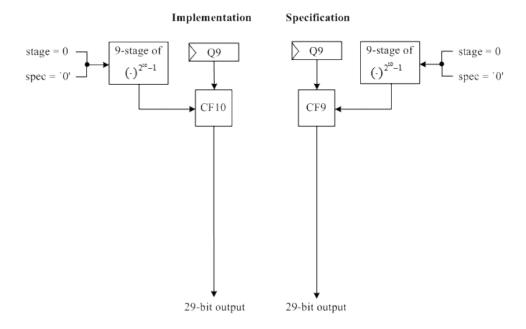

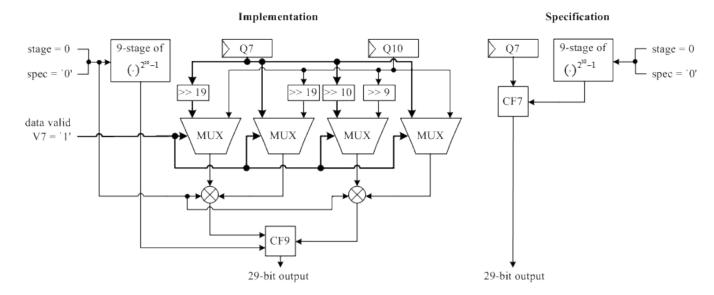

| 5.4  | Stage 8 Obligation with Skipping and $d_{-}valid='0'$                          | 73 |

| 5.5  | Stage 6 Obligation with Skipping and $d_{-}valid=$ '0'                         | 75 |

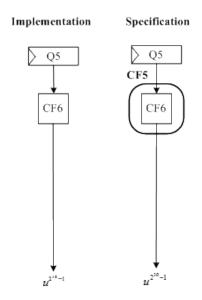

| 5.6  | Stage 5 Obligation                                                             | 75 |

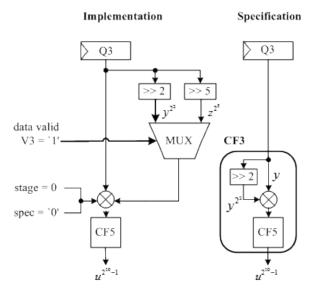

| 5.7  | Stage 3 Obligation with Skipping and $d_valid='1'$                             | 76 |

| 5.8  | Stage 1 Obligation with Skipping and $d_valid='1'$                             | 77 |

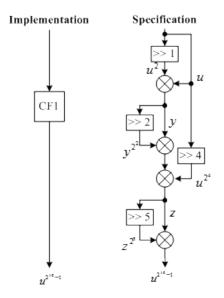

| 5.9  | Final Obligation of $(\cdot)^{2^{10}-1}$ Block                                 | 77 |

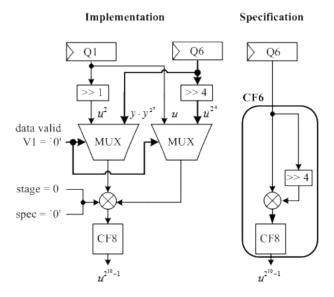

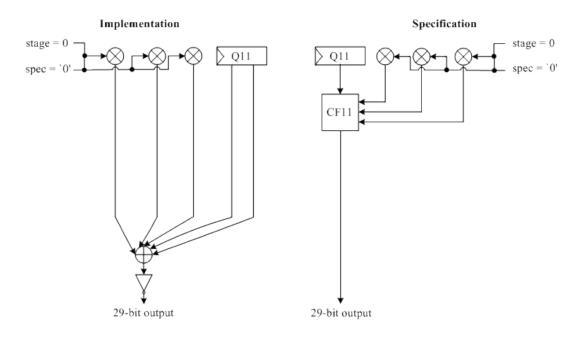

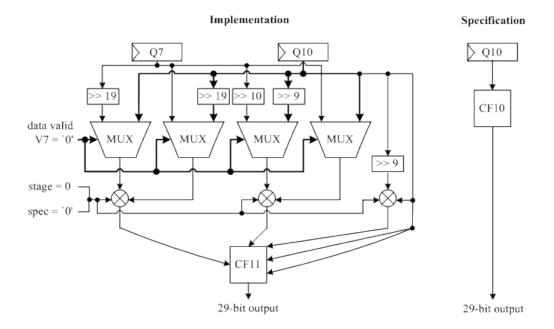

| 5.10 | Stage 11 Obligation of WG Core                                                 | 78 |

| 5.11 | Stage 10 Obligation of WG Core                                                 | 79 |

| 5.12 | Stage 9 Obligation of WG Core                                                  | 80 |

| 5.13 | Stage 7 Obligation of WG Core                                                  | 81 |

| 5.14 | Stage 1 Obligation of WG Core                                                  | 82 |

| 5.15 | Final Obligation of WG Core                                                    | 83 |

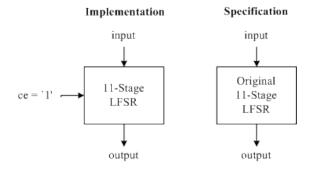

| 5.16 | Verification of LFSR with $ce='1'$                                             | 83 |

## Chapter 1

## Introduction

Many aspects of our life depend vitally on digital systems. Yet, empirical studies have shown that more than 50 percent of all application specific designs do not work properly after initial design and fabrication [15]. These dysfunctional designs can cost millions of dollars and human lives. In 1994, a bug in Intel's Pentium floating point unit costs 475 millions US dollars to replace the faulty processors [12]. Also, a data type conversion bug caused the launch failure of Ariane 5 rocket in 1996. In principle, verification methods can detect and fix these bugs at the early stages of the design process.

Verification is the process of proving or disproving the correctness of a design and it traditionally relies on exhaustive simulation. However, the increasing design size and complexity make exhaustive simulation an unattractive verification method due to the unreasonable required amount of time and computing resources. Formal verification can improve the verification procedure with the application of mathematics to formulate correctness criteria of designs, to develop mathematical models of designs, and to verify designs against their correctness criteria. In exchange of verifying all possible behaviours of a circuit, formal verification suffers from the problem of limited capacity where it can only verify detailed models of small circuits or very abstract models of complex circuits. Therefore, new verification methodologies need to be developed in order to increase the probability of achieving a bug-free design.

Most of current methods of communications either involve a personal computer or a mobile phone. To ensure that the information is exchanged in a secure manner, encryption circuits are used to transform the information into an unintelligible form. To be highly secure, this type of circuits is generally designed such that it is hard to analyze. Due to this fact, it becomes hard to locate a design error in the verification of cryptographic circuits. Therefore, cryptographic circuits pose significant challenges in the area of formal verification.

The aim of this thesis is to develop new verification methodologies by verifying cryptographic circuits. The results of this work can extend the existing collection of verification methods as well as benefiting the area of cryptography. The remaining of this chapter is organized as follows. In Section 1.1, we give a brief overview of the verification technique applied in our work and the two cryptographic circuits used as our verification case studies. Section 1.2 provides an outline of the major sections in this thesis.

## 1.1 Overview of Background

In formal verification, the technique of combinational equivalence checking is one of the most practical developments due to its high capacity and its high degree of automation. In the design of digital circuits, the initial hardware description of a specification is referred as the golden reference model. Under the assumption that the reference model has been verified by simulation or other verification methods, equivalence checking is used to prove the equivalence between the reference model and an implementation model which is derived from optimizing the reference model. The process of equivalence verification compares the combinational logic of the two models by identifying related signals in the two models, selecting a subset of the related points to be the compare points, and verifying each compare point in the implementation model against the corresponding compare point in the reference model.

In the design of digital circuits, the optimization technique of pipelining is widely used to increase the circuit throughput by overlapping the execution of instructions. Pipelining is one of the reasons for the increase in circuit complexity. For example, the specification of a processor defines how the programmer visible parts of the processor are updated after one instruction is executed, one cycle per instruction. However, pipelined implementations of processors can have partially executed instructions in the pipeline that cause the programmer visible parts to be updated at different pipeline stages or cycles. Therefore, a proper relationship between the specification and the pipelined implementation cannot be established due to partially executed instructions in the pipeline.

The verification technique of completion functions can establish a proper relationship between the specification and the pipelined implementation. Completion

functions are abstract functions used to decompose the verification of a pipeline into smaller stage-by-stage verification obligations. For each stage of a pipeline, there is a completion function that describes the effects on the programmer visible parts of completing the partially executed instruction in that stage. Thus, applying all completion functions of a pipeline has the same effect as completing all instructions in the pipeline. This verification technique can localize an implementation error and never lead to a false positive verification.

Cryptography is the study of the methods in securing information. To keep the information secret, encryption is the process used to convert comprehensible information (i.e. plaintext) into incomprehensible information (i.e. ciphertext). Decryption is the process used to recover the plaintext from the ciphertext. Together, encryption and decryption constitute a pair of algorithms which is referred as a cipher. KASUMI, also known as A5/3, is a block cipher in which encryption and decryption operations are identical with a reversal of the key schedule. It is used in the confidentiality and integrity algorithms for the third generation mobile phone system. It operates on blocks of 64 bits and outputs in block of 64 bits. WG is a synchronous stream cipher that has been designed to produce a keystream with guaranteed randomness properties such as balance, long period, large and exact linear complexity, 3-level additive autocorrelation and ideal 2-level multiplicative autocorrelation. Also, it is resistant to Time/Memory/Data tradeoff attacks, algebraic attacks and correlation attacks.

#### 1.2 Thesis Outline

The remaining of this thesis is organized as follows.

- Chapter 2 provides the necessary background for the reader to understand the work of this thesis.

- Chapter 3 describes the implementation, optimization, and verification of the KASUMI cipher.

- Chapter 4 contains the implementation and optimization of the WG cipher.

- Chapter 5 presents the verification of the WG cipher.

- Chapter 6 includes the conclusions of this thesis and future work.

## Chapter 2

## **Background Materials**

The work of this thesis involves exploring a formal verification strategy in the verification of two cryptographic circuits. The purpose of this chapter is to provide the necessary background in order to understand the contribution of this thesis, and this chapter is organized as follows. Section 2.1 and 2.2 are used to describe two verification strategies: Burch-Dill flushing and completion functions. Section 2.3 and 2.5 provides an introduction to cryptography as well as a list of algebraic terminologies. Section 2.4 and 2.6 give a description of our two verification case studies: the KASUMI cipher and the Welch-Gong cipher.

## 2.1 Burch-Dill Flushing

The research of this thesis involves the use of the verification strategy known as completion functions. The verification strategy of completion functions was derived from an earlier verification strategy called Burch-Dill flushing. To understand the verification strategy of completion functions, we explain why Burch-Dill flushing was invented and how it is used to verify a pipelined design in this section.

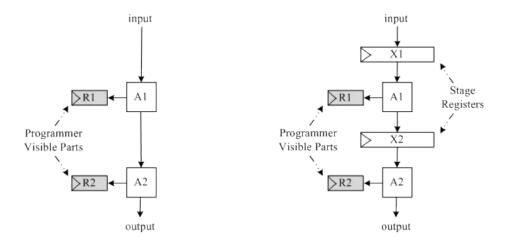

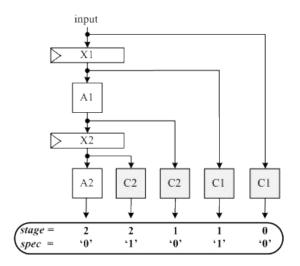

Burch-Dill flushing [6] is an important concept which was first used in the verification of pipelined processors. The specification of a processor defines how the programmer visible parts of the processor are updated after one instruction is executed, one cycle per instruction. However, pipelined implementations of processors can have partially executed instructions in the pipeline that cause the programmer visible parts to be updated at different pipeline stages or cycles. A contrived example based on Figure 2.1 to 2.3 would demonstrate this difficulty in the verification of pipelined implementations against a non-pipelined specification.

Figure 2.1: Specification

Figure 2.2: Pipelined Implementation

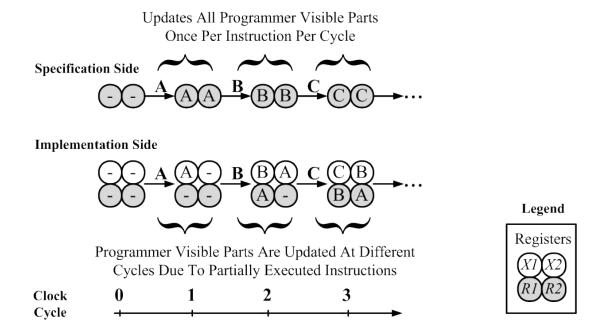

Figure 2.1 illustrates a non-pipelined specification which shows how the programmer visible parts (registers R1 and R2) are updated once per cycle depending on the instruction at the input of the combinational block A1 and A2. Figure 2.2 depicts a 2-stage implementation of the circuit shown in Figure 2.1 where the stage registers X1 and X2 are inserted to form the pipeline. For the 2-stage implementation of Figure 2.2, the circuit can execute two parcels of data simultaneously where the first pipeline stage writes to the register R1 and the second pipeline stage is used to update the register R2. Figure 2.3 illustrates how the specification and the pipelined implementation update their programmer visible parts R1 and R2. Figure 2.3 is divided into the specification side (top) and the implementation side (bottom). In addition, there is a legend for the registers (X1, X2, R1, R2) at the right end of Figure 2.3. Both the specification and the pipelined implementation begin with the registers R1 and R2 holding null values as shown in Figure 2.3. Then, the instruction sequence of  $\langle A, B, C \rangle$  is fed, one instruction per cycle, to both the specification and the pipelined implementation. On the specification side, both programmer visible parts R1 and R2 are updated at the same cycle for a given instruction. On the implementation side, the registers R1 and R2 always have different values due to partially executed instructions in the pipeline. Note that the stage registers (X1, X2) only exist on the implementation side due to pipelining, and that their behaviour are not defined as part of the specification. Thus, the correctness of the pipelined implementation is independent of the stage registers X1 and X2. Since the programmer visible parts (R1, R2) of both the specification and the pipelined implementation never hold the same value, it is impossible to draw a proper relationship between the specification and the pipelined implementation without relying on additional verification methods.

Figure 2.3: Difficulty in The Verification of Pipelined Circuits

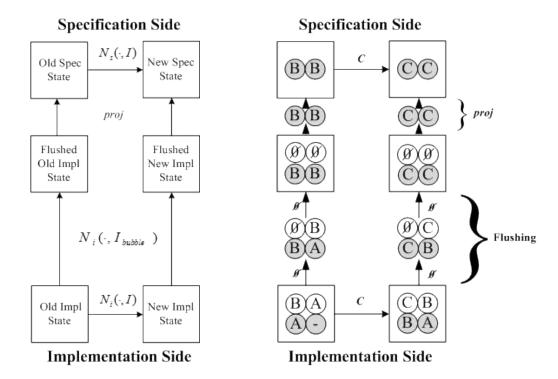

Figure 2.4 depicts how Burch-Dill flushing can be used to establish a proper relationship between a pipelined implementation and its specification. In verifying processors, both the specification and its implementation are modeled as state machines in Figure 2.4. The transition function  $N_i(\cdot, I)$  brings the old implementation state to its new implementation state given a set of inputs i. Similarly,  $N_s(\cdot, I)$  returns the new specification state given its old specification state and a set of inputs i. Burch and Dill used one of the processors properties to establish a proper relationship between the specification and its pipelined implementation. All processors have an input setting  $I_{bubble}$  that causes instructions already in the pipeline to continue execution while no new instructions are initiated, and this is known sending "bubbles" down the pipeline. Thus, all instructions already in the pipeline can be completed by sending a certain number of bubbles down the pipeline, and this is called Burch-Dill flushing.

In Figure 2.4, both old and new implementation states are flushed to emulate the effects of completing all instructions already in the pipeline. Thus, all partially executed instructions are completed and updated the programmer visible parts accordingly. Then, the *proj* function extracts the programmer visible parts from the flushed states. These extracted programmer visible parts can be compared with the old and the new specification state. The implementation satisfies the specification if and only if the diagram of Figure 2.4 commutes.

In order to demonstrate the use of Burch-Dill flushing on a simple example, the last two cycles of Figure 2.3 are used to partially form Figure 2.5. Note that Figure 2.5 and Figure 2.4 have similar structure in which the square boxes denotes exactly the same states (i.e. Old Spec, New Spec, Flushed Old Impl, Flushed New Impl, Old Impl, New Impl). In Figure 2.5, the specification states (Old, New) and the implementation states (Old, New) correspond to the ones shown in the last two cycles of Figure 2.3. However, a proper relationship between the specification and the pipelined implementation cannot be established due to partially executed instructions in the pipeline. Burch-Dill flushing is used to build this relationship from the implementation side (bottom) to the specification side (top) as shown in Figure 2.5. Since the example is a 2-stage pipeline, two bubbles (denoted as  $\emptyset$  in the figure) are sufficient to flush the pipeline and to emulate the effects of completing all instructions already in the pipeline.

In Figure 2.5, flushing brings the implementation states (Old, New) to their corresponding flushed states (Old, New). Then, proj function is applied to these flushed states in order to extract the programmer visible parts (R1, R2). In this simple example, both the implementation and the specification have a matching set of programmer visible parts (R1, R2) and it implies that the implementation is correct with respect to the specification. In the case that the set of programmer visible parts does not match, the implementation is said to be incorrect with respect to the specification.

With the idea of flushing, Burch and Dill verified a pipelined ALU and a subset of the DLX processor architecture. This section has explained the challenge in the verification of pipelined circuits, and it has demonstrated how Burch-Dill flushing is used to establish a proper relationship between a pipelined implementation and its non-pipelined specification. In the next section, the verification strategy of completion functions (based on Burch-Dill flushing) is introduced.

#### 2.2 Completion Functions

In this section, we describe why completion functions were invented, what they are and how they are used for the verification of pipelined circuits.

Burch-Dill flushing of Section 2.1 works well in the verification of small scale pipelined circuits, e.g. in-order pipelines with small number of stages. However, Burch-Dill flushing runs into the state-space explosion problem for large scale designs that support out-of-order execution and have a large number of pipeline stages.

Figure 2.4: Burch-Dill Flushing

Figure 2.5: Flushing Example

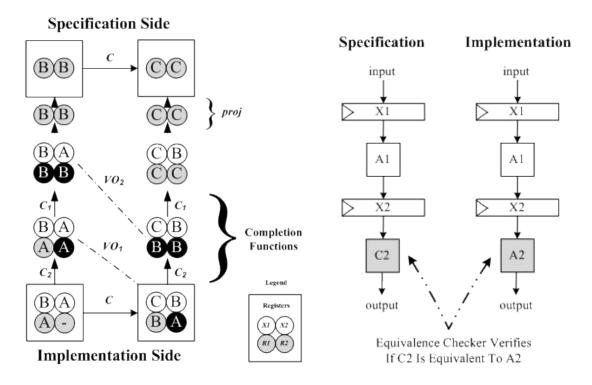

Completion functions are abstract functions used to decompose Burch-Dill flushing's monolithic verification in Figure 2.4 into multiple smaller verification obligations. Thus, the completion functions approach is a solution to Burch-Dill flushing's state-space explosion problem. For each stage of a pipeline, there is a completion function that describes the effects on the programmer visible parts of completing the partially executed instruction in that stage. Thus, applying all completion functions of a pipeline has the same effect as flushing a pipeline. Hosabettu et al. used completion functions over Burch-Dill flushing to establish a proper relationship between a pipelined implementation states and its non-pipelined specification states. This verification technique can localize an implementation error and never lead to a false positive verification.

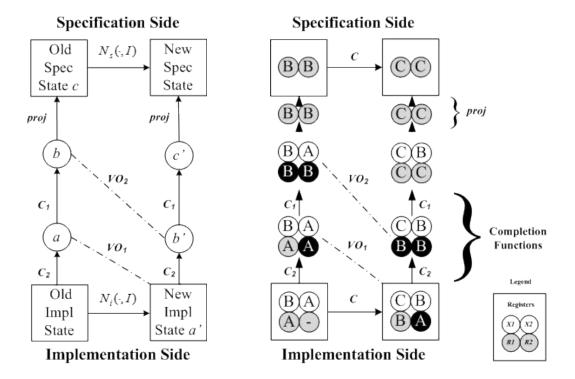

A contrived example in Figure 2.6 shows how completion functions are used for the verification of a 2-stage pipeline. The pipelined implementation satisfies its specification if and only if the diagram in Figure 2.6 commutes. A pipeline of n-stage requires n+1 verification obligations to check its correctness. In this example, the first obligation  $VO_1$  verifies the second or last pipeline stage by comparing the state a produced by applying last stage's completion function  $C_2$  to the state a' produced by taking an implementation step  $N_i(\cdot, I)$ . The second obligation  $VO_2$  is used to verify the first pipeline stage, and it compares the state b produced by

Figure 2.6: Completion Functions

Figure 2.7: Completion Functions Example

the completion function  $C_1$  to the state b' produced by taking an implementation step and then applying  $C_2$ . The last or third verification obligation compares the specification step  $N_s(\cdot, I)$  to the completion function of the first stage  $C_1$ . Therefore, mistakes in building these completion functions can be detected with this final verification obligation. Also, implementation bugs can be localized due to the stage-by-stage verification given that the completion functions are correct.

In order to show the similarities and the differences between the completion functions approach and Burch-Dill flushing, the same example of Figure 2.5 is verified with completion functions. As depicted in Figure 2.7, the four square boxes represent the four states (*Old Impl State*, *New Impl State*, *Old Spec State*, *New Spec State*). In Figure 2.7, note that the completion functions have replaced Burch-Dill flushing in establishing a proper relationship between the implementation states and the specification states.

The completion functions approach and Burch-Dill flushing uses the same correctness criteria as follows. Given that the implementation and the specification start in any matching pair of states (i.e. Old Impl State matches Old Spec State), the implementation is said to be correct when taking an implementation step  $N_i(\cdot, I)$  on the implementation side leads to a matching pair of states (i.e. New Impl State matches New Spec State) as taking a specification step  $N_s(\cdot, I)$  on the

specification side. In other words, the implementation is correct when the diagrams (Figures 2.5 and 2.7) commute.

The completion functions approach differs from Burch-Dill flushing in the way it establishes the relationship from the implementation side to the specification side as shown in Figure 2.7. Since Burch-Dill flushing runs into the state-space explosion problems for pipelines with large number of stages, the completion functions decompose the 2-stage pipeline verification of Figure 2.5 into 3 smaller verification obligations as shown in Figure 2.7.

In Figure 2.7, the first verification obligation  $VO_1$  is used to verify the correctness of the second stage of the pipeline in Figure 2.2. It compares the value of the register R2 produced by the completion function  $C_2$  to the one produced by taking an implementation step as shown in Figure 2.7. The completion function  $C_2$  completes the instruction A in the stage register X2 and updates the register R2 accordingly. The implementation step updates the register R2 according to the circuit shown in Figure 2.2. Thus, the first verification obligation  $VO_1$  verifies if the second pipeline stage is equivalent to the completion function  $C_2$ .

Similarly, the next verification obligation  $VO_2$  of Figure 2.7 is used to verify the correctness of the first pipeline stage in Figure 2.2. It compares the values of the register set (R1, R2) generated by the completion function  $C_1$  to the values created by taking an implementation step followed by the completion function  $C_2$ in Figure 2.7. Since  $VO_2$  verifies the correctness of the first pipeline stage, the completion functions  $C_1$  is applied to the stage register X1 to emulate the effects of completing the instruction B as shown in Figure 2.7. The implementation step updates the register R1 according to the circuit shown in Figure 2.2 and it is followed by the completion function  $C_2$  to update the register R2. Thus, the second verification obligation  $V0_2$  verifies if the first pipeline stage is correct with respect to the behaviour given by the completion function  $C_1$ .

Up to this point of the verification, it has been shown that the pipeline stages are functionally correct with respect to their completion functions ( $C_1$  or  $C_2$ ). However, these completion functions can have design bugs buried in them. Finally, the last or third verification obligation compares the specification step to the completion function of the first pipeline stage  $C_1$ . Therefore, any bugs in the completion functions are caught with this final verification obligation.

Completion functions have been investigated under several verification techniques. Hosabettu et al. invented completion functions and verified complex out-of-order processors in an interactive theorem prover [10]. Berezin et al. applied

completion functions to symbolic model checking in verifying an abstract model of Tomasulos algorithm [5]. Velev used completion functions and automated first-order decision procedures to verify abstract models of out-of-order processors [18]. Aagaard et al. combined completion functions and equivalence checking for the verification of a 32-bit OpenRISC processor and a Sobel edge-detector circuit at the register- transfer-level [3].

This section has covered the need for completion functions, how they are applied in the verification of a 2-stage pipeline, their similarities and their differences to Burch-Dill flushing, and how they have been used in other work.

## 2.3 The Basics of Cryptography

To better understand the two cryptographic circuits, this section provides an introduction to cryptography. This section describes the following: cryptography, encryption, decryption, symmetric key algorithms, asymmetric key algorithms, key scheduling, block ciphers, and stream ciphers. Section 2.4 describes the KASUMI cryptographic algorithm, and Section 2.6 provides the background of the Welch-Gong cipher.

Cryptography is the study of the methods in securing information. To keep the information secret, encryption is the process used to convert comprehensible information (i.e. plaintext) into incomprehensible information (i.e. ciphertext). Decryption is the process used to recover the plaintext from the ciphertext. Together, encryption and decryption constitute a pair of algorithms which is referred as a cipher. The operations of a cipher are not just determined by the algorithm, but they also depend on a key. When a different key is used for the encryption/decryption of the same plaintext/ciphertext, the cipher produces a corresponding ciphertext/plaintext for each key. Thus, keys make it more difficult in establishing the relationship between the plaintext and the ciphertext.

Depending on the type of key used, a cipher can be categorized as a symmetric key or an asymmetric key algorithm. In a symmetric key algorithm, the same key is used for both encryption and decryption. The key used to encrypt a plaintext differs from the key used to decrypt it in an asymmetric algorithm. Certain types of ciphers use an algorithm, known as the key schedule, to compute smaller keys from the input key. Then, the smaller keys are used during encryption/decryption. The contribution of this thesis involves the verification of two symmetric key algorithms.

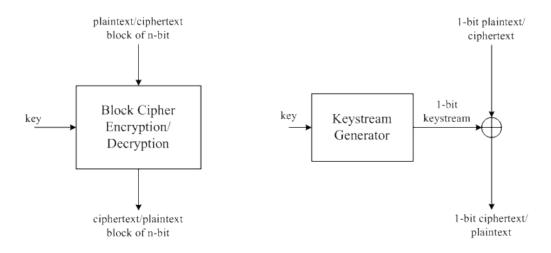

Figure 2.8: Block Ciphers

Figure 2.9: Stream Ciphers

Hence, this section focuses on symmetric key algorithms and any information relevant to the understanding of this thesis.

A symmetric key algorithm can be classified as a block cipher or a stream cipher depending on the type of input data. As the name suggested, block ciphers have the characteristic of operating on block of n-bit. Figure 2.8 illustrates the general structure of a block cipher. A block cipher takes a plaintext/ciphertext of n-bit and a key, and it computes the corresponding ciphertext/plaintext of n-bit. In contrast, stream ciphers encrypt/decrypt one bit at a time. Figure 2.9 shows the general structure of a stream cipher. Given a key, the keystream generator of the stream cipher produces a pseudorandom sequence of bits (keystream). During encryption, the keystream is XORed to the plaintext in a bitwise fashion. Similarly, decryption recovers the original plaintext by XORing the same keystream bits to its corresponding ciphertext bits. Thus, it usually requires the sender and the receiver to be synchronized in producing an identical keystream for accurate encryption and decryption. This type of cipher is known as synchronous stream cipher.

## 2.4 The KASUMI Cipher

In this section, we provide a description of the algorithm that we implemented in our first verification case study: the KASUMI cipher. Chapter 3 describes our implementation, optimization, and verification of the KASUMI algorithm.

KASUMI, also known as A5/3, is a block cipher in which encryption and decryption operations are identical with a reversal of the key schedule. Therefore,

its implementation size can be reduced by nearly half which leads to its use in the confidentiality and integrity algorithms for the third generation mobile phone system. It operates on blocks of 64 bits and outputs in block of 64 bits.

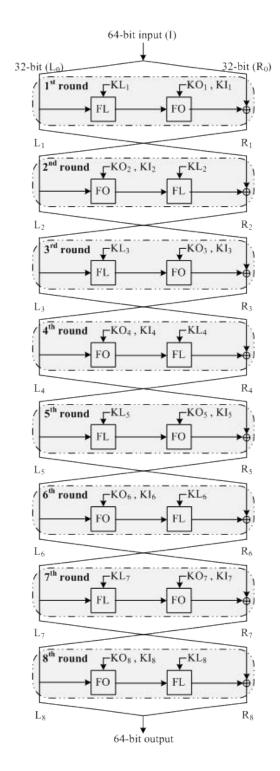

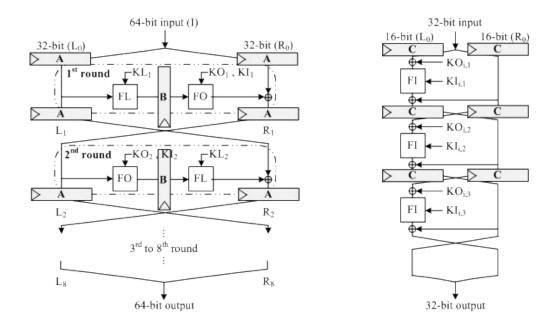

In Figure 2.10, the algorithm begins by dividing a 64-bit input i into two 32-bit strings  $L_0$  and  $R_0$  which are then introduced into the first round of the cipher. KASUMI has a total of eight rounds in which all even rounds are identical and all odd rounds are the same. A 128-bit input key is used to derive the subkeys  $KL_i$ ,  $KO_i$ ,  $KI_i$  through XOR and bitwise permutations of the input key for each round i = 1...8, and this is called the key schedule. At the end of the final round, the algorithm terminates with a 64-bit output.

Every round of the cipher in Figure 2.10 sends two 32-bit inputs  $L_{i-1}$  and  $R_{i-1}$  through the FL and FO subfunctions to compute two 32-bit outputs  $L_i$  and  $R_i$  defined as:

$$L_{i} = \begin{cases} R_{i-1} \oplus FO(FL(L_{i-1}, KL_{i}), KO_{i}, KI_{i}) & i = 1, 3, 5, 7 \\ R_{i-1} \oplus FL(FO(L_{i-1}, KO_{i}, KI_{i}), KL_{i}) & i = 2, 4, 6, 8 \end{cases}$$

(2.1)

$$R_i = L_{i-1} i = 1 \dots 8 (2.2)$$

The FL subfunction splits a 32-bit input into two 16-bit strings L and R, and it divides the 32-bit subkey  $KL_i$  into two 16-bit subkeys  $KL_{i,1}$  and  $KL_{i,2}$ . A 32-bit output is obtained through the concatenation of the two 16-bit strings L' and R' defined as:

$$R' = R \oplus ROL(L \cap KL_{i,1}) \qquad i = 1...8 \tag{2.3}$$

$$L' = L \oplus ROL(R' \cup KL_{i,2}) \qquad i = 1...8$$

(2.4)

In Figure 2.11, the FO subfunction starts by splitting a 32-bit input into two 16-bit strings  $L_0$  and  $R_0$  which are then fed into three identical rounds formed mainly by the FI subfunction. The 48-bit subkeys  $KO_i$  and  $KI_i$  are each divided into their three corresponding 16-bit subkeys  $KO_{i,j}$  and  $KI_{i,j}$  for i = 1...8 and j = 1...3. Each round of the FO subfunction is defined as:

$$R_j = FI(L_{j-1} \oplus KO_{i,j}, KI_{i,j}) \oplus R_{j-1}$$

$i = 1 \dots 8, j = 1 \dots 3$  (2.5)

$$L_j = R_{j-1}$$

$i = 1 \dots 8, j = 1 \dots 3$  (2.6)

The FI subfunction applies many bitwise permutations, truncations, and XOR to obscure the relationship between the input and the output. Its detailed description is not necessary to understand the remaining chapters of this thesis, and the reader can obtain that information in the specification of KASUMI [1].

Figure 2.10: KASUMI Circuit

Figure 2.11: FO Circuit

## 2.5 Algebraic Terminology for Finite Fields and Normal Basis

In order to understand the description of the next cryptographic circuit, the reader is required to have some knowledge about abstract algebra. In this section, the following terms are defined: field, finite field, extension field, basis, primitive polynomial, polynomial basis, and normal basis.

**Field**: a field is an algebraic structure in which the operations of addition, subtraction, multiplication and division are define with the same rules that hold for normal arithmetic.

**Finite field**: finite field, also known as Galois field, is a field that contains finitely many elements.  $\mathbb{F}_2$  denotes the finite field with two elements, 0 and 1.

**Extension field**: let L be a field. If K is a subset of L which is closed with respect to the field operations of addition and multiplication in L and the additive and multiplicative inverses of every element in K are in K, then L is an extension field of K.  $\mathbb{F}_{2^m}$  denotes the extension field of  $\mathbb{F}_2$  with  $2^m$  elements, where each element is represented as a m-bit binary vector. Thus, a field  $\mathbb{F}_{2^m}$  can be viewed as an m-dimensional vector space defined over  $\mathbb{F}_2$ .

Basis: basis is a set of vectors that, in a linear combination, can express every vector in a given vector space and such that no element of the set can be expressed as a linear combination of the others.

**Primitive polynomial**: let the set of vectors  $\{1, \beta, \beta^2, \dots, \beta^{m-1}\}$  be the basis for the field  $\mathbb{F}_{2^m}$ . Then, a polynomial with coefficients in  $\mathbb{F}_2$  is a primitive polynomial if its root is  $\beta \in \mathbb{F}_{2^m}$ , and it has to be the smallest degree polynomial having  $\beta$  as a root.

**Polynomial basis**: let  $\beta \in \mathbb{F}_{2^m}$  be the root of a primitive polynomial of degree m over  $\mathbb{F}_2$ . Then, the set of vectors  $\{1, \beta, \beta^2, \dots, \beta^{m-1}\}$  is called the polynomial basis or the canonical basis of  $\mathbb{F}_{2^m}$  over  $\mathbb{F}_2$ .

**Normal Basis**: let the set of elements  $P = \{\gamma, \gamma^2, \gamma^4, \dots, \gamma^{2^{m-1}}\}$  be the basis of  $\mathbb{F}_{2^m}$  over  $\mathbb{F}_2$ . Then, the basis P is called a normal basis and  $\gamma$  is called a normal element.

## 2.6 The Welch-Gong Cipher

This section describes the circuit structure proposed by Gong and Nawaz [14], and it explains how the cipher is initialized prior its use for encryption/decryption. Chapter 4-5 describes our implementation, optimization, and verification of the Welch-Gong cipher.

WG is a synchronous stream cipher that has been designed to produce a keystream with guaranteed randomness properties such as balance, long period, large and exact linear complexity, 3-level additive autocorrelation and ideal 2-level multiplicative autocorrelation. Also, it is resistant to Time/Memory/Data tradeoff attacks, algebraic attacks and correlation attacks.

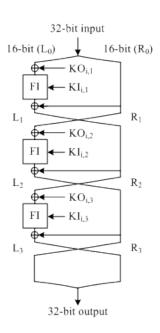

Figure 2.12 shows the general circuit structure of the WG family cipher. It consists of a linear feedback shift register, also called LFSR, followed by a WG transformation block. The mathematical definition of the WG transformation f(x) is described here:

$$f(x) = Tr_1^m(t(x+1)+1), x \in \mathbb{F}_{2^m}$$

(2.7)

The trace function  $Tr_1^m(x)$  from  $\mathbb{F}_{2^m} \to \mathbb{F}_2$  is defined as:

$$Tr_1^m(x) = \sum_{i=0}^{m-1} x^{2^{mi}}, x \in \mathbb{F}_{2^m}$$

(2.8)

The function t(x) exists only if  $m \neq 0 \mod 3$ , and it is defined as:

$$t(x) = x + x^{q_1} + x^{q_2} + x^{q_3} + x^{q_4}, x \in \mathbb{F}_{2^m}$$

(2.9)

For  $k \in \mathbb{N}$  and m = 3k - 1,  $q_i$ 's are defined as:

$$q_{1} = 2^{k} + 1$$

$$q_{2} = 2^{2k-1} + 2^{k-1} + 1$$

$$q_{3} = 2^{2k-1} - 2^{k-1} + 1$$

$$q_{4} = 2^{2k-1} + 2^{k} - 1$$

$$(2.10)$$

and for m = 3k - 2, they are defined as:

$$q_{1} = 2^{k-1} + 1$$

$$q_{2} = 2^{2k-2} + 2^{k-1} + 1$$

$$q_{3} = 2^{2k-2} - 2^{k-1} + 1$$

$$q_{4} = 2^{2k-1} - 2^{k-1} + 1$$

(2.11)

Figure 2.12: WG Family Circuit Structure

Various implementations of the WG cipher exist, and they have a different level of security depending on their design parameters. The number of LFSR stages l, the feedback polynomial of the LFSR, the number of bits m used for the WG transform computation, and the basis used to represent each field element affect the implementation complexity and security. A detailed design analysis of the WG family ciphers and how to select these design parameters are not relevant to the remaining chapters of this thesis, and the reader can find this information in Nawaz's PhD thesis [13].

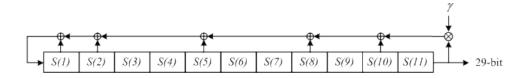

The implementation presented in [14] is one of the two verification case studies of our thesis and it is described in this section. Figure 2.13 illustrates the 11-stage LFSR(l=11) over  $\mathbb{F}_{2^{29}}(m=29)$  in which its feedback polynomial p(x) is defined as:

$$p(x) = \gamma \cdot x^{11} + x^{10} + x^8 + x^5 + x^2 + x + 1 \tag{2.12}$$

where  $\beta \in \mathbb{F}_{2^{29}}$  and the set  $\{1, \beta, \beta^2, \dots, \beta^{m-1}\}$  forms the polynomial basis of  $\mathbb{F}_{2^{29}}$ . Also,  $\beta$  is the root of the primitive polynomial g(x) defined as:

$$g(x) = x^{29} + x^{28} + x^{24} + x^{21} + x^{20} + x^{19} + x^{18} + x^{17} + x^{14} + x^{12} + x^{11} + x^{10} + x^{7} + x^{6} + x^{4} + x + 1$$

(2.13)

over  $\mathbb{F}_2$ . Note that  $S_i \in \mathbb{F}_{2^{29}}$  and the feedback polynomial of the LFSR includes a normal basis multiplication with the element  $\gamma$  which is defined, in the polynomial form, as:

$$\gamma = \beta^{1} + \beta^{2} + \beta^{3} + \beta^{5} + \beta^{6} + \beta^{7} + \beta^{10} + \beta^{11} + \beta^{12} + \beta^{13} + \beta^{14} + \beta^{15} + \beta^{16} + \beta^{17} + \beta^{20} + \beta^{23} + \beta^{24} + \beta^{26} + \beta^{27}$$

(2.14)

$\gamma$  is a normal element and it is used to define the normal basis of  $\{\gamma^{2^0}, \gamma^{2^1}, \gamma^{2^2}, \dots, \gamma^{2^{28}}\}$ . For m = 29, t(x) is defined as:

$$t(x) = x + x^{2^{10}+1} + x^{2^{19}+2^{9}+1} + x^{2^{19}-2^{9}+1} + x^{2^{19}+2^{10}-1}, x \in \mathbb{F}_{2^{29}}$$

(2.15)

and the WG transformation becomes:

$$f(x) = Tr_1^{29}(t(x+1)+1), x \in \mathbb{F}_{2^{29}}$$

(2.16)

Figure 2.13: LFSR Feedback Polynomial

The WG transformation can be implemented in both the normal basis and the polynomial basis representation. However, the normal basis representation offers the following advantages:

- From the definition of a normal basis  $\{\gamma, \gamma^2, \gamma^4, \dots, \gamma^{2^{m-1}}\}$  in  $\mathbb{F}_{2^m}$  over  $\mathbb{F}_2$ , shifting the bits of an element x cyclically to right by i position computes  $x^{2^i}$ . Thus, the squaring operation consists of rewiring the bits of a field element in terms of hardware. This operation comes up multiple times in the definition of t(x).

- In normal basis representation, the all ones vector represent 1. Therefore, the operation of adding 1 to a field element becomes inverting all the bits of that element. This operation occurs twice in the definition of the WG transformation, and it requires 2m inverters given a the field  $\mathbb{F}_{2^m}$ .

- In normal basis representation, the trace function  $Tr_1^m(x)$  of any normal basis elements is one. Therefore, the trace function of a field element is done by adding all the bits of that element over  $\mathbb{F}_2$ .

Nawaz [13] has showed that equation (2.15) can be written in order to decrease the implementation area of WG as follows:

$$t(x) = x + x^{2^{10}+1} + x^{2^{19}+2^{9}+1} + x^{2^{19}-2^{9}+1} + x^{2^{19}+2^{10}-1}$$

$$= x + x^{2^{10}+1} + x^{2^{19}+2^{9}+1} + x^{(2^{10}-1)\cdot 2^{9}+1} + x^{2^{19}+(2^{10}-1)}$$

(2.17)

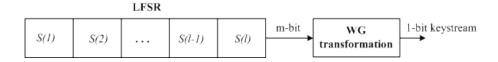

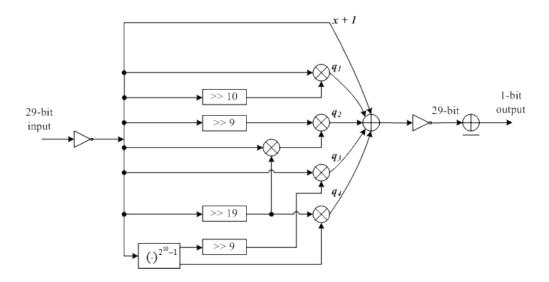

Figure 2.14 shows the implementation of the WG transformation for  $\mathbb{F}_{2^{29}}$  according to the properties of its normal basis representation.  $(x)^{-1}$  denotes the normal basis inversion of x in  $\mathbb{F}_{2^{29}}$ . x >> i denotes cyclic shift of x, i positions to the right where  $c \geq 0$ .  $x \otimes y$  means normal basis multiplication of x and y in  $\mathbb{F}_{2^{29}}$ .  $x \oplus y$  means bitwise XOR of x and y. Finally,  $\underline{\oplus}(x)$  means XORing all 29 bits of x over  $\mathbb{F}_2$ .

The WG implementation described above can be used with key sizes of 80, 96, 112 and 128 bits. In addition, it can take either a 32 or a 64 bits Initialization Vector (IV). For the purpose of this thesis, only a 80-bit key and a 32-bit IV are

Figure 2.14: Implementation of WG Transformation

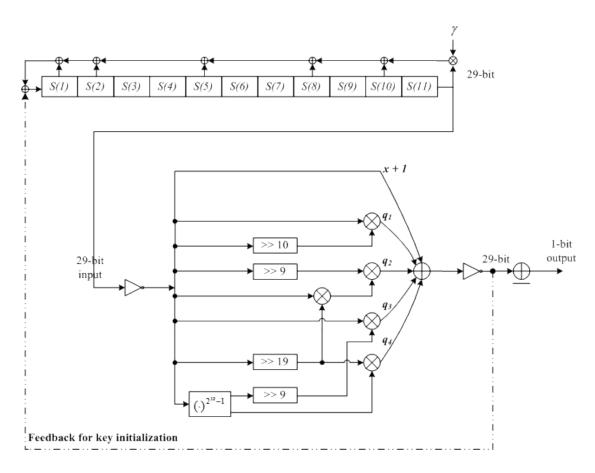

considered. The first step in initializing the cipher is to load the key bits and IV bits into the LFSR. Each stage i of the LFSR is denoted by s(i) or more precisely  $S_{1,\dots,29}(i)$  where  $1 \leq i \leq 11$ . Similarly, the key bits are denoted as  $k_{1,\dots,j}$  where  $1 \leq j \leq 80$  and the IV bits as  $IV_{1,\dots,k}$  where  $1 \leq k \leq 32$ . The 80-bit key and the 32-bit IV are loaded into the LFSR as described:

$$\begin{array}{lll} S_{1,\dots,16}(1)=k_{1,\dots,16} & S_{1,\dots,16}(2)=k_{17,\dots,32} & S_{1,\dots,16}(3)=k_{33,\dots,48} \\ S_{1,\dots,16}(4)=k_{49,\dots,64} & S_{1,\dots,16}(5)=k_{65,\dots,80} & S_{1,\dots,16}(9)=k_{1,\dots,16} \\ S_{1,\dots,16}(10)=k_{17,\dots,32}\oplus 1 & S_{1,\dots,16}(11)=k_{33,\dots,48} \\ S_{17,\dots,24}(1)=IV_{1,\dots,8} & S_{17,\dots,24}(2)=IV_{9,\dots,16} & S_{17,\dots,24}(3)=IV_{17,\dots,24} \\ S_{17,\dots,24}(4)=IV_{25,\dots,32} & S_{17,\dots,24}(2)=IV_{9,\dots,16} & S_{17,\dots,24}(3)=IV_{17,\dots,24} \end{array}$$

To complete the LFSR loading phase, all the undefined bits of the LFSR are set to zero. Once the LFSR has been loaded with the key and IV, the circuit is run for 44 clock cycles with the additional connection shown in Figure 2.15. Once the key has been initialized, the feedback connection in Figure 2.15 is disconnected from the LFSR and the first bit of the keystream is given by the 1-bit output of the WG transformation after one clock cycle.

This section has given the description of the Welch-Gong cipher, its mathematical formulation, the circuit structure of its 29-bit implementation based on normal basis, and how to initialize the cipher with the key and the initialization vector.

Figure 2.15: Key Initialization Phase

## Chapter 3

# KASUMI: Design, Optimizations and Verification

The contribution of this thesis is to verify two cryptographic circuits using the verification strategy of completion functions at the register transfer level. The goal of this chapter is to show how completion functions are used in the verification of the KASUMI cipher, and this chapter is organized as follows. Section 3.1 describes the design process of our non-pipelined KASUMI implementation, and Section 3.2 explains how RTL simulation is used to verify this non-pipelined implementation. Section 3.3 illustrates how the optimization of pipelining produces three pipelined implementations of KASUMI. Section 3.4 introduces the verification methodologies used to verify these three pipelined implementations, and Section 3.5 shows the results of our verification.

#### 3.1 The First Design

The goal of this chapter is to explore completion functions in the verification of pipelined implementations of KASUMI against its non-pipelined specification at the register transfer level. Therefore, we first need to build a non-pipelined implementation of KASUMI such that it can be used as the specification.

The circuit structure of the KASUMI cipher and its circuit operation were discussed in Section 2.4. Our research work began with the design of a purely combinational or non-pipelined implementation of the KASUMI cipher using the VHDL hardware description language. Since the KASUMI circuit has an highly recursive and modular structure formed by several components (FI, FO, FL), we

have taken a bottom-up modular design approach. We started by implementing the FI component because it is the lowest level component in the KASUMI circuit. Then, the FO component was built using a composition of XOR gates, bitwise permutations and multiple FI components. The FL component was implemented independently of the other components following the description in Section 2.4. With the implementation of the FO and the FL components, we constructed all even and odd rounds of KASUMI. Our first VHDL implementation of KASUMI was completed by connecting each round of the cipher with its corresponding subkey that was generated by the key scheduling algorithm described in the specification of KASUMI [1].

This first implementation was synthesized using Mentor Graphics Precision RTL synthesis tool. On an Altera Stratix II series field programmable gate arrays (FPGA) device EP2S15F484C, our combinational implementation of KASUMI has an area of 4748 logic elements and a performance of 9 MHz when registers are inserted at the inputs and at the outputs. The verification of this combinational implementation is described in the next section.

## 3.2 Formulating The Specification

Various verification technologies and strategies can be applied for the verification of a circuit at different level of abstraction. Our work focuses on exploring the verification strategy of completion functions in the verification of pipelined implementations with respect to a combinational specification at the register transfer level. Therefore, we are required to verify the correctness of our combinational implementation of KASUMI because it will be used as the specification for the verification of the pipelined implementations of KASUMI.

Since the main focus of our work is to verify pipelined circuits and a set of test vectors are provided in the specification of KASUMI [2], we have used conventional RTL simulation for the verification of the combinational implementation of KASUMI. In [2], various sets of test vectors are given for all three major components (FI, FL, FO) as well as for the whole KASUMI cipher. Thus, the combinational implementation is defined as correct if and only if it generates the expected outputs given its associated set of test vectors. However, there are still possibilities for a subtle bug to be undetected because our RTL simulation does not cover all possible inputs to the KASUMI cipher.

| <b></b>           | A9C9 | (AD6B | CF17  | (D35D |  |

|-------------------|------|-------|-------|-------|--|

| <b></b>           | CD58 | (F388 | (6BF0 | 7EEF  |  |

| → /fi_tb/out16  → | 4FB0 | Æ2FC  | (43CD | (D85E |  |

Figure 3.1: FI Test Vectors Results

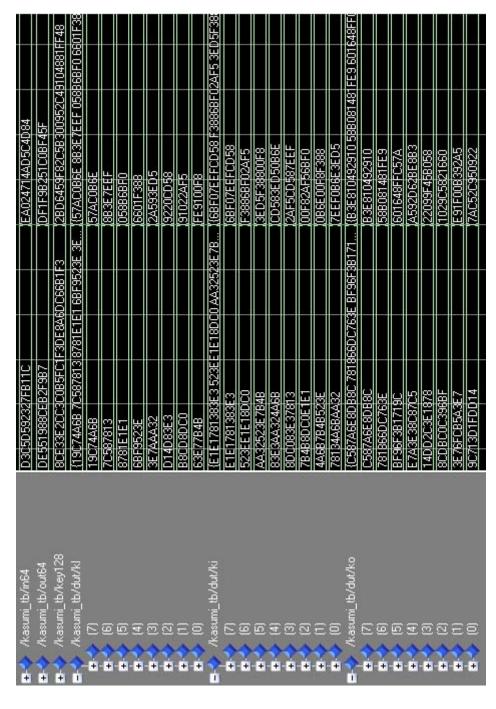

Similar to our modular bottom-up design approach, we verified the combinational KASUMI, components by components, starting from the smallest building blocks. This simulation methodology would localize an implementation bug to a component. For all of the RTL simulation runs, we have used Mentor Graphics ModelSim. Figure 3.1 shows the simulation results of the FI component in which in16 is the 16-bit input, key16 is the 16-bit subkey KL and out16 is the 16-bit output. Figure 3.2 illustrates fragments of test vectors in the specification of KA-SUMI [2], and the circled test vectors correspond to the waveform shown in Figure 3.1. Notice that all vectors holds hexadecimal values and that only a subset of test vectors from the specification of KASUMI[2] are presented here. Figure 3.3 depicts the verification of the FO component, where in32 and out32 are the 32-bit input and ouput, ki48 and ko48 are the 48-bit subkeys KI and KO respectively. Figure 3.4 illustrates the test vectors results of the FL component in which in32 is the 32-bit input, out32 is the 32-bit output and kl32 is the 32-bit subkey KL. Finally, we have verified that our combinational implementation of KASUMI produces the expected 64-bit output out64 given its corresponding 64-input in64 and 128-bit key key128 as shown in Figure 3.5. Through the key scheduling algorithm, the 128-bit key key128 has properly transformed into three sets (KL, KI, KO) of eight subkeys for all eight rounds of the KASUMI cipher as shown in Figure 3.5. For all three sets (KL, KI, KO), the subkeys of the first round are denoted by (7) and the subkeys of the eighth round are denoted by (0).

Our combinational implementation of KASUMI was verified through various sets of test vectors, and no bugs were found. Therefore, this implementation can serve as a specification for the pipelined implementations of KASUMI that are described in the next section, when using the verification strategy of completion functions.

```

Round 1

FL1 (EA024714, 57AC, 0B6E) ->7CFFC314

FO1(7CFFC314)->50871737

FI11(CF17,6BF0)->43CD

seven 17 > 00-> 47-> 72-> 6C-> 21

Rine T9E->05C->04B->1BB->1BF->1CD

FI12 (D35D, 7EEF) ->D85E

Beven 5D-> 61-> 3E-> 01-> 32-> 6C

n<del>ine 1A6->002-</del>>0<u>D</u>F->030->05F->05E

FI13 (A9C9, CD58) ->4FB0

<del>seven 49 > 63-></del> 52-> 34-> 17-> 27

nine 153->1F8->1B1->0E9->184->1B0

Round 2

FQ2-(FSDB5AB3)->03E715B9

_FI21(AD6B,F388)->E2FC

seven 6B-> 31-> 4F-> 36-> 0D-> 71

nine 15A->015->07E->1F6->0CA->0FC

FI22 (DBFB, 6BF0) ->BBA8

seven 7B-> 29-> 75-> 40-> 75-> 5D

nine 1B7->127->15C->OAC->1E8->1A8

FI23 (A7A6, 2AF5) ->165E

seven 26-> 3A-> 73-> 66-> 55-> 0B

nine 14F->06F->049->0BC->038->05E

FL2(03E715B9,8B3E,7EEF)->FC1913F5

```

Figure 3.2: Fragments of Test Vectors from KASUMI Specification

| <b></b> → /fo_tb/in32   | F5DB5AB3     | [E9F55CF7]    | (0C12818C    | [7CFFC314]    |

|-------------------------|--------------|---------------|--------------|---------------|

| <b>⊹</b> /fo_tb/out32   | 03E715B9     | (F9C9DB3F     | F9C83A1A     | 58871737      |

| <b>∓-</b> ♦ /fo_tb/ki48 | F3886BF02AF5 | (3ED5F38800F8 | CD583ED50B6E | (6BF07EEFCD58 |

| <b></b> → /fo_tb/ko48   | 58B081481FE9 | (601648FFC57A | A592D62BE8B3 | B3E810492910  |

Figure 3.3: FO Test Vectors Results

| <b></b> → /fl_tb/in32   | EA024714 | (03E715B9 | (161B54E1 | F9C83A1A  |

|-------------------------|----------|-----------|-----------|-----------|

| <b>.∓-∜</b> /fl_tb/kl32 | 57AC0B6E | X8B3E7EEF | (058B6BF0 | (6601F388 |

| → /fl_tb/out32          | 7CFFC314 | FC1913F5  | E9F55CF7  | (OEFDFA1A |

Figure 3.4: FL Test Vectors Results

Figure 3.5: KASUMI Test Vectors Results

25

# 3.3 Pipelined Implementations

In Section 3.1 and 3.2, we have explained how we obtained the combinational specification of KASUMI. In this section, we describe how the optimization technique of pipelining was used to create three pipelined implementations of KASUMI.

KASUMI was our first case study in exploring the verification strategy of completion functions at the RTL abstraction level. Therefore, we have used pipelining only to create three pipelined implementations of KASUMI, without any additional optimizations. For pure datapath circuits, the optimization technique of pipelining simply inserts registers at various locations of the implementation to divide the circuit into pipeline stages. In our second verification case study, we have explored the completion functions further by applying more sophisticated optimizations to the Welch-Gong cipher.

Since the KASUMI circuit is formed by eight rounds of FL and FO components, it was natural to insert registers at the beginning of each round so that all pipeline stages have an equal amount of gate delay. Thus, our first pipelined implementation of KASUMI consists of a 8-stage pipeline where the set of registers A are inserted at the beginning of each round of the cipher as shown in Figure 3.6. Note that both FL and FO are purely combinational circuits and that the set of registers B are not present in the 8-stage implementation of KASUMI. For our second pipelined implementation of KASUMI, we have further divided each pipeline stage of the 8-stage implementation into two pipeline stages by inserting the set of registers B between the FL and the FO components as shown in Figure 3.6. Thus, our second pipelined implementation has 16 stages in which each stage contains either the FLor the FO components. For our third pipelined implementation of KASUMI, we have divided the FO component of the 16-stage implementation of KASUMI into a 3-stage pipeline by inserting the set of registers C as depicted in Figure 3.7. Hence, our third pipelined implementation of KASUMI has 32 stages in which each stage contains either the FL or the FI components.

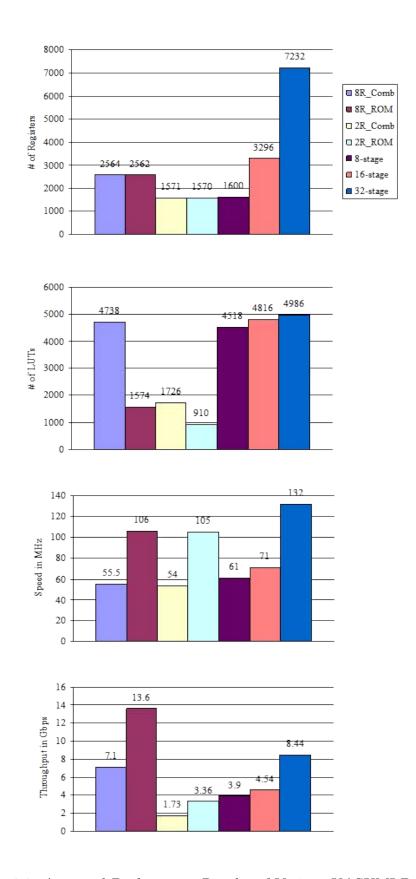

The area and performance of our pipelined implementations are shown in Figure 3.8, where LUT denotes lookup table. All of our area and performance results were synthesized on an Altera Stratix II series FPGA device EP2S15F484C using Mentor Graphics PrecisionRTL. Thus, our 8-stage implementation of KASUMI has an area of 4518 LUTs with a throughput of 3.9 Gbps. In Figure 3.8, we have included the latest(2005) optimized implementations of KASUMI by Kitsos *et al.* [11]. All of their implementations were synthesized onto the Xilinx FPGA device XCV300E-8BG432. Their four pipelined implementations are divided into two main

Figure 3.6: Registers Locations in KASUMI Figure 3.7: Registers Locations in FO

architectures: 8R and 2R. In the 8R architecture, Kitsos et al. [11] have defined each round of the KASUMI circuit to be a pipeline stage (similar to our 8-stage implementation). For the 2R architecture, the optimization of area re-use has been applied to reduce the number of pipline stages to two, where one stage is an odd round of KASUMI and the second stage is an even round of the cipher. Each of these two architectures are further divided into two different implementations, where Comb denotes that the FI component is implemented with combinational logic and ROM means that the FI block is implemented as lookup table with read-only memory (ROM). In Figure 3.8, both  $8R\_ROM$  and  $2R\_ROM$  require less LUTs for their implementations because their FI components are implemented with readonly memory.  $8R\_ROM$  uses 2752 bytes of read-only memory, and  $2R\_ROM$  uses 688 bytes of read-only memory. Finally, note that our 8-stage implementation has only half the throughput of the 8R\_Comb implementation. This difference is due to the fact that Kitsos et al. have used Double Edge Trigger (DET) pipelining in which the data are transferred between two successive registers in both rising and falling edges of the clock signal. For our pipelined implementations of KASUMI, we have used conventional single edge-triggered registers in which the data are transferred between two successive registers only at rising edges of the clock signal. Given the same circuit, replacing its single edge-triggered registers with double edge-triggered ones would double its throughput because data are processed at both rising and falling edges of the clock signal instead of being processed only at rising edges of the clock signal. In other words, a double edge-triggered pipeline would give two outputs per cycle (one at rising edge, one at falling edge of the clock signal) given that its single edge-triggered version produces one output per cycle.

In this section, we have provided descriptions of our pipelined implementations of KASUMI. Next section describes the verification methodology that we have applied with the verification of these three pipelined implementations.

# 3.4 Verification Methodology

In the verification of the three pipelined implementations of KASUMI, we have devised a set of guidelines in using the completion functions efficiently. This section describes our verification methodologies, and it is organized as follows. Section 3.4.1 provides the general steps of our verification, and a contrived example is used to show how completion functions are applied in our verification. Section 3.4.2 describes two important VHDL features used in our verification methodology. Section 3.4.3 shows how our methodology fits into a single entity design environment. Then, we show the advantages of our methodology by applying it to a multiple entities design environment in Section 3.4.4.

#### 3.4.1 General Guidelines

For the verification of our pipelined implementations of KASUMI, we have combined the verification technology of equivalence checking with the verification strategy of completion functions. A disadvantage of combinational equivalence checking is that it cannot verify pipelined implementations against a non-pipelined specification as it is limited to comparing the next-state equations of compare points based only on the combinational circuitry driving the points. By applying the verification strategy of completion functions with equivalence checking, pipelined implementations can be verified against its non-pipelined specification. The general outline of this verification has the following steps:

- 1. Create a first purely combinational implementation of the circuit as described in Section 3.1. This is usually also the first step in designing circuits.

- 2. Verify the correctness of the combinational implementation using suitable verification technologies and strategies as explained in Section 3.2. This ver-

Figure 3.8: Area and Performance Results of Various KASUMI Designs

- ified combinational implementation is used as the specification if there are additional optimized implementations of the same circuit to be verified.

- 3. Optimize the combinational implementation with optimization techniques such as pipelining or area re-use to achieve desired area/performance (described in Section 3.3).

- 4. For each pipeline stage of the optimized design, build its completion function such that it describes the effects on the programmer visible parts upon completing the instruction in that pipeline stage. Depending on which pipeline stage is under verification, the completion functions are either connected to the stage registers or to the outputs of the stage combinational circuitry. This is explained in this section.

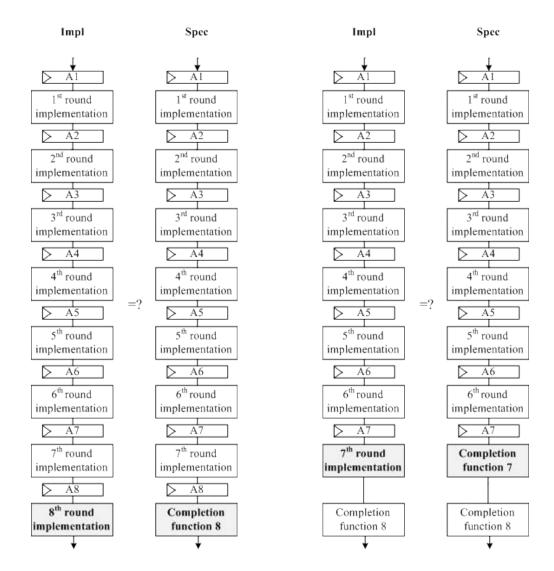

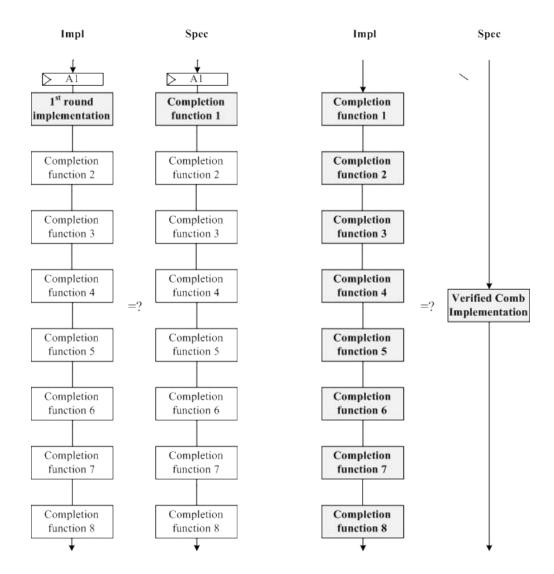

- 5. Using the completion functions, verify the optimized design stage-by-stage starting from the last pipeline stage. The verification of each pipeline stage requires one equivalence check. The optimized design is correct if the equivalence checker returns true when verifying the completion function of the first stage against the specification (verified purely combinational implementation). Therefore, there are n+1 verification obligations for a n-stage pipeline.

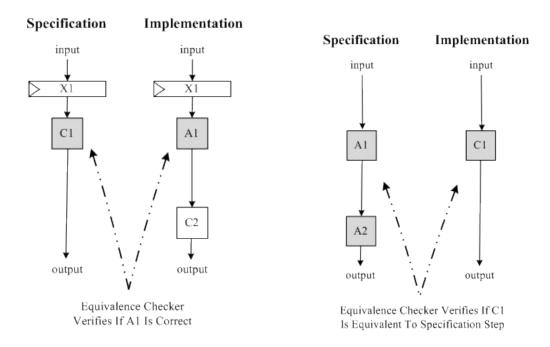

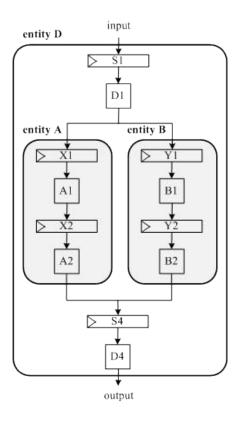

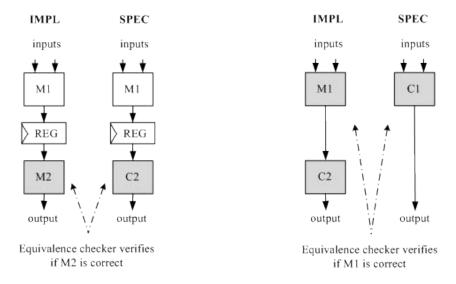

To demonstrate the last two steps of our methodology mentioned above, we have used the 2-stage verification example shown in Figure 3.9. Note that Figure 3.9 has already appeared in Section 2.2 for the general explanation of the completion functions approach that is used for the verification of the 2-stage implementation in Figure 2.2. This section describes the details of applying the completion functions approach in combination with equivalence checking.

The verification of our 2-stage contrived example in Figure 3.9 requires a total of three verification obligations. The first verification obligation  $VO_1$  is to verify the correctness of the last pipeline stage (i.e. second stage) with respect to the completion function  $C_2$  that describes the correct behaviour. Figure 3.10 illustrates the first equivalence check which corresponds to our first verification obligation  $VO_1$ . On the left hand side of Figure 3.10, the completion function  $C_2$  is connected to the stage registers  $X_2$  and emulates the effects of completing the instructions in the second pipeline stage. This corresponds to taking the register  $R_2$  from state "-" to state "A" (through completion function  $C_2$ ) in Figure 3.9. On the right hand side of Figure 3.10, the combinational block  $A_2$  is connected to the stage registers  $X_2$  and this circuit is the original pipelined implementation. This corresponds to taking the register  $R_2$  from state "-" to state "A" (through taking

Figure 3.9: 2-Stage Pipeline Verification Figure 3.10: First Verification Obligation Structure

an implementation step) in Figure 3.9. Note that the combinational block A2 of Figure 3.10 is viewed as the implementation step. Thus, the first equivalence check verifies if the combinational block A2 has the same behaviour as the completion function C2.

In Figure 3.9, the second verification obligation  $VO_2$  is used to verify the correctness of the first pipeline stage according to the behaviour given by the completion function  $C_1$ . Similarly, Figure 3.11 shows the equivalence check that is associated to our second verification obligation  $VO_2$ . On the left hand side of Figure 3.11, the effect of completing the instruction in the first stage is achieved by connecting the completion function of the first stage  $(C_1)$  to the stage registers  $X_1$ . This corresponds to taking the set of registers  $(R_1, R_2)$  from the state (A, -) to the state (B, B) (through completion function  $C_1$ ) in Figure 3.9. On the right hand side of Figure 3.11, the completion function of the second stage  $(C_2)$  is connected to the pipelined implementation through the outputs of the combinational block  $A_1$ . This corresponds to taking the set of registers  $(R_1, R_2)$  from the state (A, -) to the state (B, B) (through completion functions  $C_2$  and an implementation step) in Figure 3.9. Note that the combinational block  $A_1$  of Figure 3.11 is viewed as the implementation step in Figure 3.9. Hence, the second equivalence check verifies if

Figure 3.11: Second Verification Obliga-Figure 3.12: Third Verification Obligation tion

the combinational block A1 is correct with respect to the behaviour given by the completion function  $C_1$ .

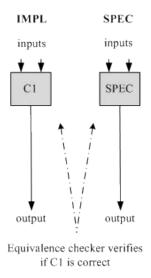

The previous two verification obligations  $(VO_1 \text{ and } VO_2)$  have verified both pipeline stages under the assumption that the completion functions are bug-free. Hence, the third verification obligation is to verify the correctness of the completion functions with respect to the specification. Figure 3.12 depicts the equivalence run for the third verification obligation. The equivalence checker verifies if the completion function of the first stage  $(C_1)$  is equivalent to the non-pipelined specification. In Figure 3.9, this corresponds to showing that the diagram commutes by proving that the completion function  $C_1$  is equivalent to the specification step. Thus, the verification of a 2-stage pipeline is completed with 3 verification obligations.

As mentioned earlier, different completion functions are connected to different locations of the circuit depending on the pipeline stage being verified. In our 2-stage contrived example, the completion function of the second stage  $C_2$  is connected to the stage register X2 for the verification of the second stage in Figure 3.10. For the verification of the first stage in Figure 3.11, the completion function  $C_2$  is connected to the outputs of the combinational block A1.

In VHDL, the process of connecting the completion functions to various registers can be cumbersome because the registers buried inside a VHDL entity cannot be

```

1 if <boolean condition> generate

2 ... hardware to be conditionally synthesized ...

3 end generate;

4 ... hardware to be synthesized ...

```

Figure 3.13: If-Generate Statement

accessed without declaring additional output ports. It is undesirable to have all the completion functions synthesized during equivalence checking because it would increase the size of the circuit being compared. Therefore, there is a need for a methodology to efficiently control the completion functions in VHDL. This can be achieved by a combination of the "if-generate" statements and the "generic" parameters in VHDL, which are introduced in the next subsection.

## 3.4.2 Background of VHDL Features

This subsection provides the background of two important VHDL features, ifgenerate statements and generic parameters, used as part of our verification methodology. Section 3.4.3 and 3.4.4 illustrate how these two VHDL features are applied with our verification methodology.

If-generate statements are evaluated at elaboration time to conditionally create some hardware, and they are similar to #ifdef in C. Figure 3.13 shows some VHDL code fragments which include the if-generate statement. Line 1-3 of Figure 3.13 is the general structure of an if-generate statement. Line 2 is the body of the if-generate statement, and its hardware is generated if the boolean condition of line 1 is true. All VHDL codes outside the scope of the if-generate statements are synthesized into actual hardware as shown on line 4 of Figure 3.13. The boolean condition controls which completion function to be synthesized and how they would be connected to the circuit depending on the pipeline stage under verification. The VHDL generic parameters can be used as control parameters, and they are introduced next.

Generic parameters are evaluated at elaboration time, and they are analogous to #define in C. Generic parameters are constant values and they are declared as part of a VHDL entity declaration as shown in Figure 3.14. Unlike the port parameters of line 3 in Figure 3.14, the generic parameters of line 2 are not actual ports of the circuit and they would not be synthesized into any additional signals or hardware. Generic parameters are commonly used to modify the bit width of

```

1 entity <entity name> is

2 generic( ... list of generic parameters ...);

3 port( ... list of input and output ports ...);

4 end entity;

```

Figure 3.14: Generic Parameters

an implementation, such as the bit width of an adder, during hardware synthesis. Generic parameters can only be assigned as constant values. A common pitfall in using generic parameters is to assign constant signals to generic parameters. However, the VHDL compiler interprets the "signal" type to have dynamic values that can be modified during circuit operation. Generic parameters can help the verification engineer to manage the completion functions in VHDL as part of the boolean condition. Our methodology in using completion functions efficiently in VHDL is described next.

## 3.4.3 Single Entity Environment

This subsection explains our verification methodologies and recommendations in the application of completion functions in equivalence checking at the register transfer level.

In using the verification strategy of completion functions for the equivalence checking of pipelined implementations against its non-pipelined specification, the first step is to build the completion functions for each pipeline stage. We recommend the circuit designers to include the completion functions for each pipeline stage with their implementation because writing the completion functions requires an indepth knowledge about the circuit operation and the designers already have that information. If the verification engineers are to build the completion functions, additional time resources would be spent on understanding the detailed circuit operation.

The completion functions are built for verification purpose only and should not be synthesized into actual hardware as part of the implementation. Only the associated completion functions and wire connections should be generated for its associated pipeline stage equivalence run because it saves time and memory resources. To avoid synthesizing additional hardware, we recommend the use of if-generate statements with boolean conditions formed by two suggested generic parameters: stage and spec.

stage is an integer used to specify which stage of a pipelined entity is under verification, and the associated completion functions are exclusively synthesized with if-generate statements. spec is a binary digit used to indicate whether the specification or the implementation is synthesized with if-generate statements during the equivalence checking of a pipeline stage as shown in Figure 3.10 to 3.12. In other words, spec specifies whether the associated completion functions are connected to the stage registers or to the outputs of a combinational block.