## **NOTE TO USERS**

This reproduction is the best copy available.

**UMI**

## A Formal Framework for Modeling and Testing Memories

by

Piotr Roald Sidorowicz

A thesis

presented to the University of Waterloo

in fulfilment of the

thesis requirement for the degree of

Doctor of Philosophy

in

Computer Science

Waterloo, Ontario, Canada, 2000

(c)Piotr Roald Sidorowicz 2000

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre référence

Our file Notre rélérence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-51227-4

The University of Waterloo requires the signatures of all persons using or photocopying this thesis. Please sign below, and give address and date.

#### Abstract

Testing is essential to VLSI circuit production. In the case of memory circuits, the cost of testing often exceeds the cost of manufacture. Current memory testing methods rely on fault models that are inadequate to accurately represent potential defects that occur in modern, often specialized, memories.

We present a formal framework for modeling and testing memories. Simple fault models are created, based on potential circuit-level defects in a given memory. This framework is demonstrated using a content-addressable memory (CAM) as an example. CAMs are used in integrated circuits where searching is a key operation.

A CAM cell is analyzed at the transistor-network, event-sequence and finite-state machine levels. A fault model is defined: it comprises input stuck-at, transistor and bridging faults. We show that functional tests can reliably detect all input stuck-at faults, most transistor faults (including all stuck-open faults), and about  $50^{\circ}_{0}$  of bridging faults. The remaining faults are detectable by parametric tests. A test, of length 7n + 2l + 9, that detects all the reliably testable faults in an n-word by l-bit CAM was designed. DFT suggestions that reduce the length of this test to 2l + 11 are proposed. Two CAM tests, by Giles & Hunter and by Kornachuk et al., are evaluated with respect to the input stuck-at faults. It is shown that the former test fails to detect certain faults: it can be modified to achieve full coverage at the cost of increased length.

To demonstrate the general applicability of our framework, an input stuck-at fault model of a word-oriented, static random-access memory (SRAM) is also given. Several commonly known tests are evaluated; some fail to detect close to 50% of faults in this model.

#### Acknowledgements

I would like to thank my supervisor, Dr. Janusz (John) Brzozowski for his support and guidance. His commitment to his work and to his students, attention to detail and professional standards are without equal; they will always remain a source of inspiration for me. I am very grateful to him.

I am thankful to the other members of my defence committee, Drs. Helmut Jürgensen. Mike McCool, Manoj Sachdev, Johnny Wong, and Yervant Zorian, for the time spent on reading my thesis and for all the valuable comments and suggestions.

Sincere thanks go to Dr. Kenneth Schultz, formerly of Nortel Corporation's Memory Development Team, for providing extensive information regarding various defects and their effects on a CAM.

I would like to express my gratitude to the all the members of the Maveric Group. particularly to Drs. Robert Berks. Tracey Bogue, and Radu Negulescu for their insightful comments and suggestions.

Many day-to-day tasks would have become bureaucratic nightmares, if it were not for the wonderful support and assistance of the members of the departmental staff, particularly of Debbie Mustin, Jane Prime, Wendy Rush and Ursula Thoene. Thank you for all your help.

I am grateful to my fiancée Ewa Madey for her patience, love, understanding, and for always being there for me.

Finally, I would like to acknowledge the support of the Natural Sciences and Engineering Research Council of Canada under grant No. OGP0000871.

#### **Dedication**

To my late grandparents. Irena and Lucjan, whose love, guidance and understanding have always made such a difference in my life. Wish you were here. Then again, you probably are...

## Contents

| 1 | Inti | roduction                      | 1  |

|---|------|--------------------------------|----|

| 2 | ting | 4                              |    |

|   | 2.1  | Logical Testing                | 4  |

|   | 2.2  | Scan Test                      | 9  |

|   | 2.3  | Summary                        | 11 |

| 3 | Mei  | mory Testing                   | 12 |

|   | 3.1  | RAM Test Classification        | 12 |

|   | 3.2  | Design-Oriented Fault Modeling | 16 |

|   | 3.3  | Summary                        | 17 |

| 4 | For  | mal Models                     | 18 |

|   | 4.1  | Memory Models                  | 19 |

|   | 4.2  | Classic Fault Models           | 20 |

|   | 4.3  | Observer                       | 22 |

|   | 4.4  | Diagnosing Languages           | 24 |

|   | 4.5  | Lower Bounds                   | 25 |

|   | 4.6  | Summary                        | 26 |

| 5 | $\mathbf{C}\mathbf{A}$ | M Fundamentals                   | 27         |

|---|------------------------|----------------------------------|------------|

|   | 5.1                    | Overview of CAM Architecture     | 29         |

|   | 5.2                    | Static CAM Cell Circuits         | 30         |

|   | 5.3                    | Dynamic CAM Cell Circuits        | 34         |

|   | 5.4                    | Summary                          | 36         |

| 6 | Sur                    | vey of CAM Tests                 | 37         |

|   | 6.1                    | Giles and Hunter (1985)          | 38         |

|   | 6.2                    | Mazumder et al. (1987)           | 39         |

|   | 6.3                    | Kornachuk et al. (1994)          | 42         |

|   | 6.4                    | Al-Assadi et al. (1994)          | 45         |

|   | 6.5                    | Lin and Wu (1998)                | 48         |

|   | 6.6                    | Summary                          | 51         |

| 7 | CA                     | M Model                          | 52         |

|   | 7.1                    | Fault-free Cell                  | 55         |

|   |                        | 7.1.1 Event-Sequence Model       | 55         |

|   |                        | 7.1.2 FSM Model                  | <b>5</b> 9 |

|   | 7.2                    | Input Stuck-at Faults            | 60         |

|   | 7.3                    | State Stuck-at Faults            | 64         |

|   | 7.4                    | Transistor On/Open Faults        | 66         |

|   | 7.5                    | Bridging Faults                  | 70         |

|   |                        | 7.5.1 Intra-cell Bridging Faults | 71         |

|   |                        | 7.5.2 Inter-cell Bridging Faults | 72         |

|   | 7.6                    | Summary                          | 75         |

| 8  | Dev  | relopment of a CAM Test                     | 78  |

|----|------|---------------------------------------------|-----|

|    | 8.1  | Test for a Single Cell                      | 79  |

|    | 8.2  | Extension to n-word by 1-bit CAM            | 80  |

|    |      | 8.2.1 Testing the w-sa-1 fault              | 82  |

|    |      | 8.2.2 Complete Test for n-word by 1-bit CAM | 82  |

|    | 8.3  | Extension to a 1-word by l-bit CAM          | 83  |

|    | 8.4  | Extension to n-word by l-bit CAM            | 85  |

|    | 8.5  | DFT Suggestions                             | 87  |

|    | 8.6  | Summary                                     | 88  |

| 9  | Eva  | luation of CAM Tests                        | 89  |

|    | 9.1  | Giles and Hunter Test                       | 90  |

|    | 9.2  | Kornachuk et al. Test                       | 94  |

|    | 9.3  | Summary                                     | 98  |

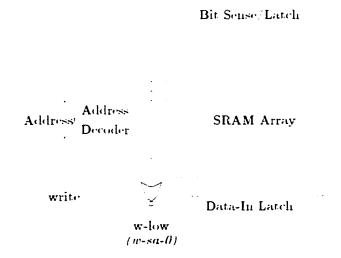

| 10 | SRA  | AM Testing                                  | 99  |

|    | 10.1 | Analysis of an SRAM Cell                    | 100 |

|    |      | 10.1.1 SRAM Cell Circuit                    | 100 |

|    |      | 10.1.2 Event-Sequence Model                 | 101 |

|    |      | 10.1.3 FSM Model                            | 103 |

|    | 10.2 | Input Stuck-at Faults in an SRAM Cell       | 104 |

|    |      | 10.2.1 Extension to n-word by 1-bit SRAM    | 107 |

|    |      | 10.2.2 Extension to a 1-word by l-bit SRAM  | 109 |

|    |      | 10.2.3 Extension to n-word by l-bit SRAM    | 109 |

|    | 10.3 | Evaluation of Tests                         | 10  |

|    |      | 10.3.1 Evaluation of the Mats+ test         | 10  |

|    |      | 10.3.2 Evaluation of the Mars++ test        | 13  |

|    |       | 10.3.3  | Evaluation of the MARCH Y test   | 113 |

|----|-------|---------|----------------------------------|-----|

|    |       | 10.3.4  | Evaluation of the MARCH C- test  | 114 |

|    | 10.4  | DFT S   | Suggestions                      | 114 |

|    | 10.5  | Summ    | ary                              | 115 |

| 11 | Con   | clusior | 18                               | 116 |

|    | 11.1  | Review  | 7                                | 116 |

|    | 11.2  | Contri  | butions                          | 120 |

|    | 11.3  | Future  | Work                             | 121 |

| A  | CA    | M Faul  | t Analysis and Test Verification | 122 |

|    | A.1   | CAM I   | Fault Analysis                   | 122 |

|    |       | A.1.1   | Input Stuck-at Faults            | 123 |

|    |       | A.1.2   | State Stuck-at Faults            | 127 |

|    |       | A.1.3   | Transistor Faults                | 128 |

|    |       | A.1.4   | Bridging Faults                  | 134 |

|    | A.2   | CAM 7   | Test Verification                | 145 |

| В  | SRA   | M Fau   | ult Analysis and Test Evaluation | 147 |

|    | B.1   | SRAM    | Fault Analysis                   | 147 |

|    | B.2   | SRAM    | Test Evaluation                  | 150 |

|    |       | B.2.1   | Evaluation of the MATS++ test    | 150 |

|    |       | B.2.2   | Evaluation of the MARCH Y test   | 152 |

|    |       | B.2.3   | Evaluation of the MARCH C- test  | 154 |

| Bi | bliog | raphy   |                                  | 157 |

# List of Figures

| 2.1        | External stuck-at fault model for: (a) gate, (b) fork             | 6          |

|------------|-------------------------------------------------------------------|------------|

| 2.2        | Output stuck-at fault model for: (a) gate, (b) fork               | G          |

| 2.3        | Activation and propagation of faults                              | 6          |

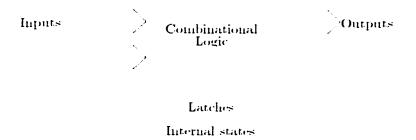

| 2.4        | Sequential circuit overview                                       | 8          |

| 2.5        | Arbitrary sequential circuit                                      | 9          |

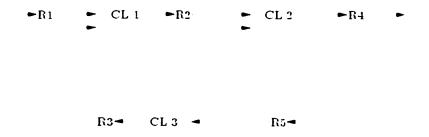

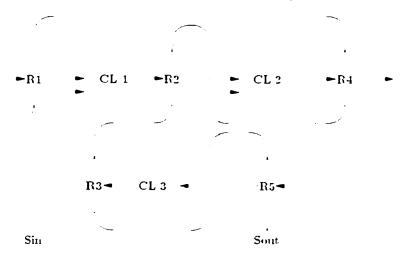

| 2.6        | Scan Test design.                                                 | 9          |

| <b>-</b> , |                                                                   | 20         |

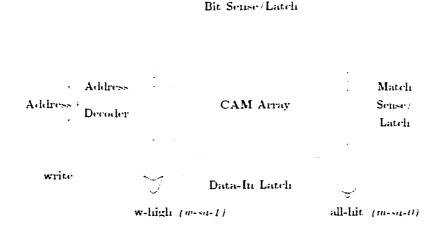

| 5.1        | CAM: a block diagram.                                             | 29         |

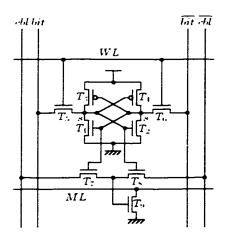

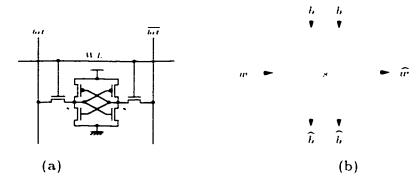

| 5.2        | CMOS implementations of a single-port static CAM cell             | 31         |

| 5.3        | Dual-port static CAM cell                                         | 33         |

| 5.4        | Dynamic CAM cell designs. (a) Wade. (b) Yamagata                  | 34         |

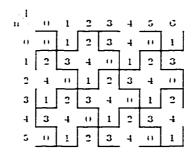

| 6.1        | Cell number assignment [34]                                       | 40         |

| 7.1        | Dual-port static CAM cell with dedicated compare lines            | 53         |

| 7.2        | Two neighboring CAM cells                                         | 54         |

| 7.3        | Model of the CAM cell of Fig. 7.1                                 | 55         |

| 7.4        | Model of two neighboring CAM cells                                | 58         |

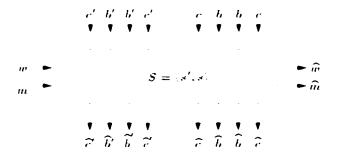

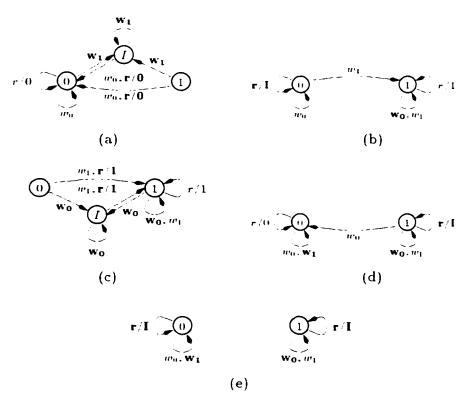

| 7.5        | (a) Simplified behavioral model (b) Behavior of a fault-free cell | <b>5</b> 9 |

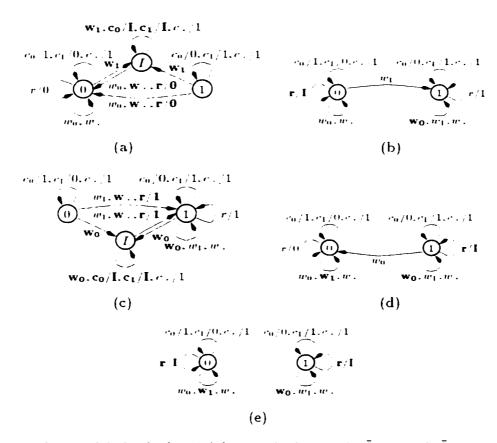

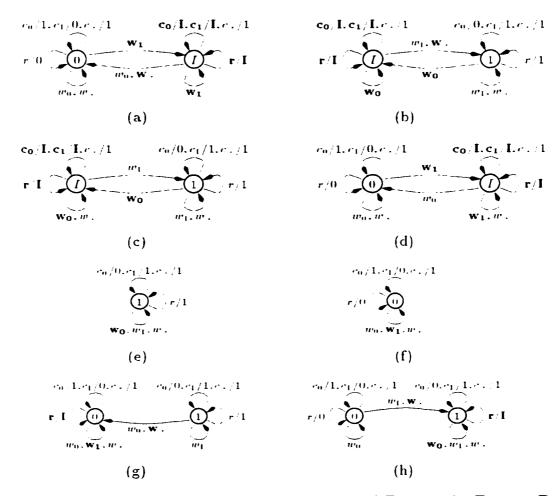

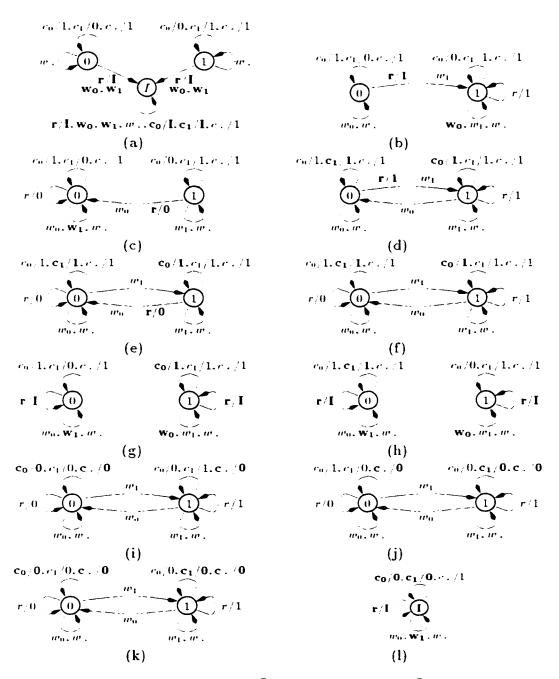

| 7.6  | FSM models for faults: (a) $b$ -sa-0, (b) $b$ -sa-1, (c) $\bar{b}$ -sa-0, (d) $\bar{b}$ -sa-1, (e) $w$ -                 |            |

|------|--------------------------------------------------------------------------------------------------------------------------|------------|

|      | sa-0                                                                                                                     | 62         |

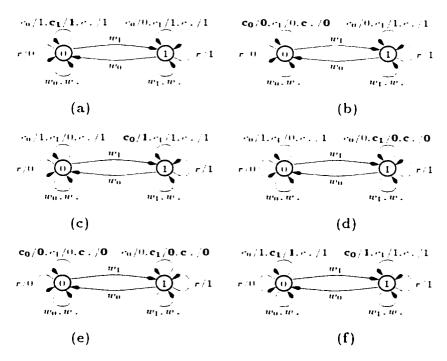

| 7.7  | FSM models for faults: (a) $c$ -sa-0, (b) $c$ -sa-1, (c) $\bar{c}$ -sa-0, (d) $\bar{c}$ -sa-1, (e) $m$ -                 |            |

|      | sa-0, (f) m-sa-1                                                                                                         | 63         |

| 7.8  | C'ell behavior: (a) correct. (b) s-sa-0                                                                                  | 65         |

| 7.9  | FSM models for faults: (a) $s$ - $sa$ - $0$ and $\bar{s}$ - $sa$ - $1$ , (b) $s$ - $sa$ - $1$ and $\bar{s}$ - $sa$ - $0$ | 65         |

| 7.10 | Cell behavior: (a) correct, (b) T <sub>7</sub> -on                                                                       | 67         |

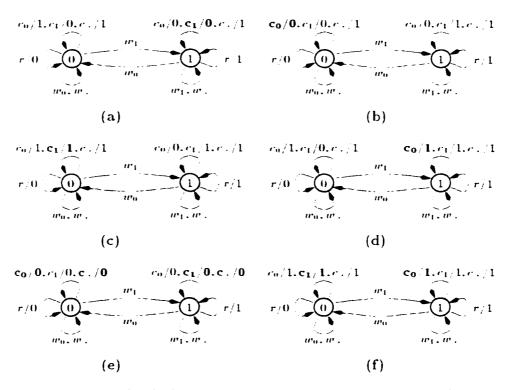

| 7.11 | FSM models for faults: (a) $T_1$ -on, $T_2$ -open and $T_3$ -open. (b) $T_1$ -open. $T_2$ -                              |            |

|      | on and $T_3$ -on. (c) $T_3$ -on. (d) $T_4$ -on, (e) $T_5$ -on, (f) $T_6$ -on. (g) $T_5$ -open. (h)                       |            |

|      | $T_{G}$ -open                                                                                                            | 69         |

| 7.12 | FSM models for faults: (a) $T_7$ -on, (b) $T_8$ -on, (c) $T_7$ -open, (d) $T_8$ -open, (e)                               |            |

|      | $T_{\mathfrak{I}}$ -on, (f) $T_{\mathfrak{I}}$ -open                                                                     | 70         |

| 7.13 | C'ell behavior: (a) correct, (b) c-c̄-hrd                                                                                | 72         |

| 7.14 | Behavior of two adjacent CAM cells: (a) correct, (b) $\bar{c}'$ -c-hrd                                                   | <b>7</b> 3 |

| 7.15 | FSM models for faults: (a) $b-\bar{b}-hrd$ , (b) $b-w-hrd$ , (c) $\bar{b}-hrd$ , (d) $b-m-hrd$ . (e)                     |            |

|      | $\bar{b}$ -m-hrd, (f) c- $\bar{c}$ -hrd, (g) c-w-hrd, (h) $\tilde{c}$ -w-hrd, (i) c-m-hrd and c-m-res, (j)               |            |

|      | $\bar{c}$ -m-hrd and $\bar{c}$ -m-res. (k) m-w-hrd and m-w-res. (l) s- $\bar{s}$ -hrd                                    | 74         |

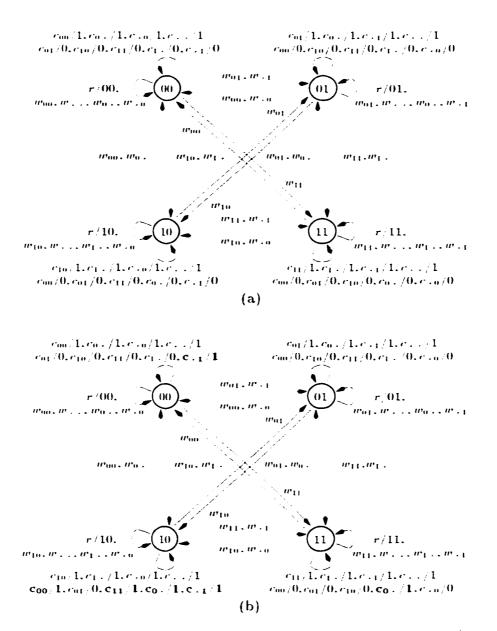

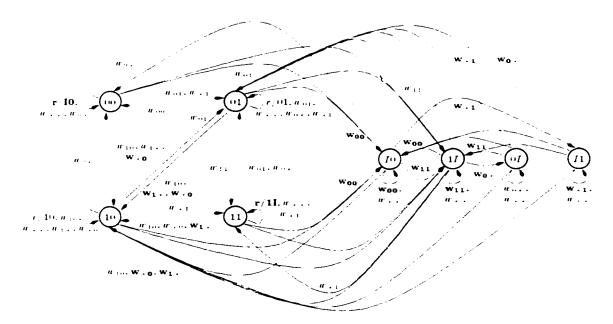

| 7.16 | FSM model: inter-cell $\bar{b}'$ -b-hrd bridging fault                                                                   | 76         |

| 8.1  | DFT suggestions                                                                                                          | 87         |

| 10.1 | (a) SRAM cell, (b) its model                                                                                             | 100        |

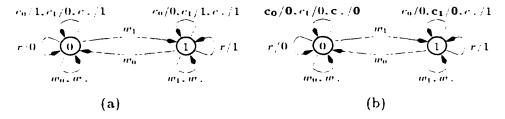

| 10.2 | (a) Simplified behavioral model (b) Behavior of a fault-free SRAM cell                                                   | 103        |

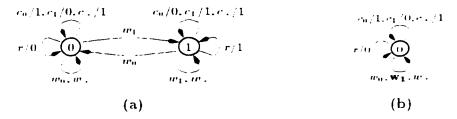

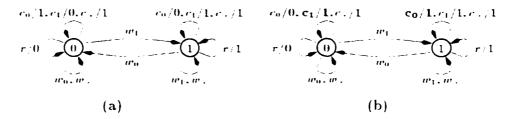

| 10.3 | Faulty behaviors of an SRAM cell: (a) $b$ -sa-0, (b) $b$ -sa-1, (c) $\bar{b}$ -sa-0, (d) $\bar{b}$ -                     |            |

|      | sa-1, (e) w-sa-0                                                                                                         | 105        |

| 10.4 | DFT suggestions                                                                                                          | 114        |

## List of Tables

| 3.1 | Comparison of memory tests for n-bit RAMs [20]                 | 14 |

|-----|----------------------------------------------------------------|----|

| 4.1 | Lower bounds and known test lengths for faults in n-bit RAMs   | 25 |

| 6.1 | Example of test algorithm by Giles and Hunter                  | 39 |

| 6.2 | Test patterns used in the algorithm by Mazumder et al. [34]    | 41 |

| 6.3 | CAM BIST March Element [31]                                    | 44 |

| 6.4 | Behavior of the CAM cell under storage cell faults [4]         | 46 |

| 6.5 | Faults in the comparison logic of a CAM cell [4]               | 47 |

| 6.6 | Functional fault model for the CAM cell [4]                    | 48 |

| 7.1 | Read, write and compare operations in a fault-free CAM cell    | 57 |

| 7.2 | A 'write 0' operation in a correct and faulty CAM cell         | 61 |

| 7.3 | Summary of input stuck-at faults                               | 64 |

| 7.4 | Summary of state stuck-at faults                               | 66 |

| 7.5 | A 'compare 1' operation in a correct and faulty CAM cell       | 67 |

| 7.6 | Summary of transistor faults                                   | 68 |

| 7.7 | A 'compare 1' operation in a correct and faulty CAM cell       | 71 |

| 7.8 | A 'compare +1' operation in a correct and faulty CAM cell pair | 75 |

| 7.9 | Summary of intra- and inter-cell bridging faults.              | 77 |

| 8. | Summary of elementary tests for a CAM                                | 79  |

|----|----------------------------------------------------------------------|-----|

| 10 | 1 Read and write operations in a fault-free SRAM cell                | 102 |

| 10 | 2 Summary of input stuck-at faults and elementary tests              | 106 |

| 10 | 3 Evaluation of the MATS+ test for a single cell                     | 111 |

| Α. | Faulty CAM cell behavior due to the b-sa-0 fault                     | 123 |

| Α. | 2 Faulty CAM cell behavior due to the b-sa-1 fault                   | 124 |

| Α. | B Faulty CAM cell behavior due to the w-sa-0 fault                   | 124 |

| Α. | Faulty CAM cell behavior due to the c-sa-0 fault                     | 125 |

| Α. | Faulty CAM cell behavior due to the c-sa-1 fault                     | 125 |

| Α. | Faulty CAM cell behavior due to the m-sa-0 fault                     | 126 |

| Α. | Faulty CAM cell behavior due to the m-sa-1 fault                     | 126 |

| Α. | Faulty CAM cell behavior due to the s-sa-0 fault                     | 127 |

| Α. | Faulty CAM cell behavior due to the s-sa-1 fault.                    | 127 |

| Α. | .0 Faulty CAM cell behavior due to the $T_1$ -on fault.              | 128 |

| Α. | .1 Faulty CAM cell behavior due to the $T_1$ -open fault             | 129 |

| A. | $2$ Faulty CAM cell behavior due to the $T_3$ -on fault              | 129 |

| Α. | .3 Faulty CAM cell behavior due to the $T_3$ -open fault             | 130 |

| Α. | 4 Faulty CAM cell behavior due to the $T_5$ -on fault                | 131 |

| Α. | 5 Faulty CAM cell behavior due to the $T_5$ -open fault              | 131 |

| Α. | 6 Faulty CAM cell behavior due to the $T_7$ -on fault                | 132 |

| Α. | 7 Faulty CAM cell behavior due to the $T_7$ -open fault              | 132 |

| A. | 8 Faulty CAM cell behavior due to the $T_0$ -on fault                | 133 |

| Α. | 9 Faulty CAM cell behavior due to the T <sub>0</sub> -open fault     | 133 |

| A. | 20 Faulty CAM cell behavior due to the $b$ - $\bar{b}$ - $hrd$ fault | 134 |

| Α. | 21 Faulty CAM cell behavior due to the b-w-hrd fault.                | 135 |

| A.22 | Faulty CAM cell behavior due to the b-m-hrd fault                                | 135 |

|------|----------------------------------------------------------------------------------|-----|

| A.23 | Faulty CAM cell behavior due to the c-c̄-hrd fault                               | 136 |

| A.24 | Faulty CAM cell behavior due to the m-w-hrd fault.                               | 137 |

| A.25 | Faulty CAM cell behavior due to the c-w-hrd fault                                | 138 |

| A.26 | Faulty CAM cell behavior due to the c-m-hrd fault                                | 139 |

| A.27 | Faulty CAM cell behavior due to the $s$ - $\bar{s}$ - $hrd$ fault                | 140 |

| A.28 | Faulty 'read' behavior due to the $\tilde{b}'$ -b-hrd fault                      | 141 |

| A.29 | State-independent faulty 'write' behavior due to the $\bar{b}'$ -b-hrd fault     | 141 |

| A.30 | State-specific faulty 'write' behavior due to the $\bar{b}'$ - $b$ - $hrd$ fault | 142 |

| A.31 | Faulty CAM cell pair behavior due to the $\bar{c}'$ -c-hrd fault                 | 143 |

| A.32 | Faulty CAM cell behavior due to the $b-\bar{b}-res$ fault                        | 144 |

| A.33 | Faulty CAM cell behavior due to the m-w-res fault                                | 144 |

| A.34 | Faulty CAM cell behavior due to the c-m-res fault                                | 145 |

| A.35 | Verification of the $T_{c\epsilon ll}$ test                                      | 146 |

| B.1  | Faulty SRAM cell behavior due to the b-sa-0 fault                                | 148 |

| B.2  | Faulty SRAM cell behavior due to the b-sa-1 fault                                | 149 |

| B.3  | Faulty SRAM cell behavior due to the w-sa-0 fault                                | 149 |

| B.4  | Evaluation of the Mats++ test for a single cell                                  | 151 |

| B.5  | Evaluation of the MARCH Y test for a single cell                                 | 153 |

| B.6  | Evaluation of the MARCH C- test for a single cell.                               | 155 |

### Chapter 1

### Introduction

"If you don't test it, it won't work! Guaranteed." [54]

This adage embodies the undisputed necessity of testing. Particularly, in the realm of VLSI circuits where millions of devices are located in an area of approximately 1 cm<sup>2</sup> and no fabrication method, no matter how meticulous, can guarantee perfect results, testing is an essential and integral part of the production process. There are numerous reasons for VLSI circuit failure. During chip fabrication, defective silicon substrate, improper doping, mask misalignments or imperfections, contamination with dust particles, or etching flaws may result in outright faulty devices, or devices which fail soon after being put into operation. Even correctly operating chips may, in time, fail due to electro-migration, oxidation, corrosion, or mechanical stress. Moreover, such aging processes can be accelerated by extreme environmental conditions. It is, therefore, necessary to test integrated circuits throughout their life-cycle, from fabrication to in-service maintenance.

Memory circuits constitute a large part of all integrated circuit production. High bit-densities of modern memory chips render them particularly prone to failure, thus magnifying the need for thorough testing methods that are efficient enough to be economically justifiable. Not surprisingly, a substantial research effort has been devoted to testing random-access memories (RAMs). The development and utilization of fault models for RAMs has led to qualitative comparisons among existing testing methods. It also facilitated the construction of more efficient testing methods and the establishment of lower bounds on the lengths of test sequences for various faults.

As technologies and cell designs change and as the circuits become smaller, it is no longer clear if fault models designed some ten years ago are still applicable to the memories of today. This is particularly true for special-purpose memories that incorporate additional, non-standard circuitry. Although new tests for these memories are being developed [21], the approach taken is still rather ad-hoc, and results in an ever increasing number of highly abstract fault models, completely detached from the design and the technology for which they were developed.

In this thesis we demonstrate the need for establishing simple formal fault models that are created for specific memory cell designs. As a representative of a special-purpose memory we chose a CAM, a word-oriented storage device that is being utilized increasingly often in digital designs for its parallel search abilities. Although CAMs have been known since the sixties, their higher complexity and cost effectively excluded them from use by the digital systems industry. By the same token, research devoted to testing CAMs has also been limited. Today, due to the never-ending quest for increased processing power and advancement in VLSI technology, CAMs are usually found embedded in various high performance application-specific integrated circuits (ASICs).

We have developed a cell-specific fault model based on a transistor circuit of a static CMOS CAM cell utilized by Nortel Corporation in their telecommunication ASICs. We have found that only a fraction of the faults that can occur in the CAM cell do, indeed, correspond to the well-established fault types such as *cell stuck-at* faults.

Our fault model provides a basis for comparisons among test methods currently used

for testing CAMs in terms of coverage of faults that are specific to a particular CAM cell circuit design. It provides a precise mathematical foundation for determining shortest test sequences for various faults in the model. Short test sequences are particularly relevant to embedded memories, where testing is accomplished by built-in self test (BIST) schemes.

By applying our formal framework for fault modeling, test generation and evaluation to an SRAM cell we demonstrate that our approach can be easily applied to any type of memory.

The remainder of this thesis is organized as follows: General issues regarding testing are discussed in Chapter 2. Chapter 3 is devoted to common methodologies used for testing random access memories. Formal memory models are described in Section 4. CAM fundamentals are the topic of Section 5. A survey of existing CAM tests is given in Chapter 6. Section 7 presents the formal model of the three types of faults contained in our fault model. The development of an efficient CAM test is described in Chapter 8. An evaluation of some of the CAM tests of Chapter 6 is presented in Chapter 9. An application of the framework to an SRAM circuit is given in Chapter 10. Chapter 11 contains concluding remarks and future areas of investigation.

### Chapter 2

## Testing

The goal of testing is to distinguish good circuits from malfunctioning ones. A more detailed analysis leading to localization of the cause of a malfunction is known as diagnosis; hence, testing is only a part of a diagnostic process.

Digital electronic circuits may be tested in several ways. The analysis of various electrical properties, such as voltages, currents, noise, power dissipation, etc. is called parametric testing. Another approach to testing digital integrated circuits relies on a comparison of the behavior of the circuit to its functional specification without any regard for the structural implementation of the circuit. This type of analysis is referred to as functional testing. The study of how deviations in the structural implementation of a circuit may affect its logical functionality is called logical testing. Our efforts concentrate on the last approach.

#### 2.1 Logical Testing

Any time a circuit's behavior deviates from that prescribed by its specification, we say that the circuit is malfunctioning, or that an error has occurred. Every error is the

result of some physical defect or design miscalculation. A variety of different physical defects may occur in a circuit. Severed connections, shorts to ground or to supply voltage  $V_{dd}$ , any flaws caused by improper masking, or poor semiconductor doping during the manufacturing process, even an incorrect design, are all considered defects.

The large number of diverse physical defects renders any circuit analysis in terms of these defects impractical. It is much easier to analyze circuits in terms of faults. A fault is a term used to describe a group of physical defects which manifest themselves in the same way. For example, let us consider a group of defects that cause a node in a circuit to be permanently connected to a high voltage. Such a node can be referred to as being subject to a stuck-at-1 fault. Stuck-at-1 and stuck-at-0 faults are the best known and the most commonly analyzed faults. If under certain input conditions a fault causes an erroneous output value, the given fault is called detectable. Some faults are not detectable, which means that there are physical defects that do not cause a circuit to malfunction, but affect its performance. Other faults manifest themselves only if the circuit is tested at speeds approaching its design extrema; they are referred to as dynamic faults.

Logical testing of digital circuits is performed by applying a sequence of logical values to the circuit's input ports and observing the resulting output. If the output differs from the expected one, a fault is detected.

The nature of a fault determines the fault model; in case of stuck-at faults, the stuck-at fault model. In order to reflect faults of a different nature — for example, transistor stuck-on(open) or bridging faults — appropriate fault models have to be defined. This is particularly important in the case of CMOS circuits where certain defects may convert a combinational circuit into a sequential one or may cause the circuit to generate logically indeterminate output. Sequential behavior of a faulty combinational circuit can be detected by an application of an appropriate sequence of test patterns. Faults that cause logically indeterminate output, on the other hand, are often detectable by parametric

tests.

One well known fault model is the external stuck-at fault model. It describes faults that may cause inputs as well as outputs of a gate to be permanently set to logic 0 or logic 1. The definition of this fault model has facilitated reasoning about forks as separate entities within the circuit, with their own respective faults [25]. Figure 2.1 depicts locations of faults for the external stuck-at fault model.

Figure 2.1: External stuck-at fault model for: (a) gate, (b) fork.

A simpler, output stuck-at fault model considers only those faults that occur on outputs of gates, thus effectively, on inputs of forks. Locations of faults for the output stuck-at fault model are presented in Fig. 2.2.

Figure 2.2: Output stuck-at fault model for: (a) gate, (b) fork.

It is clear that digital circuits need to be tested in terms of an appropriate fault model. The fact that not all faults (for a given fault model) are detectable in a particular circuit brings about the issue of testability. A circuit is completely testable if every fault in a given fault model can be detected. Detection of a fault requires that it be activated and the resulting error propagated. Consider the circuit in Fig. 2.3. The fault Z = Sa-1 is said

$$\begin{array}{ccc} A & & & Z = Sa - 1 \\ B & & & & \end{array}$$

Figure 2.3: Activation and propagation of faults.

to be activated when input A of the circuit is set to logic 1. Consequently, node Z is set to logic 0 in a fault-free circuit. This process is often referred to as fault sensitization. In effect an erroneous input value is presented on the upper input to the AND gate. This error will be propagated to the output F when input B is set to logic 1. Therefore, fault Z = Sa-1 is detectable because, for the input vector AB = 11, a fault-free circuit would produce a 0 on the output, whereas the faulty circuit yields a 1. In this case it can be said that the node Z can be controlled and observed. Clearly, testability of a circuit is determined by the observability and controllability of all its internal nodes. A comprehensive study of these issues can be found in [1].

Let us now look at the testability of circuits under the stuck-at fault model.

Digital circuits are classified as either combinational or sequential. The issue of testing combinational circuits is a well studied one [1, 17]. The simplest circuits to test are the fan-out free circuits, such as the one presented in Fig. 2.3. The reason for this simplicity can be explained by following Theorem [8]:

"In fanout-free circuits (i.e., circuits where each primary input and each gate output are inputs to at most one gate), there exists a single stuck fault test set of minimal cardinality which detects all multiple stuck faults."

Unfortunately, most combinational circuits contain reconvergent fan-out, which means that an arbitrary fault could be activated, and the resulting error propagated through multiple paths. It may also be the case that coherent input values can be determined for detection of a particular fault only for a subset of possible paths. The selection of appropriate paths is done algorithmically. Many such algorithms have been developed for testing for stuck-at faults. These algorithms include the D-algorithm. Podem, Fan, etc.

Testing of sequential circuits is a different matter. Consider the circuit of Fig. 2.4. The next state of this sequential circuit depends on the present input values and on the

Figure 2.4: Sequential circuit overview.

current internal state of the circuit. A common way of testing a sequential circuit is to visualize it as testing a series of combinational circuits which in addition to inputs and outputs from the sequential circuit, have additional inputs denoting the current state, and additional outputs denoting the next state of the sequential circuit. Unfortunately, the internal state is often not observable and its controllability is limited. In order to determine a sequential circuit's adherence to its specification, a sequence of input values has to be applied from a known initial state. This implies that the circuit has to be somehow initialized. Unless the circuit has a resetting capability, an initializing sequence of input values has to be applied beforehand. This sequence is also known as a homing sequence. It has been shown that input sequences for determining the internal state of a sequential circuit are in the worst case exponential in length [29]. In general, exhaustive testing of sequential circuits is an NP-hard problem [17].

As stated earlier, the testability of a circuit is determined by its controllability and observability. By introducing circuit design modifications that improve either of these two factors, the complexity of necessary tests can be greatly reduced. To date, a substantial research effort has been dedicated to design for testability (DFT). Scan test design is a popular method of DFT.

#### 2.2 Scan Test

Scan design is a method of increasing sequential circuit testability. To illustrate it, we present the sequential circuit of Fig. 2.5. It consists of five registers interleaved with some combinational logic. The only inputs that are directly controllable are those attached to

Figure 2.5: Arbitrary sequential circuit.

register R1, and the only outputs that are directly observable are those from register R4. The remaining three registers are internal and, therefore, practically inaccessible.

Figure 2.6: Scan Test design.

Now, suppose that all the registers are scan registers (which are similar to shift regis-

ters) and are connected together with a serial line to form a single scan path, as depicted in Fig. 2.6. Through this path arbitrary values can be scanned in and out of every register. In this manner all the registers are made fully controllable and also fully observable. Since every register can be now loaded with useful test vectors, the hard problem of testing sequential circuits has been reduced to that of testing combinational circuits.

In the above example every register is made scannable, which constitutes a full scan test design. Circuits designed in this manner are fully testable. This ability, however, comes at a price. Scan registers are slower and more complex than their non-shiftable counterparts. Additional serial and control lines are also required. Consequently, fully scannable circuits are larger, more complex, slower, and use more energy than their non-scannable counterparts. Furthermore, full scan designs entail extensive scan paths resulting in prohibitively long scan-in/scan-out times.

Limiting the number of registers included in the scan path in order to reduce overhead constitutes a partial scan test design. These registers must be selected in a way that does not impede the circuit's testability. Significant amount of research has been devoted to establishing optimal partial scan tests [6, 12, 23, 27, 51].

Scan path techniques are not limited to intra-chip testing. At the system level, test sequences can be provided to individual chips on a circuit board via a serial path line. This method, called *boundary scan*, has proven so useful that it has been standardized by the IEEE<sup>1</sup> [54].

Scan path techniques, although very useful in improving the testability of a sequential circuit, have the disadvantage of being serial in nature. This imposes a practical upper bound on the length of the test vectors. Hence the goal is to obtain maximal fault coverage with shortest possible tests.

<sup>&</sup>lt;sup>1</sup>IEEE 1149 Boundary Scan architecture.

#### 2.3 Summary

Fundamental aspects of testing digital circuits have been described using the most common fault model, the stuck-at fault model, as an example. This fault model is insufficient to describe all possible faulty behaviors of a digital circuit, particularly one implemented in CMOS technology. Other fault models are required and appropriate tests have to be devised. Moreover, due to the existence of non-logical faults, logic tests have to be complemented with parametric tests.

Logic testing, in itself is a complex issue, particularly when applied to sequential circuits. Exhaustive testing is an NP-hard problem in general, so fault models have to be tailored to the circuits under test in order to be accurate, and for the respective tests to be short enough to be useful.

Although circuits should be designed to include features that improve testability, such as scan paths (DFT), test lengths should be minimal while providing optimal fault coverage in the fault model.

## Chapter 3

## **Memory Testing**

Memory-based products make up a significant percentage of the total production of integrated circuits. As technologies change and bit densities continue to increase, new causes of failure emerge; defects that were of no consequence in earlier generations have to be dealt with now. Consequently, testing methods have to evolve continuously in order to maintain the expected levels of quality control with efficiency.

Testing of random-access memories (RAMs) has been the topic of extensive research. The content of this chapter is a summary of fundamental aspects of functional RAM testing, based on the comprehensive studies on testing RAMs presented in [20, 42].

#### 3.1 RAM Test Classification

RAMs are large sequential circuits used for storing binary information. Their large state space and regular structure has led to the development of memory-specific testing methodologies. Testing methodologies can be divided into two categories: traditional and modern; the latter is also known as reduced.

Traditional tests such as 'Zero-One', 'Checkerboard', 'GALPAT', 'Walking 1/0', 'Slid-

ing Diagonal' and 'Butterfly' were not designed on the basis of any fault model. Fault coverage of these tests could not be determined and qualitative comparisons between these tests were difficult. Moreover, these tests were often  $O(n^2)$  in length, where n is the number of bits stored in the chip. Since modern memory chip capacities reach the 1Gb range, any tests of such length are unacceptable.

Modern functional memory testing techniques define their coverage in terms of faults, such as: (cell) stuck-at, toggling, coupling and pattern-sensitivity. Examples of modern tests are: 'MATS', 'MATS+', 'MATS++', 'March C-', etc. These tests are also known as march tests. They derive their name from the fact that memory cells are analyzed one by one in ascending or descending order. The sequence of operations that are performed on each consecutive cell is referred to as the march element. March tests can be easily generated and thus are often used in built-in self-test designs.

Van de Goor presents a study of several march tests in terms of their fault coverage and complexity, followed by a qualitative comparison to traditional ones [20]. These results are summarized in Table 3.1. This table contains the fault coverages of several tests. The listed faults include both those of the memory array (i.e., cell stuck-at faults, transition faults and coupling faults) and those of the peripheral circuitry (i.e., address decoder faults, refresh faults, sense amplifier recovery faults and write recovery faults). The latter three faults are dynamic, as they occur when the memory is operated at speeds approaching its design extrema. For instance, a slow sense amplifier may fail to read a 0 after reading several consecutive 1s, or a slow address decoder may fail to access a correct memory location in time for a subsequent operation. It should be noted that traditional tests not only detect faults, but also locate them within the memory array; however, this diagnostic ability comes at a substantial increase in test time and is usually not required, since a faulty chip will often be discarded.

Two types of storage mechanisms are used in current RAMs. When data is stored

Fault coverage Test time Algorithm AF SAF  $\overline{\mathsf{TF}}$ CF Others Zer-One O(n) Checkerboard L Refresh O(n)L Walking 1/0 L L L Sense amplif, rec.  $O(n^2)$ GALPAT L L L Write recovery  $O(n^2)$ L GALROW LS T. L L Write recovery  $O(n\cdot\sqrt{n})$ GALCOL LS L L L Write recovery  $O(n/\sqrt{n})$ LS L L  $O(n \cdot \log_2(n))$ Sliding Diag. LS  $O(n \cdot \log_2(n))$ Butterfly L MATS DS D O(n)D D MATS+ O(n)-Marching 1/0 D D D O(n)D MATS++D D D O(n)March X D Unlinked CFins D D D O(n)D March C-D D D Unlinked CFins O(n)March A D Ð D D Unlinked CFs O(n)D D March Y D D Linked TFs O(n)March B D D D D Linked CFs O(n)

Table 3.1: Comparison of memory tests for *n*-bit RAMs [20].

AF = Address decoder Fault

SAF = Stuck-at Fault

L = Locate D = Detect

TF = Transition Fault CF(in) = (inversion) Coupling Fault LS = Locate Some DS = Detect Some

as a charge on a capacitor the RAM is called a *dynamic* RAM (DRAM). This charge dissipates in time due to leakage currents, and has to be dynamically refreshed; hence the name. In fact DRAMs are largely analog devices. On the other hand, data can also be stored in a latch - a digital device. In this case, as long as power is supplied to the chip, the data is retained indefinitely. For this reason such a RAM is called a *static* RAM (SRAM).

Defects in memory circuits can be partitioned into two categories: global and local. Global defects are often related to the manufacturing process. They include incorrect thickness of polysilicon or gate oxide that may result from variations of oven temperature, and affect a large area of a wafer. These defects are readily detectable by various parametric tests. Local or *spot* defects, such as dust particles on the chip or gate oxide pinholes, manifest themselves mostly as *functional* faults. They are interpreted at the

layout level as broken wires, shorts between wires, missing contacts, extra contacts and newly created transistors. Spot defects are mapped into the following functional classes:

- A stuck-at fault in a cell,

- A stuck-open fault in a cell, i.e. the cell cannot be accessed by read or write operations,

- A multiple cell access fault.

- A data retention fault, where a cell changes its state spontaneously,

- A coupling fault,

- state coupling (SRAMs only), where the coupled cell is driven to some state only when the coupling cell is in a particular state,

- idempotent coupling, where the coupled cell is driven to some state due to a change of state in a coupling cell,

- dynamic coupling (DRAMs only), where the coupled cell is driven to some state when the coupling cell is being accessed.

- A transition fault (SRAMs only), where a cell's state can change only in one direction (e.g., from 0 to 1, but not from 1 to 0),

- A pattern-sensitivity fault (DRAMs only), where a cell's state is influenced by the state, or change of state of the neighboring cells. The cell's neighborhood may be defined by physical adjacency, a common row or column.

It is clear that due to the fundamental differences in the data storage mechanism, different fault models apply to DRAMs and SRAMs. A comprehensive survey of defect-based fault models for DRAMs and SRAMs is given in [5, 42].

Experimental studies have indicated that traditional and pattern-sensitivity fault tests are ill-suited for testing SRAMs, as the fault coverage of these tests falls in the  $50^{\circ}_{0} - 70^{\circ}_{0}$  range [20]. An inductive fault analysis method, described in [20, 43], revealed that stuckat faults constitute about  $50^{\circ}_{0}$  of faults occurring in SRAMs and data retention faults constitute up to  $18^{\circ}_{0}$ .

On the basis of these observations special SRAM tests, such as *IFA-9* and *IFA-13*, have been designed [20]. The IFA-9 test is an extension of the March C- test, allowing it to detect data retention faults. IFA-13 (a further extension of IFA-9) has been designed to deal with the sequential behavior of sense amplifiers in the presence of stuck-open faults. These tests are more efficient and yield higher fault coverage than general functional tests that detect coupling faults, such as MARCH A. B., or C.

#### 3.2 Design-Oriented Fault Modeling

Defect-oriented fault modeling and inductive fault analysis techniques allow for the generation of tests that are more efficient than traditional tests. However, with the development of special-purpose memories, such as multi-port-RAMs, CAMs and FLASH memories, the number of fault models is growing at an alarming rate [4, 20, 21, 33], making them increasingly difficult to track. Unfortunately, many fault models also fail to specify the design details and the underlying technology (Bipolar, NMOS, CMOS, BiCMOS) of the circuit for which they were designed. As a result, tests designed to detect faults for a given fault model may inadvertently be used to test functionally similar memories for which that fault model may not apply. This confusing situation often forces industrial test engineers to use the old, well known fault models and tests, regardless of how inefficient or unreliable they may be.

In order to remedy this situation, we postulate the following guidelines for design-

oriented fault modeling:

- The circuit and the underlying technology should be specified to avoid confusion.

- Faults should be labeled in terms of defective circuit components, not in terms of functional behavior (e.g. transistor stuck-on fault, not transition fault).

- Particular attention should be paid to application-specific aspects of the design.

These guidelines are in agreement with the concept of logical testing, described in the previous chapter. However, in this thesis we will show that by following these guidelines simpler and more accurate fault models and logical tests can be developed.

#### 3.3 Summary

An overview of memory testing topics has been presented. Traditional and modern tests have been described and compared in terms of their lengths and fault coverage. Faults indigenous to static and dynamic memories have been described. This characterization is a result of defect-based fault modeling techniques. We have also listed tests designed exclusively for SRAMs. These tests are more efficient and yield higher fault coverage than general functional tests. A design-oriented approach to fault modeling has been proposed. Its purpose is to categorize faults in terms of defects in the cell circuit and not in the cell's functional behavior. This approach should result in more accurate fault models that take into account the cell design, implementation technology, and design-specific functionality of a memory.

### Chapter 4

## Formal Models

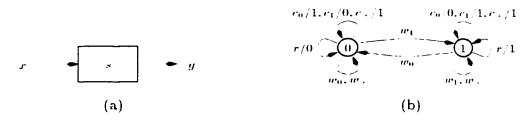

In order to reason about memory faults a proper formalism is required. We adopt a formalism developed by Brzozowski and Jürgensen [11] for sequential circuit testing and diagnosis.

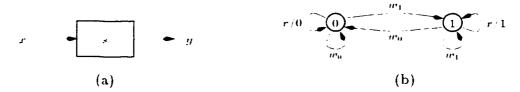

Finite-state automata are used to describe possible behaviors of a sequential circuit. The correct behavior of the circuit is modeled by a Mealy automaton  $A^0 = (Q^0, X, Y^0, \delta^0, \lambda^0)$  called the good machine type. Here,  $Q^0$  is the set of states, X is the input alphabet,  $Y^0$  is the output alphabet,  $\delta^0:Q^0+X\to Q^0$  is the transition function, and  $\lambda^0:Q^0+X\to Y^0$  is the output function. A good machine type initialized to some state  $q^0\in Q^0$ , is referred to as a good machine  $(A^0,q^0)$ . Similarly, any incorrect behavior, referred to as a fault type is also a Mealy automaton  $A^i=(Q^i,X,Y^i,\delta^i,\lambda^i)$ . Fault types have the same input alphabet as  $A^0$ , but differ from it in the set of states, the output alphabet, transition and output functions. By the same token, a fault type initialized to some state is called a fault. The good machine type  $A^0$ , together with a finite family of fault types  $A^1,\ldots,A^m$  and a set of potential initial states  $P^i\subseteq Q^i$  for  $i=0,\ldots,m$  constitute a fault model for  $A^0$  denoted as  $\mathcal{F}_{A^0}$ .

Since random-access memories are in fact sequential circuits (i.e., the output depends

on the input and the internal state of the circuit), we shall use a sample RAM to illustrate a summary of the above formalism.

#### 4.1 Memory Models

We define a model of a bit-addressable RAM of size n. A fault-free n-cell RAM type is a Mealy automaton [11]

$$M = (Q, X, Y, \delta, \lambda).$$

where  $Q = \{0,1\}^n$ ,  $X = \bigcup_{i=1}^n X_i$  with  $X_i = \{r^i, w_0^i, w_1^i\}$ ,  $Y = \{0,1,\$\}$ , and the transition function  $\delta$  and the output function  $\lambda$  are defined by

$$\delta((q_1, \dots, q_i, \dots, q_n), r^i) = (q_1, \dots, q_i, \dots, q_n),

\delta((q_1, \dots, q_i, \dots, q_n), w_0^i) = (q_1, \dots, 0, \dots, q_n),

\delta((q_1, \dots, q_i, \dots, q_n), w_1^i) = (q_1, \dots, 1, \dots, q_n),

\lambda((q_1, \dots, q_i, \dots, q_n), r^i) = q_i,

\lambda((q_1, \dots, q_i, \dots, q_n), w_0^i) = \$.$$

$$\lambda((q_1, \dots, q_i, \dots, q_n), w_1^i) = \$.$$

Inputs  $r^i$ ,  $w^i_0$ ,  $w^i_1$  denote a 'read', 'write 0' and 'write 1' operations on cell *i*, respectively.

Output \$\$ is merely a formal symbol denoting lack of output during 'write' operations.

Similarly, a model for an n-word by l-bit memory has been developed [15]. It is specified as an n-tuple automaton

$$M_{n,l} = (Q_{n,l}, X_{n,l}, Y_l, \delta_{n,l}, \lambda_{n,l}),$$

where

$$Q_{n,l} = \{0, 1, \dots, 2^l - 1\}^n,$$

$$X_{n,l} = \{r^1, w_0^1, w_1^1, \dots, w_{2^l - 1}^1, \dots, r^n, w_0^n, w_1^n, \dots, w_{2^l - 1}^n\}.$$

and

$$Y_l = \{0, 1, \dots, 2^l - 1, \$\}.$$

The transition function  $\delta_{n,l}$  and the output function  $\lambda_{n,l}$  are defined by

$$\delta_{n,l}((q^{1},\ldots,q^{i},\ldots,q^{n}), \quad \text{if } x = r^{i},$$

$$(q^{1},\ldots,0,\ldots,q^{n}), \quad \text{if } x = w_{0}^{i},$$

$$(q^{1},\ldots,1,\ldots,q^{n}), \quad \text{if } x = w_{1}^{i},$$

$$(q^{1},\ldots,2,\ldots,q^{n}), \quad \text{if } x = w_{2}^{i},$$

$$(q^{1},\ldots,3,\ldots,q^{n}), \quad \text{if } x = w_{3}^{i},$$

$$\vdots \quad \vdots \quad \vdots \quad \vdots \quad \vdots$$

$$(q^{1},\ldots,2^{l}-1,\ldots,q^{n}), \quad \text{if } x = w_{2^{l}-1}^{i},$$

and

$$\lambda_{n,l}((q^1,\ldots,q^i,\ldots,q^n),x) = \left\{ egin{array}{ll} q^i, & ext{if } x=r^i, \\ \$, & ext{otherwise.} \end{array}

ight.$$

Inputs  $r^i$ , and  $w^i_j$  denote a 'read' and 'write j' operations on word i, respectively, where  $j \in \{0, 1, 2, 3, \dots, 2^l - 1\}$ . Symbol \$ is used as before to denote lack of output.

### 4.2 Classic Fault Models

Classic memory faults, described in the previous chapter, can be formalized as follows [11]:

• A stuck-at-a fault type is denoted as:

$$M^{i=a} = (Q^{i=a}, X, Y, \delta^{i=a}, \lambda^{i=a}),$$

where the set of states is

$$Q^{i=a} = \{q \mid q = (q_1, \ldots, q_{i-1}, a, q_{i+1}, \ldots, q_n)\}.$$

the input alphabet X and the output alphabet Y remain unchanged, and the transition function  $\delta^{i=a}$  is a restriction of  $\delta$  to  $Q^{i=a} \cdot X$ , except for the transitions under input  $w^i_a$  where  $\bar{a}$  is the complement of a. In this case the next state function takes the form:

$$\delta^{i=n}((q_1,\ldots,q_{i-1},a,q_{i+1},\ldots,q_n),w_a^i)=(q_1,\ldots,q_{i-1},a,q_{i+1},\ldots,q_n).$$

• A transition fault type is denoted as:

$$M^{i \neg a} = (Q, X, Y, \delta^{i \neg a}, \lambda).$$

In this Mealy automaton  $\delta^{i\neg a}$  is identical to  $\delta$  with the exception of the transition resulting from the input  $w_a^i$ , when cell i is in the state  $\bar{a}$ :

$$\delta^{i=a}((q_1,\ldots,q_{i-1},\bar{a},q_{i+1},\ldots,q_n),w_a^i)=(q_1,\ldots,q_{i-1},\bar{a},q_{i+1},\ldots,q_n).$$

• A coupling fault type involves two separate cells i and j, respectively. Cell i is referred to as the coupling cell, and cell j is the coupled cell. This fault is also

defined as a Mealy automaton:

$$M^{ia\Rightarrow jb} = (Q, X, Y, \delta^{ia\Rightarrow jb}, \lambda),$$

where  $\delta^{ia=\cdot jh}$  differs from  $\delta$  in the transition resulting from the input  $w_a^i$ , when cell i is in the state  $\bar{a}$  and cell j is in the state  $\bar{b}$ :

$$\delta^{i=a}((q_1,\ldots,q_{i-1},\bar{a},q_{i+1},\ldots,q_{j-1},\bar{b},q_{j+1},\ldots,q_n),w_a^i)$$

$$= (q_1,\ldots,q_{i-1},a,q_{i+1},\ldots,q_{j-1},b,q_{j+1},\ldots,q_n).$$

### 4.3 Observer

The goal of testing is to determine whether a circuit A' under test can be classified as a good machine type A'' or some other fault type  $A^i$   $(1 \le i \le m)$ , on the basis of its input and output sequences. Initially A' is in some unknown state p. This is denoted by a machine (A', p). One step in the process of this classification consists of applying a test input to A', obtaining its response, and then comparing both input and output to possible behaviors of A'' through A'''. This comparison will divide the set of machine types into two sets: one with outputs identical to that of A', and one with outputs different from that of A'. Machine types belonging to the latter set may be discarded as A' does not belong to them. Successive and successful repetition of this step will result in the first set to become a singleton  $(A' = A^i)$ , or an empty set, which means that A' belongs to some other, unspecified fault type. This process of fault detection can be accomplished by means of a  $(\det ext{terministic})$  observer, which is an initialized deterministic semi-automaton  $\Delta = \Delta(A'', \mathcal{F}) = (D, X + Y, \delta, d_0)$ , defined as follows [10, 11].

For  $i=0,1,\ldots,m$ , let  $A^i=(Q^i,X,Y^i,\delta^i,\lambda^i)$  and let  $\tilde{Q}^i=Q^i\cup\{\omega\}$  where  $\omega$  is a

new state symbol denoting the discarded machine types. Furthermore, for  $q \in Q^i$  and  $(x,y) \in X \times Y^i$ , let the transition function be defined as

$$ilde{\delta}^i(q,(x,y)) = \left\{ egin{array}{ll} \delta^i(q,x), & ext{if } \lambda^i(q,x) = y, \ & \omega, & ext{if } \lambda^i(q,x) \neq y. \end{array}

ight.$$

and let  $\tilde{\delta}^i(\omega,(x,y)) = \omega$ . Each state of the observer's state set  $d \in D$  is a tuple with components  $d^i_{ij}$  for  $i = 0, 1, \ldots, m$  and  $q \in P^i$  (set of potential initial states). Therefore the set D is defined as

$$D = \{d \mid d_{ij}^{i} \in \tilde{Q}^{i}, i = 0, 1, ..., m, q \in P^{i}\}.$$

The observer's initial state  $d_0$  is denoted by  $[d_0]_q^i = q$  which includes all possible initial states of all fault models and the good machine. Its transition function  $\delta(d,(x,y))$  equals  $\epsilon$  if and only if each component of  $\epsilon$  is  $\epsilon_q^i = \tilde{\delta}^i(d_q^i,(x,y))$  for all i and q.

The maximum amount of information about an arbitrary sequential circuit A' obtainable from a test is: the initial state q, the current state q', and the value of the index i indicating the machine type. All possible outcomes of such identification can be described by the set

$$K = \{(i, q, q') \mid i = 0, 1, ..., m, q \in P^i, q' \in Q^i\}.$$

A complete deterministic observer can easily become unmanageably large as demonstrated in [10]. However, since we are only interested in establishing whether A' is a good machine or not, the observer can be substantially reduced. This is accomplished by extracting, out of the set of observer's states D, a partition  $B_F$  where the affiliation to either the good machine type or to the faulty machine types, but not both, has been established.

The partition  $B_F = (B_0, B_{\pm 0})$  called a fault partition consists of two disjoint sets of states  $B_0 = \{(0, q, q') \mid q \in P^0, q' \in Q^0\}$  and  $B_{\pm 0} = \{(i, q, q') \mid i = 1, \dots, m, q \in P^i, q' \in Q^i\}$  which uniquely determine whether the circuit under test is modeled by the good machine type or not. In other words, these states are  $B_F$ -decided.

The fault partition  $B_F$  is one of a number of other useful partitions, referred to in general as *B-partitions*. An input word which results in a transition to a *B-partition*, consisting of sets of *B-decided* states, is said to *B-diagnose* the circuit A' [10, 11].

### 4.4 Diagnosing Languages

An observer  $\Delta$  can be modified in the following manner:

- 1. The output part Y from the input alphabet  $X \cdot Y$  is removed, thereby introducing nondeterminism.

- 2. A set F of B-decided states is introduced as a set of final or accepting states.

As a result a nondeterministic B-acceptor  $\overline{\Delta}(A_0, \mathcal{F}_0, B) = (D, X, \overline{\delta}, \{d_0\}, F)$  is obtained, where

$$\overline{\delta}(d,x) = \{d' \mid \exists y \in Y : \delta(d(x,y)) = d'\}.$$

Any word w is said to B-diagnose if and only if it always results in  $\overline{\Delta}$  ending up in an accepting state. The set of all B-diagnosing words for the fault model  $\mathcal{F}$  constitute a regular language  $L_B(\mathcal{F})$  [11]. This observation has led to several useful properties:

• If  $L_B(\mathcal{F}_1) \subseteq L_B(\mathcal{F}_2)$  then a fault model  $\mathcal{F}_1$  is said to *B-cover* a fault model  $\mathcal{F}_2$  for a diagnosis goal B. This is particularly useful in determining whether tests for one type of fault are applicable to testing for another type of fault, i.e. establishing the fault coverage of a particular test [55].

• Given several sets of B-diagnosing words for different fault models that constitute a family **F**, a single set of B-diagnosing words can be obtained for the entire set of these fault models by the following formula [55]:

$$L_{B}\left(\bigcup_{\mathcal{F}\in\mathbf{F}}\mathcal{F}\right)=\bigcap_{\mathcal{F}\in\mathbf{F}}L_{B}\left(\mathcal{F}\right).$$

### 4.5 Lower Bounds

One of the early papers on lower bounds for the detection of coupling faults in RAMs was presented by Brzozowski and Cockburn [9]. Due to the recent rapid increase in memory sizes, efficient detection of faults is the subject of extensive research. Cockburn and Brzozowski [14] have presented a summary of known lower bounds and test sequence lengths for detecting various faults in RAMs. These bounds have been established using language theoretic tools and are shown in Table 4.1.

Table 4.1: Lower bounds and known test lengths for faults in n-bit RAMs.

| Fault Model          | Best Lower Bound          | Best Known Test Length           | Comments                             |

|----------------------|---------------------------|----------------------------------|--------------------------------------|

| general toggling     | $2n^2 + n$                | $ 2n^2+n $                       | optimal for $n \geq 2$ .             |

| 2-limited toggling   | $n[\log_2(n-1)] + 5n$     | $4n\lceil \log_2 n \rceil + n$   | optimal for $n=2$ :                  |

|                      |                           |                                  | shortest known for $n \geq 0$ .      |

| single toggling      | 5n-2                      | 5n-2                             | optimal for $n \geq 2$ .             |

| general coupling     | 16. for $n = 2$ :         | $2n^2 + 4n$                      | optimal for $n = 2$ :                |

|                      | $2n^2 + 3n$ , for $n > 2$ |                                  | conjectured optimal for $n \geq 3$ . |

| 4-limited coupling   | $n[\log_2(n-1)] + 7n$     | $4n\lceil \log_2 n \rceil + 17n$ | shortest known for $n \geq 15$ .     |

| 3-limited coupling   | 9n-2                      | 14n - 12                         | optimal for $n=2$ :                  |

|                      |                           |                                  | shortest known for $n \geq 7$ .      |

| 2-limited coupling   | 9n-2                      | 12n - 8                          | optimal for $n=2$ :                  |

|                      | 1                         |                                  | conjectured optimal for $n \geq 3$ . |

| single coupling      | 9n - 2                    | 10n - 4                          | optimal for $n=2$ :                  |

|                      |                           |                                  | conjectured optimal for $n \geq 3$ . |

| toggle-free coupling | 9n-2                      | 15n - 14                         | optimal for $n=2$ :                  |

|                      |                           |                                  | shortest known for $n \geq 4$ .      |

## 4.6 Summary

We have presented an overview of a formalism developed by Brzozowski and Jürgensen for sequential circuit testing and diagnosis [11]. We utilize this formalism in our behavioral analysis of memory cells. It provides the means to distinguish faulty behaviors from the fault free ones and to derive shortest input sequences with which that distinction can be made.

## Chapter 5

# **CAM Fundamentals**

In a typical random-access memory (RAM) stored data is accessed by specifying the address of the location in memory where data resides. On the other hand, a content-addressable memory (CAM), as the name suggests, allows access to stored data on the basis of a simultaneous comparison of the content of all memory locations with a particular datum, called the search key. This ability lends itself naturally to applications where simultaneous comparison is a principal operation. Chisvin and Duckworth [13] provide an extensive list of such applications: "file maintenance, pattern recognition, symbolic representation of information, data retrieval, parallel arithmetic algorithms, data correlation, speech recognition, radar analysis, connectivity testing, spelling checking, list and string processing, air traffic control, relaxation problems, language translations and intelligent network routing systems."

Some authors [7, 13, 26, 41] use the terms content-addressable memory and associative memory interchangeably. However, as pointed out in [30], the proper meaning of associativity applies to the more abstract concept of links between the meanings of data items — for example, associating the word "fire" with the word "hot" — as opposed to a particular organization of storage elements that facilitate a simultaneous bit-pattern

matching operation: consequently, we will use only the term content-addressable.

The potential utility of CAMs has been recognized by the computer industry at least since the late sixties [30, 40]; however, the implementation of such memories has been hindered by the following factors reported by Chisvin and Duckworth in 1989 [13]:

- functional and design complexity,

- relatively high cost of storage capacity,

- poor storage density compared to conventional memory,

- slow access time.

- lack of software to properly utilize CAM's capabilities.

Since then, implementation methods have improved dramatically, but because of the inherent higher complexity of a CAM cell (exceeding that of static RAM). CAMs are unlikely to replace RAMs as general purpose memories, although general purpose CAM designs have been investigated [2].

Most CAMs manufactured today can be found in custom designs, and are often embedded in larger circuits. Many application-specific CAM configurations have been reported [3, 7, 18, 24, 26, 28, 31, 32, 36, 41, 45, 50]. The most significant functional differences between these configurations include the accessibility by address as well as content, match-and-update, resolution of multiple hits, synchronous or asynchronous operation, etc., resulting in diverse implementations of CAM's peripheral circuitry. However, the design of the storage element of a core cell, in most cases, is similar and consists of a cross-coupled inverter circuit, such as those found in static RAMs [2, 3, 7, 18, 26, 31, 40, 41, 45]. Different designs of the core cell's comparison circuitry represent attempts to address various electrical pitfalls such as data-dependent bit line loads, or charge sharing problems [44].

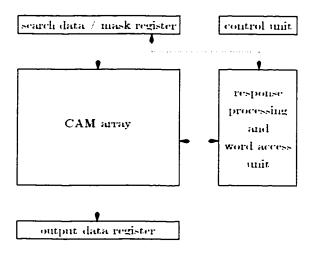

Figure 5.1: CAM: a block diagram.

Notable exceptions to the static CAM schema are dynamic implementations of the core cell [35, 38, 53, 56]. They are more complex than those of a typical high-density dynamic RAM, due to the necessity of charge retention during the simultaneous data comparison process. Like all dynamic memory implementations, these CAMs have to incorporate additional refresh circuitry.

Embedded memories of ASICs are usually static, as they are considered to be less troublesome [54], easier to build, and are generally faster than dynamic configurations. Hence, the analysis in this thesis is limited to static memories.

### 5.1 Overview of CAM Architecture

As mentioned earlier, most of the CAMs manufactured today are designed with a specific application in mind. Before analyzing some of these various implementations, we take a brief look at general components of a CAM. A generic architecture of a CAM and its basic cell are depicted in Fig. 5.1.

All CAM implementations consist of the following functional blocks:

- data and mask register, which stores a particular word according to which memory is to be accessed. Since it is possible that a part of data word may be irrelevant to the search criteria, the ability to mask irrelevant parts is usually provided. The search key is, therefore, composed of the parts of the word stored in the data register that have not been masked out.

- response processing and word access unit, which determines the functionality of the CAM. The implementation of this functional block is the main source of differences between various CAM designs. This block handles resolution of multiple hits, keeps track of unused locations for use during write operations, and with other application specific operations. The unit also often contains an address register for reading and writing in RAM mode.

- output data register, which incorporates sensing circuitry that retrieves and holds words picked up from bit lines during a read operation.

- CAM array, which stores the data. It consists of a homogeneous matrix of core cells. A number of existing designs will be considered in the next section.

- Control unit, which is used to coordinate the operation of the aforementioned blocks.

### 5.2 Static CAM Cell Circuits

A common CMOS implementation of a CAM cell is depicted in Fig. 5.2 (a). It is composed of a typical six-transistor SRAM cell (storage section) and a three-transistor matching circuitry (comparison section), which brings the transistor count of this CAM cell to nine. Various special-purpose CAM circuits have been developed using this design [4, 18, 22, 26].

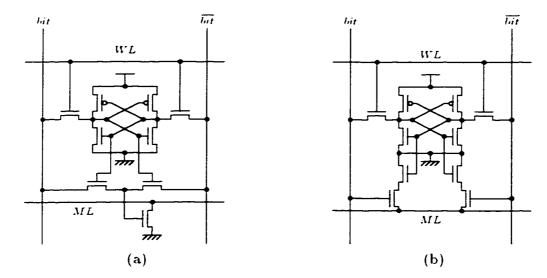

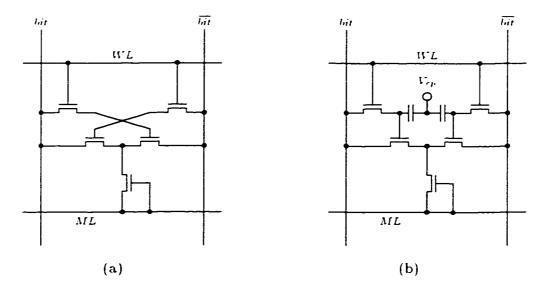

Figure 5.2: CMOS implementations of a single-port static CAM cell.

'Read' and 'write' operations are identical to to those in a SRAM cell. During a 'write' operation, the bit and  $\overline{bit}$  lines are driven to complementary logic values representing the bit to be stored. Next, by raising and then lowering the word line WL the bit is stored by forcing the inverter outputs to coincide with the values on the bit and  $\overline{bit}$  lines. Unlike SRAMs, CAMs have one more 'write' operation - 'write - ', which preserves the previous state of the cell. It is used for bit-masking purposes, where only a part of the word is to be overwritten. During a 'write - ' both bit and  $\overline{bit}$  are driven to high voltage.

A 'read' operation is performed by pre-charging both bit and  $\overline{bit}$  lines, and then raising the word line WL, thus causing one of the bit lines to discharge. The resultant voltage differential between the bit and  $\overline{bit}$  lines is detected by sense amplifiers that recreate the content of the accessed word.

The process of searching is unique to the CAM, and is performed in the comparison section of the cell. In Fig. 5.2 (a), this section consists of the bottom three transistors of the cell's circuit. The match line ML together with the bottom-most transistor constitute a wired-AND for all the cells in the memory word. This means that the ML line will

remain isolated from ground as long as all the transistors connecting it to ground are not conducting. The remaining two transistors implement an XOR function between the bit and  $\overline{bit}$  lines and values stored on the outputs of the inverters. Note that only one of these transistors conducts at any given time. The compare operation is a two-step process. Initially, both bit lines are grounded and the ML line in the CAM cell is precharged. Next, bit lines are driven according to the search key. If a mismatch occurs, the bottom-most transistor will be forced to conduct, thus discharging the ML line. Note that if a particular bit in the search word is masked out, both corresponding bit and  $\overline{bit}$  lines remain grounded, thus preventing any influence on the ML line. Such masking is called a 'compare  $\cdot$ ' operation.

This design has a few shortcomings. In order to discharge the ML line, a logical 1 has to appear on the gate of the bottom-most transistor. This value is supplied by one of the  $bit/\overline{bit}$  lines via a conducting n-MOS transistor, which causes a voltage drop of approximately 0.7V. A 'weak' 1 appears on the gate of the bottom-most transistor, effectively excluding this design from low power applications. Moreover, these n-MOS pass transistors constitute variable loads for the differential bit lines. This results in unpredictable delays during 'read' and 'write' operations and, in effect, slower worst-case operation [44].

Another problem with this implementation is the fact that the state of the match line is affected by non-compare operations. Therefore, both  $bit/\overline{bit}$  lines have to be discharged, and the match line has to be pre-charged before an actual compare operation, causing additional delays.

A ten-transistor CAM cell design has been reported in [28, 34]. It differs slightly from the previous cell in its implementation of the matching section, as shown in Fig. 5.2 (b). As before, it contains two transistors controlled by the storage section; however, here, each of the  $bit/\overline{bit}$  lines drives the gate of a dedicated transistor. Since the loads on  $bit/\overline{bit}$  lines

Figure 5.3: Dual-port static CAM cell.

are no longer data-dependent and the discharge path is gated directly by the  $bit/\overline{bit}$  lines, this design could yield itself to low power, high speed applications. Unfortunately, this design, as well as the one proposed by McAuley and Cotton [36], are prone to accidental match-line discharge due to charge-sharing across stray capacitances on the dedicated transistors as described in [44]. This problem has been addressed by reversing the order of the transistors between the match line and ground [44, 52].

Although also ill-suited for low power, a dual-port implementation of a CAM cell presented in Fig. 5.3, is free from the shortcomings of the previous cells [7, 31, 44, 45]. Separate pairs of differential lines are used:  $bit/\overline{bit}$  lines for reading and writing data, and compare bit lines  $(cbl/\overline{cbl})$  for performing matching operations. Constant loads on the  $bit/\overline{bit}$  lines precisely define delays during reads and writes. The match line is not affected by non-compare operations and, therefore, can be kept pre-charged by default, resulting in faster 'compare' operations. The separation of differential lines also facilitates efficient match-and-update operations required, for example, in real-time image processing applications [45].

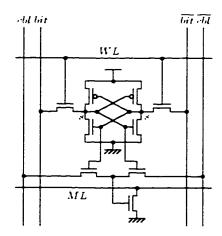

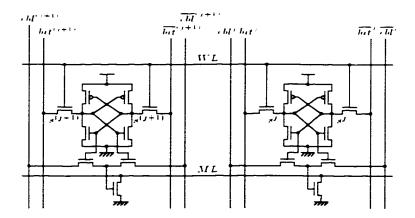

Figure 5.4: Dynamic CAM cell designs. (a) Wade. (b) Yamagata.

## 5.3 Dynamic CAM Cell Circuits

The CAM cell implementations presented so far were all static. For applications where speed and robustness are not as critical as high storage capacity, a dynamic CAM cell implementation has been considered [35, 38, 53, 56]. The increase of bit density has been accomplished by reduction of the number of transistors in each cell. Two such designs: by Wade and Sodini [53], and Yamagata et al. [56], are shown in Fig. 5.4 (a) and (b), respectively.

The ability to compare the entire cell array contents against a search key requires that DCAM cells retain their charge even in an event of a mismatch. This constraint precludes the use of destructive 'read' techniques, dominant in DRAM designs.

In the circuit presented by in Fig. 5.4 (a), data is stored as an electric charge on the gate capacitance of a storage transistor. Cross-coupling of the bit lines facilitates higher storage charges due to the presence of an inversion layer caused by a substantial gate-to-source voltage  $V_{gs}$ , thus overcoming problems encountered in earlier designs [38].

This cross-coupling scheme requires inverted values on the bit and  $\overline{bit}$  lines during a write operation.

A 'write ' operation involves driving both bit lines to 0 during a write operation: this action results in no charge being stored on either transistor. In effect, such a cell stores no value and the ML line is truly isolated at that location. The ability of storing no value is indigenous solely to dynamic cells, in contrast to static ones which always hold some value.

Compare operations are performed by first pre-charging both  $bit/\overline{bit}$  lines then the match line ML, and finally driving the  $bit/\overline{bit}$  lines to values reflecting the search key in a non-inverted manner. A mismatch will discharge ML through the bit line set to 0. Unlike in their static counterparts, 'compare -' operations in dynamic CAM cells entail keeping the bit lines at 1, thus preventing ML from discharging.

The above-mentioned design is limited by the physical dimensions of the storage transistors in the circuit, since charge stored on the gate of a transistor is directly proportional to its size. A minimum storage capacitance of 30fF is required in order to preserve data integrity from alpha-particle-induced soft errors. Capacitances of this magnitude are difficult to obtain in transistors developed using sub-micron processes. In the circuit presented in Fig. 5.4 (b) this issue has been addressed by augmenting the gate capacitances of the storage transistors with stacked capacitors, thus facilitating a successful utilization of a  $0.8\mu$ m process. The capacitors are configured differentially to a reference voltage  $V_{cp}$  equal to half of the supply voltage. The utilization of stacked capacitors as a means of increasing storage charge is superior to the cross-coupling schema presented above. Moreover, the absence of cross-coupling makes this design closely related to that presented by Mundy [38]. The 'write' and 'compare' operations of this dynamic CAM cell are performed identically to those presented above for Wade's CAM design. Fig. 5.4 (a), except that the bit line values need not be inverted during the write operation. The

approach taken by Yamagata, Fig. 5.4 (b). has the potential to achieve the highest bit packing density, akin to that of DRAMs, though at the expense of performance.

### 5.4 Summary