# **Investigation of Current Sensing Using Inherent Resistance**

by

# Shahin Solki

A thesis

presented to the University of Waterloo

in fulfillment of the

thesis requirement for the degree of

Master of Applied Science

in

Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2010

© Shahin Solki 2010

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

Shahin Solki

## **Abstract**

A novel method of current sensing using resistance of power delivery path is introduced as a mean to measure static or dynamic load current in high-power system-on-chips, where conventional methods deemed inadequate. It is named "IRS" here, and it stands for <u>Inherent Resistance Current Sensing</u>.

To explain its application and to provide motivation beyond this work, pros and cons of conventional techniques are reviewed with a look at previous works done in this area.

It is followed with review of discreet implementation of the sensor (IRS) in chapter three. The measurements results collected using the discrete circuits are included with an in-depth analysis of the results and compensation techniques. It offers insight to effectiveness of the solution and its potential, while highlighting shortcomings and limitation of discrete implementation. This would set the tone to design integrated version of the sensor.

In order to select amplifier architecture, a rundown of common methods to construct the instrumentation amplifier is discussed in chapter 4, primarily based on the latest work already done in this field per cited references. This is to help readers to get an overall view of the challenges and techniques to overcome them.

Finally, the architecture for the integrated version of the sensor (IRS) is presented, with a proof of concept design. The design is targeted for low voltage VLSI systems to allow integration within large SoCs such as GPUs and CPUs. The primary block, the instrumentation amplifier, is constructed using rail-to-rail current conveyers and simulated using TSMC 32nm process node. The simulation results are analyzed and observations are provided.

Acknowledgements

I would like to take this opportunity to thank my supervisor Dr. Manoj

Sachdev for granting me the chance to participate in this program, and

furthermore for his support and guidance thorough out the program until

completion.

Here is also a chance to thank Ming Chen, who facilitated my

participation in this program, and Advanced Micro Devices (AMD) that

provided the scholarship and a great place to work.

This is a small step forward on the science and technology ladder, and it

wouldn't be possible without work of others came before me. I see fit to

thank all scientists and authors, who their work and efforts helped me

through this investigation, some of which are the references listed in this

work.

Special thanks to my wife, **Mojgan**, and my sweet heart **Tina**, who their

love and support are my motivation to overcome challenges in life; this is

just one of many.

Best Regards,

Shahin Solki

iv

# **Contents**

| List of l | Figures                                                | vii        |

|-----------|--------------------------------------------------------|------------|

|           | Tables                                                 |            |

|           | Abbreviations                                          |            |

|           |                                                        |            |

| Chapter   | r 1 Introduction                                       | 1          |

| 1.1       | Discrete Techniques for Current Sensing                | 2          |

| 1.1.1     | Voltage Regulator Current Read back                    | 2          |

| 1.1.2     | Series Sense Resistor                                  |            |

| 1.1.3     | Hall Sensor                                            | 3          |

| 1.2       | Integrated Techniques for Current Sensing              | 4          |

| 1.2.1     | High-Side Current Sensing                              | 4          |

| 1.2.2     | Iddq Sensing                                           | 5          |

| 1.3       | Criteria for Current Sensor Architecture               | 6          |

| Chapter   | T 2 Inherent Resistance current Sensing (IRS)          | 7          |

| 2.1       | The Concept                                            |            |

| 2.2       | Temperature Dependence of Inherent Resistance          |            |

| 2.2.1     | Temperature Compensation Technique                     |            |

| 2.2.2     | Using Thermal Chip Sensors as Gain Resistor            |            |

| 2.3       | Conclusions                                            |            |

| 2.5       | Conclusions                                            | 17         |

| Chapter   | Discrete Implementation of IRS                         | 15         |

| 3.1       | Circuit Schematic                                      |            |

| 3.2       | Characterization Results and Analysis                  |            |

| 3.3       | PCB Temperature None Uniformity                        |            |

| 3.4       | Dynamic Behavior Analysis                              |            |

| 3.5       | Conclusions                                            |            |

|           |                                                        | <b>=</b> 0 |

| Chapter   | Selecting Instrumentation Amplifier Architecture       | 29         |

| 4.1       | Voltage Mode Instrumentation Amplifier                 |            |

| 4.2       | Current Mode Instrumentation Amplifier                 |            |

| 4.3       | Current Conveyor Based Instrumentation Amplifier       |            |

| 4.3.1     | Current Conveyor – Second Generation (CCII)            |            |

| 4.3.2     | Building Instrumentation Amplifier using CCII+         |            |

| 4.3.3     | CCII Cell Input Stage                                  |            |

| 4.4       | Noise and Offset Cancelation Techniques                |            |

| 4.4.1     | Auto Zero Technique                                    |            |

| 4.4.2     | Chopper Technique                                      |            |

| 4.5       | Conclusions                                            |            |

| Chapter   | 5 Integrated Implementation of IRS                     | Δ1         |

| 5.1       | Design Targets                                         |            |

| 5.2       | Conceptual Block Diagram                               |            |

| 5.3       | Rail-to-Rail CCII Schematic Cell View (ccii_r2r)       |            |

| 5.4       | Instrumentation Amplifier Schematic Cell View (ia_r2r) |            |

| 5.5       | Simulation Results.                                    |            |

|           |                                                        |            |

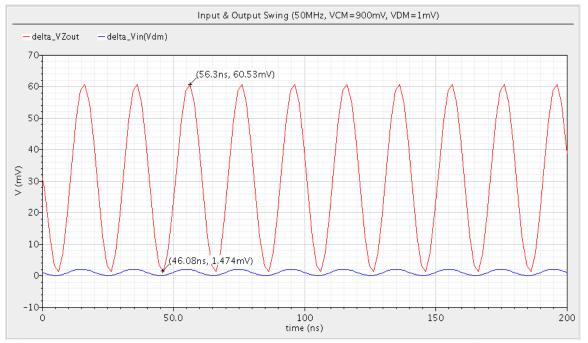

| 5.5.1   | Transient Response                    | 48 |

|---------|---------------------------------------|----|

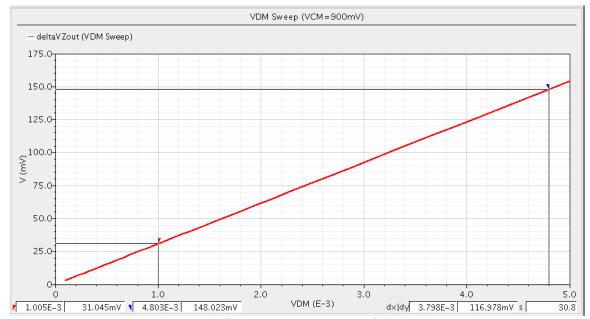

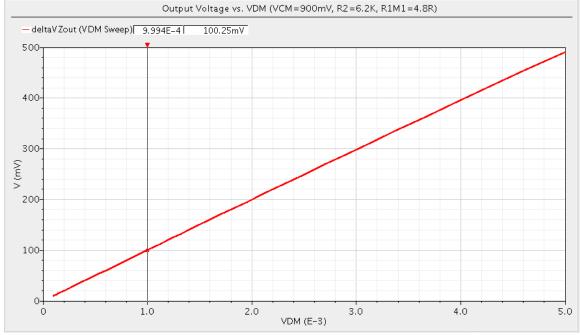

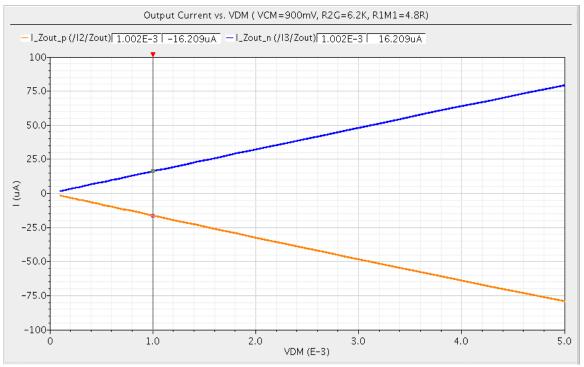

| 5.5.2   | Differential Mode Voltage (VDM) Sweep | 49 |

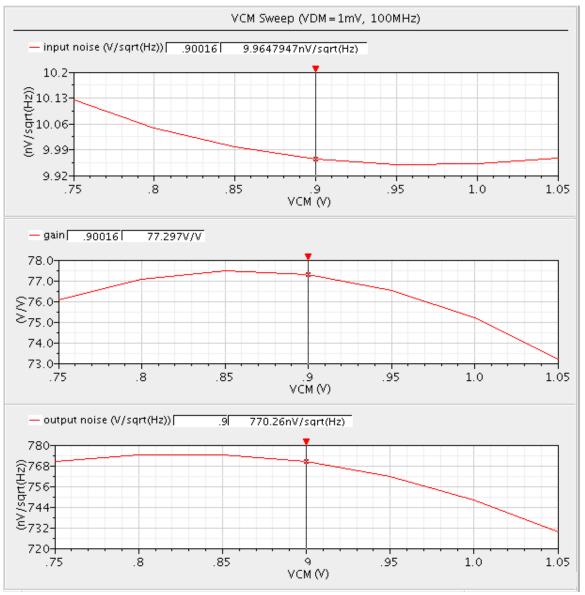

| 5.5.3   | Common Mode Voltage (VCM) Sweep       | 52 |

| 5.5.4   | Gain Resistor (R2) Sweep              | 54 |

| 5.5.5   | Bias Voltage Sweep                    | 55 |

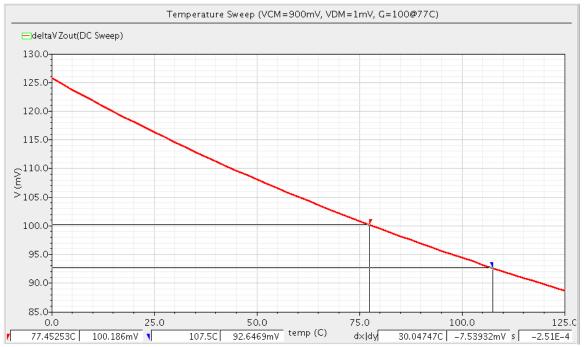

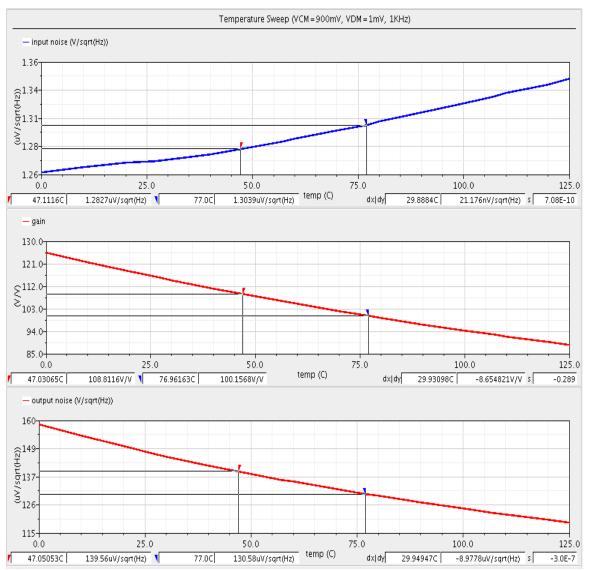

| 5.5.6   | Temperature Sweep                     | 56 |

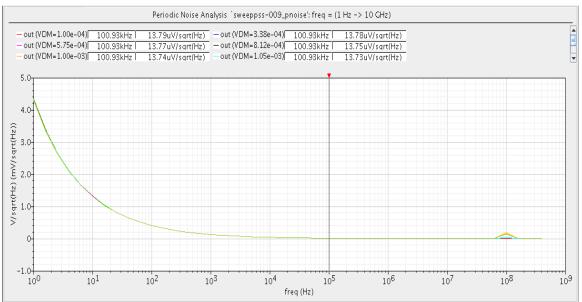

| 5.5.7   | Noise Analysis                        | 58 |

| 5.6     | Conclusions                           | 63 |

|         |                                       |    |

| Referen | ces                                   | 64 |

# **List of Figures**

| Figure 1-1: CMRR as function of frequency [1]                                    | 5   |

|----------------------------------------------------------------------------------|-----|

| Figure 1-2: Example of Iddq Current Sensing [2]                                  | 5   |

| Figure 2-1: Conceptual view of current path                                      | 7   |

| Figure 2-2: Typical Voltage-Mode Instrumentation Amplifier                       |     |

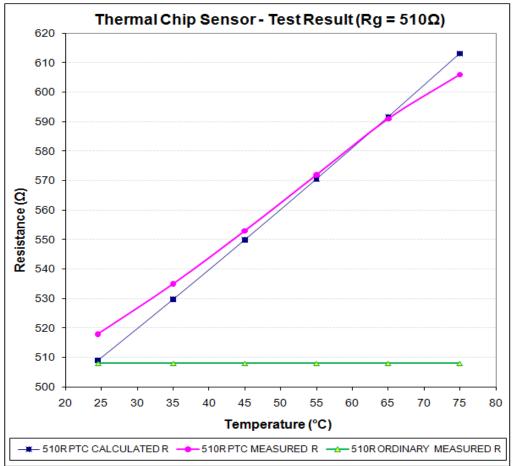

| Figure 2-3: Characterization result for thermal chip resistor $(510\Omega)$      |     |

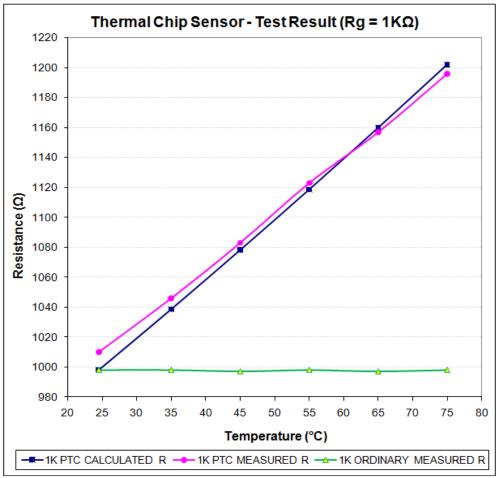

| Figure 2-4: Characterization result for thermal chip resistor (1K)               |     |

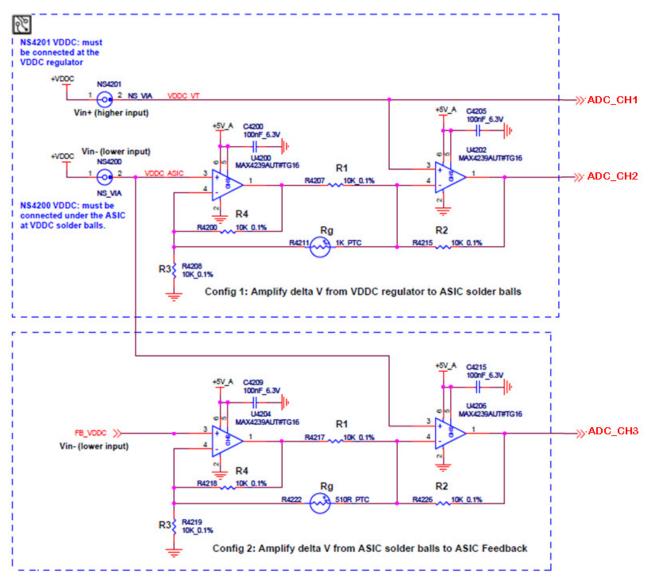

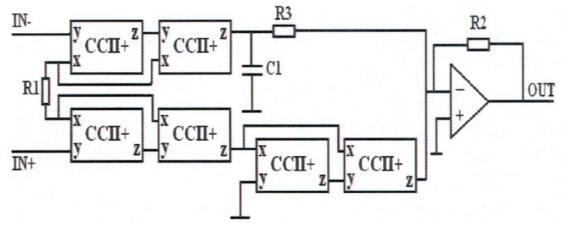

| Figure 3-1: Discrete Implementation of the instrumentation amplifier             | .16 |

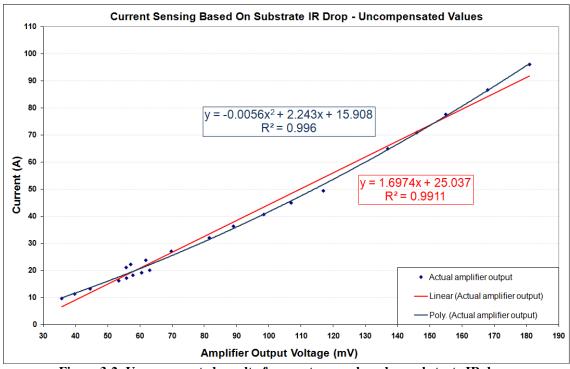

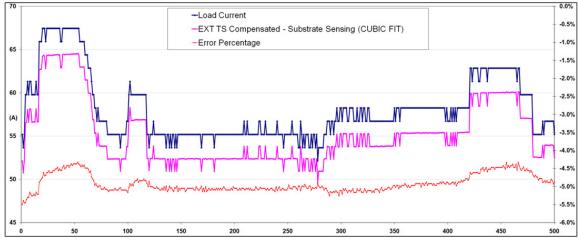

| Figure 3-2: Uncompensated result of current sensor based on substrate IR drop.   | .21 |

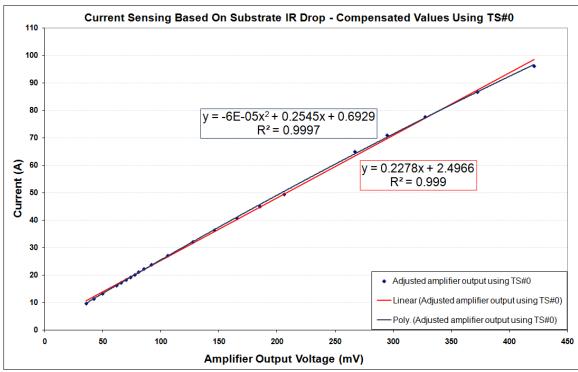

| Figure 3-3: TS0 Compensated result of current sensor based on substrate IR drop  | p   |

|                                                                                  | .22 |

| Figure 3-4: TS3 Compensated result of current sensor based on substrate IR drop  | p   |

|                                                                                  | .22 |

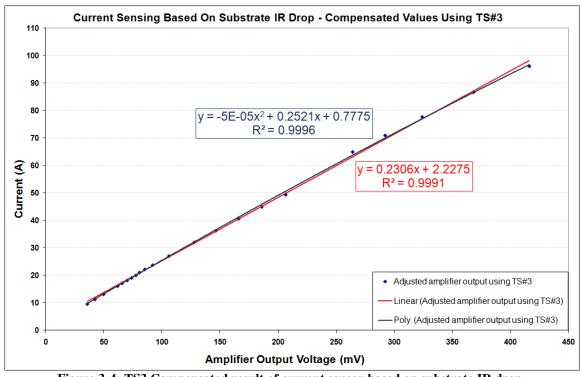

| Figure 3-5: Infrared photos of the PCB under test with two different cooling     |     |

| solutions                                                                        | .25 |

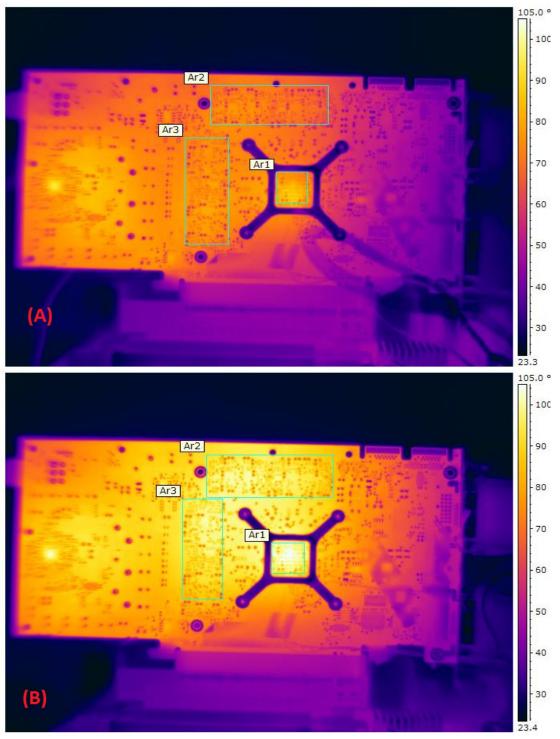

| Figure 3-6: Current measurement result using substrate IR drop sensing under     |     |

| static load                                                                      | .26 |

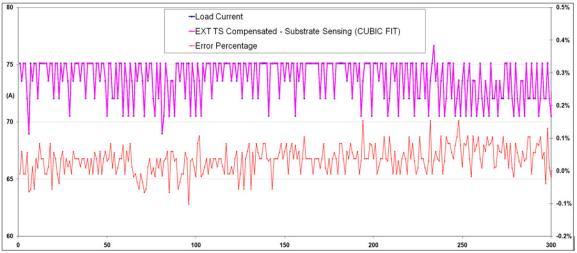

| Figure 3-7: Current measurement results using substrate IR drop sensing under    |     |

| dynamic load                                                                     | .27 |

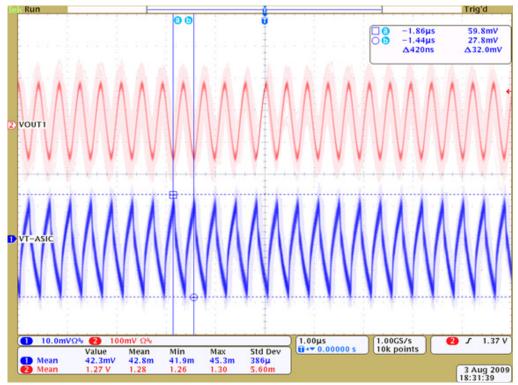

| Figure 3-8: IA differential input (VT-ASIC) and output (VOUT1) at 140A/2.38      | 2.5 |

| MHz load                                                                         | .27 |

| Figure 4-1: Voltage-Mode IA using three operational amplifiers                   | .29 |

| Figure 4-2: Current-mode IA using three operational amplifiers [5]               | .30 |

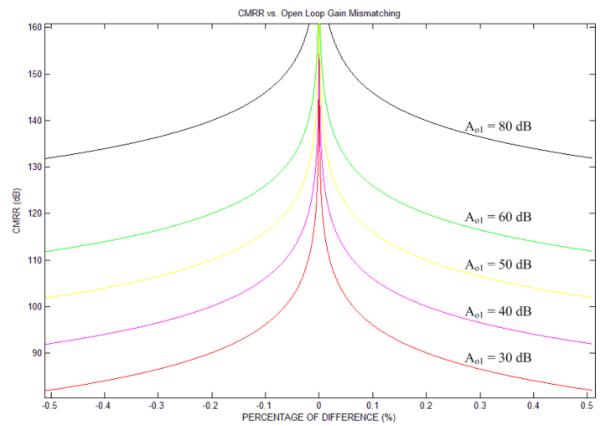

| Figure 4-3: CMRR vs. Open Loop Gain Mismatching in CM IA [5]                     | .31 |

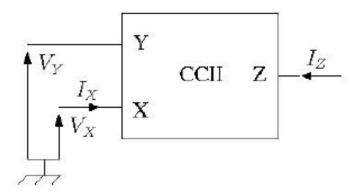

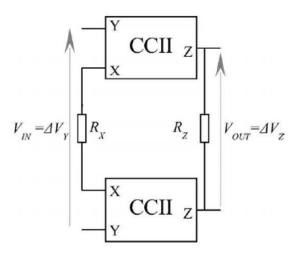

| Figure 4-4: Current conveyor second generation (CCII) as a three-port device     | .32 |

| Figure 4-5: Equivalent function of CCII in the form of circuit model and matrix  | [6] |

|                                                                                  |     |

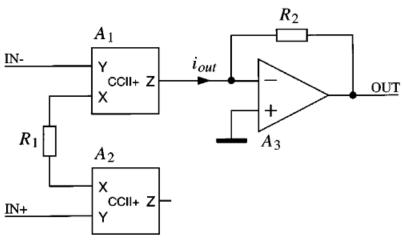

| Figure 4-6: Conventional IA using CCII                                           |     |

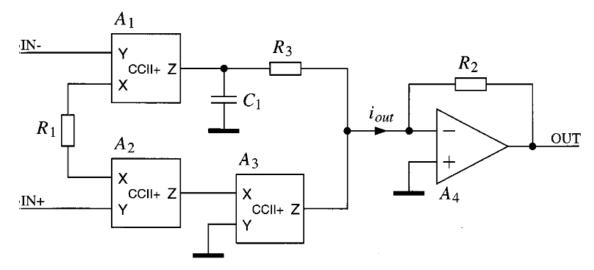

| Figure 4-7: Improved CMRR using current inverting technique [7]                  |     |

| Figure 4-8: High CMRR IA using Cascade CCII [4]                                  |     |

| Figure 4-9: Differential input/output IA using CCII [6]                          |     |

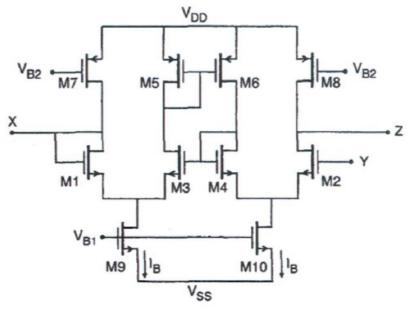

| Figure 4-10 CCII Cell with NMOS input stage [4]                                  |     |

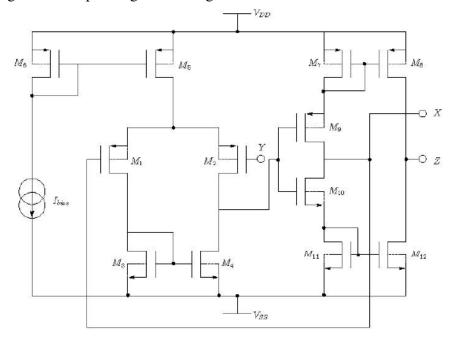

| Figure 4-11: CCII Cell with PMOS input stage [6]                                 |     |

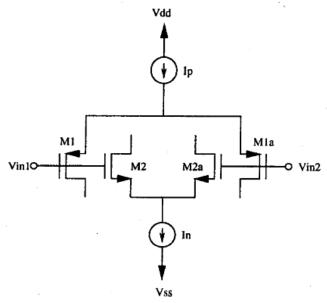

| Figure 4-12: Conceptual diagram for rail-to-rail CMOS input stage                |     |

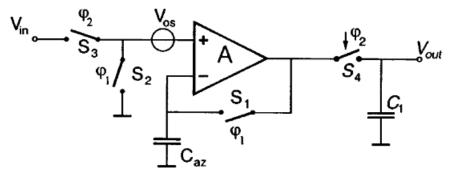

| Figure 4-13: Conceptual diagram of autozero [27]                                 |     |

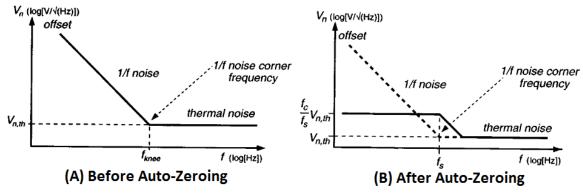

| Figure 4-14: CMOS amplifier typical noise profile before and after autozero [27] |     |

|                                                                                  |     |

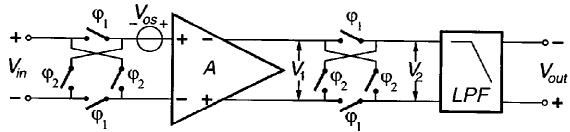

| Figure 4-15: Conceptual diagram of chopper technique [27]                        | .40 |

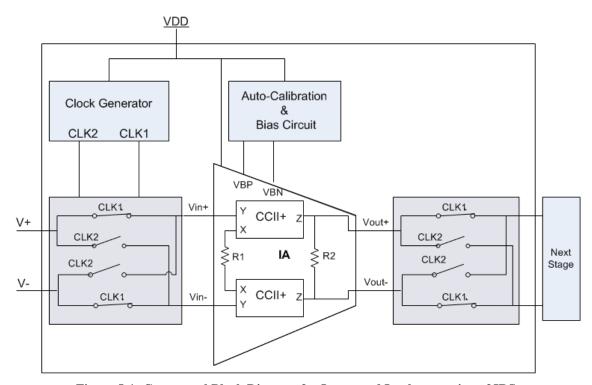

| Figure 5-1: Conceptual Block Diagram for Integrated Implementation of IRS        | .42 |

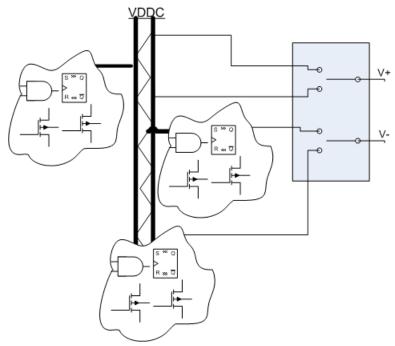

| Figure 5-2: Conceptual view of VDDC power path and monitoring points             |     |

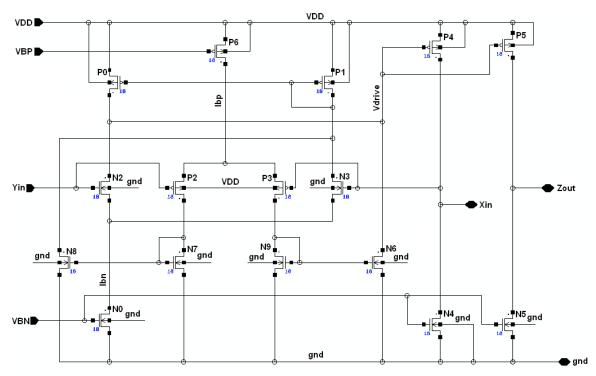

| Figure 5-3: Schematic Cell View of rail-to-rail CCII (ccii_r2r)                  |     |

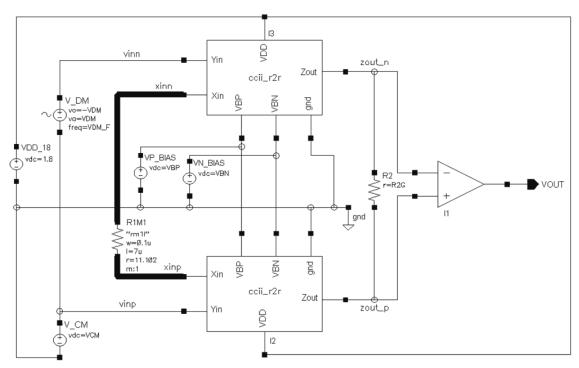

| Figure 5-4: Schematic Cell View of the instrumentation amplifier (ia r2r)        |     |

| Figure 5-5: Transient response of the IA                                  | 48  |

|---------------------------------------------------------------------------|-----|

| Figure 5-6: Output Voltage vs. VDM @ Gain=30                              | 49  |

| Figure 5-7: Output Voltage vs. VDM @ Gain=100                             | 49  |

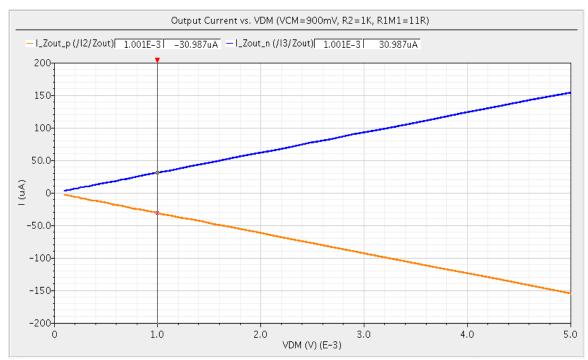

| Figure 5-8: Output Current vs. VDM @ Gain=100                             | 50  |

| Figure 5-9: Output Current vs. VDM @ Gain=30                              | 50  |

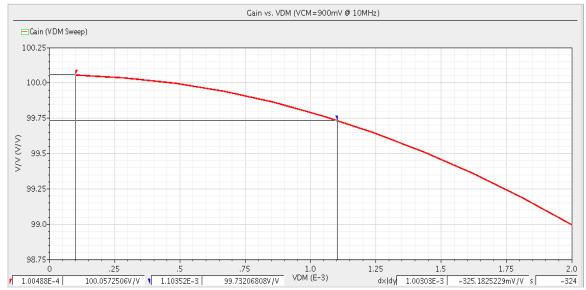

| Figure 5-10: Gain vs. VDM at 10MHz with gain 100                          | 51  |

| Figure 5-11: Gain vs. VDM at 10MHz with gain 30                           | 51  |

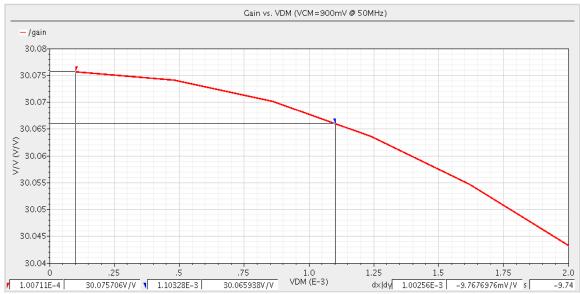

| Figure 5-12: Output Voltage vs. VCM @ Gain=30, 50MHz                      | 52  |

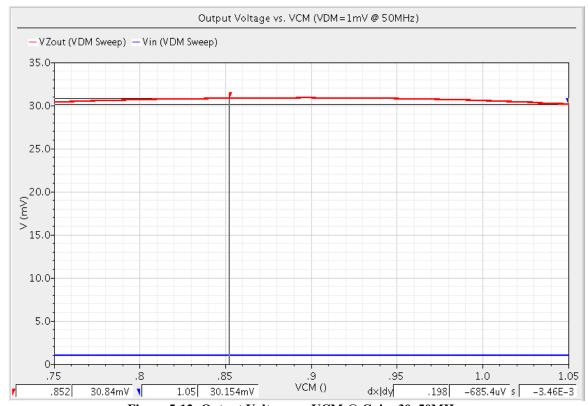

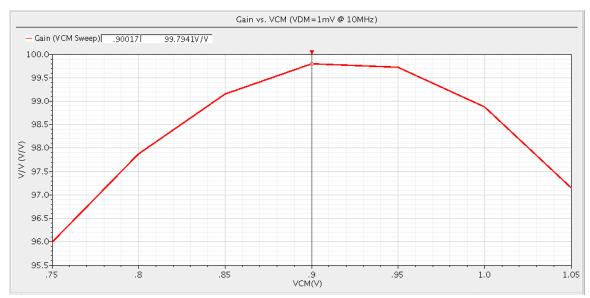

| Figure 5-13: Gain vs. VCM @ Gain=100, 10MHz                               | 53  |

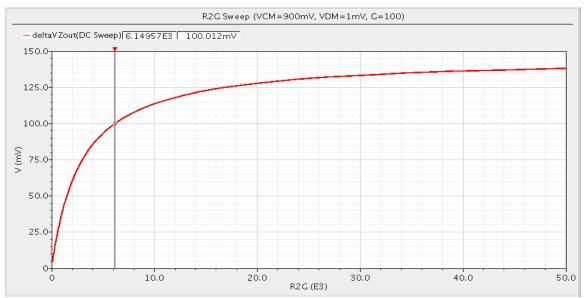

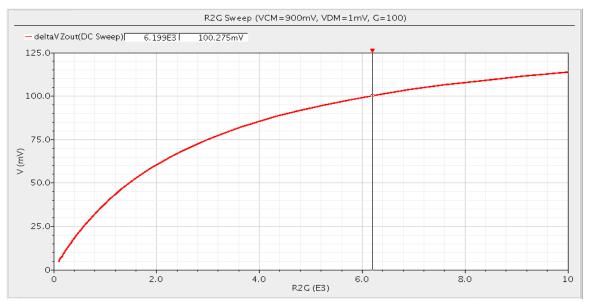

| Figure 5-14: Output Voltage vs. Gain Resistor (R2)                        | 54  |

| Figure 5-15: Output Voltage vs. Gain Resistor (R2) – Zoomed in            | 54  |

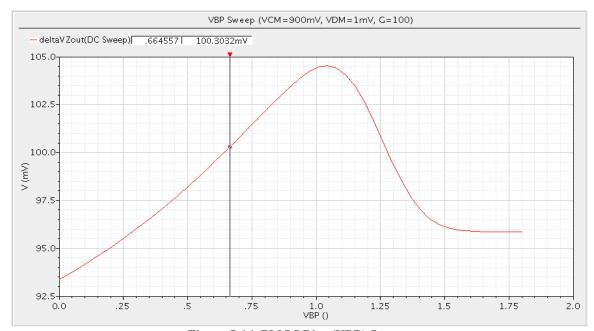

| Figure 5-16: PMOS Bias (VBP) Sweep                                        | 55  |

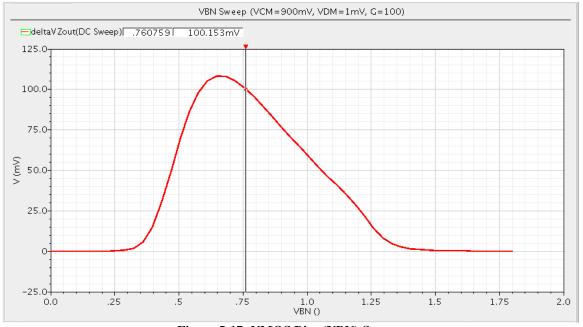

| Figure 5-17: NMOS Bias (VBN) Sweep                                        | 55  |

| Figure 5-18: Output Voltage vs. Temperature @ Gain=100                    | 56  |

| Figure 5-19: Input noise, gain and output noise at Gain=100               | 57  |

| Figure 5-20: Output Noise vs. Frequency for VDM 0.1mV to 2mV              | 58  |

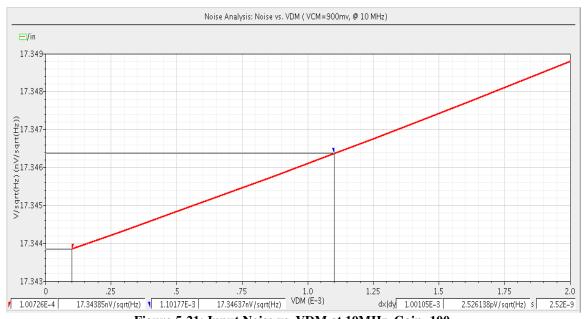

| Figure 5-21: Input Noise vs. VDM at 10MHz, Gain=100                       | 59  |

| Figure 5-22: Output Noise vs. VDM at 10MHz, Gain=100                      | 59  |

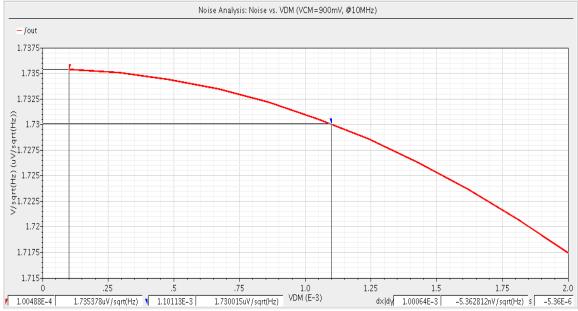

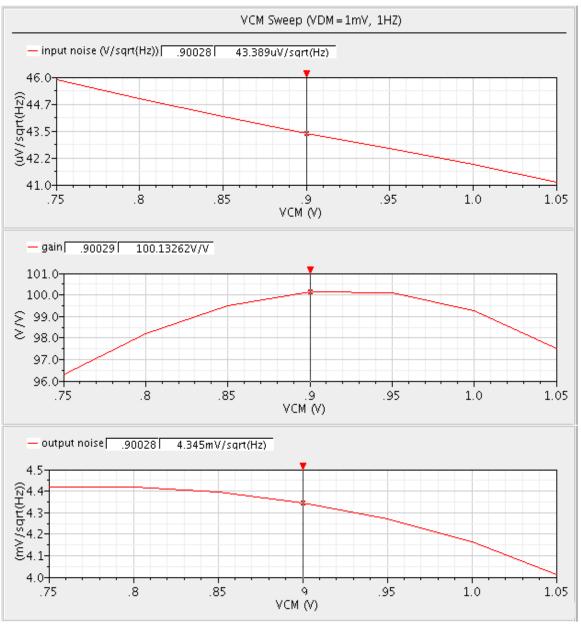

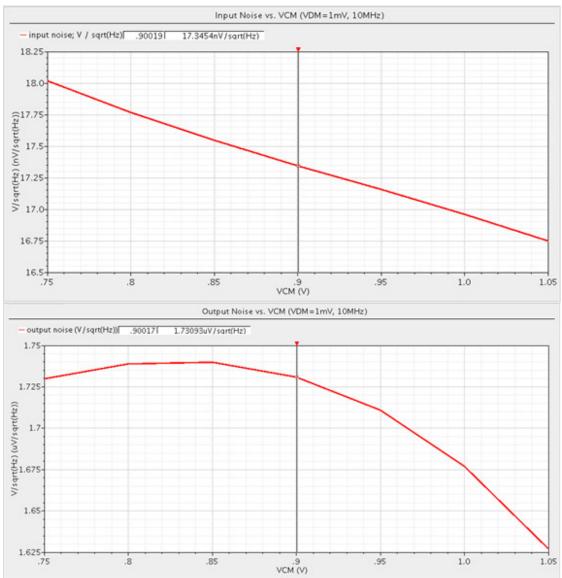

| Figure 5-23: Input noise, gain and output noise vs. VCM @ 1Hz Gain=100    | 60  |

| Figure 5-24: Input and output noise vs. VCM at 10MHz, Gain=100            | 61  |

| Figure 5-25: Input noise, gain and output noise vs. VCM @ 100MHz Gain=100 | .62 |

|                                                                           |     |

# **List of Tables**

| Table 2-1: Characterization result for thermal chip resistor (510 $\Omega$ ) | 12 |

|------------------------------------------------------------------------------|----|

| Table 2-2: Characterization results for thermal chip resistor $(1K\Omega)$   | 12 |

| Table 3-1: Characterization results of discrete IRS (circuit in Figure 3-1)  | 18 |

| Table 3-2: Comparison results of current sensor using PCB IR drop            | 19 |

| Table 3-3: Comparison results of current Sensor using substrate IR drop      | 20 |

| Table 3-4: Comparing accuracy of current sensor using substrate IR drop with |    |

| linear fit                                                                   | 23 |

| Table 3-5: PCB Surface temperature at different spots marked on Figure 3-5A  | 24 |

| Table 3-6: PCB Surface temperature at different spots marked on Figure 3-5B  | 24 |

| Table 5-1: Input and output targets for integrated circuit of IRS            | 41 |

| Table 5-2: Suggested transistor sizing for Figure 5-3                        |    |

|                                                                              |    |

#### **List of Abbreviations**

3D Three Dimensional

ADC Analog to Digital Converter ALU Arithmetic Logical Unit

ASIC Application Specific Integrated Circuit

BW Bandwidth

BOM Bill Of Material

CM Common Mode

CMRR Common Mode Rejection Ratio

CPU Central Processing Unit CUT Circuit Under Test

DAC Digital to Analog Converter

DM Differential Mode

GBWP Gain Bandwidth Product GPU Graphics Processor Unit IA Instrumentation Amplifier

IC Integrated Circuits

IR Voltage drop across a resistive path indicated as IR where "I" is

the current multiplied by "R" resistant per ohm's law.

IRS Inherent Resistance current Sensing

PCB Printed Circuit Board

PDN Power Delivery Network

SKU Stock Keeping Unit

SoC System on Chip; or SOC

VR Voltage Regulator

# **Chapter 1** Introduction

In the modern era of large scale integrated circuits (IC), System-on-Chips (SoCs) are being designed capable of drawing current in excess of 100A at voltage of 1V. The trivial examples of these devices are multi-core Central Processing Units (CPUs) and Graphics Processing Units (GPUs), which are found in personal computers, work stations, servers, laptops and other form of computers.

Once an IC is designed and fabricated, its power consumption depends on:

- Operating parameters such as junction temperature, voltage and frequency.

- Utilization of power containment features such as clock gating, power gating, voltage/frequency islands, and dynamic voltage control.

- Activity factor as how much hardware is utilized and for how long; it mainly depends on the software application used.

In this concept, product requirements such as performance, cost, and form factor along with environmental conditions such as ambient temperature define the bounding conditions for power. An extensive post-design characterization is required to measure and analyze all the above parameters within their practical and feasible range to properly define operating clocks and voltages.

One of the critical parameters to measure is the electrical current itself. Any inaccuracy in the current measurement can impact end product performance, cost or power consumption. As such, an accurate and sophisticated measurement system is required to handle this task.

In this dialogue, post-design characterization, the electrical current is considered as combination of static and dynamic components. It might not be possible to physically separate these two components, yet it allows analyzing them individually.

#### **Static Component**

The static component of the load current is defined by silicon leakage when all clocks are turned off and all activities are seized. The leakage is function of:

- Silicon Physics (defined by the technology used)

- Junction Temperature

- Operating Voltage

#### **Dynamic Component**

The dynamic component of the load current is function of:

- Operating Frequency

- Operating Voltage

- Activity Factor

In CMOS technology the majority of current consumption is expected to be dynamic component. But, the device leakages are increasing generation over generation, as a result, the proportion of the static load is growing.

The dominant portion of total power consumption and dynamic component in GPUs is application dependent. To a degree that specialized applications are developed to stress GPUs beyond typical conditions that games or 3D application could do.

With this introduction, the question stands what are the methods to measure current and ultimately power consumptions in large size silicon devices?

# 1.1 Discrete Techniques for Current Sensing

Monitoring power supply current has become an increasingly standard requirement for many circuits and systems, and in particular, for GPUs and CPUs. Conventional techniques for monitoring power supply current rely on board level circuits to provide a signal representing the monitored current. Such a signal is often analog in form or digital, relayed via an interface data bus (like I2C - Inter IC) for the voltage rail, which the current is being monitored (e.g., VCC for bipolar circuits, or VDD voltages for MOS circuits). Such conventional techniques are often problematic. For example, such techniques require special or custom circuit board design or voltage regulator controllers, all of which add to the BOM (Bill Of Material) costs for the overall product and are often impractical for use in a mass production environment. In the following, common methods are discussed.

# 1.1.1 Voltage Regulator Current Read back

There are commercially available voltage regulators that provide a digital value corresponding to output current. Some may also provide an analog output for on board amplification and conversion to digital signal. As it may sound trivial, the reality is that VR monitors an external signal such as DCR (series resistance) of output stage inductor or  $R_{DSON}$  (on-state drain to source resistance) of high-side power MOSFET. Either way, it has practical limitations as follow:

- The external components to voltage regulator are subject to change SKU (Stock Keeping Unit) to SKU. Even functional equivalent component from different vendors can be used on the same SKU, which will require qualification and engineering verification of the solution each and every time a different component is used.

- Manufacturing tolerances (part to part variation) of power inductors can easily reach to 20%. This is too much error to be tolerated in most applications. To put this in perspective, consider that 20% error in a 100A design with a 4-phase regulator means 20A, which is nearly output current of one phase of VR. This could easily change design target to a 3 or 5 phase solution. Tolerance of power MOSFET is less than of inductors (~10%) yet it is still too high given other sources of error.

- Both inductor DCR and MOSFET  $R_{DSON}$  have temperature dependency and inherent nonlinearity, which add to the error. Even if it can be calibrated over operating

temperature range it would require temperature sensor of some kind added, which adds to the cost.

- The provided signal has limited effective bandwidth (BW) of less than Kilo-hertz (KHz) in most cases, or few KHz in some cases. This is mainly due to nature of voltage-mode instrumentation amplifier used to eliminate common-mode voltage. This will be reviewed further in this investigation. As such, it is not useful for dynamic load monitoring, where high BW in order of tens of MHz needed.

- Some regulators have integrated power stage. It allows compensating for  $R_{DSON}$  variation, to increase the accuracy of current measurement, but they still suffer from low BW, which perhaps can be corrected via architecture proposed in chapter 4. Yet, this type of regulator have premium cost adder that limits their usage to high end products. Aside from cost impact, it still monitors current going through high-side MOSFET as oppose to load behavior. This is a fundamental difference between this method and that of proposed in this thesis.

#### 1.1.2 Series Sense Resistor

Sense Resistor may be placed between output of regulator and the load, in such a case it can provide adequate accuracy for measurement and with right choice of resistor, very low temperature and part-to-part variation can be achieved. Although in high-end CPUs and GPUs, the load current can easily exceed 100A. Even with a  $0.1 \text{m}\Omega$  resister, there is > 1W power wasted in the resistor. Furthermore, PCBs (printed circuit boards) for such application are designed to minimize power delivery network resistance between source and the load. In a practical case, it is  $0.3 \sim 0.5 \text{m}\Omega$ , such a series sense resistor yields 20% to 30% negative impact. Therefore, it is counter intuitive to use it. Alternatively, the inherent PCB resistance itself may be used as sense resistor; this indeed is the idea, which will be further reviewed in this thesis.

#### 1.1.3 Hall Sensor

Other technique is to include a HALL sensor on the current path, which yields acceptable error of 5%, but it is challenging to be incorporated into small form factors, and yet has considerable BOM cost increase, and offers limited bandwidth (in KHz range).

#### Summary

Here is the list of short coming and concerns with conventional discrete current sensing methods:

Demands special/custom board-level design or voltage regulator controller that adds to the BOM cost and makes it impractical to be used in mass production or in value segment.

- Static current measurement requires calibration, which needs to be done per SKU variant as oppose to ASIC variant. This impacts time to market and increases engineering cost.

- Considerably inaccurate dynamic current measurement due to either inherent amplifier limited gain bandwidth product or monitoring power component's current profile as oppose to actual load current profile.

- Poor accuracy (board to board) even after calibration due to component variation or drift over temperature

# 1.2 Integrated Techniques for Current Sensing

Built-in current sensors have speed and resolution enhancements over off-chip current sensors, mainly because the large transient currents in the output drivers are bypassed and less parasitic are encountered [2]. In this section, conventional integrated current sensor architectures are reviewed.

#### 1.2.1 High-Side Current Sensing

In this method, the current is typically determined by measuring small voltage drop across a current sense resistor inserted in series within the circuits. The sense-resistor can either be implemented between the negative power supply and the load, which is called Low-Side current-sensing, or between the positive power supply and the load, so called high-side current-sensing. An amplifier is required to measure this voltage drop across the sense resistor [1]. Both methods are implemented in commercially available ICs [1], although the high-side sensing is more popular, as such it is reviewed here.

In a recent work [1], considerable improvements made in the circuit characteristics compared to LTC6102, like reduced offset voltage, reduced power consumption, while increasing CMRR, but there are two fundamental differences between this technique and proposal in this investigation:

- The high-side sensing is effective method for monitoring battery charge, also known as Coulomb counting, which was the purpose of the author as well [1]. But, in most applications, there is some type of voltage regulator between source (battery or otherwise) and the load (GPU or CPU). Therefore, current information extracted by this method doesn't represent load behavior and it depends on voltage regulator design and its performance such as efficiency.

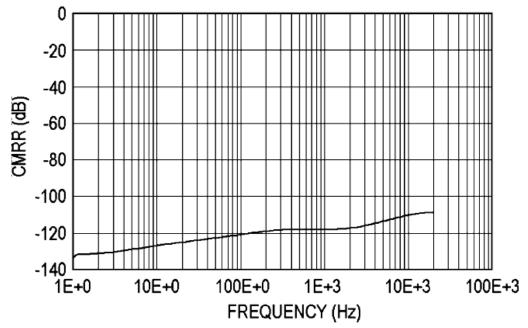

- Despite high CMRR achieved (140dB), it is limited to a relatively narrow frequency range like 10Hz, and as frequency increases the CMRR falls rapidly. At 10 KHz, CMRR is reduced to 110dB (per Figure 1-1). This can also be realized by relatively low Gain Bandwidth Product (GBWP) of the amplifier specified as 1MHz [1]. For dynamic current sensing, high CMRR is required over much wider BW like tens of MHz in order to archive adequate dynamic gain accuracy.

Figure 1-1: CMRR as function of frequency [1]

### 1.2.2 Iddq Sensing

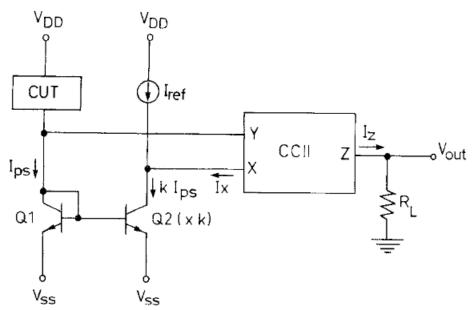

*Iddq* current sensing is a known method for local current sensing in the integrated circuits. It can be used to measure quiescent or transient current of the analog or digital circuits. There are both CMOS and Bipolar implementation of *Iddq* sensing. Figure 1-2 is an example of bipolar method [2] intended as a built-in test cell, which is briefly reviewed here.

Figure 1-2: Example of Iddq Current Sensing [2]

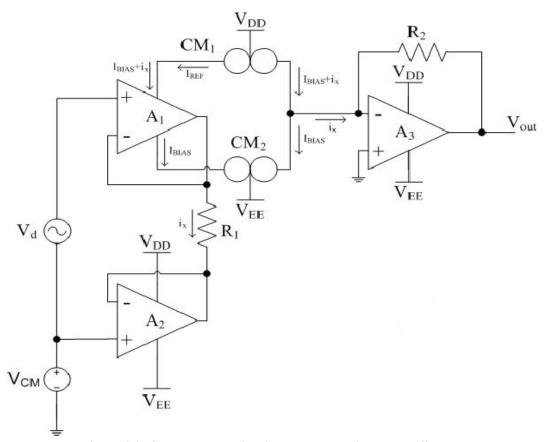

The proposed circuit, based on a current conveyor second generation (CCII) as signal processing circuit, provides an analogue output proportional to the variation of the Iddq or  $I_{ps}$  current of the CUT (Circuit Under Test). The built-in current sensor utilizes a bipolar transistor as a current sink device. The quiescent current  $I_{ps}$ , drawn by the detecting transistor, Q1, is mirrored and scaled to transistor Q2. The current drawn by Q2, which is an image of the quiescent current of the CUT, is compared to the reference current to generate the  $V_{out}$  [2].

This method is effective, where CUT consumption is low to moderate. For large size silicon devices such as GPUs and CPUs the load current can exceed 100A, where sizing of Q1 becomes impractical even during test cycle. The highlight of this implementation is CCII, which is used as amplifier circuit. Advantages offered by CCII are reviewed in chapter 4.

## 1.3 Criteria for Current Sensor Architecture

Accordingly, it would be desirable to have a technique for monitoring current flow to an IC in a temperature-compensated manner which is not dependent upon individual product designs incorporating the IC to be monitored. Further, or alternatively, it would be desirable to avoid any requirement for adding or using special discrete components, structures or designs within the circuit under test, i.e., to use elements or parameters inherent in the design of the IC being monitored. Further, or alternatively, it would be desirable to have such a technique capable of being integrated into the IC, i.e., the silicon die itself, within which the current is to be monitored. Yet, it must provide adequate bandwidth to allow profiling dynamic behavior of the load.

In this investigation above criteria is used and referred to as the guideline to compare different architectures and solutions to decide about effectiveness and robustness each can offer.

# Chapter 2 Inherent Resistance current Sensing (IRS)<sup>1</sup>

# 2.1 The Concept

In this section, method is provided for monitoring current flow to an integrated circuit (IC), alone or mounted on a substrate, in a temperature-compensated manner. In accordance with a preferred embodiment, a plurality of resistances having substantially equal temperature coefficients establishes a ratio of an output voltage and an internally measured voltage, with the output voltage corresponding to a voltage drop across an inherent resistance within the IC or on the substrate (Figure 2-1).

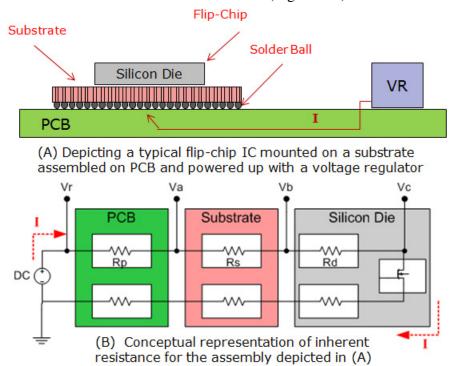

Figure 2-1: Conceptual view of current path

Figure 2-1A depicts a side view of a flip-chip IC mounted on a substrate assembled on PCB and powered up by a voltage regulator (VR). The current 'I' supplied by VR, flows through PCB power planes, traces and vias to get to substrate. Then it flows through solder balls, substrate's micro-vias to get to the silicon bumps, where it finds its way through metal layers to the silicon devices. Figure 2-1B is a conceptual representation of inherent resistance realized as a lump sum for each individual assembly as follow:

$R_p$  = Equivalent PCB inherent resistance between voltage regulator output and solder balls

$R_s$  = Equivalent substrate inherent resistance between solder balls and silicon bumps

$R_d$  = Equivalent silicon-die inherent resistance between silicon bumps and silicon devices

(2-1)

<sup>&</sup>lt;sup>1</sup> AMD, Advanced Micro Devices, has filed patent application on this technique (AMD Ref# 090247)

$R_p$ ,  $R_s$ , and  $R_d$  are all function of temperature. Generally, silicon die, substrate and PCB each are fabricated separately and assembled together to build a product. Figure 2-1B also depicts inherent resistance on the return path. It is acknowledged here that such resistance exists and it is an important factor in power delivery network analysis, but it is not evaluated in this investigation. Yet, similar conclusions and methods would apply.

The evaluation of these current delivery paths includes measuring the voltages at the ends of such paths to determine the voltage drop V between them, which is equal to a product of the resistance R of such current path and the current I flowing through such current path per Ohm's law:

$$V = IR (2-2)$$

Referring to Figure 2-1B, this can be better understood by realizing, relative to the circuit reference potential, e.g., circuit ground, a voltage  $V_a$  will appear at the substrate electrode, another voltage  $V_b$  will appear at the IC electrode and another voltage  $V_c$  will appear at the node or electrode connecting the one or more devices. These voltages  $V_a$ ,  $V_b$ , and  $V_c$  will be different, albeit slightly, due to voltage drops across the resistances, as such let be:

$$V_p = V_r - V_a = IR_p$$

$$V_s = V_a - V_b = IR_s$$

$$V_d = V_b - V_c = IR_d$$

(2-3)

Given  $R_p$ ,  $R_s$ , and  $R_d$  are minimized by design to reduce power dissipation and improve PDN bandwidth (BW), they are in the order of milliohms or less. Therefore even at high current level like 100A the voltage difference between each pair of electrodes (Figure 2-1B) is in few millivolts or less. Thus, an amplifier circuit, such as instrumentation amplifier (IA), is required with amplification gain of G. Thereby, these voltage differences  $V_p$ ,  $V_d$ , and  $V_s$  are amplified to provide  $GV_p$ ,  $GV_d$  and  $GV_s$ , which are proportional to the load current I. Then, output voltage of IA can be digitized and calibrated under known load conditions. Now by measuring the output voltage, the equivalent load current can be calculated at any given moment.

Since this method uses inherent resistance of the current carrying material, there is no need for any additional series components, so the circuit performance is not impacted. Yet, the actual current profile can be extracted to provide insight into the circuit behavior, which may not be available otherwise. To achieve this, adequate bandwidth and amplification circuit is required, which is reviewed in chapter 3 and 4. The target is to use substrate or on-die inherent resistances instead of PCB ones, to meet criteria specified in section 1.3. The reason is that once silicon die and substrate designed and verified,  $R_s$  and  $R_d$  are no longer variable, but several circuit boards usually are designed per application requirement. Therefore, PCB inherent resistance is subject to change (see chapter 3 for further details). Despite simplicity of the idea, there are challenges and details to be considered in order to yield adequate results. One of many is the temperature effect on the material resistance. It is reviewed in details in section 2.2.

# 2.2 Temperature Dependence of Inherent Resistance

Each equivalent inherent resistance illustrated in Figure 2-1 can be considered as the variable R, which is a function of the geometry and effective temperature coefficient of the materials used to fabricate it. Once the substrate, for given silicon, has been designed, the material and the geometries are no longer variable, with the exception of fabrication tolerances. However, this resistance R will be a function of temperature T, and it can be written as:

$$R(T) = R_0(1 + Coeff(T - T_0))$$

(2-4)

Where,  $R_0$  is the resistance at temperature  $T_0$  and Coeff is the equivalent temperature coefficient in percent per degrees Centigrade. For purposes of this investigation, a linear temperature coefficient is presumed.

**Example:** A typical junction temperature increase of 40°C (e.g., ranging from 50°C to 90°C) is expected for a commercially available GPU used in a video card. With copper currently being the dominant conductive material, with temperature coefficient of 0.39% per degree Centigrade the inherent resistance varies by 16% over the specified temperature range. Accordingly, even assuming and ideal IA (with no error) to amplify the voltage difference, the measured current will have up to 16% inaccuracy just due to temperature variation presumed here.

This example shows for IRS to be an effective current measurement technique, need to develop a compensation mechanism for temperature variation. Now, to take into account temperature effect equation 2-2 can be rewritten as:

$$\Delta V(t) = I(t)R(T) \tag{2-5}$$

Where, t is time to indicate variation over time is expected, and  $\Delta V$  can be voltage difference between each pair of electrodes shown in Figuer-1B.  $\Delta V$  is changing due to both current I(t), and resistance R(T) function of temperature T.

#### 2.2.1 Temperature Compensation Technique

The following methods can be used to compensate for temperature drift:

- Building compensation circuit into the amplifier circuit; referred to as analog compensation in this work.

- Measuring temperature at any given interval that voltage difference is measured to adjust the output voltage numerically afterward; referred to as digital or numerical compensation in this work.

Either method has its own pros and cons. In this section, the analog compensation technique is reviewed. In section 3.2, the digital or numerical method is described.

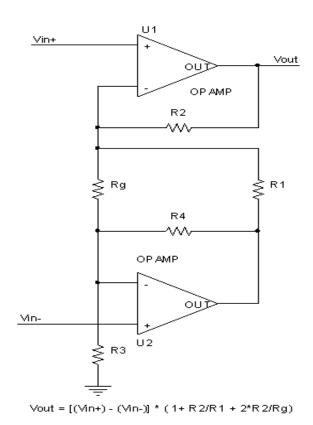

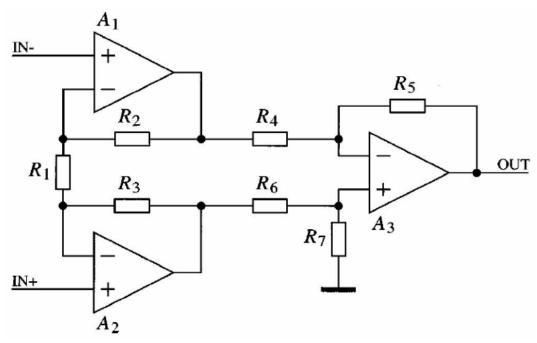

Since the inherent resistance R is very small (e.g., in the range of milliohm), the change in voltage  $\Delta V$  is also very small (e.g., in the range of millivolts), thereby it requires amplification of some sort. In order to describe the analog compensation technique a typical instrumentation amplifier, such as in Figure 2-2, with a gain of G is assumed. The characteristics of the amplifier, such as thermal drift, input and output offsets, etc, will affect the overall accuracy of the circuit, although those are circuit design challenges that need to be dealt with regardless of current sensing technique used. Thereby assuming an ideal IA for the evaluation for Figure 2-2, it can be written that:

$$V_{out} = \Delta VG \tag{2-6}$$

Where:

$$G = 1 + R2/R1 + R2/Rg$$

(2-7)

$\Delta V = Vin_{+} - Vin_{-}$

Figure 2-2: Typical Voltage-Mode Instrumentation Amplifier

For IRS, as discussed in section 2.1, the amplifier can be designed to have its gain function of temperature in a way to cancel out variation of  $\Delta V$  due to temperature. To realize this, the resistances, R1, R2, R3, and R4, are established with absolute and mutually relative values as follows:

$$R1 = R2$$

$$R3 = R4$$

(2-8)

By plugging equations (2-8) into (2-7), it yields:

$$G = 2(1 + R1/Rg) (2-9)$$

By keeping G >> 1, it can be simplified to:

$$G = 2R1/Rg$$

$G >> 1$  (2-10)

Now by choosing proper type of resistors for R1 and  $R_g$ , this circuit can be thermally compensated. R1 (so as R2 to R4) must have a negligible change of resistance within target operating temperature range, while Rg must have same temperature coefficient as the inherent resistance material. The nominal value of  $Rg_0$  is selected to provide adequate gain at nominal temperature  $T_0$ . It can be expressed as follow:

$$Rg(T) = Rg_0(1 + Coeff(T - T_0))$$

(2-11)

By plugging equations (2-10) into (2-6), the amplified output voltage  $V_{out}$  can be expressed as function of temperature as follow:

$$V_{out}(t) = \Delta V(t, T) G(T) = \frac{2R1}{Rg(T)} I(t) R(T)$$

(2-12)

Substituting the temperature dependency relationships for the resistances, equations (2-11) and (2-4), the relationship between the inherent resistance R(T), see equation (2-2), and gain resistance Rg(T) can be expressed as follows:

$$\frac{R(T)}{Rg(T)} = \frac{\left[R_0 \left(1 + Coeff (T - T_0)\right)\right]}{\left[Rg_0 \left(1 + Coeff (T - T_0)\right)\right]} = \frac{R_0}{Rg_0}$$

(2-13)

Substituting this result into equation (2-12) yields:

$$V_{out}(t) = \Delta V(t, T) G(T) = 2R1 \frac{R_0}{R g_0} I(t) = Kr I(t)$$

(2-14)

As it can be seen from (2-14) expression, the amplified voltage difference is independent from temperature variations, where Kr is the overall gain of the system.

## 2.2.2 Using Thermal Chip Sensors as Gain Resistor

In section 2.2.1, it was specified that for adequate analog compensation the gain resistor in the amplifier circuit must have same temperature coefficient as the inherent resistance material. In this section an example is provided to prove practicality of such requirement. Given common material used in PCB and substrate fabrication is copper, the gain resistor temperature coefficient must be same as of copper.

KOA manufactures thin film resistors, LP73 family, with various coefficients so called thermal chip sensors. To compensate for the resistance across copper path, part with the closet coefficient, 0.4%/°C, is selected. The typical gain needed at nominal temperature

defines the nominal value  $(Rg_0)$ . In this evaluation, gain resistor values of  $510\Omega$  and  $1K\Omega$  are chosen, which will be used in chapter 3 to review discrete implementation of the circuit (for locations R4222 and R4211 in Figure 3-1 accordingly). Equation (2-15) is provided in the manufacturer's datasheet to calculate the resistance.

$$R(T) = R_{25}(C_0 + C_1T + C_2T^2)$$

(2-15)

Where, T is the ambient temperature in degree Centigrade, R(T) is the resistance value at given T, and  $R_{25}$  resistance value at 25°C. For T.C.R 4000ppm (0.4%/°C) parts, the constants are:

$$C_0 = 0.907050$$

$C_1 = 0.00361010$  (2-16)

$C_2 = 4.33462 \times 10e - 6$

Table 2-1 and Table 2-2 provide calculated and measured values for each resistor (510 $\Omega$  and 1K) at various temperatures. The difference between measured and calculated values is better than  $\pm 2\%$ . Given uncertainty in the measurement, temperature stability of the environment, and uncontrolled humidity while performing the test, the yielded results deemed acceptable.

| Tomporaturo         | 510Ω (Ordinary) | R              | g = 510Ω (PTC)  |                   |

|---------------------|-----------------|----------------|-----------------|-------------------|

| Temperature<br>(°C) | MEASURED<br>(Ω) | CALCULATED (Ω) | MEASURED<br>(Ω) | Difference<br>(%) |

| 24.5                | 508             | 509.03         | 518             | 1.76%             |

| 35.0                | 508             | 529.74         | 535             | 0.99%             |

| 45.0                | 508             | 549.92         | 553             | 0.56%             |

| 55.0                | 508             | 570.55         | 572             | 0.25%             |

| 65.0                | 508             | 591.61         | 591             | -0.10%            |

| 75.0                | 508             | 613.12         | 606             | -1.16%            |

Table 2-1: Characterization result for thermal chip resistor (510 $\Omega$ )

| Tomporaturo         | 1KΩ (Ordinary)  | F              | Rg = 1KΩ (PTC)  |                   |

|---------------------|-----------------|----------------|-----------------|-------------------|

| Temperature<br>(°C) | MEASURED<br>(Ω) | CALCULATED (Ω) | MEASURED<br>(Ω) | Difference<br>(%) |

| 24.5                | 998             | 998.10         | 1010            | 1.19%             |

| 35.0                | 998             | 1038.71        | 1046            | 0.70%             |

| 45.0                | 997             | 1078.28        | 1083            | 0.44%             |

| 55.0                | 998             | 1118.72        | 1123            | 0.38%             |

| 65.0                | 997             | 1160.02        | 1157            | -0.26%            |

| 75.0                | 998             | 1202.19        | 1196            | -0.51%            |

Table 2-2: Characterization results for thermal chip resistor  $(1K\Omega)$

Both tables also contain measurements for an ordinary resistor at same nominal value, where expected to have a negligible variation over the same temperature range.

Figure 2-3: Characterization result for thermal chip resistor (510 $\Omega$ )

Figure 2-4: Characterization result for thermal chip resistor (1K)

## 2.3 Conclusions

The concept of current sensing using inherent resistance was described. The temperature dependence of the inherent resistance was indicated as a critical parameter impacting accuracy of this technique. Analog compensation technique was introduced and mathematically proved being effective to compensate for temperature drift within an amplifier circuit (as gain resistor). A practical example of resistor that can provide desired behavior for compensation was given. Further in this work, this technique, inherent resistance current sensing, is referred to as *IRS*.

# **Chapter 3** Discrete Implementation of IRS

In this chapter, discrete implementation of IRS is reviewed, followed by analysis of the characterization results. The importance of discrete case study is to provide insight to effectiveness of the solution and reveals the challenges to overcome. All at much lower development and fabrication cost compared to an integrated implementation. Despite that, there are systematic limitations in the discrete implementation that will be highlighted at the end of this chapter, which are the motivation to design integrated version of IRS.

#### 3.1 Circuit Schematic

Figure 3-1 is the schematic of IRS discrete implementation. Two instrumentation amplifiers are constructed each using two commercially available operation amplifiers. One IA, labeled as Config1, to amplify the voltage drop across PCB, difference between output of voltage regulator and BGA solder balls at PCB. The other IA, labeled as Config2, is to amplify the voltage drop across substrate, between BGA solder balls and top of the substrate (accessible via another BGA ball labeled as  $FB\_VDDC$ ). The outputs of the IAs could be monitored via oscilloscope, precision digital multi-meter, on-board 12-bit ADC, or built-in 10-bit ADC as needed. The circuit was tested on two graphics card designs one with a high end GPU capable of consuming typical current of 120A and one mid-range GPU consuming typical current of 80A on core logic (labeled as VDDC).

The opamp specs such as noise, input offset and offset drift are crucial to achieve adequate accuracy. In this implementation, MAX4239A was selected primary due to having very low input offset voltage (typical  $0.1\mu V$ , Max  $2\mu V$ ), low offset drift (typical 50nV/1000hr) and low input noise ( $30nV/\sqrt{Hz}$  @ 1KHz). It also provides adequate GBWP (6.5MHz) and CMRR (Min 120dB, typical 140dB) as good starting point. But it requires minimum closed loop gain of 10 for stability, which can be met.

All resistors  $R_1$  through  $R_4$  are shown as 10K, although in order to maximize the gain they were increased to 14.7K for Config1 and to 78.7K for Config2. The mismatch between  $R_1 \sim R_4$  will add to circuit gain inaccuracy and decreases CMRR. Thus, 0.1% tolerance resistors were used for R1 through R4 in both IAs. With these settings, two gain resistors  $R_g$  (locations R4211 and R4222) define each amplifier gain and they must also provide thermal compensation as described in section 2.2.1. Hence, thermal chip sensors introduced in section 2.2.2 with same values of  $510\Omega$  and 1K used for locations R4222 and R4211 accordingly. The amplification gain was calculated, using equation (2-7), to be about 31 for Config1 and about 310 for Config2 at 25°C.

Figure 3-1: Discrete Implementation of the instrumentation amplifier

Per Figure 2-1B, voltage level must be sampled at  $V_r$ ,  $V_a$ , and  $V_b$  nodes for current sensing purpose. Based on that and Figure 3-1, the following equations show the mapping of  $V_r$ ,  $V_a$  and  $V_b$  to circuit opamp inputs and provide relation between inputs and outputs of IAs:

Voltage at the regulator:

$$ADC CH1 = V_r$$

Voltage drop across PCB power planes:

$$ADC\_CH2 = G_{PCB} I R_p = G_{PCB} (V_r - V_a) \text{ where } G_{PCB} \cong 31$$

(3-1)

Voltage drop across substrate:

$$ADC\_CH3 = G_{sub} I R_s = G_{sub} (V_a - V_b) \text{ where } G_{sub} \cong 310$$

(3-2)

# 3.2 Characterization Results and Analysis

In this section, characterization results are presented. The analysis of the data gives insight into the circuit performance and load behaviors. Table 3-1 lists inputs, outputs, ASIC junction and PCB temperature at multiple points. It also contains comparison between current measured and reported numbers by the voltage regulator. The GPU under test has four on-die temperature sensors ( $TS_0$  to  $TS_4$ ) and one external temperature sensor (on-board), which measures the GPU temperature via remote sensing of on-die thermal diode.

The bolded row in Table 3-1 corresponds to midpoint temperature  $\sim 73.1^{\circ}\text{C}$  reported by on-die temperature sensor number zero  $(TS_0)$ . This row is used as the reference for compensation over temperature in Table 3-2 and Table 3-3. The highlighted numbers, in the red, in Table 3-1 show excess of inaccuracy in the regulator current read back at light loads. This is a known issue with regulator current readout.

Table 3-2 provides first order linearity error in percentage compared to the reference row (midpoint temperature in bold). This hand-calculated indicator can be used to compare effectiveness of a solution without having sophisticated tools for curve fitting. Note must be taken that it is not representing the current readout accuracy; although the better this number gets the better accuracy can be achieved via post numerical calibration. The first column of Table 3-2 represents the actual measured values of PCB IR drop as shown in Table 3-1. The following two columns are calculated effective resistance and linearity error. These sets of data are benefitting from gain adjustment provided by  $R_g$  (1K) over temperature range. It shows an overall linearity better than  $\pm 6\%$ . By calculating  $R_g$  (1K) using equation (2-15) and (2-16), the expected output voltage using equation (2-15) and circuit settings the next five columns of Table 3-2 are equated. The calculated error is about  $\pm 6\%$  inline with the measurement.

The  $R_g$  (R4211 in Figure 3-1) is installed on the surface of the PCB and it can monitor temperature of one spot only. However, such arbitrary spot is not necessarily the optimal point (see section 0). To evaluate this matter, PCB temperature was measured at different spots like closer to power plane, where current was flowing through. The results are reported under Plane-1 and Plane-2 columns in Table 3-1. The last five columns of Table 3-2 are calculated in the similar manner described above but instead of using  $R_g$  temperature, this time temperature reported under Plane-1 column was used. Comparing the maximum linearity errors, highlighted numbers in **green** and in **red**, it clearly shows a considerable improvement.

|           | VDDC (GP | VDDC (GPU Core Voltage | age )    |              | PCB Ter  | PCB Temperature Measured @ | • Measur | ed @    | ASICJ   | ASIC Junction Temperature Measured By | mperatur | e Measur | ed By  | <u>a</u>                  | PCB IR Drop           |            | Substrate IR<br>Drop  |

|-----------|----------|------------------------|----------|--------------|----------|----------------------------|----------|---------|---------|---------------------------------------|----------|----------|--------|---------------------------|-----------------------|------------|-----------------------|

| Measured  | Measured | Current                | Current  |              | VDDC     | VDDC                       | Rg       | R       | 1S0     | TSI                                   | TS2      | TS3      | EXT TS | Measured<br>Voltage Delta | Measured<br>Amplifier | Calculated | Measured<br>Amplifier |

| Feedback  | Current  | Reported<br>By VR      | Error    | rower<br>(W) | Ħ        | 5                          | (510R)   |         | Average | Average                               | Average  | Average  | đ      | [VDDC_VT-                 | Output                | Gain       | Output                |

| Point (V) | (A)      | (A)                    | <u>%</u> | ,            | ()<br>() | (0,)                       | <u>0</u> | <u></u> | (c)     | (0,)                                  | (0,)     | (0,)     | (°C)   | VDDC_ASIC]<br>(mV)        | Voltage<br>(mV)       | (۸/۸)      | Voltage<br>(mV)       |

| 0.9972    | 9.647    | 6.132                  | 36.43%   | 9.620        | 43.6     | 43.6                       | 39       | 41      | 49.04   | 50.98                                 | 44.09    | 45.8     | 53.25  | 3.27                      | 101                   | 30.89      | 35.8                  |

| 1.0473    | 11.325   | 9.197                  | 18.79%   | 11.861       | 44.9     | 44.9                       | 40       | 42      | 50.85   | 52.91                                 | 45.77    | 47.78    | 55.13  | 3.762                     | 115                   | 30.49      | 39.8                  |

| 1.097     | 13.220   | 9.197                  | 30.43%   | 14.502       | 46.0     | 46.3                       | 41       | 43      | 52.93   | 54.5                                  | 47.43    | 49.52    | 57.15  | 4.34                      | 131                   | 30.18      | 44.6                  |

| 1.1603    | 16.195   | 15.329                 | 2.35%    | 18.791       | 47.8     | 48.1                       | 42       | 44      | 56.43   | 57.95                                 | 9.05     | 52.99    | 60.4   | 5.27                      | 158                   | 29.98      | 53.5                  |

| 1.1603    | 17.176   | 15.329                 | 10.75%   | 19.929       | 48.2     | 48.6                       | 42       | 45      | 56.84   | 58.42                                 | 50.99    | 53.45    | 60.89  | 5.556                     | 166                   | 29.88      | 55.9                  |

| 1.1603    | 18.236   | 15.329                 | 15.94%   | 21.160       | 49.1     | 49.5                       | 43       | 45      | 57.8    | 59.33                                 | 51.95    | 54.51    | 61.88  | 5.86                      | 175                   | 29.86      | 57.9                  |

| 1.1603    | 19.160   | 15.329                 | 20.00%   | 22.231       | 49.3     | 49.4                       | 43       | 45      | 58.5    | 60.16                                 | 52.83    | 55.23    | 62.57  | 6.164                     | 182                   | 29.53      | 9.09                  |

| 1.1603    | 20.091   | 18.395                 | 8.44%    | 23.312       | 49.6     | 50.1                       | 43       | 45      | 59.05   | 60.72                                 | 53.5     | 55.93    | 63.14  | 6.448                     | 190                   | 29.47      | 63.1                  |

| 0.9974    | 22.239   | 21.461                 | 3.50%    | 22.182       | 49.2     | 49.5                       | 43       | 45      | 57.51   | 59.55                                 | 52.36    | 54.11    | 61.44  | 7.048                     | 207                   | 29.37      | 57.2                  |

| 0.9973    | 21.099   | 21.461                 | -1.72%   | 21.042       | 48.6     | 49.1                       | 43       | 45      | 57      | 59                                    | 51.7     | 53.6     | 86.09  | 6.685                     | 197                   | 29.47      | 55.8                  |

| 1.0473    | 23.785   | 21.461                 | 9.77%    | 24.910       | 20.0     | 50.5                       | 43       | 46      | 59.32   | 61.59                                 | 54.25    | 56.26    | 63.33  | 7.516                     | 220                   | 29.27      | 61.9                  |

| 1.097     | 27.086   | 27.592                 | -1.87%   | 29.714       | 51.8     | 52.5                       | 44       | 47      | 62.32   | 64.8                                  | 57.2     | 59.5     | 66.4   | 8.593                     | 249                   | 28.98      | 8.69                  |

| 1.1604    | 32.042   | 30.73                  | 4.09%    | 37.181       | 54.7     | 55.2                       | 45       | 49      | 66.7    | 69.72                                 | 61.9     | 64.13    | 70.8   | 10.17                     | 292                   | 28.71      | 81.6                  |

| 1.1604    | 36.320   | 33.812                 | 6.91%    | 42.146       | 29.7     | 57.8                       | 47       | 20      | 69.7    | 73.35                                 | 65.47    | 67.2     | 73.8   | 11.555                    | 331                   | 28.65      | 89.1                  |

| 1.1604    | 40.677   | 39.862                 | 2.00%    | 47.202       | 58.5     | 59.5                       | 47       | 51      | 73.1    | 77.07                                 | 69.01    | 70.62    | 77.19  | 12.99                     | 370                   | 28.48      | 98.5                  |

| 1.1603    | 44.973   | 45.987                 | -2.25%   | 52.182       | 61.1     | 62.0                       | 49       | 53      | 76.25   | 9.08                                  | 72.54    | 73.99    | 80.23  | 14.445                    | 408                   | 28.25      | 107                   |

| 1.1603    | 49.415   | 49.89                  | -0.96%   | 57.336       | 64.0     | 9.49                       | 51       | 55      | 9.62    | 84.3                                  | 75.9     | 77.1     | 83.3   | 15.97                     | 449                   | 28.12      | 117                   |

| 1.1603    | 64.943   | 64.88                  | 0.10%    | 75.353       | 61.6     | 29.0                       | 46       | 49      | 75.6    | 79.28                                 | 71.66    | 69.61    | 79.15  | 20.42                     | 584                   | 28.60      | 137                   |

| 1.1604    | 70.938   | 70.75                  | 0.26%    | 82.316       | 64.3     | 9.19                       | 48       | 51      | 78.5    | 83.25                                 | 75.75    | 73       | 82.5   | 22.7                      | 645                   | 28.41      | 146                   |

| 1.1603    | 77.629   | 77.77                  | -0.18%   | 90.073       | 8.79     | 64.3                       | 49       | 53      | 82.75   | 88.5                                  | 80.5     | 76.75    | 86.125 | 25.31                     | 60/                   | 28.01      | 155                   |

| 1.1603    | 86.676   | 86.64                  | 0.04%    | 100.571      | 72.6     | 68.5                       | 52       | 55      | 88      | 95                                    | 86.75    | 81.75    | 91.125 | 28.88                     | 800                   | 27.70      | 168                   |

| 1.1603    | 96.104   | 95.43                  | 0.70%    | 111.510      | 78.2     | 72.9                       | 54       | 58      | 93.75   | 101.25                                | 92.75    | 87.25    | 96.5   | 32.52                     | 894                   | 27.49      | 181                   |

Table 3-1: Characterization results of discrete IRS (circuit in Figure 3-1)

|                                                    |               |                           |                          | Current       | Current Sensor Comparison -                       | mparis         |                           | PCB IR Drop              |                |                                                         |                |                           |

|----------------------------------------------------|---------------|---------------------------|--------------------------|---------------|---------------------------------------------------|----------------|---------------------------|--------------------------|----------------|---------------------------------------------------------|----------------|---------------------------|

| Ā                                                  | PCB IR Drop   | Ь                         | Calcı                    | lated O       | Calculated Output Based on Rg (1K)<br>Temperature | on Rg (1       | IK)                       | Compen                   | sation Us<br>T | Compensation Using Measured VDDC Plane-1<br>Temperature | ad VDDC        | Plane-1                   |

| Measured<br>Amplifier<br>Output<br>Voltage<br>(mV) | ΙΔ/VΔ<br>(Ωm) | Linearity<br>Error<br>(%) | Rg<br>Calculated<br>(KΩ) | Gain<br>(V/V) | Calculated<br>Output<br>Voltage<br>(mV)           | IΔ//VΔ<br>(Ωm) | Linearity<br>Error<br>(%) | Rg<br>Calculated<br>(KΩ) | Gain<br>(V/V)  | Calculated<br>Output<br>Voltage<br>(mV)                 | Δ//\Δ <br>(Ωm) | Linearity<br>Error<br>(%) |

| 101                                                | 1             | -                         | 1.062                    | 29.67         | 97.04                                             | 1              | 1                         | 1.073                    | 29.41          | 96.16                                                   | -              |                           |

| 115                                                | 8.163         | -5.84%                    | 1.066                    | 29.57         | 111.25                                            | 8.468          | -4.58%                    | 1.078                    | 29.28          | 110.14                                                  | 8.325          | -3.21%                    |

| 131                                                | 8.395         | -3.16%                    | 1.070                    | 29.47         | 127.90                                            | 8.636          | -2.68%                    | 1.082                    | 29.16          | 126.57                                                  | 8.510          | -1.05%                    |

| 158                                                | 8.705         | 0.41%                     | 1.074                    | 29.37         | 154.76                                            | 8.816          | -0.65%                    | 1.090                    | 28.98          | 152.75                                                  | 8.641          | 0.48%                     |

| 166                                                | 8.633         | -0.41%                    | 1.078                    | 29.27         | 162.60                                            | 8.708          | -1.87%                    | 1.091                    | 28.94          | 160.82                                                  | 8.587          | -0.15%                    |

| 175                                                | 8.615         | -0.62%                    | 1.078                    | 29.27         | 171.50                                            | 8.669          | -2.31%                    | 1.095                    | 28.86          | 169.09                                                  | 8.490          | -1.28%                    |

| 182                                                | 8.514         | -1.78%                    | 1.078                    | 29.27         | 180.39                                            | 8.762          | -1.26%                    | 1.096                    | 28.84          | 177.74                                                  | 8.575          | -0.29%                    |

| 190                                                | 8.521         | -1.71%                    | 1.078                    | 29.27         | 188.70                                            | 8.776          | -1.10%                    | 1.097                    | 28.81          | 185.74                                                  | 8.576          | -0.28%                    |

| 207                                                | 8.418         | -5.90%                    | 1.078                    | 29.27         | 206.26                                            | 8.674          | -2.25%                    | 1.095                    | 28.85          | 203.30                                                  | 8.508          | -1.07%                    |

| 197                                                | 8.383         | -3.30%                    | 1.078                    | 29.27         | 195.64                                            | 8.610          | -2.97%                    | 1.093                    | 28.90          | 193.23                                                  | 8.476          | -1.45%                    |

| 220                                                | 8.417         | -2.91%                    | 1.082                    | 29.16         | 219.20                                            | 8.641          | -2.63%                    | 1.098                    | 28.77          | 216.21                                                  | 8.491          | -1.27%                    |

| 249                                                | 8.486         | -2.11%                    | 1.086                    | 29.06         | 249.75                                            | 8.757          | -1.32%                    | 1.106                    | 28.59          | 245.67                                                  | 8.573          | -0.32%                    |

| 292                                                | 8.529         | -1.62%                    | 1.094                    | 28.87         | 293.56                                            | 8.775          | -1.11%                    | 1.117                    | 28.31          | 287.90                                                  | 8.562          | -0.45%                    |

| 331                                                | 8.623         | -0.53%                    | 1.098                    | 28.77         | 332.40                                            | 8.824          | -0.57%                    | 1.126                    | 28.12          | 324.90                                                  | 8.575          | -0.29%                    |

| 370                                                | 8.669         | %00.0                     | 1.102                    | 28.67         | 372.40                                            | 8.874          | %00.0                     | 1.133                    | 27.95          | 363.03                                                  | 8.600          | %00.0                     |

| 408                                                | 8.690         | 0.25%                     | 1.111                    | 28.47         | 411.29                                            | 8.896          | 0.25%                     | 1.144                    | 27.70          | 400.18                                                  | 8.606          | 0.07%                     |

| 449                                                | 8.751         | 0.94%                     | 1.119                    | 28.28         | 451.63                                            | 8.917          | 0.48%                     | 1.156                    | 27.44          | 438.15                                                  | 8.599          | -0.01%                    |

| 584                                                | 8.735         | 0.76%                     | 1.094                    | 28.87         | 589.43                                            | 8.905          | 0.35%                     | 1.146                    | 27.66          | 564.76                                                  | 8.474          | -1.46%                    |

| 645                                                | 8.876         | 2.39%                     | 1.102                    | 28.67         | 650.77                                            | 9.034          | 1.81%                     | 1.157                    | 27.41          | 622.17                                                  | 8.582          | -0.21%                    |

| 60/                                                | 8.944         | 3.17%                     | 1.111                    | 28.47         | 720.65                                            | 9.173          | 3.37%                     | 1.172                    | 27.09          | 685.67                                                  | 8.672          | 0.83%                     |

| 800                                                | 9.074         | 4.68%                     | 1.119                    | 28.28         | 816.73                                            | 9.343          | 5.29%                     | 1.192                    | 26.66          | 770.07                                                  | 8.749          | 1.73%                     |

| 894                                                | 9.172         | 2.80%                     | 1.131                    | 27.99         | 910.37                                            | 9.407          | 6.01%                     | 1.216                    | 26.18          | 851.38                                                  | 8.735          | 1.57%                     |

Table 3-2: Comparison results of current sensor using PCB IR drop

|                                        |                   |                           |                                             |                                            |                           | Curren                                             | t Sensol                                       | Current Sensor Comparison – |                                                    | Substrate IR Drop                              | 3 Drop                 |                                       |                                                |                        |                                                                             |                     |                        |

|----------------------------------------|-------------------|---------------------------|---------------------------------------------|--------------------------------------------|---------------------------|----------------------------------------------------|------------------------------------------------|-----------------------------|----------------------------------------------------|------------------------------------------------|------------------------|---------------------------------------|------------------------------------------------|------------------------|-----------------------------------------------------------------------------|---------------------|------------------------|

| Unad                                   | Unadjusted Values | alues                     | Compensation Using On<br>Temperature Sensor | ompensation Using Or<br>Temperature Sensor | g On-Die<br>1sor #0       | Compensation Using On-Die<br>Temperature Sensor #1 | mpensation Using On-E<br>Temperature Sensor #1 | ig On-Die<br>Isor #1        | Compensation Using On-Die<br>Temperature Sensor #2 | mpensation Using On-D<br>Temperature Sensor #2 | ig On-Die<br>isor #2   | Compens                               | mpensation Using On-E<br>Temperature Sensor #3 | ng On-Die<br>nsor #3   | Compensation Using On-Die Compensation Using External Temperature Sensor #3 | tion Usin<br>Sensor | g External             |

| Amplifier<br>Output<br>Voltage<br>(mV) | IΔ//VΔ<br>(Ωm)    | Linearity<br>Error<br>(%) | Adjusted<br>Output<br>Voltage<br>(mV)       | ΙΔ//VΔ<br>(ΩΠΙ)                            | Linearity<br>Error<br>(%) | Adjusted<br>Output<br>Voltage<br>(mV)              | IΔ//ΔI<br>(Ωm)                                 | Linearity<br>Error<br>(%)   | Adjusted<br>Output<br>Voltage<br>(mV)              | ΙΔ//VΔ<br>(Ωm)                                 | Linearity<br>Error (%) | Adjusted<br>Output<br>Voltage<br>(mV) | ΙΔ//VΔ<br>(Ωm)                                 | Linearity<br>Error (%) | Adjusted<br>Output<br>Voltage<br>(mV)                                       | ΙΔ//VΔ<br>(ΩΠ)      | Linearity<br>Error (%) |

| 35.8                                   | ,                 | 1                         | 35.80                                       | 1                                          | 1                         | 35.80                                              |                                                | 1                           | 35.80                                              | -                                              | 1                      | 35.80                                 | •                                              |                        | 35.80                                                                       | 1                   |                        |

| 39.8                                   | 2.383             | 17.9%                     | 42.34                                       | 3.894                                      | <b>%6.9-</b>              | 42.36                                              | 3.906                                          | -7.5%                       | 42.31                                              | 3.881                                          | -7.61%                 | 42.37                                 | 3.912                                          | -6.85%                 | 42.35                                                                       | 3.901               | -6.71%                 |

| 44.6                                   | 2.463             | 21.9%                     | 49.83                                       | 3.927                                      | -6.1%                     | 49.76                                              | 3.906                                          | -7.5%                       | 49.72                                              | 3.896                                          | -7.25%                 | 49.80                                 | 3.918                                          | -6.70%                 | 49.84                                                                       | 3.928               | -6.08%                 |

| 53.5                                   | 2.703             | 33.8%                     | 61.90                                       | 3.985                                      | -4.8%                     | 61.79                                              | 3.970                                          | -6.0%                       | 61.68                                              | 3.953                                          | -5.91%                 | 61.85                                 | 3.978                                          | -5.27%                 | 61.84                                                                       | 3.976               | -4.91%                 |

| 55.9                                   | 2.670             | 32.1%                     | 65.75                                       | 3.978                                      | -4.9%                     | 99:59                                              | 3.966                                          | -6.1%                       | 65.52                                              | 3.947                                          | -6.04%                 | 65.71                                 | 3.973                                          | -5.39%                 | 65.71                                                                       | 3.973               | -5.00%                 |

| 57.9                                   | 2.573             | 27.3%                     | 70.07                                       | 3.990                                      | -4.6%                     | 96.69                                              | 3.977                                          | -5.8%                       | 69.83                                              | 3.961                                          | -5.70%                 | 70.06                                 | 3.988                                          | -5.02%                 | 70.04                                                                       | 3.986               | -4.68%                 |

| 9.09                                   | 2.607             | 29.0%                     | 73.82                                       | 3.997                                      | -4.5%                     | 73.74                                              | 3.988                                          | -5.6%                       | 73.62                                              | 3.975                                          | -5.38%                 | 73.82                                 | 3.996                                          | -4.84%                 | 73.78                                                                       | 3.993               | -4.52%                 |

| 63.1                                   | 2.614             | 29.4%                     | 77.57                                       | 3.999                                      | -4.4%                     | 77.50                                              | 3.992                                          | -5.5%                       | 77.40                                              | 3.983                                          | -5.20%                 | 77.62                                 | 4.003                                          | -4.66%                 | 77.54                                                                       | 3.996               | -4.43%                 |

| 57.2                                   | 1.699             | -15.9%                    | 85.36                                       | 3.935                                      | -5.9%                     | 85.39                                              | 3.938                                          | -6.8%                       | 85.29                                              | 3.930                                          | -6.45%                 | 85.31                                 | 3.931                                          | -6.38%                 | 85.27                                                                       | 3.928               | -6.07%                 |

| 55.8                                   | 1.746             | -13.6%                    | 80.82                                       | 3.931                                      | -6.0%                     | 80.84                                              | 3.933                                          | %6:9-                       | 80.71                                              | 3.921                                          | -6.66%                 | 80.77                                 | 3.927                                          | -6.49%                 | 80.75                                                                       | 3.925               | -6.15%                 |