### Statistical Yield Analysis and Design for Nanometer VLSI

by

### Javid Jaffari

A thesis

presented to the University of Waterloo

in fulfillment of the

thesis requirement for the degree of

Doctor of Philosophy

in

Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2010

© Javid Jaffari 2010

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### **Abstract**

Process variability is the pivotal factor impacting the design of high yield integrated circuits and systems in deep sub-micron CMOS technologies. The electrical and physical properties of transistors and interconnects, the building blocks of integrated circuits, are prone to significant variations that directly impact the performance and power consumption of the fabricated devices, severely impacting the manufacturing yield. However, the large number of the transistors on a single chip adds even more challenges for the analysis of the variation effects, a critical task in diagnosing the cause of failure and designing for yield. Reliable and efficient statistical analysis methodologies in various design phases are key to predict the yield before entering such an expensive fabrication process.

In this thesis, the impacts of process variations are examined at three different levels: device, circuit, and micro-architecture. The variation models are provided for each level of abstraction, and new methodologies are proposed for efficient statistical analysis and design under variation.

At the circuit level, the variability analysis of three crucial sub-blocks of today's system-on-chips, namely, digital circuits, memory cells, and analog blocks, are targeted. The accurate and efficient yield analysis of circuits is recognized as an extremely challenging task within the electronic design automation community. The large scale of the digital circuits, the extremely high yield requirement for memory cells, and the time-consuming analog circuit simulation are major concerns in the development of any statistical analysis technique. In this thesis, several sampling-based methods have been proposed for these three types of circuits to significantly improve the run-time of the traditional Monte Carlo method, without compromising accuracy. The proposed sampling-based yield analysis methods benefit from the very appealing feature of the MC method, that is, the capability to consider any complex circuit model. However, through the use and engineering of advanced variance reduction and sampling methods, ultrafast yield estimation solutions are provided for different types of VLSI circuits. Such methods include control variate, importance sampling, correlation-controlled Latin Hypercube Sampling, and Quasi Monte Carlo.

At the device level, a methodology is proposed which introduces a variation-aware design perspective for designing MOS devices in aggressively scaled geometries. The method introduces a yield measure at the device level which targets the saturation and leakage currents of an MOS transistor. A statistical method is developed to optimize the advanced doping profiles and geometry features of a device for achieving a maximum device-level yield.

Finally, a statistical thermal analysis framework is proposed. It accounts for the process and thermal variations simultaneously, at the micro-architectural level. The analyzer is developed, based on the fact that the process variations lead to uncertain leakage power sources, so that the thermal profile, itself, would have a probabilistic nature. Therefore, by a co-process-thermal-leakage analysis, a more reliable full-chip statistical leakage power yield is calculated.

### Acknowledgements

I would like to express my sincere gratitude to my supervisor Prof. Mohab Anis for his guidance and support during the course of my studies, particularly during the most challenging times. Also, I would like to thank Prof. Dennis Sylvester, Prof. Manoj Sachdev, Prof. Mark Aagaard, Prof. John T.W. Yeow, and Prof. Karim Karim for reviewing this work as well as their valuable comments to make the thesis come out in this current form.

I have been fortunate to work with many wonderful people in the VLSI research group, including: Yasser Azizi, Reza Chaji, Ehsanollah Fathi, Hassan Hassan, Akhilesh Kumar, Minoo Mirsaeedi, Ahmed Nour, and many others. I wish to thank them all for providing a friendly and joyful environment and for their valuable comments and discussions. I would also like to thank Prof. Kumaraswamy Ponnambalam, from Department of Systems Design Engineering for his valuable comments and sharing of his source codes for optimization under uncertainty, Prof. Christiane Lemieux from Department of Statistics and Actuarial Science for her comments on variance reduction methods, Dr. Mohamed Abu-Rahma of Qualcomm Inc for the useful discussions on SRAM cell design for yield, and Dr. Trent McConaghy of Solido Design Automation for comments on analog circuit yield estimation. I would like to thank Dr. Nizar Abdallah and Dr. Julien Dunoyer for their valuable support during my internship at Actel Corporation in 2008.

I am also extremely grateful to my M.Sc. supervisor during my studies at the University of Tehran, Prof. Ali Afzali-Kusha, for his endless kindness and support. Additionally, I want to thank the University of Waterloo administration for providing me with the opportunity to pursue my Ph.D. studies. Particularly, I would like to express my thanks to Wendy Boles, Lisa Hendels, and Annette Dietrich, of ECE Graduate Office. I would like to acknowledge the support of Ontario Graduate Scholarship (OGS) while I was an international student.

I am always grateful to my wife, Neda Nouri, for her invaluable support and inspiration. Her love and understanding played a major role in helping me finish this thesis. I also, would like to thank my parents for their endless love and support.

### **Dedication**

This thesis is dedicated to my wife, Neda Nouri.

# **Contents**

| Li | st of T | ables                                   | i |

|----|---------|-----------------------------------------|---|

| Li | st of l | igures xvii                             | i |

| 1  | Intr    | duction                                 | 1 |

|    | 1.1     | Variations: Sources and Impact on Yield | 1 |

|    | 1.2     | Motivations                             | 4 |

|    | 1.3     | Contributions                           | 5 |

|    | 1.4     | Structure of this Thesis                | 5 |

| I  | Dev     | ice-Level                               | ) |

| 2  | Vari    | ability-Aware MOS Device Design         | 0 |

|    | 2.1     | Introduction                            | ) |

|    | 2.2     | Selected Device Structure               | 2 |

|    |         | 2.2.1 Geometrical Parameters            | 3 |

|    |         | 2.2.2 Doping Parameters                 | 5 |

|    | 2.3     | Problem Formulation                     | 8 |

|    |         | 2.3.1 General Approach                  | 8 |

|    |         | 2.3.2 Yield Estimation                  | 9 |

|    |         | 2.3.3 Final Optimization Problem        | 1 |

|    | 2.4     | Constraint Verification Scheme          | 2 |

|    |                  | 2.4.1 Surface Extraction                                                        | 23                                                       |

|----|------------------|---------------------------------------------------------------------------------|----------------------------------------------------------|

|    |                  | 2.4.2 Direct Evaluation                                                         | 24                                                       |

|    | 2.5              | Results and Discussion                                                          | 25                                                       |

|    | 2.6              | Conclusions                                                                     | 30                                                       |

|    |                  |                                                                                 |                                                          |

| II | Ci               | ircuit-Level                                                                    | 33                                                       |

| 3  | Ove              | rview of Advanced Sampling and Variance Reduction Methods                       | 34                                                       |

|    | 3.1              | Introduction to Monte Carlo method                                              | 34                                                       |

|    | 3.2              | Latin Hypercube Sampling                                                        | 36                                                       |

|    | 3.3              | Quasi Monte Carlo Sampling                                                      | 37                                                       |

|    | 3.4              | Control Variate Method                                                          | 38                                                       |

|    | 3.5              | Importance Sampling                                                             | 40                                                       |

|    | 3.6              | Stratified Sampling                                                             | 41                                                       |

| 4  | Diai             | ital Circuitas Advanced Monte Caula Daged Statistical Timing Analysis Mathad    |                                                          |

| 4  | olog             | ital Circuits: Advanced Monte Carlo-Based Statistical Timing Analysis Methodies | 43                                                       |

| 4  | _                |                                                                                 | <b>43</b>                                                |

| 4  | olog             | ries                                                                            |                                                          |

| 4  | <b>olog</b> 4.1  | ies Introduction                                                                | 43                                                       |

| 4  | olog 4.1 4.2     | Introduction                                                                    | 43<br>45                                                 |

| 4  | olog 4.1 4.2     | Introduction                                                                    | 43<br>45<br>48<br>48                                     |

| 4  | olog 4.1 4.2     | Introduction                                                                    | 43<br>45<br>48<br>48<br>53                               |

| 4  | olog 4.1 4.2     | Introduction                                                                    | 43<br>45<br>48<br>48<br>53<br>59                         |

| 4  | olog 4.1 4.2 4.3 | Introduction                                                                    | 43<br>45<br>48<br>48<br>53<br>59                         |

| 4  | olog 4.1 4.2 4.3 | Introduction                                                                    | 43<br>45<br>48<br>48<br>53<br>59<br>61                   |

| 4  | olog 4.1 4.2 4.3 | Introduction                                                                    | 43<br>45<br>48<br>48<br>53<br>59<br>61<br>61             |

| 4  | olog 4.1 4.2 4.3 | Introduction                                                                    | 43<br>45<br>48<br>48<br>53<br>59<br>61<br>61<br>62       |

| 4  | olog 4.1 4.2 4.3 | Introduction                                                                    | 43<br>45<br>48<br>48<br>53<br>59<br>61<br>61<br>62<br>66 |

| 5 | Ana | log Circ | cuits: Correlation Controlled Sampling for Efficient Variability Analysis | <b>7</b> 4 |

|---|-----|----------|---------------------------------------------------------------------------|------------|

|   | 5.1 | Introdu  | action                                                                    | 74         |

|   | 5.2 | Traditi  | onal Monte Carlo Analysis and the Required Number of Samples              | 76         |

|   |     | 5.2.1    | Estimation of the Mean                                                    | 76         |

|   |     | 5.2.2    | Estimation of the Standard Deviation                                      | 77         |

|   |     | 5.2.3    | Estimation of the Yield                                                   | 78         |

|   | 5.3 | The Pr   | roposed Method                                                            | 81         |

|   |     | 5.3.1    | Assessing the Performance Metrics' Response Surface                       | 81         |

|   |     | 5.3.2    | Permutation Controlled LHS                                                | 83         |

|   |     | 5.3.3    | Finding Yield from the Statistical Moments                                | 88         |

|   | 5.4 | Conclu   | asions                                                                    | 91         |

| 6 | SRA | M Cell   | s: Adaptive Sampling for Failure Probability Estimation                   | 92         |

|   | 6.1 | Introdu  | action                                                                    | 92         |

|   | 6.2 | Backg    | round                                                                     | 93         |

|   |     | 6.2.1    | Problem Formulation                                                       | 93         |

|   |     | 6.2.2    | Adaptive Sampling Method                                                  | 95         |

|   | 6.3 | SRAM     | I Failure Mechanisms                                                      | 98         |

|   | 6.4 | Adapti   | ve Multivariate Normal Sampling                                           | 100        |

|   |     | 6.4.1    | The Algorithm                                                             | 100        |

|   |     | 6.4.2    | Results                                                                   | 105        |

|   |     | 6.4.3    | Determining the Number of Iterations, the Stop Criteria                   | 105        |

|   | 6.5 | The A    | nalytical Framework for Optimum Drift and Covariance Matrix Extraction    | 107        |

|   |     | 6.5.1    | The Analysis                                                              | 107        |

|   |     | 6.5.2    | Results by Integrating the Analytical Framework with the Adaptive Engine  | 109        |

|   | 66  | Conclu   | isions                                                                    | 110        |

| II | I N        | Iicro-A   | Architectural-Level                                                          | 113   |

|----|------------|-----------|------------------------------------------------------------------------------|-------|

| 7  | Stat       | istical T | Thermal Profile under Process Variations: Analysis and Applications          | 114   |

|    | 7.1        | Introd    | uction                                                                       | . 114 |

|    | 7.2        | Prelim    | iinaries                                                                     | . 117 |

|    |            | 7.2.1     | Deterministic Thermal Profile Extraction                                     | . 117 |

|    |            | 7.2.2     | Physical Parameter Variation Model                                           | . 118 |

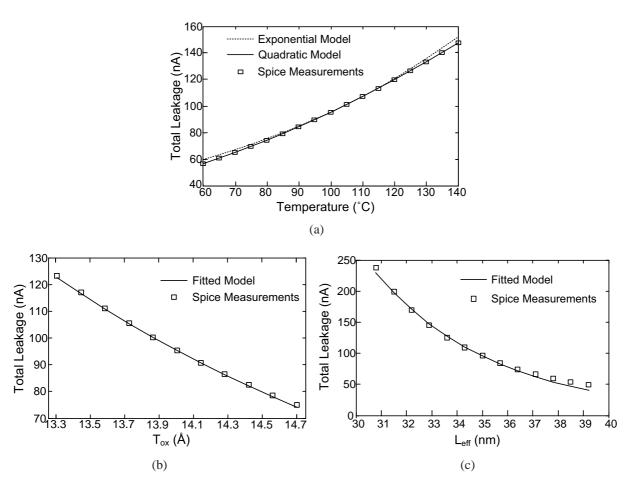

|    |            | 7.2.3     | Leakage Power Model                                                          | . 120 |

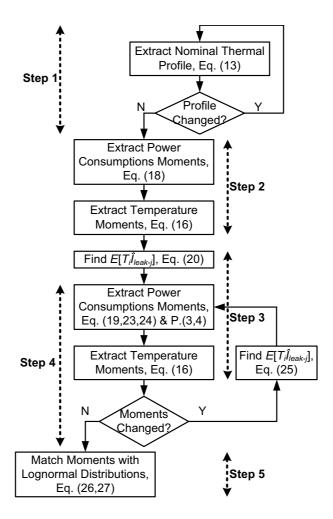

|    | 7.3        | Statist   | ical Thermal Analysis                                                        | . 122 |

|    | 7.4        | Applic    | cations                                                                      | . 128 |

|    |            | 7.4.1     | Early Stage Statistical Thermal and Process Aware Full-Chip Power Estimation |       |

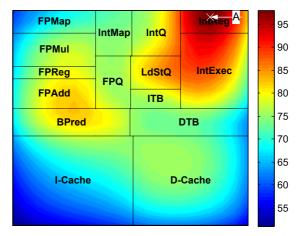

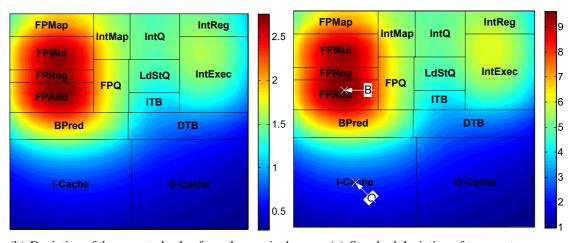

|    |            | 7.4.2     | Evaluation of Hotspots Relocations                                           | . 131 |

|    | 7.5        | Imple     | mentation, Results, and Discussions                                          | . 132 |

|    | 7.6        | Conclu    | usions                                                                       | . 140 |

| I  | / <b>Т</b> | hesis (   | Closure                                                                      | 141   |

| 8  | Con        | clusion   | s                                                                            | 142   |

|    | 8.1        | Future    | Works                                                                        | . 144 |

| Re | eferen     | ices      |                                                                              | 145   |

# **List of Tables**

| 2.1 | Desired bounds and operating supply voltage for designed devices in 90nm technology                                                                                                                                                                            | 26 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Obtained design parameters for each application                                                                                                                                                                                                                | 26 |

| 2.3 | Specifications of designed devices                                                                                                                                                                                                                             | 27 |

| 2.4 | The means and standard deviations of devices' characterisites                                                                                                                                                                                                  | 29 |

| 4.1 | Benchmark Circuits                                                                                                                                                                                                                                             | 46 |

| 4.2 | The relative importance of ANOVA terms for of the yield function                                                                                                                                                                                               | 52 |

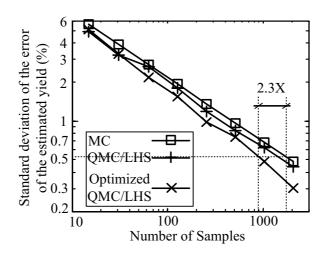

| 4.3 | Standard deviation reduction (percentage) of the estimated yield compared to the traditional-MC analysis. The proposed technique (QMC/LHS) is tested with and without applying the optimized direction values                                                  | 60 |

| 4.4 | Correlation between the defined control variable and the actual critical delay, with and without considering gate length spatial correlations                                                                                                                  | 65 |

| 4.5 | Standard deviation reduction (percentage) of the estimated yield compared to the traditional-MC analysis. The order statistics-based control variate technique is tested with and without considering spatially correlated random variables                    | 66 |

| 4.6 | Standard deviation reduction (percentage) and bias $(100E[\hat{y}] - 95)$ of the estimated yield compared to the traditional-MC analysis. The classical control variate technique is tested with and without considering spatially correlated random variables | 72 |

| 5.1 | Sample circuits and their <i>q</i> -measures                                                                                                                                                                                                                   | 84 |

# **List of Figures**

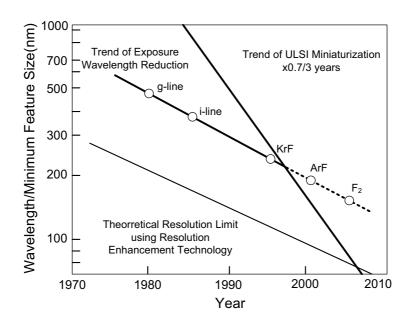

| 1.1 | Wavelength scaling versus feature size [1]                                                                                                                                                                                                                                                                           | 2  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

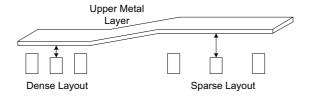

| 1.2 | The effects of layout density on Post-CMP ILD thickness [2]                                                                                                                                                                                                                                                          | 2  |

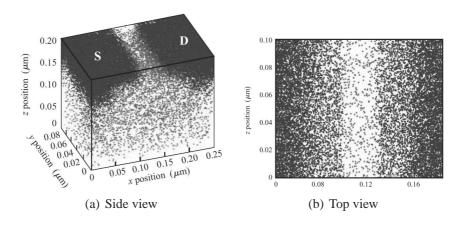

| 1.3 | Atom fluctuations in a MOSFET's channel[3]                                                                                                                                                                                                                                                                           | 2  |

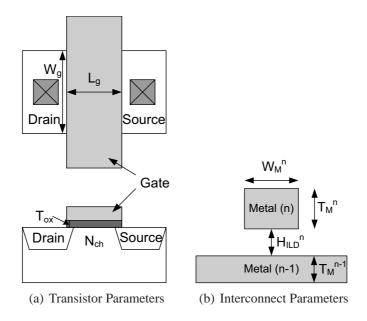

| 1.4 | Physical parameters experiencing variation                                                                                                                                                                                                                                                                           | 3  |

| 1.5 | Frequency and standby leakage current distribution (0.18 $\mu$ m technology) [4]                                                                                                                                                                                                                                     | 4  |

| 2.1 | Symmetrical Bulk–MOS structure. Parameters: gate length $(L_g)$ , oxide thickness $(T_{ox})$ , sidewall spacer width $(W_{sp})$ , gate/SDE overlap $(L_{ov})$ , SDE junction depth $(X_{jSDE})$ , contact junction depth $(X_{jCon})$ , Gaussian Halo, and Super Steep Retrograde Well                               | 12 |

| 2.2 | Total Leakage ( $TL$ ) estimation scheme                                                                                                                                                                                                                                                                             | 18 |

| 2.3 | Simplified problem in two dimensions                                                                                                                                                                                                                                                                                 | 19 |

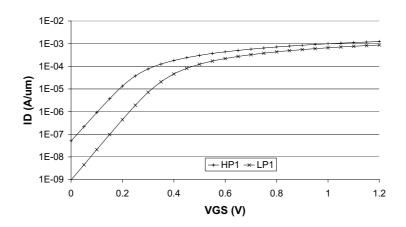

| 2.4 | I-V characteristics of the HP1 and LP1                                                                                                                                                                                                                                                                               | 28 |

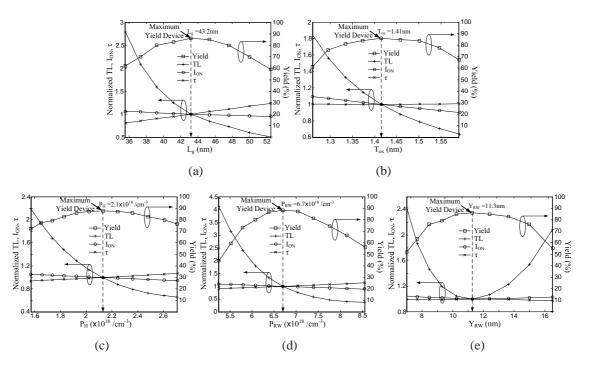

| 2.5 | Yield, and the average of total leakages, $I_{ON}$ , and $\tau$ , obtained by Monte-Carlo simulations for HP1 when the device parameters are shifted from the obtained optimum ones. Each figure is extracted from the cases when one device parameter is swept while others are kept equal to the parameters of HP1 | 30 |

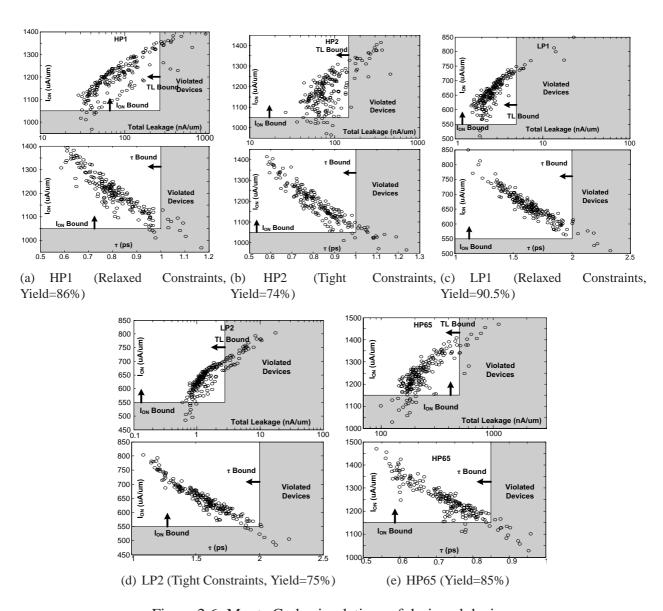

| 2.6 | Monte Carlo simulations of designed devices                                                                                                                                                                                                                                                                          | 31 |

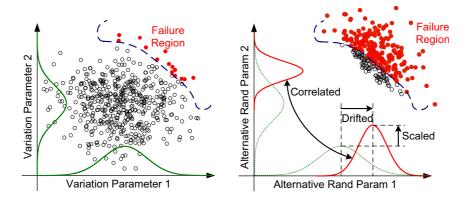

| 3.1 | An example of importance sampling: capturing more failure cases by using a multi-variate correlated-scaled-drifted Gaussian alternative distribution                                                                                                                                                                 | 40 |

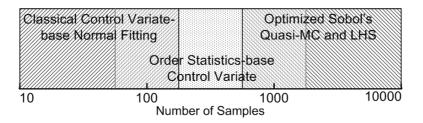

| 4.1 | The approximate range preferred for each proposed method                                                                                                                                                                                                                                                             | 45 |

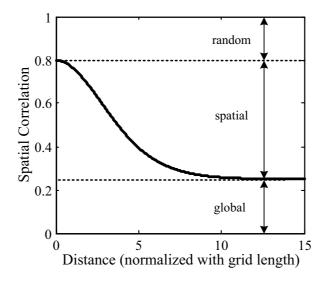

| 4.2 | Spatial Correlation                                                                                                                                                                                                                                                                                                  | 47 |

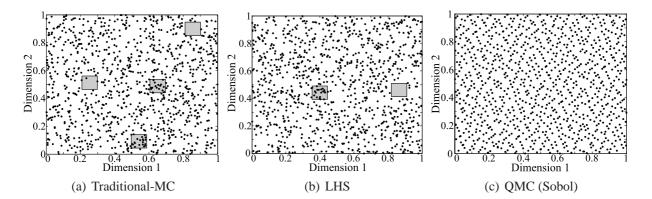

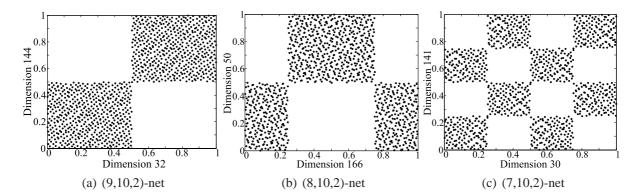

| 4.3 | 2-D projections of different sampling approaches. The gray squares represent areas with high or low concentration of samples                                                                                                                                                                                         | 50 |

| 4.4 | Some bad pairing (high-discrepancy) of Sobol's samples                                                                                                                                                                                                                                                                | 54   |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

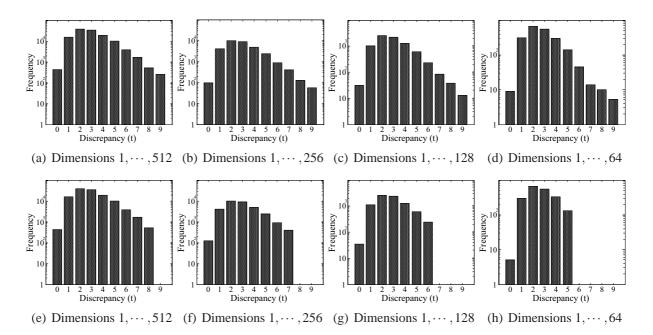

| 4.5 | Distribution of $t$ , the measure of discrepancy, for 1024 Sobol samples using (top) random initial direction values and (bottom) optimized initial direction values                                                                                                                                                  | 57   |

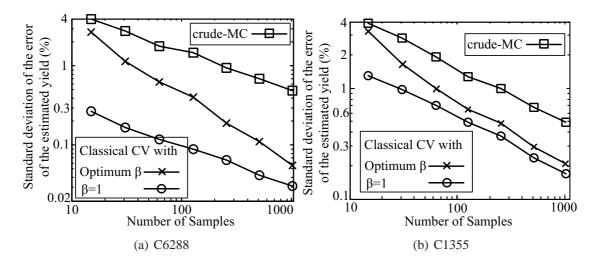

| 4.6 | Standard deviation of the error of the estimated yield for C6288: comparison of traditional-MC, QMC/LHS method with non-optimized IDV, and proposed QMC/LHS method with optimized IDV                                                                                                                                 | 61   |

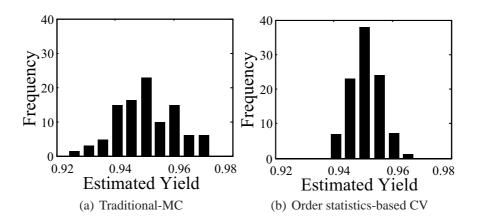

| 4.7 | Histogram of 100 estimated yields each obtained from 512 samples of (a) traditional-MC and (b) order statistics-based control variate, for C499 circuit. The proposed method's estimation is unbiased with E[y]=0.95 but shows 48% standard deviation reduction.                                                      | 67   |

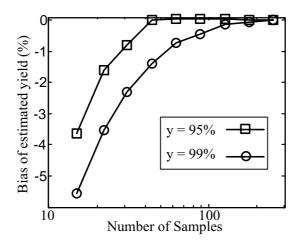

| 4.8 | Bias of the estimated yield for C6288: comparison of 99% and 95% yield                                                                                                                                                                                                                                                | 68   |

| 4.9 | Standard deviation of the error of the estimated yield using Gaussian approximation: comparison of the traditional-MC and the proposed classical control variate method using optimum- $\beta$ and constant- $\beta$ (= 1)                                                                                            | 71   |

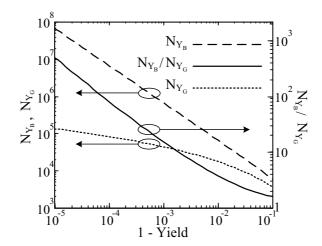

| 5.1 | Required number of samples to obtain 99% confidence inerval range with $\beta=0.1$ . Comparison between the Bernoulli and Gaussian assumptions                                                                                                                                                                        | 80   |

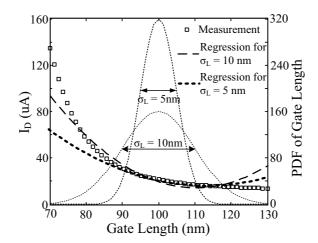

| 5.2 | Assessing the quality of a quadratic response model for the drain current with respect to gate length variation                                                                                                                                                                                                       | 82   |

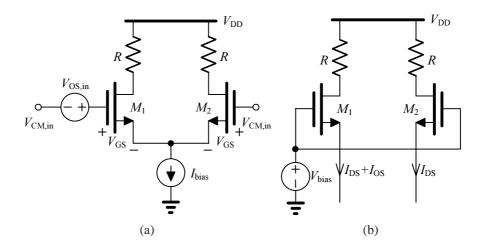

| 5.3 | Transistor pairing arrangements and the effects of mismatches on the DC operating points: (a) current biasing: the mismatches causes the $V_{GS}$ to vary and (b) voltage biasing: the mismatches causes the $I_{DS}$ to vary                                                                                         | 83   |

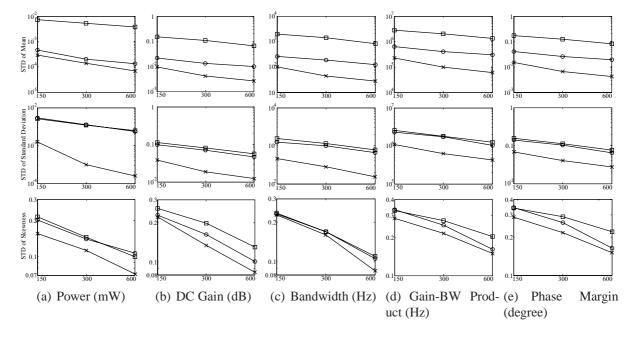

| 5.4 | Standard deviation (STD) of the estimations of the mean, standard deviation, and skewness with respect to the number of samples (x-axis) for the OTA's performance metrics. Square: Monte Carlo, Circle: traditional LHS, X-mark: the proposed permutation controlled-LHS                                             | 85   |

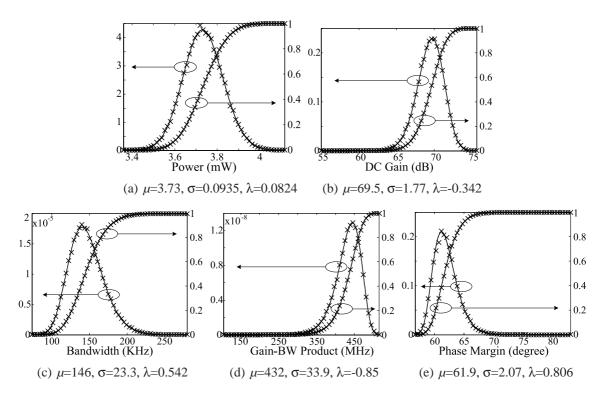

| 5.5 | Fitting shifted-lognormal distributions to histogram of 60000 samples of Monte Carlo simulation of the OTA. X-mark: MC histogram and cumulative distribution, Solid line: the fitted shifted lognormal PDF and CDF                                                                                                    | 87   |

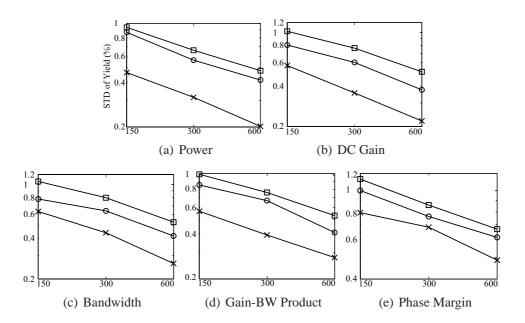

| 5.6 | Standard deviation of 100 runs of yield estimation using the lognormal fitting model with respect to number of samples. $P(power<3.92mW) = P(gain>65.7dB)$ = $P(BW>106.5KHz) = P(GBW>353.4MHz) = P(PM>58.65) = 0.975$ . Square: Monte Carlo, Circle: traditional LHS, X-mark: the proposed permutation controlled-LHS | . 89 |

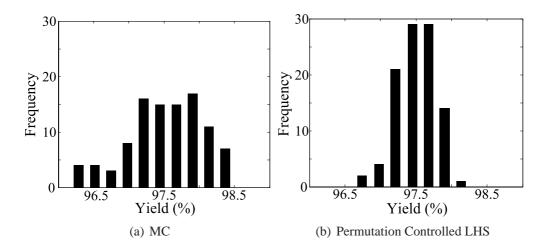

| 5.7 | Histograms of 100 estimated gain-bandwidth yields using the MC and proposed                                                                                                                                                                                                                                           | 0)   |

|     | methods for 600 samples                                                                                                                                                                                                                                                                                               | 90   |

| 5.1  | A 6T SRAM cell                                                                                                                                                                                    | 96  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.2  | Mismatch simulation of Read Noise Margin Low (RNML), $V_L$ zero write time $(T_W)$ , and $V_R$ zero read time $(T_R)$ . Process parameters are normalized over their standard deviation           | 96  |

| 5.3  | PDF of mismatch parameters for following failure conditions (RNML<2mV, $T_W>\!\!30pS,$ and $T_R>\!\!50pS).$                                                                                       | 97  |

| 5.4  | Positive and negative cross-correlation among the failure (RNML $<2mV$ ) mismatch parameters                                                                                                      | 100 |

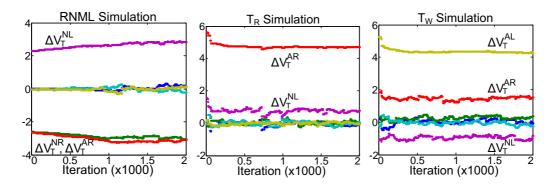

| 5.5  | Adaptive updates of the alternative distribution's drifts                                                                                                                                         | 105 |

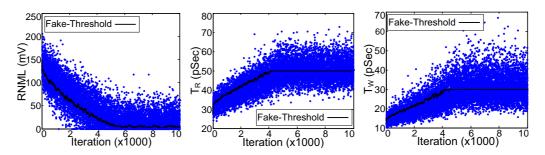

| 5.6  | Performance metrics and the fake-thresholds                                                                                                                                                       | 105 |

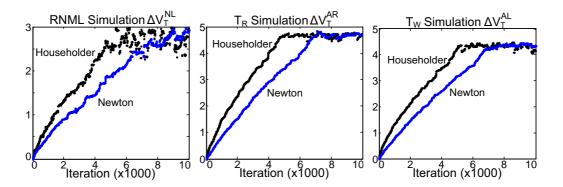

| 5.7  | Convergence comparison between the Newton's and the Householder's method                                                                                                                          | 106 |

| 5.8  | Drifts started from analytically calculated initial values                                                                                                                                        | 110 |

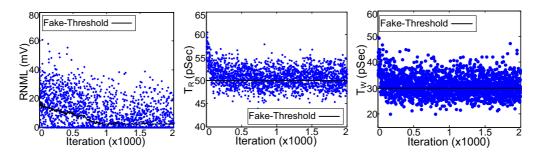

| 5.9  | Performance metrics for non-identity covariance matrix and starting from non-zero drift                                                                                                           | 110 |

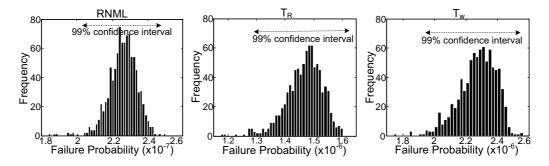

| 5.10 | The histogram and 99% confidence interval of the estimated yield for 5,000 simulations                                                                                                            | 110 |

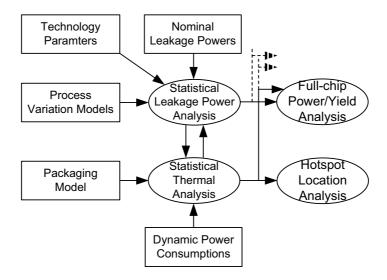

| 7.1  | Dependency among parameters and models in the developed framework                                                                                                                                 | 116 |

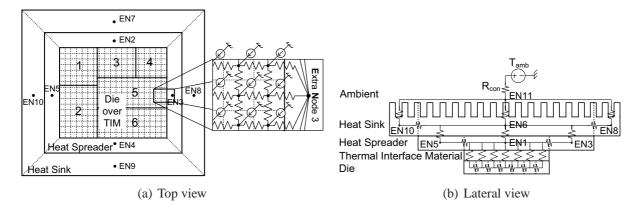

| 7.2  | The views of a 6-core sample die with its packaging structure (dimensions are not scaled) [5]                                                                                                     | 118 |

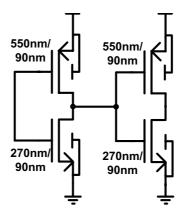

| 7.3  | A sample inverter used for demonstrating the leakage model                                                                                                                                        | 120 |

| 7.4  | Comparison between Spice measured total leakage current of the circuit depicted in Figure 7.3 and the fitting models when process parameters and temperature vary around the nominal value        | 122 |

| 7.5  | Flowchart of the proposed statistical thermal analyzer                                                                                                                                            |     |

|      | Statistical thermal profile of Alpha 21364 CPU core                                                                                                                                               |     |

| 7.7  | The obtained PDF from our method compared with the Monte-Carlo simulations                                                                                                                        |     |

| 7.8  | The standard deviation and expected value of node B's temperature in each iter-                                                                                                                   | 133 |

| 7.0  | ation                                                                                                                                                                                             | 136 |

| 7.9  | Corner based thermal extraction of node B. All $\Delta L_i$ and $\Delta T_{ox_i}$ variations are from $(-1.8\sigma_L, -1.8\sigma_{T_{ox}})$ to $(1.8\sigma_L, 1.8\sigma_{T_{ox}})$ simultaneously | 136 |

| 7.10 | The obtained full-chip total power consumption PDF from our method compared with the Monte-Carlo simulations                                                                                      | 137 |

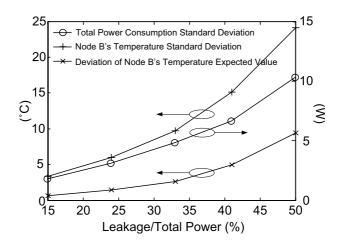

| 7.11 | The total power consumption std and node B's temperature moments with respect          |     |

|------|----------------------------------------------------------------------------------------|-----|

|      | to leakage/total power consumption ratio                                               | 138 |

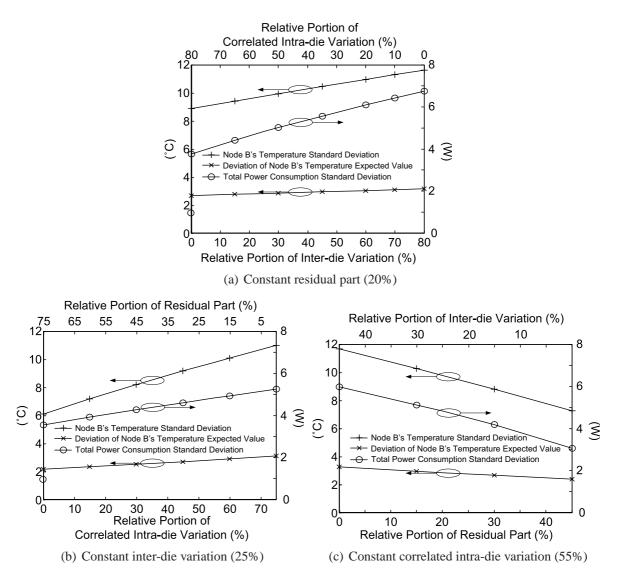

| 7.12 | The total power consumption standard deviation and node B's temperature mo-            |     |

|      | ments with respect to relative portions of inter-die, correlated intra-die, and resid- |     |

|      | ual part variations                                                                    | 139 |

### **Chapter 1**

### Introduction

### 1.1 Variations: Sources and Impact on Yield

The scaling of the CMOS technology has introduced enormous challenges that must be resolved by the designers. As the silicon industry moves toward nanometer designs, one of the most important design challenges cited is the increasing variability in the device characteristics [6] which threatens the silicon technology, and why CMOS scaling is facing critical yield concerns.

As can be seen in Figure 1.1, the exposure wavelength used for the lithography process to print layouts of different layers has not been scaled as fast as technology minimum feature size [1]. As a result, the printed features will not be exactly the same as the desired shapes.

These lithography-driven variations bring lateral layout variations for gate length  $(L_g)$ , gate width  $(W_g)$ , and metal interconnect width  $(W_M)$  which affects delay and subthreshold leakage of CMOS transistors and the characteristics of interconnects.

Vertical variations due to Chemical Mechanical Polishing (CMP) is another source of process variations (Figure 1.2) which originates from the difference in the removal rates of materials [7, 8]. The density of a lower layout affects the Inter Layer Dielectrics heights ( $H_{ILD}$ ), oxide thickness ( $T_{ox}$ ), and metal thickness ( $T_{ox}$ ) during CMP processes that consequently impacts the characteristics of interconnects and CMOS gates.

Another source of variation that directly influences the threshold voltage ( $V_{th}$ ) of MOS transistors comes from ion implantation, chemical vapor deposition (CVD), and thermal annealing processes. This type of variation, called Random Dopant Fluctuations (RDF), causes variability in the number and position of dopant atoms in the channel of MOS devices [9, 10]. Figure 1.3 shows a side and top view of an MOSFET's channel to depict the randomness of atoms in a channel. The shorter the channel, the less dopant atoms are in a channel making the transistor more sensitive to RDF in scaled technologies.

Figure 1.1: Wavelength scaling versus feature size [1].

Figure 1.2: The effects of layout density on Post-CMP ILD thickness [2].

Figure 1.3: Atom fluctuations in a MOSFET's channel[3].

In closing, the physical parameters, experiencing variability and impacting the circuit delay and total leakage current, are depicted in Figure 1.4.

Figure 1.4: Physical parameters experiencing variation

It should be noted that as nominal physical dimensions are rapidly shrunk, more variations are seen in the various physical parameters [11]. The feature size of layouts reduces faster than the lithography wavelength, hence, more aggressive subwavelength effects are seen. Also, due to the increase in the contribution of interconnect to total delay in ultra-DSM CMOS technologies, the CMP-based variations become more critical in each new technology [12]. Finally, the RDF-driven threshold voltage variation increases in each technology as the number of dopant atoms in the shortened channel is rather reduced [3].

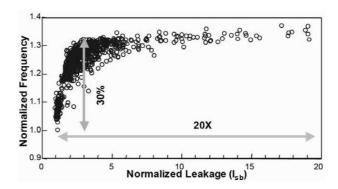

The variations on physical parameters cause performance and leakage alteration on a whole chip. Figure 1.5 shows a measured leakage variation as high as 20X for a 30% variation in chip frequency. Consequently, yield of a circuit (probability to meet the desired performance or power specification) is expected to suffer, unless careful statistical design followed by reliable statistical timing and power analysis are performed. In fact, if a circuit does not pass a maximum desired power budget or a minimum clock frequency, it may not be functional and hence reduce the production yield [13, 14]. However, even if a chip could be used in a lower operating frequency (mostly the general purpose processors using frequency binning [15]), the profitability will be reduced as the slower ICs are sold for cheeper.

Besides the mentioned time-invariant variations, there is another type of physical variation which impacts the threshold voltage of devices in time. Negative Bias Temperature Instability

Figure 1.5: Frequency and standby leakage current distribution (0.18µm technology) [4].

(NBTI) increases the absolute value of the MOS transistor's threshold voltage over a period of months or years, depending on the operating conditions of the device. This phenomenon which degrades the performance of circuits gradually over time is worsen with technology scaling [16] and has brought serious reliability concerns in nanoscale technologies as well.

Another type of yield lost is due to process defects causing a short or open in the circuit wires. This type of problems can lead to functional failures and may be addressed by redundancy in design.

In this thesis, only the performance-driven time-invariant variations are considered. Therefore, the usage of the term *yield* is referred to the ratio of the devices/circuits that pass certain performance metric constraints in presence of process variation.

### 1.2 Motivations

The design of Very Large Scale Integrated (VLSI) systems can be divided into many levels of abstraction. The design process, at each level, requires comprehensive and accurate models of the physical phenomena and the appropriate tools to simulate them in an efficient manner. The VLSI system specifications, such as power consumption, speed (performance), life-time, and thermal behavior must be considered during the various design phases, at each level of abstraction. This is essential to diagnose the sources of mal-functioning as early as possible and to reduce the chance of project failure. To achieve these goals, high performance and high capacity design automation and analysis tools are required.

On top of these traditional design challenges, it is the process variations, introduced during the IC manufacturing process which adds even more challenges to the design process at each level. For example, circuits undergoing variability now may exhibit very high leakage power consumption, pushing them over the power budget. The byproduct of this power consumption shift is the generation of heat leading to a higher operating temperature that, itself, raises reliability, packaging, and increased leakage power concerns. All are factors that can finally impact the yield. In addition, the performance of a digital circuit is affected by the transistor and interconnect variations, limiting the operating frequency of the circuit, and the yield of a system relying on a high-throughput digital processing. The process variations can also be very harmful for analog blocks and memory cores, directly impacting the yield and the success of a product.

Such an insight has been the motivation to target the process variation at three levels of device, circuit, and micro-architecture. In this thesis, the process variations are first modeled at each level. While the device level parameter variation models are designed to consider the details of channel doping profiles and device geometries, the circuit-level models lump them together as basic transistor-level electrical parameters such as threshold voltage variation. Consequently, the micro-architectural-level models unify the transistor-level parameters into a high-level model of circuit specifications variations, encapsulated in grids of equally varying process parameters. Finally, at each level, a number of computer-aided design and analysis solutions are proposed, each designed to address a gap in design for yield or analysis of variability of nanometer VLSI systems and circuits due to process variations.

### 1.3 Contributions

At the device-level, the variations of the drive-in capability and leakage currents are considered in order to optimize the geometry and doping profiles of an MOS device. The proposed device optimization methodology incorporates variability-awareness into the device design process by maximally satisfying certain bounds on total leakage, saturation current, and the intrinsic delay of the device undergoing process variations. This approach introduces a new strategy for the design of devices, where traditionally, nominal drive-in and leakage currents have been the objectives of the process design.

However, at circuit-level, the focus of this thesis is on accurate and efficient estimation of the yield for the different types of VLSI circuits: digital, analog, and SRAM cells. The statistical estimation of the circuit yield has been one of the major research areas in electronic design automation in recent years. Despite the considerable progress in this domain, the Monte-Carlo method is still the most reliable method as it can account for any circuit models and their secondary effects. However, the MC method suffers greatly from the lack of efficiency due to its slow convergence rate. In this thesis, a number of advanced sampling and variance reduction methods are developed to enhance the convergence rate of the traditional-MC method for circuit-level process variation-driven yield estimation. The sampling-based yield estimation solutions have been proposed for digital and analog circuits, and SRAM cells.

Finally, at the micro-architectural level, the effects of process variations are studied in a high-level co-thermal-leakage analysis framework. The process variations have traditionally

been studied as a source of full-chip total leakage power variation, leading to an estimation of system-level power consumption yield. However, the generated heat, due to higher leakage power consumption, increases the operating temperature of the chip, that itself in a positive feedback increases the sub-threshold leakage current. In an extreme case, these phenomena can lead to a thermal runaway. A statistical analysis methodology is proposed in this thesis to account for the thermal-leakage loop at micro-architectural-level in presence of process variation.

### 1.4 Structure of this Thesis

The rest of this thesis is organized as follows:

#### • Part I: Device-Level

- Chapter 2: The MOS device-level models of the various leakage current mechanisms, the saturation current, and the intrinsic delay are presented. Then, a device design methodology is proposed to maximize the yield of MOS devices for a desirable performance and leakage constraints.

#### • Part II: Circuit-Level

- Chapter 3: An overview of advanced sampling and variance reduction methods, used for efficient sampling-based circuit variability analysis, is presented. These methods are the core of the proposed techniques in the later chapters that perform circuit yield estimation with a significantly lower number of samples compared to that of the traditional-MC.

- Chapter 4: Three methods for efficient MC-based timing yield estimation of digital circuits are proposed. The methods are based on Quasi-MC sampling and control variates.

- Chapter 5: The process variation effects on analog circuit performance metrics are studied through the analysis of the response surface of the metrics. The required number of MC samples for sufficiently accurate yield estimation is calculated. Then, an enhanced LHS-based is proposed for the yield analysis of the analog blocks.

- Chapter 6: The failure mechanisms of SRAM cells are investigated. An adaptive importance sampling-based approach is developed for the efficient yield estimation of the SRAM cells with rare failure rate.

#### • Part III: Micro Architectural-Level

Chapter 7: A high-level model of leakage power uncertainty, due to process variations, is adopted to develop a co-thermal-leakage variation analysis engine. A hotspot formation analyzer and a full-chip leakage power yield analyzer are proposed as two applications of the engine.

### • Part IV: Thesis Closure

- **Chapter 8**: The conclusion and future works are presented in the last chapter.

### Part I

### **Device-Level**

As CMOS technology is scaling down toward the nano-scale regime, the drastically growing leakage currents and variations in device characteristics are becoming two important design challenges. Traditionally, the device design methodology is based on finding the device parameters which minimize the leakage current while provide enough saturation current for the performance needs. This methodology may change when variations are accounted for design. In this part of the thesis, the process variations are studied in device-level, and a novel device optimization methodology is presented that incorporates variability awareness into the device design flow such that the designed devices satisfy certain bounds on the total leakage, saturation current, and intrinsic delay under parameter variabilities.

### Chapter 2

### Variability-Aware MOS Device Design

### 2.1 Introduction

These needs have been satisfied by the increase in transistor density and performance, as suggested by "Moore's Law" and guided by CMOS scaling theory. However, the scaling of technology brings up enormous challenges that must be resolved by designers. As the silicon industry moves toward nanometer designs, the two most important design challenges cited are the growing leakage power dissipation [17] and the increasing variability in process dependent device characteristics [18]. Leakage power has been growing at an alarming rate, and constitutes a larger fraction of the total chip power in current and future technology generations. In addition, the manufacturing process of nanometer transistors and structures has introduced several new sources of variation that has made the control of process variation more difficult [19]. Process variations significantly impact chips' performance and power dissipation [18, 20]. The growing leakage power and variability in device characteristics are indeed the two most serious issues that threaten the life time of silicon technology [21].

The leakage power problem is further compounded by its strong dependence on the design parameters and hence on their variations [20]. As a result, circuits experiencing variability, now may exhibit very high leakage power consumption, pushing them over the power budget. In fact, variations in transistor parameters in the 180 nm CMOS technology node causes up to 20X variation in the chip's total leakage and 30% variation in its maximum operating frequency [4] and are worse when the technology scales [22].

Traditionally the device design methodology is based on maximizing the  $I_{ON}/I_{OFF}$  ratio, in which a device is designed such that its total leakage current is minimized while it provides a minimum saturation current satisfying the application's performance needs. Typically, the total leakage current consists of three major components, namely: subthreshold, gate direct tunneling,

and reversed biased junction band-to-band-tunneling [17]. However, the analytical models for mean and standard deviation of leakage current components suggest different sensitivity measures to various device parameters [23]. Hence, the variance of the total leakage current depends not only on device's parameter variations, but also on the relative magnitude of the leakage components of the device. Therefore, different devices with relatively equal nominal total leakage current may see considerably different variances on their total leakage current in the presence of variability. This reemphasizes the fact that exclusively minimizing the total leakage may yield a device with a large sensitivity to process parameters and hence less immunity against leakage current variations. Therefore, trading off among the magnitude of leakage components can produce more robust devices in terms of performance and leakage variability.

Motivated by the above challenges, the design of CMOS devices must be revisited to include variability. The objective of this work is to re-design the CMOS device to increase its yield by maximizing its immunity against process variations. To achieve this goal, a Bulk-MOS design methodology is proposed which not only deals with total leakage current reduction but also increases its tolerance to variability, while accounting for the minimum required drive-in current  $(I_{ON})$  and maximum intrinsic delay  $(\tau = C_g V/I_{ON})$  of the device.

With the aid of our proposed methodology, the designer would define a targeted technology and three bounds on  $I_{ON}$ , intrinsic delay, and total leakage current, and can now exploit the allowable design space for variability to maximize the device's yield. Physical gate length, oxide thickness, and channel doping profile (halo and super steep retrograde well) parameters are considered as the main design variables. These variables form a five-dimensional space where each point represents a device with parameters equal to the coordinates of the point. Then, based on the defined bounds, a problem feasible space is formed where every point (device) in this space satisfies the defined constraints of  $I_{ON}$  and the total leakage current. Finally, the yield maximizing step places a cube in the feasible space such that the device lies in the center of that cube has maximum immunity against process variations. It should be noted that to assure compliance of the designed device with the targeted technology, fabrication limitations (e.g. minimum gate length and oxide thickness) and variation parameters of the technology should also be given to the optimizer as technology specific constraints.

The variability has been included into technology optimization by the framework proposed in [24]. The circuit (e.g.  $V_{DD}$ , mean repeater sizing and width) and device level variables (e.g. gate length, oxide thickness, and peak halo doping) are optimized such that a design shows a maximum performance-driven yield subject to a maximum average power consumption. Therefore, the variability of the power consumption is simply modeled by the average sub-threshold leakage current based on  $V_{th}$  variation. This may lead to a design variable set which shows a satisfying power consumption expected value but high power consumption (leakage) variance. Moreover, the tunneling (gate oxide and BTBT) leakage variations are ignored. Also, the yield is only defined based on the performance which means a fabricated circuit is acceptable if it only pass a minimum performance metric regardless of its leakage current magnitude. Finally, using

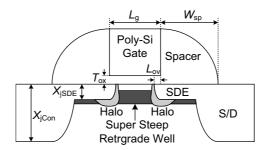

Figure 2.1: Symmetrical Bulk–MOS structure. Parameters: gate length  $(L_g)$ , oxide thickness  $(T_{ox})$ , sidewall spacer width  $(W_{sp})$ , gate/SDE overlap  $(L_{ov})$ , SDE junction depth  $(X_{jSDE})$ , contact junction depth  $(X_{jCon})$ , Gaussian Halo, and Super Steep Retrograde Well

simplified device models with numerous fitting curves makes the approach useful for fast general technology variable optimization (as listed before). However, there is still a need to make use of the trade-offs between various leakage components and its effects on a leakage-performance based yield and consider them in a detailed device parameter optimization to build variation immune devices for different technologies.

The rest of this chapter is organized as follows. In Section 2.2, the selected device structure and design parameters are presented, whereas the problem is formulated in Section 2.3. The way the defined constraints on currents are verified is discussed in Section 2.4, and the implementation and results with discussions are given in Section 2.5. Finally, conclusions are presented in Section 2.6.

### 2.2 Selected Device Structure

As mentioned earlier, the objective of this work is to optimize a device's geometry and doping profiles in order to obtain the highest immunity against variability in the performance and leakage current of the device.

To achieve this goal, a symmetrical Bulk-NMOS device structure as shown in Figure 2.1 is selected. The device with various channel doping implants (Source/Drain Extension (SDE), Gaussian Halo, and vertical Retrograde Well) has been developed to mitigate the short channel effects and improve the leakage characteristics [25]. The parameters of this structure are discussed in two categories: *geometrical* and *doping* parameters.

### 2.2.1 Geometrical Parameters

The geometrical parameters are physical gate length  $(L_g)$ , oxide thickness  $(T_{ox})$ , sidewall spacer width  $(W_{sp})$ , and transistor width (W).

### 2.2.1.1 Physical Gate Length

The threshold voltage of MOSFET devices decreases with the reduction in gate length. Using depletion approximation, the threshold voltage of a MOS device,  $V_{th}$ , can be defined as [26]:

$$V_{th} = V_{fb} + \phi_s + \frac{Q_B}{C_{ox}} \tag{2.1}$$

where  $V_{fb}$  is the flat-band voltage;  $\phi_s$  is the surface potential;  $C_{ox}$  is the capacitance across the oxide; and  $Q_B$  is the depletion charge in the bulk. In short channel devices, the source-drain distance is comparable to the depletion width in the vertical direction under the oxide. As a result, the source and drain depletion regions now penetrate more into the channel, resulting in part of the channel being already depleted. Therefore, less bulk charge  $(Q_B)$  is needed for the device to be inverted by the applied gate voltage. The change in the threshold voltage,  $V_{th}$ , as a result of channel length scaling can be approximated as [27]:

$$\Delta V_{th} = -\left[2\left(V_{bi} - \phi_{s}\right) + V_{DS}\right] \left(e^{-L/2l} + 2e^{-L/l}\right)$$

(2.2)

where  $V_{bi}$  is the potential of the channel/source edge,  $V_{DS}$  is the drain-source voltage, L is the effective channel length, and

$$l = \sqrt{\frac{\varepsilon_{si} T_{ox}}{\varepsilon_{ox}} \times \frac{W_{dep}}{\eta}}$$

(2.3)

where  $W_{dep}/\eta$  is the average depletion layer width along the channel, and  $T_{ox}$  is oxide thickness. Considering Eq. (2.2), in a long channel device (L >> l)  $\Delta V_{th}$  is almost zero, while in the short channel devices, the negative  $\Delta V_{th}$  causes a reduction in threshold voltage. This Short Channel Effect (SCE) is known as  $V_{th}$  roll-off [17].

In addition, subthreshold leakage, *I<sub>sub</sub>* of a MOSFET device can be modeled as [28]:.

$$I_{sub} = \mu_0 C_{ox} \frac{W}{L} v_T^2 e^{1.8} e^{(V_{GS} - V_{th})/nv_T} \left( 1 - e^{-v_{DS}/v_T} \right)$$

(2.4)

where  $\mu_0$  is carrier mobility,  $\frac{W}{L}$  is width over length ratio of the device,  $v_T$  is the thermal voltage, and n is the subthreshold swing coefficient. Considering the exponential dependency between subthreshold leakage and  $V_{th}$ , it can be inferred that the gate length as one of the contributors to the threshold voltage variation should be taken into account in a variation driven device design.

It has been shown that  $V_{th}$  rolling off can be reduced by applying halo(pocket) implants [29]. However, this improvement may lead to a  $V_{th}$  roll-up (Reversed SCE) followed by an abrupt roll-off which can be troublesome for devices beyond the 100 nm regime [30, 31]. By increasing the channel length in the halo implanted device, one can reduce the variation in threshold voltage  $(dV_{th}/dL_g \rightarrow \text{zero})$ . However, this leads to a penalty in performance because of the reduction in saturation current [22].

Besides to the discussed trade-off role of the gate length between providing enough saturation current and threshold voltage stability, the physical gate length is the main parameter in the hand of device designers to design various devices for different purposes from Low Power (LP) to High Performance (HP) applications [11].

#### 2.2.1.2 Oxide Thickness

The oxide thickness has a considerable effect on threshold voltage [26] since any variation in oxide thickness changes  $C_{ox} = \varepsilon_{ox}/T_{ox}$ . Hence, it will affect threshold voltage and subthreshold leakage current (as per Eq.2.1 and 2.4). Moreover, the SCE is affected by oxide thickness as given in Eg.2.3, therefore, thinner oxide is needed to overcome  $V_{th}$  roll-off in scaled technologies. However, the gate-tunneling leakage cannot be neglected when the oxide thickness is less than 3nm [17]. The gate leakage is due to the tunneling of an electron (or hole) from the bulk silicon through the gate-oxide potential barrier into the gate. Direct tunneling gate leakage density,  $J_{DT}$ , is modeled as [32]:

$$J_{DT} = A \left(\frac{V_{ox}}{T_{ox}}\right)^2 \exp\left\{-B\frac{T_{ox}}{V_{ox}}\left[1 - \left(1 - \frac{V_{ox}}{\phi_{ox}}\right)^{\frac{3}{2}}\right]\right\}$$

(2.5)

where  $V_{ox}$  is the drop across the thin oxide and  $\phi_{ox}$  is the barrier height for the tunneling particle (electron or hole). A and B are physical parameters depended on barrier height and are given in [32]. It can be seen from Eq. (2.5) that the tunneling current increases exponentially with a decrease in oxide thickness.

In addition, the saturation current and intrinsic delay are also sensitive to variation in  $T_{ox}$  due to variations in threshold voltage and gate oxide capacitance.

#### 2.2.1.3 Other Parameters

The transistor width is chosen by the circuit designers to size transistors in order to meet the required specifications for the system. Therefore, it is not considered as a device level design variable in our optimization problem. In addition, sidewall spacers are used to form SDE regions in the two sides of the channel and their width is determined based on the physical gate length

[33]. Hence, their values are determined for every transistor based on its gate length ( $W_{sp} = 1.1 \times L_g$ ) [11], so it is not included in the proposed device design parameter list.

### 2.2.2 Doping Parameters

Various channel profiles have been developed to overcome short channel effects and improve leakage characteristics [25]. Today's MOS transistors have three profiles in their channel: Source/Drain Extension (SDE), Halo, and Super Steep Retrograde Well (SSRW).

### 2.2.2.1 Source/Drain Extensions

SDE regions which are traditionally known as Lightly Doped Drain (LDD) are critical for deep sub-micron devices since they suppress the buildup of wide electric fields in the drain and source regions, hence reducing Drain Induced Barrier Lowering (DIBL) and  $V_{th}$  roll-off known as short channel effects [34]. The two important aspects associating with SDE region profiles are junction depth and lateral abruptness.

SDE junction depth  $(X_{jSDE})$  plays an important role in deep sub-micron devices. Deeper junctions result in more severe short channel effects due to further spreading potential contours and hence the depletion region into the channel. However, shallower junctions can impose higher series resistance to the transistor's source/drain terminal [35]. This trade-off has pushed designers to find the optimum SDE junction depth which not only reduces the series resistance and hence boosts the drive-in current but also improves short channel effects [35, 36]. Now, it is well understood that in the sub 100 nm regimes the extension junction depth should be scaled more aggressive than the past [11]. Motivated by the needs which are suggested in ITRS (International Technology Roadmap for Semiconductors), the ultra-shallow junctions is now achievable by the new innovations in fabrication techniques [34, 37, 38, 39]. In this work, the existing guidelines reported in ITRS are used for the depth of SDE regions [11].

Another important aspect of the SDE profile is its lateral abruptness. Detailed studies of SDE profiles showed that extension resistance which is an obstacle to achieve high-performance devices is strongly linked to lateral abruptness of the SDE. While more abrupt profile yields less resistivity to the extension, DIBL and threshold roll-off is impacted by too abrupt or too gradual junctions [40]. Based on the above facts, another guideline for optimum lateral abruptness has been reported in ITRS which is used in this work (lateral abruptness in nm/decade drop-off in doping concentration =  $0.11 \times L_g$ ) [11]. It should be noted that, the length of the gate drain overlap ( $L_{ov}$ ) is correlated with SDE lateral abruptness [35, 41] and is implicitly determined by the lateral abruptness of the SDE.

#### **2.2.2.2** S/D Contacts

Due to existence of extensions, S/D contacts are placed far from the channel. As a result, the short channel effects are independent of the contact junction depth  $(X_{jCon})$ , and only the saturation current increases with the increase in  $X_{jCon}$  [42]. Therefore, the  $X_{jCon} = 1.1 \times L_g$  is determined based on physical gate length as given in ITRS [11].

#### 2.2.2.3 Halo and Super Steep Retrograde Well

In short channel devices, additional non-uniform implants in the lateral and vertical directions are used to improve short channel effects [43, 44]. Halo, a non-uniform lateral doping, has been introduced to improve short channel effects and reduce subthreshold leakage current [45]. Tilt implanting of halo impurities places the pocket regions adjacent to SDE edge which made the profile more useful to suppress punch-through and short channel effects [46]. By proper usage of the profile, a 25 nm CMOS transistor design is feasible without continued scaling of the supply voltage. Therefore, a considerable improvement in device performance is achievable [46, 47].

In addition, to keep acceptable subthreshold leakage current in scaled devices, the channel doping should be increased as the gate length is decreased. However, increasing the channel doping leads to increase in threshold voltage, and consequently degrades device performance. A nonuniform vertical channel doping known as retrograde well can overcome the problem by providing a low surface concentration [17]. Due to suppressing channel impurity scattering, the lower concentration keeps surface channel mobility high while reduces subthreshold current. In fact, Super Steep Retrograde Well (SSRW) is preferred due to the increase in the linear drive current which causes performance improvement for logic gates [48, 49].

The symmetrical 2-D non-uniform channel doping,  $N_{CH}(x,y)$ , composed by halo and retrograde which is typically assumed to be Gaussian [50] is given as:

$$N_{CH}(x,y) = N_{Halo}(x,y) + N_{RW}(y) + N_{Sub}$$

where

$$N_{Halo}(x,y) = P_{H} \left[ \exp\left(\frac{-(x-\alpha_{1})^{2}}{S_{halox}^{2}}\right) + \exp\left(\frac{-(x-\alpha_{2})^{2}}{S_{halox}^{2}}\right) \right] \exp\left(\frac{-(y-\beta)^{2}}{S_{haloy}^{2}}\right)$$

and

$$N_{RW}(y) = P_{RW} \exp\left(\frac{-(y-Y_{RW})^{2}}{S_{RW}^{2}}\right)$$

(2.6)

where  $P_H$  and  $P_{RW}$  represent the peak halo and retrograde well concentrations, and  $N_{Sub}$  is the constant uniform doping of the bulk.  $S_{halo_y}$  and  $S_{halo_x}$  denote the characteristic decay lengths of the Gaussian halo profile in the vertical and lateral directions, and  $S_{RW}$  is the decay length on the vertical retrograde well. Finally, the positions of the halo and retrograde peaks are defined by  $\alpha_1$ ,  $\alpha_2$ ,  $\beta$ , and  $Y_{RW}$ .  $\alpha_1$  and  $\alpha_2$  are lateral positions of the pocket implant peaks while  $\beta$  and  $Y_{RW}$  are

the vertical position of the halo and retrograde peaks, respectively. In this work, the halo(pocket) peaks are placed beside the SDE edge where the extension and background concentrations are equated.

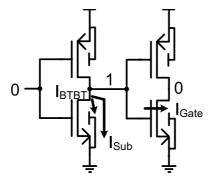

Band To Band Tunneling (BTBT) leakage is strongly linked to the channel and junction profiles [43], and hence, is very sensitive to any channel doping variation [23]. The BTBT current,  $I_{BTBT}$  can be estimated as [43]:

$$I_{BTBT} = \left(WX_{jSDE}\hat{A} / E_g^{1/2}\right) \xi V_{DD} \exp\left(-\hat{B}E_g^{3/2} / \xi\right)$$

where

$$\xi = \sqrt{\frac{2qN_{aside}N_{sdside}}{\varepsilon_{si}(N_{aside} + N_{sdside})}} \left[V_{DD} + \frac{KT}{q} \ln\left(\frac{N_{aside}N_{sdside}}{n_i^2}\right)\right]}$$

(2.7)

where  $N_{aside}$  and  $N_{sdside}$  are the p-side and n-side junction doping.  $E_g$  is the band-gap of the silicon, and  $\hat{A}$  and  $\hat{B}$  are physical coefficients given in [10]. Variation on channel peek dopings (halos and retrograde well) and vertical position of the retrograde well affect  $N_{aside}$  and hence BTBT leakage [43].

Furthermore, the variation of the peak values and the position of the retrograde well strongly affect threshold voltage and hence subthreshold leakage current, due to the impact on the threshold roll-off and Random Dopant Fluctuation (RDF)-driven threshold voltage variations [10]. In fact, in scaled technologies, RDF is becoming a dominant source of threshold voltage variations as the average number of dopant atoms in the channel is rather reduced. Finally, any change in the threshold voltage impacts the drive—in current and intrinsic delay as well. Moreover, there are no predefined exact values for halo and retrograde peaks and position in ITRS.

Consequently, the following device parameters will be used in forming the device optimization problem.

- $L_g$ : Physical gate length

- $T_{ox}$ : Oxide thickness

- $P_H$ : Halo peak doping concentration

- P<sub>RW</sub>: Retrograde well peak doping concentration

- $Y_{RW}$ : Vertical position of the retrograde well peak

As shown earlier, each leakage component is a function of the number of five process parameters under consideration.  $I_{gate}$ ,  $I_{BTBT}$ , and  $I_{sub}$  are exponentially depends on  $T_{ox}$ ,  $N_{aside}$ , and  $V_{th}$ , respectively [17], while  $V_{th}$  is a function of all selected process parameters [23]. Therefore, ON drive-in current as well as intrinsic delay is also a function of listed parameters. Hence, the

Figure 2.2: Total Leakage (TL) estimation scheme

following representations could be used to show the device characteristics and their dependency to each selected design parameter.

$$\tau = f(L_g, T_{ox}, P_H, P_{RW}, Y_{RW})

I_{ON} = f(L_g, T_{ox}, P_H, P_{RW}, Y_{RW})

I_{sub} = f(L_g, T_{ox}, P_H, P_{RW}, Y_{RW})

I_{BTBT} = f(P_H, P_{RW}, Y_{RW})

I_{gate} = f(L_g, T_{ox})$$

(2.8)

### 2.3 Problem Formulation

### 2.3.1 General Approach

Considering a five-dimensional space composed by  $L_g$ ,  $T_{ox}$ ,  $P_H$ ,  $P_{RW}$ , and  $Y_{RW}$ , a yield optimization problem can be represented as follows:

$$\underset{x=\left(L_{g},T_{ox},P_{H},P_{RW},Y_{RW}\right)}{\operatorname{argmax}} \quad Yield = P_{x}\left\{C\left(x\right) = 1\right\}$$

$$(2.9)$$

where C(x) denotes a boolean random variable function defined based on desired bounds on the ON current  $(I_{ON})$ , intrinsic delay  $(\tau)$ , and total leakage (TL) and is formulated by Eq. (2.10).

$$C(x) = (I_{ON}(x) \ge I_{ON-Min})AND(\tau(x) \le \tau_{Max})$$

$$AND(TL(x) \le TL_{Max})$$

(2.10)

where  $I_{ON-Min}$ ,  $\tau_{Max}$ , and  $TL_{Max}$  are desirable bounds for device parameters of interest. Therefore,  $P_x\{C(x)=1\}$  represents the probability that a device (x) satisfies the currents and

delay constraints in the presence of variations in x elements. This type of problem formulation enables developing different devices for high-performance or low-power applications by assigning various values to  $I_{ON-Min}$ ,  $\tau_{Max}$ , and  $TL_{Max}$ . The selection criteria for two performance metrics (ON current and intrinsic delay) is based on the fact that the performance improvement is primarily achieved by reduction of gate capacitance and hence reduction of intrinsic delay in every technology node for sub 100nm regime [11], while the  $I_{ON}$  is almost constant in scaled technologies and should only meet a minimum to prevent negative impact on the device drivability, critical for driving parasitic/interconnect capacitances.

To have a more realistic indication of the total leakage, TL, in digital circuits, all of the worst case leakage components are added together as given in ITRS [11].

$$TL = I_{Sub} (V_{GS} = 0, V_{DS} = V_{DD}) + I_{BTBT} (V_{GS} = 0, V_{DS} = V_{DD}) + I_{gate} (V_{GS} = V_{DD}, V_{DS} = 0)$$

(2.11)

Figure 2.2 shows a typical scheme where all three leakage components contribute in total leakage power.

#### 2.3.2 Yield Estimation

To solve the optimization problem stated in Eq. (2.9), one should estimate the probability of placing a device in the feasible space defined by the design constraints in the presence of variation in device parameters. This means that the probability which a device with parameters x satisfies the desired constraints on intrinsic delay, leakage, and drive-in current should be estimated. To

Figure 2.3: Simplified problem in two dimensions

estimate such probability,  $P_x(C=1)$ , a 5-D cube is formed in the problem space where all points within the cube satisfy the constraints on the  $I_{ON}$  and TL bounds.

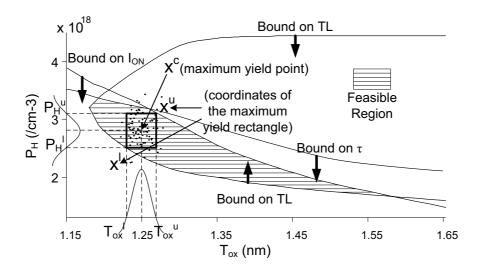

To clarify this point, a problem with two design variables ( $T_{ox}$ , $P_H$ ) is shown in Figure 2.3. A feasible region is defined based on the problem constraints. A rectangle is figured where its area is in the feasible region (all devices lying in the rectangle have the  $I_{ON}$ ,  $\tau$ , and TL within the desired bounds). The center of the rectangle is the max yield point. Now, considering a device placed in the center, the probability of the constraints satisfaction for such device in the presence of independent parameter variations can be estimated as follows:

$$P_{x(2-D)} = P_x \{ C(x) = 1 \} = P\{ T_{ox}^l \le T_{ox} \le T_{ox}^u \} \times P\{ P_H^l \le P_H \le P_H^u \}$$

(2.12)

where  $T_{ox}^{l}$ ,  $T_{ox}^{u}$ ,  $P_{H}^{l}$ , and  $P_{H}^{u}$  are coordinates of the rectangle.

By expanding this 2-D problem to the original 5-D problem given in Eq. (2.9), the 5-D yield probability can be represented as:

Assuming:

$$\begin{cases} x = (L_g, T_{ox}, P_H, P_{RW}, Y_{RW}) \\ x^l = (L_g^l, T_{ox}^l, P_H^l, P_{RW}^l, Y_{RW}^l) \\ x^u = (L_g^u, T_{ox}^u, P_H^u, P_{RW}^u, Y_{RW}^u) \end{cases}$$

(2.13)

$$Yield\left(x^{l}, x^{u}\right) = P_{x}\left\{C = 1\right\} = \prod_{i=1}^{5} P\left\{x_{i}^{l} \leq x_{i} \leq x_{i}^{u}\right\} = \prod_{i=1}^{5} \left(CDF_{X_{i}}\left(x_{i}^{u}\right) - CDF_{X_{i}}\left(x_{i}^{l}\right)\right)$$

where  $x_i$  is the  $i^{th}$  design parameter of device x.  $x^u$  and  $x^l$  represent the coordinates of the inscribed 5-D cube (instead of rectangle of 2-D problem). Thus,  $CDF_{X_i}$  is the cumulative distribution function of the parameter  $x_i$ . In this work, the variability of each design parameter is considered to be independent and the distribution is assumed to be Gaussian [20]. But, Gaussian distribution does not have a closed form cumulative distribution function (CDF) which is needed for yield evaluation, so the Kumaraswamy's distribution model is utilized [51, 52]. This double bounded probability density function (DB-PDF), is appropriate for physically bounded variables and provide a simple closed form expression for any probability distribution function [52]. The probability distribution function (PDF) f(z) of this model is in the form of:

$$f(z) = abz^{a-1}(1-z^a)^{b-1}$$

$$z = \frac{x-x^{lb}}{x^{ub}-x^{lb}} , \quad x^{lb} \le x \le x^{ub}$$

(2.14)

where  $x^{ub}$  and  $x^{lb}$  represent upper and lower bounds of double-bounded random variable x. Depending on the values chosen for parameters a and b, DB-PDF can take various shapes. In this work, a truncated Gaussian shape with range  $x^{ub} - x^{lb} = 6\sigma_x$  has been used by setting a and b to 3.6 and 8. Therefore  $x^{ub}$  and  $x^{lb}$  are set to  $x^c + 3\sigma_x$  and  $x^c - 3\sigma_x$ , respectively. However, other forms of distributions such as uniform, triangular, and log-normal can also be used. The

closed-form CDF of this model F(z) which is called DB-CDF is easily available from its integral [52]:

$$F(z) = 1 - (1 - z^a)^b (2.15)$$

Due to the symmetrical nature of design variables, the final optimized device,  $x^o$ , is assumed to be in the center of the inscribed 5-D cube. Therefore, its coordinates can be easily calculated as:

$$x^o = x^c = \frac{x^l + x^u}{2} \tag{2.16}$$

By using the closed form of the obtained DB-CDF and Eq. (2.16), the yield function of Eq. (2.13) can be rewritten as follows:

$$Yield (x^{l}, x^{u}) = \prod_{i=1}^{5} \left( F\left(\frac{x_{i}^{u} - x_{i}^{lb}}{x_{i}^{ub} - x_{i}^{lb}}\right) - F\left(\frac{x_{i}^{l} - x_{i}^{lb}}{x_{i}^{ub} - x_{i}^{lb}}\right) \right)$$

$$= \prod_{i=1}^{5} \left( F\left(\frac{x_{i}^{u} - (x_{i}^{c} - 3\sigma_{x_{i}})}{6\sigma_{x_{i}}}\right) - F\left(\frac{x_{i}^{l} - (x_{i}^{c} - 3\sigma_{x_{i}})}{6\sigma_{x_{i}}}\right) \right) = \prod_{i=1}^{5} \left( F\left(\frac{x_{i}^{u} - x_{i}^{l} + 6\sigma_{x_{i}}}{12\sigma_{x_{i}}}\right) - F\left(\frac{x_{i}^{l} - x_{i}^{u} + 6\sigma_{x_{i}}}{12\sigma_{x_{i}}}\right) \right)$$

(2.17)

The gate length and oxide thickness variations are constant for a given technology driven by the lithographic precision. Therefore, their values are set as technology specific parameters. However, the variations of other parameters are defined as percentage of the center point in every yield estimation iteration.

### 2.3.3 Final Optimization Problem

Till now, the probability of finding a device in a 5-D cube is estimated. However, to solve the optimization problem of Eq. (2.9), a 5-D cube should be inscribed in a feasible region which is defined based on marginal currents values. This 5-D cube is defined as follows:

$$Cube(x^{l}, x^{u}) = \left\{ x \in \Re^{5} | x^{l} \le x \le x^{u} \right\}$$

(2.18)

The cube is inscribed in the feasible region of  $F_c$  where every point  $x \in F_c$  satisfies the  $I_{ON}$  and TL constraints.

$$F_c = \left\{ x \in \Re^5 \, | C(x) = 1 \right\} \tag{2.19}$$

The yield maximization objective is to find the 5-D cube inscribed in the  $F_c$  such that the portion of points lies in the cube be maximized. Therefore, by using Eq. (2.17), (2.18), and

(2.19), the optimization problem of Eq. (2.9) can be represented as follows:

Given:

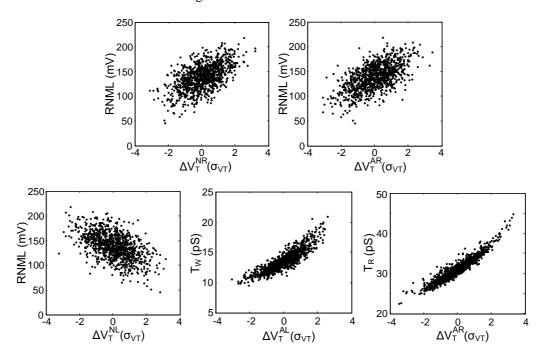

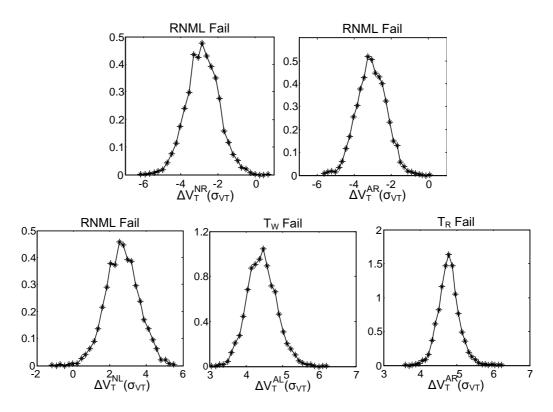

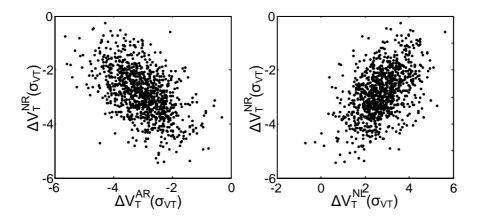

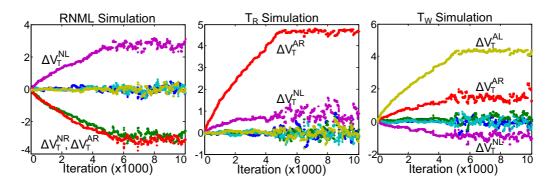

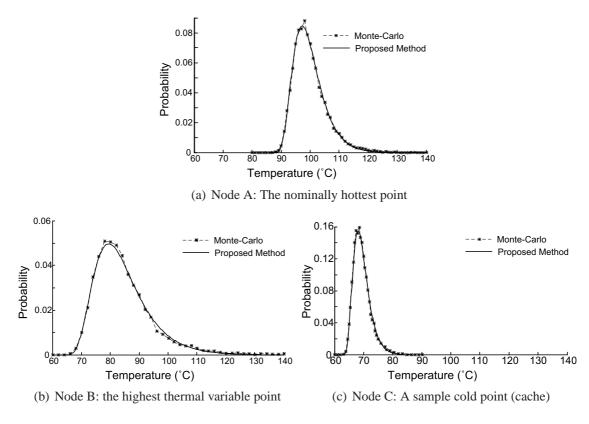

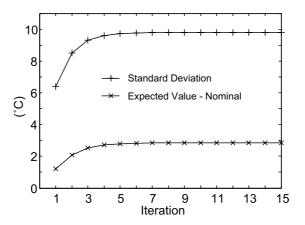

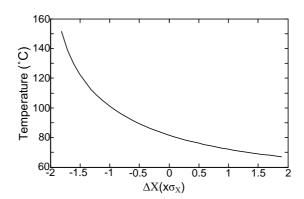

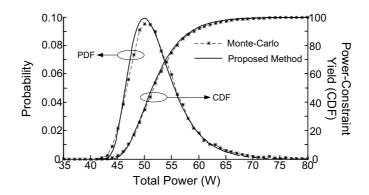

$$\begin{cases} \text{Constraints}: I_{ON-Min}, \tau_{Max}, \text{and } TL_{Max} \\ \text{Technology} - \text{Specific Variances}: \\ \sigma_x = \left[\sigma_{L_g}, \sigma_{T_{ox}}, \sigma_{P_H}, \sigma_{P_{RW}}, \sigma_{Y_{RW}}\right] \\ \text{Technology} - \text{Specific Limits}: x_i^{min}, x_i^{max} \end{cases}$$