# Photon Quantum Noise Limited Pixel and Array architectures in a-Si Technology for Large Area Digital Imaging Applications

by

Mohammad Yeke Yazdandoost

A thesis

presented to the University of Waterloo

in fulfilment of the

thesis requirement for the degree of

Doctor of Philosophy

in

**Electrical and Computer Engineering**

Waterloo, Ontario, Canada, 2011

© Mohammad Yeke Yazdanoost 2011

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

### **Abstract**

A Voltage Controlled Oscillator (VCO) based pixel and array architecture is reported using amorphous silicon (a-Si) technology for large area digital imaging applications. The objectives of this research are to (a) demonstrate photon quantum noise limited pixel operation of less than 30 input referred noise electrons, (b) theoretically explore the use of the proposed VCO pixel architecture for photon quantum noise limited large area imaging applications, more specifically protein crystallography using a-Si, (c) to implement and demonstrate experimentally a quantum noise limited (VCO) pixel, a small prototype of quantum noise limited (VCO) pixelated array and a quantum noise limited (VCO) pixel integrated with direct detection selenium for energies compatible with a protein crystallography application.

Electronic noise (phase noise) and metastability performance of VCO pixels in low cost, widely available a-Si technology will be theoretically calculated and measured for the first time in this research. The application of a VCO pixel architecture in thin film technologies to large area imaging modalities will be examined and a small prototype a-Si array integrated with an overlying selenium X-ray converter will be demonstrated for the first time.

A-Si and poly-Si transistor technologies are traditionally considered inferior in performance to crystalline silicon, the dominant semiconductor technology today. This work aims to extend the reach of low cost, thin film transistor a-Si technology to high performance

analog applications (i.e. very low input referred noise) previously considered only the domain of crystalline silicon type semiconductor. The proposed VCO pixel architecture can enable large area arrays with quantum noise limited pixels using low cost thin film transistor technologies.

Index terms – Voltage Controlled Oscillator, Ring Oscillator, Amorphous silicon, thin film transistor, active pixel sensor, medical imaging, quantum noise, large area electronics.

## Acknowledgements

I consider myself more than fortunate to have Prof. Karim S. Karim as my supervisor. I would like to thank him for his non-stop support all over my PhD program. His depth of knowledge along side with his privileged characteristic always helped me not only to conduct my research with highest performance, but also to earn a number of academic accomplishments. In addition, I have to add that I am deeply indebted to my parents, Dr. Farhad Yeke Yazdandoost and Rahimeh pournourbakhsh and to my sisters, Zahra and Fatemeh for their constant support and prayers.

I am grateful to Dr. Kai Wang and Kyung Wook Shin for their help in fabrication and support to conduct this research. I am also grateful to Dr. Nader Safavian for his support and useful talks. I would like to thank all of the members of the Silicon Thin-Film Applied Reseach (STAR) group for their useful comments and help. I have to thank Nicholas Allec specifically for his generous help for the testing of the amorphous selenium samples.

I would like to thank Government of Canada for giving me this opportunity and supporting me during my PhD studies. Also, I have to thank all of the friendly ECE staff for their generous help. I would like to thank Professor Jim Barby, Professor Ajoy Opal and Professor John Yeow for being my committee members and giving me useful guidance throughout my PhD studies. I have to thank Professor David Nairn, Professor Selvakumar,

Professor John Hamel (RIP), Dr. Hassan Hassan and Professor Hany Aziz for teaching me the highest level of knowledge during my PhD studies.

I have to thank all of my friends at Waterloo (best friends money can't buy) for supporting me and for all the fun we had together.

Lastly and most importantly I have to thank my God for all of his generous giving to me. Thank you Lord!

## To my Parents and my sisters

## **Table of Contents**

#### **List of Tables**

#### **List of Figures**

#### **List of Abbreviations**

| 1 Introduction                                                | 1                          |

|---------------------------------------------------------------|----------------------------|

| 1.1 Novelty and Application                                   | 3                          |

| 1.1.1 Protein Crystallography                                 | 4                          |

| 1.1.2 Requirements for Protein Crystallography                | 5                          |

| 1.1.2.1 Detector Area                                         | 6                          |

| 1.1.2.2 Dynamic Range                                         | 6                          |

| 1.1.2.3 Sensitivity                                           | 6                          |

| 1.1.2.4 Readout Time                                          | 7                          |

| 1.1.2.5 Spatial Resolution                                    | 7                          |

| 1.2 Thesis Organization                                       | 8                          |

| 2 Active Matrix Pixels                                        | 9                          |

| 2.1 PPS                                                       | 9                          |

| 2.2 APS                                                       | 11                         |

| 2.2.1 3-TFT APS structure                                     | 11                         |

| 2.2.2 2_TFT APS structure                                     | 14                         |

| 2.2.3 Hybrid APS structure                                    | 15                         |

| 2.2.4 Current programmed APS structure                        | 16                         |

| 3 Voltage Controlled Oscillators and the Suitable Structure f | or Digital Medical Imaging |

| Applications                                                  | 18                         |

| 3.1 LC Tank Oscillators                                       | 19                         |

| 3.2 Crystal Oscillator                                        | 20                         |

|     | 3.3 Wein-Bridge Oscillator                       | 21 |

|-----|--------------------------------------------------|----|

|     | 3.4 Phase-Shift Oscillator                       | 22 |

|     | 3.5 Relaxation Oscillators                       | 23 |

|     | 3.6 RVCO Pixel Architecture and Operation        | 24 |

| 4 R | RVCO Structure and Operation                     | 28 |

|     | 4.1 RVCO Pixel Structure and Operation           | 28 |

|     | 4.1.1 RVCO single pixel design                   | 29 |

|     | 4.2 RVCO Array Structure and Operation           | 31 |

|     | 4.3 Ultra Low Noise RVCO Structure and Operation | 36 |

| 5 F | Fabrication Process                              | 40 |

|     | 5.1 Mask 1                                       | 41 |

|     | 5.2 Mask 2                                       | 43 |

|     | 5.3 Mask 3                                       | 45 |

|     | 5.4 Mask 4                                       | 47 |

|     | 5.5 Mask 5                                       | 49 |

|     | 5.6 Mask 6                                       | 51 |

|     | 5.7 In-House Fabricated Sample                   | 53 |

|     | 5.8 Single TFT Results                           | 54 |

|     | 5.9 Fabrication Conditions                       | 56 |

|     | 5.10 a-Se Layer Deposition                       | 57 |

| 6 P | Phase noise, Jitter and Metastability in RVCO    | 58 |

|     | 6.1 Phase Noise in RVCO                          | 58 |

|     | 6.2 Jitter in RVCO                               | 63 |

|     | 6.3 Metastability in RVCO                        | 63 |

| 7 N | Measurement Results                              | 68 |

| 7.1 Single RVCO Pixel Results                                | 68  |

|--------------------------------------------------------------|-----|

| 7.2 RVCO Array Results                                       | 69  |

| 7.3 Single RVCO Pixel Interfaced with a-Se Results           | 75  |

| 8 Detective Quantum Efficiency of RVCO                       | 83  |

| 8.1 DQE (0)                                                  | 84  |

| 8.1.1 Cascaded Linear System Model                           | 85  |

| 8.1.2 X-ray Attenuation                                      | 86  |

| 8.1.3 Conversion Gain                                        | 87  |

| 8.1.4 Charge Collection                                      | 88  |

| 8.1.5 Electronic Noise                                       | 89  |

| 8.2 DQE(0) Simulation Result                                 | 89  |

| 9 Conclusion and Contributions                               | 92  |

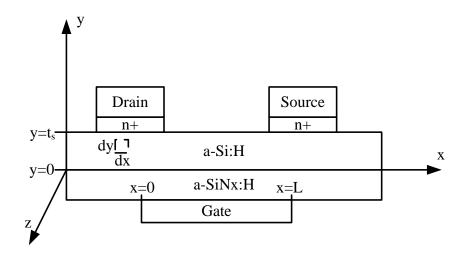

| Appendix A-Amorphous Silicon TFT                             | 96  |

| A.1 Application of a-Si TFT                                  | 97  |

| A.2 Basic Structure of the a-Si TFT                          | 97  |

| A.3 Operation of a-Si TFT                                    | 99  |

| A.3.1 Amorphous Silicon Density Of States (DOS               | 99  |

| A.3.2 Mobility Gap Models                                    | 101 |

| A.3.3 A Summary of a-Si TFT Operation                        | 103 |

| A.4 Introduction to a-Si TFT Static Forward Current Analysis | 104 |

| A.5 TFT Operation                                            | 105 |

| A.6 I <sub>DS</sub> Calculation                              | 108 |

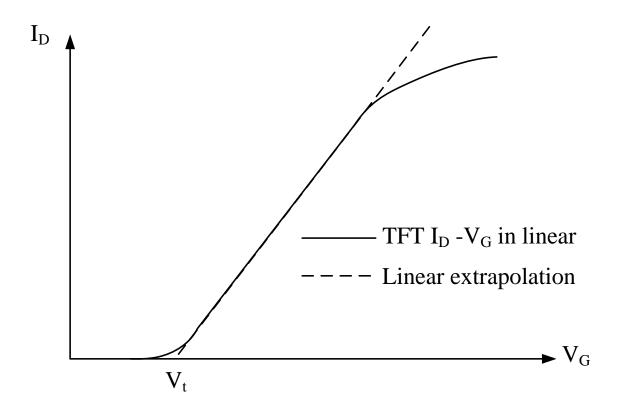

| A.7 TFT Parameter Extraction                                 | 113 |

| Appendix B-Mask Layouts                                      | 116 |

| References                                                   | 120 |

## **List of Tables**

| Table I. Fabrication conditions for in-house fabricated TFT process at the University of Wate |          |

|-----------------------------------------------------------------------------------------------|----------|

|                                                                                               | 56       |

| Table II. Parameters of phase noise power spectral density and their description and qua      | ntity59  |

| Table III. Model parameters for $V_t$ shift calculation.                                      | 66       |

| Table IV. Sizing of the TFTs in the RVCO array                                                | 70       |

| Table V. Parameters used to analyze the DQE for an RVCO pixel using a-Se as the               | detector |

| layer                                                                                         | 91       |

| Table VI. Design considerations for a protein crystallography X-ray detector [36]             | 93       |

| Table VII. Comparing the RVCO structure in different technologies                             | 94       |

## **List of Figures**

| Figure 1. Ring Voltage Controlled Oscillator Pixel Schematic                                       |

|----------------------------------------------------------------------------------------------------|

| Figure 2. Setup for a typical protein crystallography experiment [36]5                             |

| Figure 3. Image of a diffraction pattern containing a Bragg peak [36]5                             |

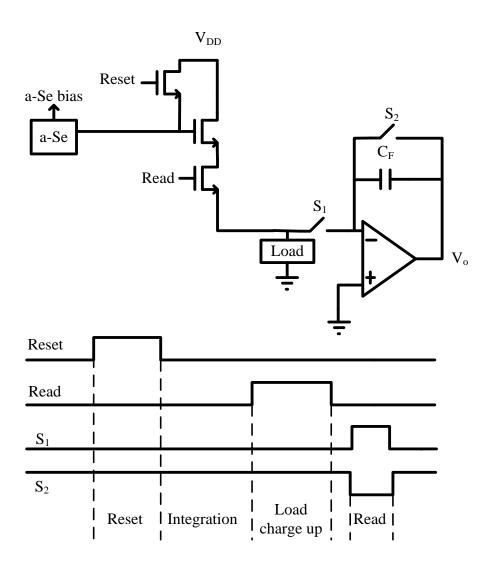

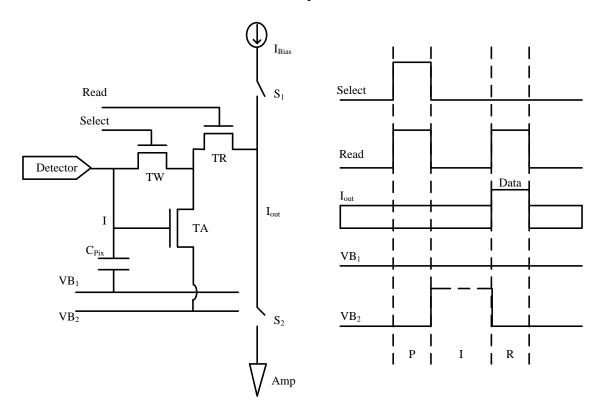

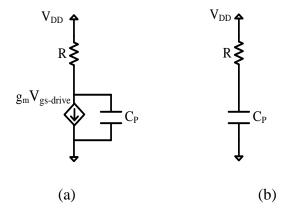

| Figure 4. PPS architecture (a) and operation cycle (b)                                             |

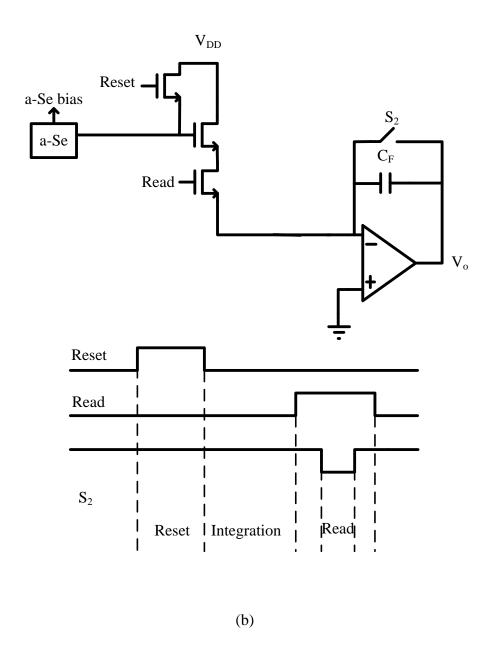

| Figure 5. V-APS architecture and timing diagram (a), C-APS architecture and timing diagram         |

| $(S_1 \text{ and } S_2 \text{ are active high}).$ 13                                               |

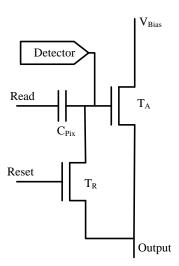

| Figure 6. 2-TFT APS structure [28]                                                                 |

| Figure 7. Hybrid APS structure [43]15                                                              |

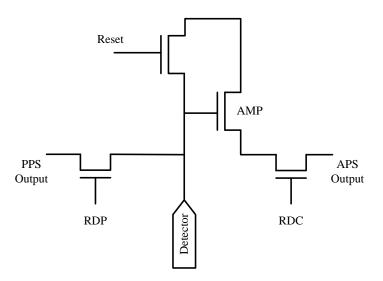

| Figure 8. Current-programmed APS structure [44].                                                   |

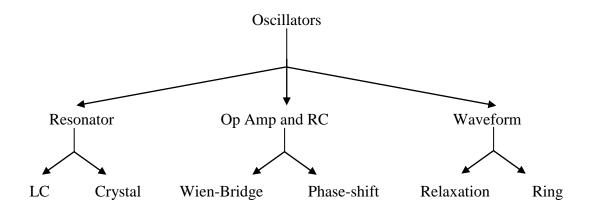

| Figure 9. Different types of VCOs                                                                  |

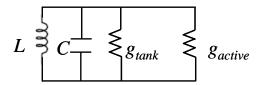

| Figure 10. LC oscillator structure.                                                                |

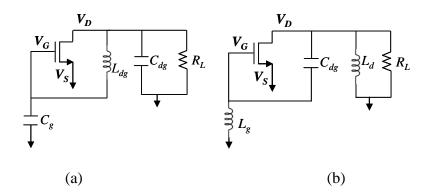

| Figure 11. Colpits oscillator (a), Hartley oscillator structures (b)                               |

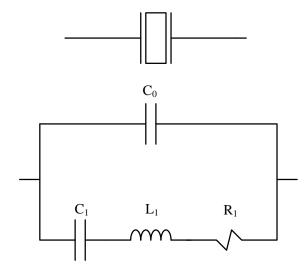

| Figure 12. Electronic symbol and equivalent circuit for a quartz crystal in an oscillator21        |

| Figure 13. Wein-Bridge oscillator architecture.                                                    |

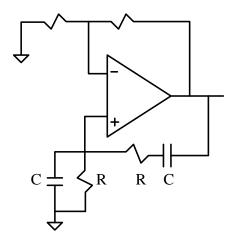

| Figure 14. Phase-Shift oscillator architecture.                                                    |

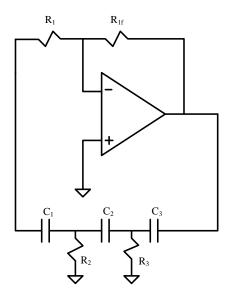

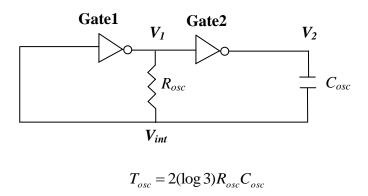

| Figure 15. Structure and frequency of oscillation for a relaxation oscillator24                    |

| Figure 16. Positive cycle in each inverter stage (a), Negative cycle in each inverter stage (b)25  |

| Figure 17. In-house fabricated RVCO pixel with bigger size TFTs(a), with smaller size TFTs (b).    |

| Figure 18. RVCO pixel architecture and layout (a), Timing diagram of the RVCO pixel29              |

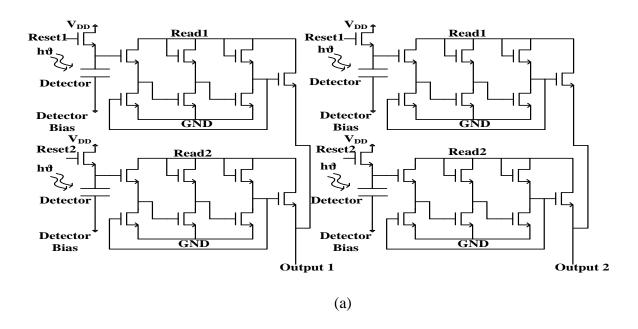

| Figure 19. Schematic of a 2 by 2 array (a), operation of the array (b) ( $V_{dd}$ =25 V). Read and |

| Reset signals are controlled row by row and the readout is done column by column (Vin is the       |

| middle voltage of the linear range of the frequency-voltage plot plus the threshold voltage of the |

| reset TFT)33                                                                                       |

| Figure 20. The different readout circuits used for RVCO pixel and array readout34                  |

| Figure 21. Layout of the 24 by 21 RVCO array (a) and 3 by 3 array (b)                                                                                                            | 5              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Figure 22. Ultra low noise RVCO structure and timing diagram                                                                                                                     | 8              |

| Figure 23. Chromium deposition (a), n+ nc-Si:H layer deposition (b), using mask 1 and etchin                                                                                     | ıg             |

| Chromium and n+ nc-Si:H layer to form drain and source contacts (c)                                                                                                              | -2             |

| Figure 24. Mask 1 used for this fabrication process                                                                                                                              | 3              |

| Figure 25. a-Si, a-Si $N_x$ and Molybdenum deposition (a), Using mask 2 and etching n+ nc-Si:H a Si, a-Si $N_x$ and Molybdenum (b)                                               |                |

| Figure 26. Mask 2 used for this fabrication process                                                                                                                              | 15             |

| Figure 27. a-SiN <sub>x</sub> deposition (a), opening via for interconnecting metal using mask 3 (b)4                                                                            | 6              |

| Figure 28. Mask 3 used for this fabrication process                                                                                                                              | ₽7             |

| Figure 29. Al layer deposition for interconnecting metal (a), using mask 4 and patterning the interconnecting metal (b)                                                          |                |

| Figure 30. Mask 4 used for this fabrication process                                                                                                                              | 9              |

| Figure 31. Polyimide coating using spinning (a), etching polyimide using mask 5, lithograph and RIE (b)                                                                          | •              |

| Figure 32. Mask 5 used for this fabrication process                                                                                                                              | 1              |

| Figure 33. Al sputtering for the bottom electrode contact of a-Se (a), Al layer patterning usin mask 6 (b)                                                                       |                |

| Figure 34. Mask 6 used for this fabrication process                                                                                                                              | í3             |

| Figure 35. The in-house fabricated TFT process in University of Waterloo                                                                                                         | <b>i</b> 4     |

| Figure 36. Transfer (a), and Output characteristics of single in-house fabricated TF (W/L=500 $\mu$ m/50 $\mu$ m). This TFT was fabricated in the same run as the RVCO array (b) | 55<br>51<br>th |

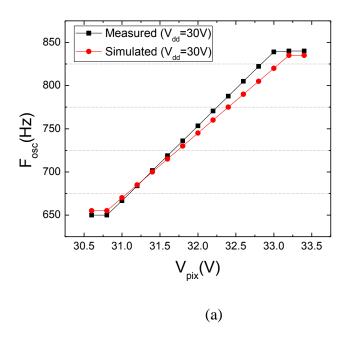

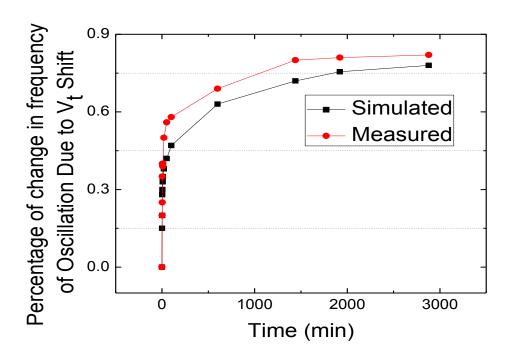

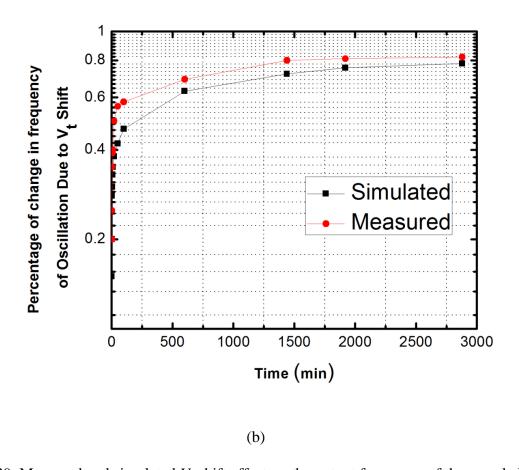

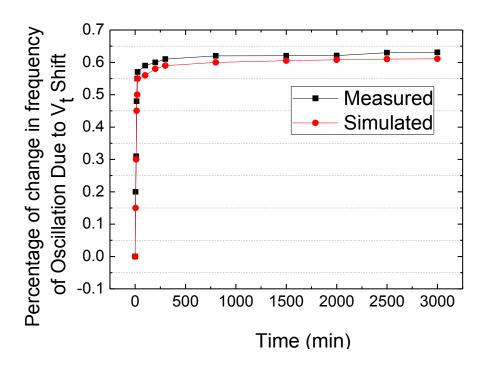

| Figure 39. Measured and simulated $Vt$ shift effect on the output frequency of the sample RVC0                                                                                   |                |

| pixel over time for pixel in Figure 15 (a), (a), for pixel in Figure 15 (b), (b)                                                                                                 | 1              |

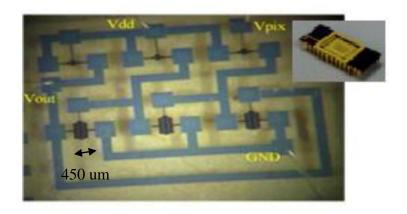

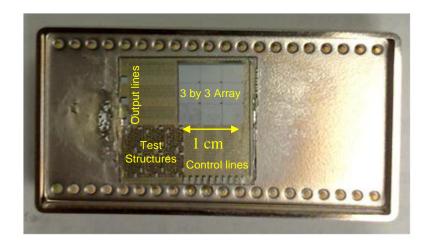

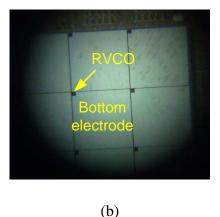

| Figure 40. In house fabricated 3 by 3 RVCO array in the package (a), zoomed in version of the 3          |

|----------------------------------------------------------------------------------------------------------|

| by 3 RVCO array (b)69                                                                                    |

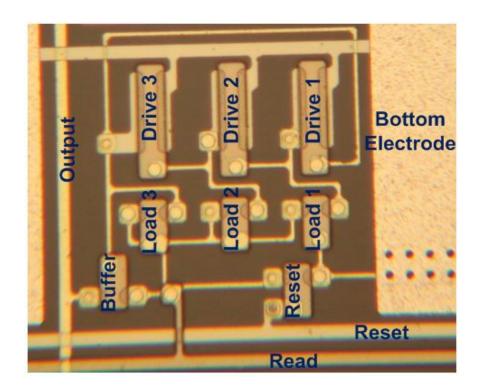

| Figure 41. The die-micrograph of the RVCO pixel in an array70                                            |

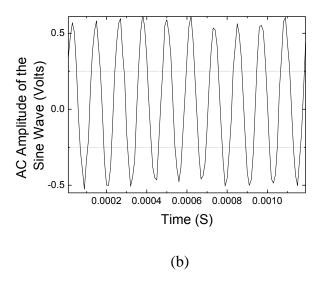

| Figure 42. Figure 42. Off-panel readout circuit for testing the RVCO 3 by 3 array (a), Sample            |

| output oscillation in time domain detected by NI card (b)                                                |

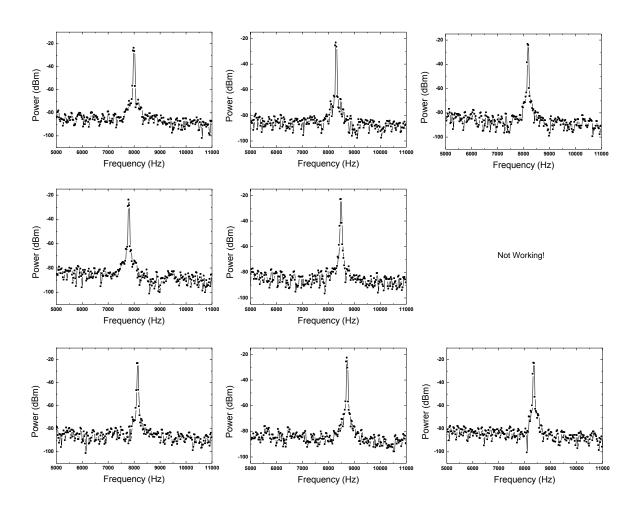

| Figure 43. Output spectrum for the pixels in a 3×3 array of RVCOs (As it can be seen the                 |

| frequency of oscillation is around 7.5 to 8.5 kHz for the pixels; the change in the center               |

| frequency is due to non uniformities in the fabrication process)                                         |

| Figure 44. Measured vs. Simulated $V_t$ shift effect on the output frequency over time for the worst     |

| case for the 3 by 3 RVCO array                                                                           |

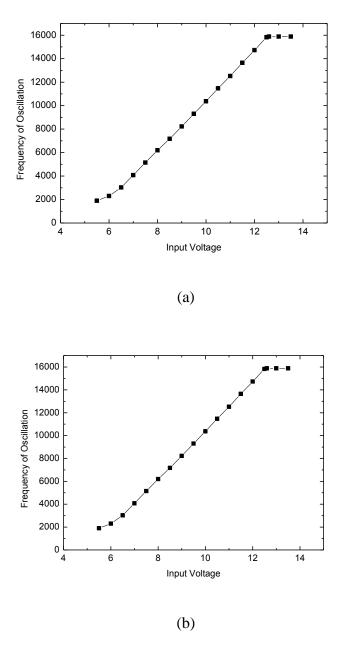

| Figure 45. Frequency-voltage gain characteristics of A1 pixel (a) and A9 pixel (b) (two sample           |

| pixels in the in house fabricated 3 by 3 RVCO array)74                                                   |

| Figure 46. Failed attempt of the selenium direct deposition on the 3 by 3 RVCO array                     |

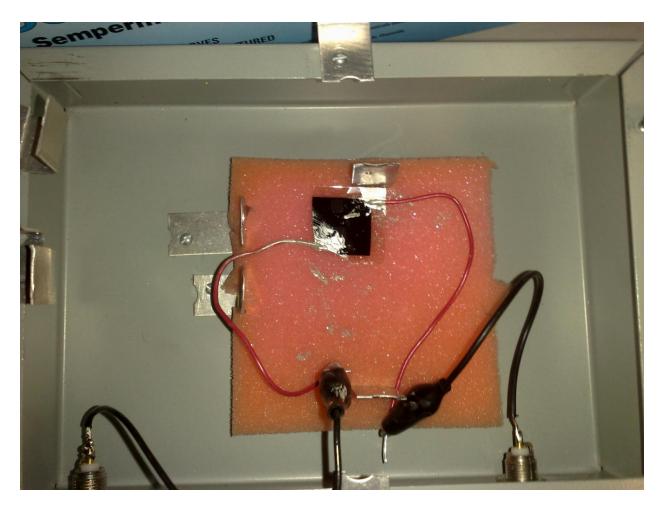

| Figure 47. 50 um thick a-Se sample used to interact with RVCO pixel76                                    |

| Figure 48. The off-panel readout circuit for testing RVCO pixel interacted with a-Se layer76             |

| Figure 49. Measurement setup for testing RVCO pixel interacted with a-Se layer77                         |

| Figure 50. Fe 55 gamma source used to generate 6 keV photons                                             |

| Figure 51. Timing diagram used for testing the RVCO pixel interfaced with a-Se layer79                   |

| Figure 52. Co 57 gamma source used to generate 122 keV photons                                           |

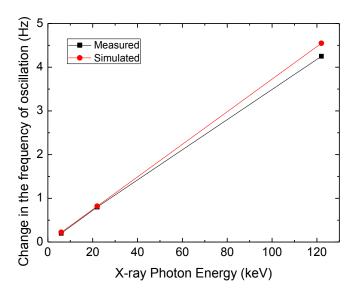

| Figure 53. Frequency change versus the incoming X-ray photon energy                                      |

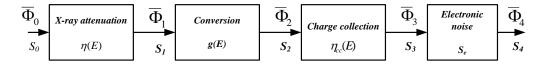

| Figure 54. The linear cascaded-system model flow graph showing the propagation of signal and             |

| noise through the main four stages of the X-ray imager83                                                 |

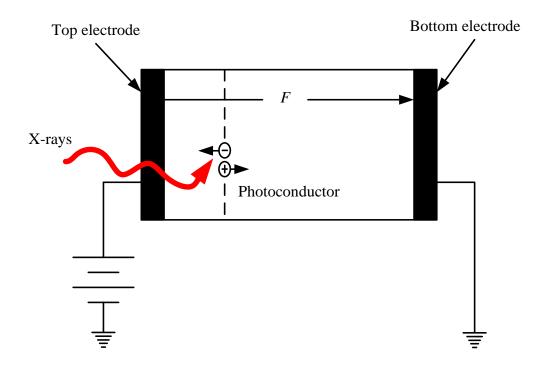

| Figure 55. Model used for calculating $DQE(0)$ [85]84                                                    |

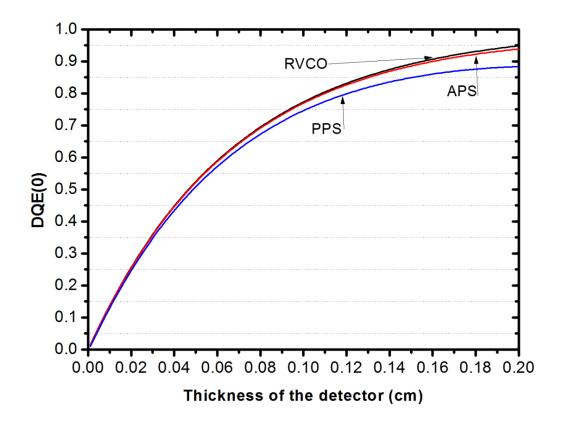

| Figure 56. <i>DQE</i> (0) versus detector thickness with the constant bias value of 10 kV applied to the |

| radiation receiving electrode and a monoenergetic X-ray beam of photon energy E = 52.1 keV               |

| for PPS, APS and RVCO structures                                                                         |

|                                                                                                          |

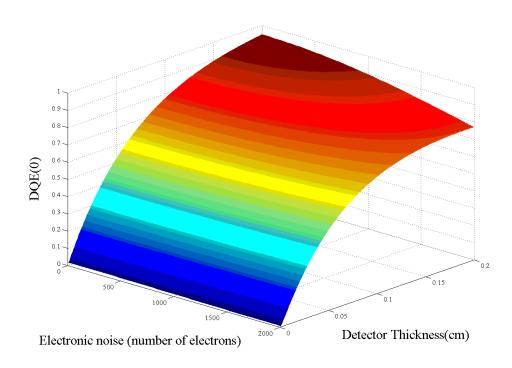

| Figure 57. $DQE(0)$ versus electronic noise and detector thickness (with the constant bia                   | s value of   |

|-------------------------------------------------------------------------------------------------------------|--------------|

| 10 kV applied to the radiation receiving electrode and a monoenergetic X-ray beam                           | of photon    |

| energy $E = 52.1 \text{ keV}$ )                                                                             | 91           |

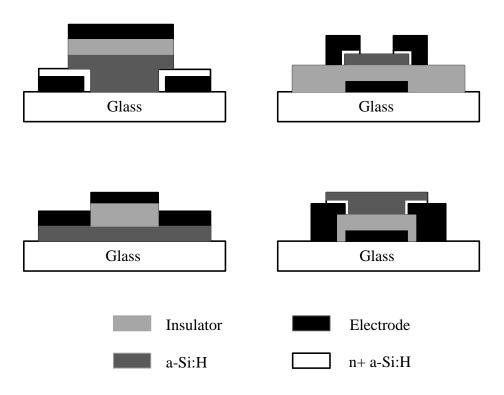

| Figure A.1. Basic a-Si TFT structures [67]                                                                  | 98           |

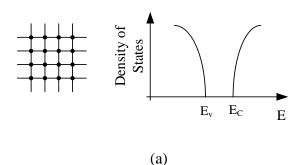

| Figure A.2. Atomic structure and band model for c-Si (a), and a-Si (b) [73]                                 | 100          |

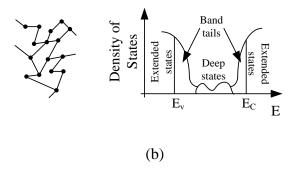

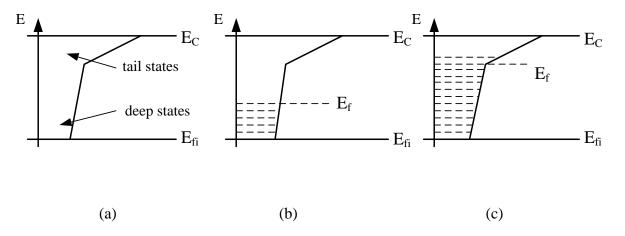

| Figure A.3. Density of states using the Powell model [68], $V_{GS}=0$ (equilibrium), The Fe                 | ermi level   |

| is at the intrinsic Fermi level position, $E_{fi}$ (a), $V_{GS} < V_t$ (subthreshold), Deep states trapping | ng control   |

| the device behaviour. Few electrons are trapped by the tail states (b) and $V_{GS} > 1$                     | $V_t$ (above |

| threshold), the Fermi level is pinned by the tail states (c)                                                | 101          |

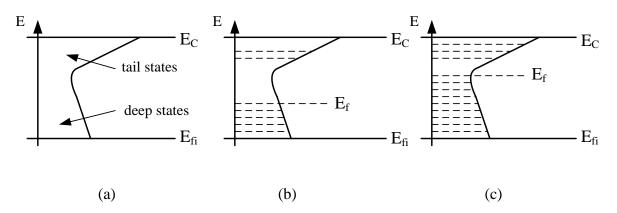

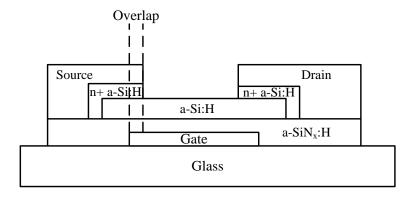

| Figure A.4. DOS using the Shur model [76], $V_{GS}=0$ . The Fermi level is at the intrins                   | sic Fermi-   |

| level position ( $E_{fi}$ ) (a), $V_{GS} < V_t$ . Deep states trapping controls the device behaviou         | r (b) and    |

| $V_{GS} > V_t$ . The Fermi level is at the intersection of deep and tail states (c).                        | 102          |

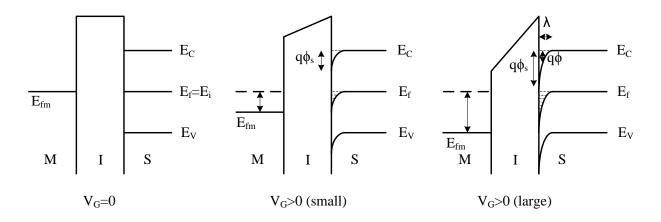

| Figure A.5. Inverted staggered a-Si TFT [9]                                                                 | 104          |

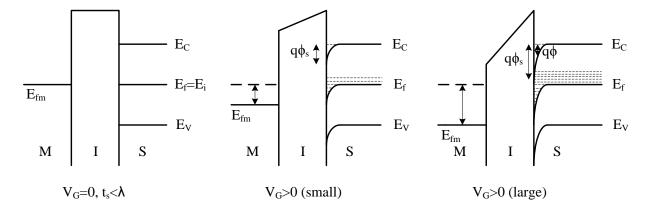

| Figure A.6. Band Diagram for MIS device [9]                                                                 | 106          |

| Figure A.7. MIS band diagrams for a thin layer of a-Si [9]                                                  | 107          |

| Figure A.8. Reference figure for calculating $I_{DS}$ [80]                                                  | 108          |

| Figure A.9. $V_t$ extraction from the linear region of the a-Si TFT [9]                                     | 114          |

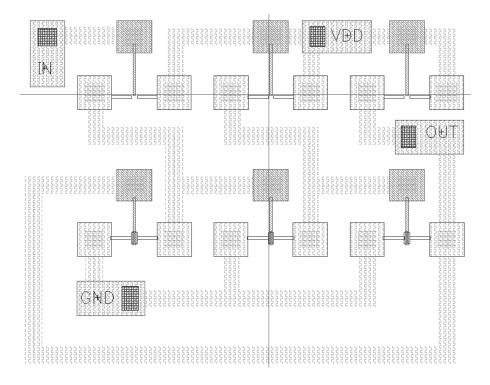

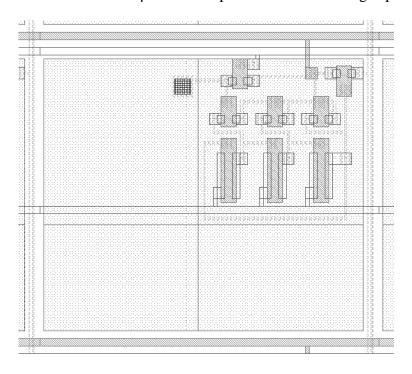

| Figure B.1. The $780 \times 650 \ \mu m^2$ RVCO pixel without a-Se coating capability                       | 116          |

| Figure B.2. The 200×210 $\mu m^2$ RVCO pixel with a-Se coating capability                                   | 117          |

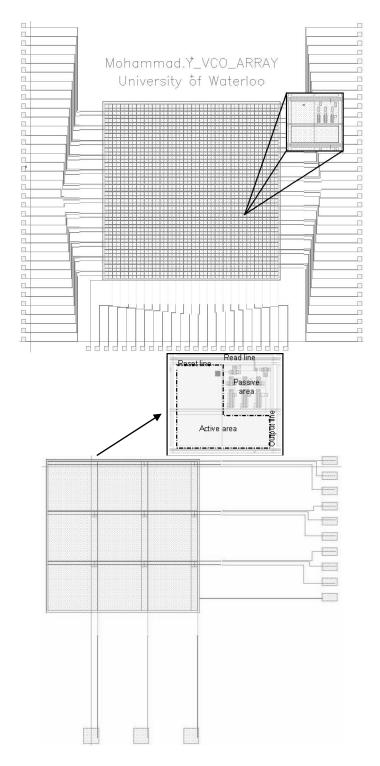

| Figure B.3. RVCO pixel layout in an array                                                                   | 117          |

| Figure B.4. Sample RVCO array layouts. (24 by 21 and 3 by 3)                                                | 118          |

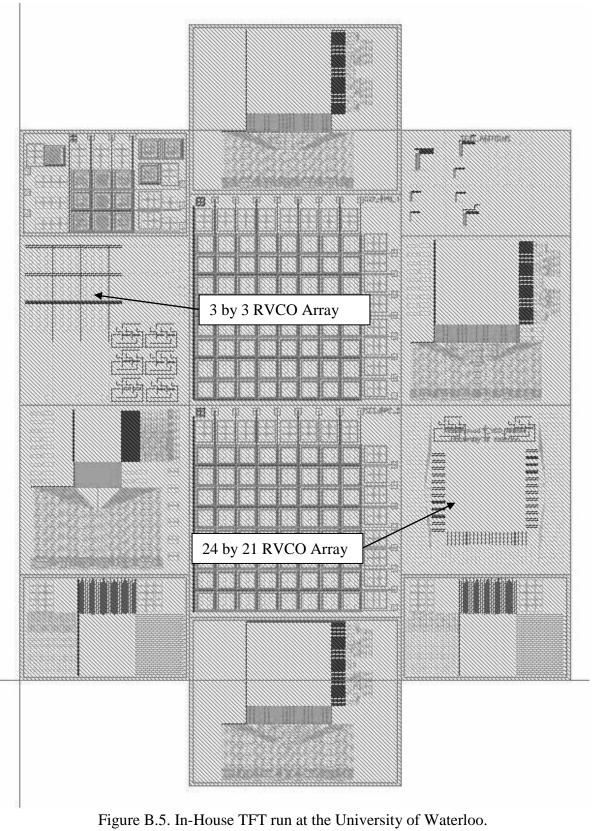

| Figure B.5. In-House TFT run at the University of Watrerloo                                                 | 119          |

## **List of Abbreviations**

PPS Passive Pixel Sensor

APS Active Pixel Sensor

VCO Voltage Controlled Oscillator

RVCO Ring Voltage Controlled Oscillator

TFT Thin Film Transistor

VAPS Voltage mediated Active Pixel Sensor

CAPS Current mediated Active Pixel Sensor

LC Inductance Capacitance

CMOS Complementary Metal Oxide

Semiconductor

PAN Phosphoric - Acetic - Nitric

## 1 Introduction

Many pixel architectures have been proposed to date for active matrix flat panel imagers (AMFPIs). These include passive pixel (i.e. TFT switch based) [1][2] or active pixels (i.e. pixel level amplifier based) [3]. Both types of pixel designs are based on converting the collected charge at the input into an output voltage or current and require either a charge or transimpedance amplifier in the off-panel readout circuit to extract the output signal and make it suitable for further processing.

SNR (Signal to Noise Ratio) is an important metric for AMFPIs. The signal component consists of the X-ray generated charge in the X-ray sensor, while the noise component consists of two independent noise sources [4]: photon shot noise (i.e. photon quantum noise) added in quadrature with electronic noise (consisting of flicker, thermal, and reset noise) from the various semiconductor devices in the readout circuit. The goal for the ideal imaging pixel is to minimize electronic noise such that SNR is a function only of photon shot noise (i.e. a fundamental limit). In considering pixel readout circuits and the related electronic noise, input referred electronic noise is a design parameter that is of interest. Input referred electronic noise in digital imaging pixels is the electronic noise at the output of the pixel divided by the pixel gain. The goal of this thesis is to demonstrate a pixel and a sample array architectures in amorphous silicon (a-Si)

technology that have a negligible input referred electronic noise and therefore, the pixel noise is dominated by only the photon shot or quantum noise.

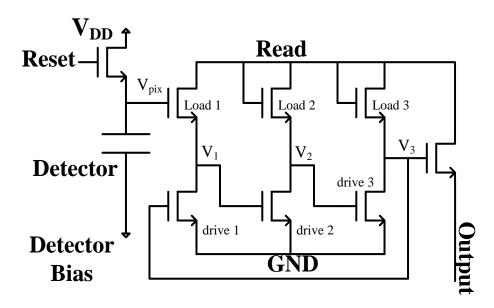

An alternate oscillator a-Si pixel design to PPS and APS architectures was introduced in 2006 [5]. In the oscillator pixel architecture, a voltage controlled oscillator (VCO) plays a central role in signal conversion and transfer. The impinging X-ray beam produces a charge in a pixel level capacitor and the change in the voltage on that capacitor due to the impinging X-ray beam controls the frequency of oscillation of the VCO. The key difference between the previously reported PPS and APS designs and the proposed design is that now the output signal is a frequency. In this thesis, we extend the VCO architecture [5] for X-ray quantum noise limited applications for large area digital imaging. The schematic of the VCO pixel is shown in Figure 1. Since the output of the circuit is frequency and not voltage or current, and also because of the use of an on-pixel buffer, the input referred electronic noise of the pixel is very low, making the pixel suitable for quantum noise limited imaging applications. This is discussed in detail in next chapters. A number of off-panel circuit architectures have been proposed and tested in this thesis.

Figure 1. Ring Voltage Controlled Oscillator Pixel Schematic.

The off-panel readout circuit architecture suitable for in lab testing of the VCO based pixel and array are given as well. Note that the off-panel circuit is used to detect the output of the pixel and storing it for further image reconstruction processes.

In designing the VCO pixel, noise, power consumption, tuning range, pixel area, and frequency of oscillations [6] were considered. Given the range of parameters and primarily the need for simplicity, a ring VCO was fabricated in a-Si technology [5]. The reported ring-oscillator VCO pixel architecture (referred to as RVCO henceforth) is designed to interface with a detector. The choice of a detector is flexible: an indirect detection a-Si PIN photodiode coupled to an X-ray scintillator [7] can be used or alternately, an overlying a-Se direct detection layer [8].

The ultimate goal of this research is to demonstrate via measurements that the input referred electronic noise for the fabricated a-Si pixel oscillator is negligible, making it ideal to detect even single photon interactions in protein crystallography applications (i.e. 6 keV X-ray photons) when used with an amorphous selenium layer as the detector. The second purpose is to simulate and measure the stability and input referred electronic noise for the in-house fabricated RVCO pixel and array. The third target is to optimize the off-panel readout circuitry in order to reduce the fix pattern noise and fringing effects.

#### 1.1 Novelty and Application

The circuit proposed in this thesis is aiming to do Protein Crystallography. Therefore, in this chapter general concepts and requirements of the Protein Crystallography are given. In 2009

a novel way for Protein Crystallography using a-Si TFT flat panel imagers was introduced in [36], which is briefly, using the Avalanche a-Se for the detector level and using the traditional PPS a-Si pixels as the flat panel imager. This approach is not scalable and hence it is challenging to make a large area low cost Avalanche a-Se. The scalability issue in this proposal is addressed by using the ordinary a-Se detector layer and using the proposed RVCO as the pixels in the flat panel imager.

#### 1.1.1 Protein Crystallography

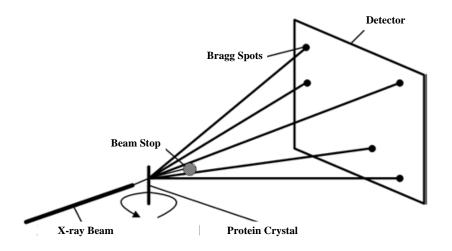

Protein Crystallography is a way to resolve the atomic structure of protein using the intensity distribution of its X-ray diffraction pattern [35]. A conventional crystallography is done by putting the protein crystal inside a thin walled capillary and using a mono energetic X-ray beam of 6 – 20 keV (which has the wavelength of 2.1 to 0.6 angstrom which is comparable to the protein crystal's inter-atomic distances) [36]. The setup is shown in Figure 2. This mono energetic X-ray beam is applied to the crystal structure and a diffracted pattern is formed on the 2D flat panel imager. In order to get a 3D image out of the crystal, several hundred diffraction patterns are recorded in the computer and will be reconstructed using a signal processing software (The protein crystal is rotated around an axis perpendicular to the X-ray beam so that every atomic plane can be exposed to X-rays) [36]. The intensity of the diffracted beam is maximized when it satisfies Bragg's law. Each recorded pattern contains several thousand diffraction maxima, commonly known as Bragg peaks [37]. These peaks are used to reconstruct the crystal structure in the software. An image of a diffraction pattern containing a Bragg peak is shown in Figure 3.

Figure 2. Setup for a typical protein crystallography experiment [36].

Figure 3. Image of a diffraction pattern containing a Bragg peak [36].

#### 1.1.2 Requirements of a Protein Crystallography Detector

There are some requirements that have to be considered for a detector so that it can be used in Protein Crystallography applications. These requirements are detector area, dynamic range, sensitivity, readout time and spatial resolution (pixel size) [37][38].

#### 1.1.2.1 Detector Area

The imaging area is the area required for an ideal detector to collect all the diffraction data with a specified resolution [38]. The detector has to be a large area detector because of two reasons. First, the first 100 orders of diffraction data contain useful data about the protein crystal, therefore a 20 by 20 cm<sup>2</sup> detector area is sufficient to collect all the data about the protein crystal [38][39]. Secondly, background X-ray scatter noise is reduced by using a large area detector farther from the protein crystal. This is because the background X-ray scatter noise drops with the square of the crystal-to-detector distance [39].

#### 1.1.2.2 Dynamic Range

The pixel has to be capable of reading the weak and the strong diffraction spots (one X-ray photon per pixel all the way to  $1.2 \times 10^5$  X-ray photon per pixel) [39][40]. Most of the pixels have to detect the weak spots and a few should detect strong spots.

#### 1.1.2.3 Sensitivity

The protein crystals diffract the X-ray photons weakly, typically less than 0.1% of the incident X-ray beam scatters from the crystal. Therefore, the intensity of the diffracted X-ray is very low [41]. Moreover, radiation damage to the protein crystal might result in a gradual degradation of the resolution of the diffracted pattern [42]. Therefore, the dose of exposure has to be diminished to prevent the protein crystal damage due to the X-ray exposure. So, a very

sensitive pixel is mostly required to detect the small diffraction signal generated from low dose X-ray. Ideally, the detector should detect 1 absorbed X-ray photon. Low quantum energy X-ray photon used in protein crystallography can produce as few as 120 electrons.

#### 1.1.2.4 Readout Time

Readout time is the time required by the detector to read the charge integrated on the detector to the external circuitry. The readout time of the detector should be in the range of seconds to minimize the total X-ray exposure time as well as radiation damage to protein [36].

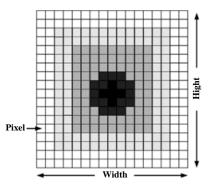

#### 1.1.2.5 Spatial Resolution

The pixel size of the detector should be in a way that a few pixels (typically 3 to 5) can hold each Bragg peak. Therefore, to resolve two adjacent Bragg peaks, there should be about five pixels between them [38][39].

For instance, a 12 keV X-ray source (wavelength about 1 angstrom) and a unit cell dimension of 20 nm in protein crystal and the crystal-to-detector distance of 20 cm, result in Bragg peaks of 100-300 µm. Therefore, a 50-150 µm pixel size is needed [37].

#### 1.2 Thesis Organization

The rest of the thesis is organized as follows. First, a brief introduction to Active Matrix Pixels is given followed by a brief discussion on different structures of oscillators and the suitable structure for being fabricated in a-Si technology (which is the RVCO). Next, the design of the RVCO single pixel and its operation as a pixel and an array are discussed. After that, an ultra low noise RVCO architecture is given and discussed, which has less input referred electronic noise compared to the RVCO architecture given in Figure 1. Then, the fabrication process is described followed by measurements of phase noise and metastability and also measured results of the single RVCO pixel implemented without and with an amorphous selenium (a-Se) layer as the detector for protein crystallography X-ray ranges for an in-house developed RVCO pixel. After that, measurement results of a sample in-house fabricated array of RVCOs are given and discussed. Lastly, Detective Quantum Efficiency (DQE) for the proposed structure (RVCO) is analyzed followed by the conclusion and contributions.

## 2 Active Matrix Pixels

In this chapter a brief background on different structures of Active Matrix Pixels which are passive pixel sensors (PPS) [1][2] or active pixel sensors (APS) [3] are presented.

#### **2.1 PPS**

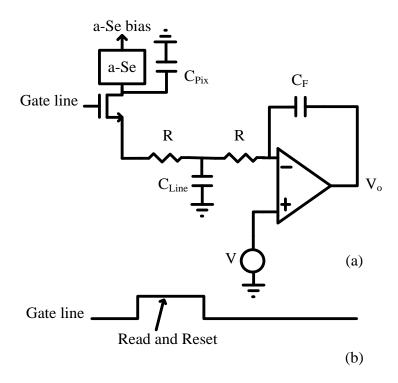

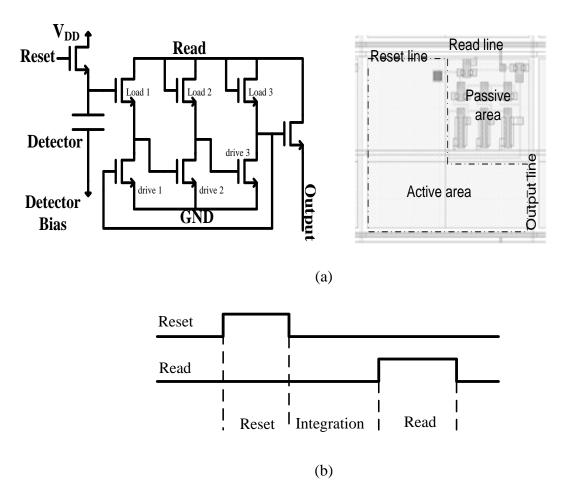

The passive pixel was first proposed by Gene Weckler in 1967. In a PPS structure as it is shown in Figure 4 (a), the charge induced on the pixel capacitor in the integration time is converted to an output voltage in the readout time by means of a TFT switch. Figure 4 (b) shows the operation cycle of the PPS. There are many important factors in designing a PPS structure such as gain and linearity, readout rate and input referred noise (detector noise and electronic noise) [9]. **Gain and linearity**: the passive pixel readout circuit is just a simple switch, therefore it does not provide any gain to the signal on the charge detection node. A voltage gain can be achieved by means of off-panel charge amplifier. This will increase the electronic noise as well. The TFT switch works in the linear mode of the TFT and as a result if the X-ray sensor (Here is a-Se in Figure 4) behaves linearly, the pixel's operation is linear [9]. **Readout rate**: this rate is characterized by the RC time constant of the pixel which is R<sub>on</sub>C<sub>Pix</sub>. For a complete charge readout (95% - 99.3%), about 3-5 time constants are usually sufficient. Given this factor and the

number of rows in a pixelated array of PPS, one can design  $C_{Pix}$  and  $R_{on}$  to achieve the desired frame rate (frames/second) [9]. **Input referred noise**: Based on simulations and measurements in [2] the smallest input referred electronic noise measured for a PPS pixel is around 1000 electrons. This makes PPS to be suitable for applications with higher incoming level of X-ray signals such as chest radiography.

Figure 4. PPS architecture (a) and operation cycle (b).

#### **2.2 APS**

APS was first imported from crystalline Silicon (c-Si) to a-Si technology by Dr. Karim S. Karim in 2001 [3]. He proposed a 3 Thin film transistor (TFT) structure (Figure 5) that extends a-Si TFT technology from traditional switching applications to on-pixel small signal amplification for diagnostic digital medical imaging applications. This a-Si pixel amplifier offers improved signal-to-noise ratios, lower cost, and less off-panel circuit complexity compared to its traditional a-Si switch counterpart (passive pixel sensor). This structure can be used for large area real-time imaging for low-noise fluoroscopic medical imaging that is not viable with current a-Si switch based pixels. More significantly, the pixel (because of its circuit gain) offers potentially reduced patient x-ray doses for other medical imaging modalities, hence improving the safety standards associated with current x-ray imaging practices [3]. Later on, some other researchers proposed other APS structures, each targeted for a specific application.

There are some known different architectures of APS to date. 3-TFT APS structure, 2-TFT APS structure, Hybrid APS structure and Current programmed APS structure. RVCO pixel is novel type of APS pixel which will be discussed in details later on.

#### 2.2.1 3-TFT APS structure

There are two commonly used architectures of 3-TFT APS structures: voltage mediated active pixel sensor (V-APS) [10] and current mediated active pixel sensor (C-APS) [10]. Figure 5 shows these two structures and their timing diagram. Each of these structures has their own benefits as well as some disadvantages which make each of them suitable for specific digital medical imaging applications. For instance it has been shown in [11][12] that the V-APS

structure has a relatively lower electronic noise compared to C-APS architecture. However, V-APS suffers from a constant change of the signal integrated on the line capacitor due to the leakage current of the OFF pixels.

(a)

Figure 5. V-APS architecture and timing diagram (a), C-APS architecture and timing diagram (b)  $(S_1 \text{ and } S_2 \text{ are active high}).$

After the invention of 3-TFT APS, this technology (APS) was carried on in different ways. Each way focused on a specific target such as: higher resolution, higher speed, lower noise, hybrid readout and  $V_t$  shift compensated APS structures.

#### 2.2.2 2\_TFT APS structure

The next APS structure was proposed by Dr. Farhad Taghibakhsh in 2008 (Figure 6) [28]. This architecture uses 2 TFTs aiming at relatively higher resolution and lower noise compared to 3-TFT structure. The advantages over 3-TFT APS are less complexity, smaller pixel pitch, increased pixel gain and higher speed. These advantages make the 2-TFT APS promising for low noise, high resolution and fast digital medical imaging applications including emerging medical imaging modalities, such as mammography tomosynthesis and cone beam computed tomography [28]. The timing and readout of this pixel is exactly the same as the readout of the current mediated active pixel sensor (C-APS).

Figure 6. 2-TFT APS structure [28].

#### 2.2.3 Hybrid APS structure

Dr. Mohammad Hadi Izadi in 2006 reported a hybrid amplified pixel architecture based on a combination of PPS and amplified pixel designs (Figure 7) that, in addition to low noise performance, also resulted in large-signal linearity and consequently higher dynamic range [43]. He showed that this architecture increases the large signal linearity. This is because in traditional APS structure compared to Passive Pixel Sensor (PPS) structure, the output signal suffers from nonlinearity due to higher pixel level input (control) voltages. This research also showed input referred noise levels less than 1000 electrons in real world is approachable [43], making the proposed architecture suitable for low noise digital X-ray fluoroscopy. This pixel's readout is the same as 3-TFT structure and PPS structure if it is used in APS and PPS readout modes, respectively.

Figure 7. Hybrid APS structure [43].

#### 2.2.4 Current programmed APS structure

Dr. Nader Safavian in 2009 reported a dual mode current-programmed, current-output pixel amplifier (Figure 8) for digital medical imaging applications [44]. This architecture can be used in hybrid fluoroscopic and radiographic imagers. The reported architecture promises dual mode X-ray imaging while compensating for the long term electrical and thermal stress known as a-Si TFT threshold voltage ( $V_t$ ) shift due to its specific architecture and on-pixel and off-pixel readout schemes [44]. Refer to [44] for the detailed operation scheme.

Figure 8. Current-programmed APS structure [44].

It is worthwhile to mention that none of the Active Matrix Pixels listed above can have a quantum limited electronic noise at the input of the pixel [13][14]. Therefore, there is a severe need to design an architecture which has a quantum limited electronic noise to be able to be used

for quantum noise limited digital imaging applications, such as protein crystallography, which is the aim of this work. Quantum limited means that the input noise is dominated by the photon quantum shot noise in the detector layer and not the electronic noise.

# 3 Voltage Controlled Oscillators and the Suitable Structure for Digital Medical Imaging Applications

The voltage controlled oscillator (VCO) has the central role of converting the charge accumulated by the impinging X-ray beam to frequency. The output circuit suitable for frequency readout is given in the following sections. There are a lot of VCO structures used in industry and for research purposes. The different structures are shown in Figure 9.

Figure 9. Different types of VCOs.

#### 3.1 LC Tank Oscillators

This structure of oscillator is shown in Figure 10. An LC oscillator can be considered as two 1-port networks connected together. One of them represents the frequency selective tank, where the oscillation occurs. However, the oscillations will die through  $RI^2$  losses in the circuit which is modeled by  $g_{tank}$ . If this energy could be pumped back into the tank as the same rate as it was being dissipated, the circuit would ring forever and this is the basic idea of an LC resonant oscillator. So, the other 1-port represents the active circuit which is modeled by  $g_{active}$  that cancels out the losses in the tank [15]. This oscillator will oscillate when the  $g_{active}$  cancels out the  $g_{tank}$  and also the close loop gain has a zero phase-shift.

Figure 10. LC oscillator structure.

Therefore the close loop gain has to be a real number with a magnitude of greater than or equal to one for the oscillation to occur. Two common used LC oscillators are shown in Figure 11.

Figure 11. Colpits oscillator (a), Hartley oscillator structures (b).

It has been shown in [16] that the frequency of oscillation in a Hartley oscillator in which a TFT is used is as follows,

$$\omega_0 = 1/\sqrt{(L_d + L_g)C_{dg}} \tag{1}$$

And for the oscillations to start, we should have,

$$g_m > L_d / (L_q \times R_L) \tag{2}$$

The equation above shows that for the oscillation to start the gain from gate to drain which is  $g_m R_L$  must be greater than the voltage ratio provided by inductive divider. This means that the gain should be greater than unity.

The calculations in [16] show that the maximum inductor which can be fabricated in the  $200\times200~\mu\text{m}^2$  is 30nH-50nH. The fabrication results in [16] have shown that we can fabricate a 30nH inductor in the  $200\times200~\mu\text{m}^2$  area and we can have a frequency of approximately 500MHz with this inductor size. But, for designing an LC oscillator in a-Si TFT technology, we need an inductor above  $1000~\mu\text{H}$ , to have about 1 MHz of oscillation frequency, which is due to the limit of maximum TFT speed. There is currently no way to design and fabricate an LC oscillator in a-Si technology in the desired area.

#### 3.2 Crystal Oscillator

Crystal oscillator is an electronic oscillator circuit based on a piezoelectric material. The mechanical resonance of the crystal of the piezoelectric material is used to generate an oscillating signal with a precise frequency. Figure 12 shows the electronic symbol and the equivalent circuit of a quartz crystal oscillator. This oscillator has two modes of oscillations (series  $\omega_s$  and parallel  $\omega_p$ ). Depending on the frequency of oscillation and load capacitance and series resistor, the

crystal oscillates in one of the modes or in a frequency between two modes. For further information on crystal oscillators which are beyond the target of this thesis, refer to [45][46][47].

Figure 12. Electronic symbol and equivalent circuit for a quartz crystal in an oscillator.

$$\omega_S = \frac{1}{\sqrt{L_1 C_1}}$$

,  $\omega_p = \sqrt{\frac{C_1 + C_0}{L_1 \cdot C_1 \cdot C_0}}$  (3)

This configuration is not suitable for voltage controlled oscillators and also it cannot be fabricated over large area. Therefore, this configuration cannot be used for large area digital imaging applications.

### 3.3 Wein-Bridge Oscillator

The Wein-Bridge oscillator was first introduced in 1981 by Max Wein. The schematic of the circuit is shown in Figure 13. The bridge has four resistors and two capacitors, as it is shown in Figure 13. One can say that this oscillator is a combination of a positive feedback system and a band pass filter [48].

$$W = \frac{1}{RC} \tag{4}$$

This architecture has an op-amp and a number of resistors in it. As a result, it is challenging to fabricate this architecture in a-Si technology in a reasonable area due to the huge size of TFTs compared to CMOS transistors and also the area of the resistors. In other words, each pixel is going to be very huge in terms of size, which makes it useless for large area digital imaging (more specifically, protein crystallography).

Figure 13. Wein-Bridge oscillator architecture.

### 3.4 Phase-Shift Oscillator

This oscillator configuration consists of an inverting amplifier and a feedback filter which shifts the phase of the amplifier's output by 180 degrees at the oscillation frequency. A simple phase-shift oscillator architecture is shown in Figure 14. The frequency of oscillation for such configuration is as follows,

$$W = \frac{1}{2\pi RC\sqrt{6}}$$

$$(R_1 = R_2 = R_3, C_1 = C_2 = C_3)$$

(5)

The overall gain of this configuration has to be greater than 1 or else the oscillation will die ( $R_{1f}>29R_1$ ). This architecture is not suitable for a-Si large area fabrication because of the presence of the op-amp and resistors in the configuration. Op-amps and resistors cannot be fabricated in a reasonable area in a-Si technology and therefore, each pixel will be very big which makes it useless for digital imaging applications (more specifically, protein crystallography).

Figure 14. Phase-Shift oscillator architecture.

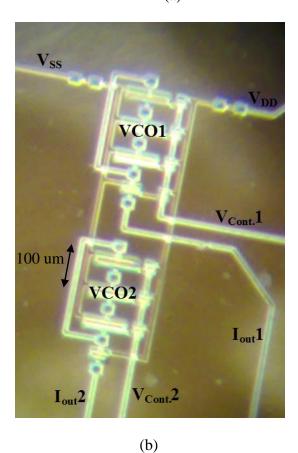

### 3.5 Relaxation Oscillator

The structure and period of oscillation are shown below (Figure 15). Circuit simulations for  $V_T = 5 \text{V}$ ,  $\mu_{band} = 0.6 \text{cm}^2/\text{V}$ .s and circuit dimensions of  $m_{load(1,2)} = 350 \mu\text{m}/5 \mu\text{m}$ ,  $m_{drive(1,2)} = 550 \mu\text{m}/5 \mu\text{m}$ ,  $m_{osc} = 50 \mu\text{m}/5 \mu\text{m}$ ,  $m_{osc} = 2 \text{pF}$ , and  $m_{osc} = 2 \text{pF}$ , an

higher phase noise [17]. Therefore, a relaxation oscillator is not a good choice for being fabricated in a-Si technology.

Figure 15. Structure and frequency of oscillation for a relaxation oscillator.

### 3.6 RVCO Pixel Architecture and Operation

The ring oscillator structure is formed by connecting an odd number of inverter stages in a loop. Although usually at least five inverters are used to ensure oscillations will start, it is possible to start oscillations with a minimum of three inverters (Figure 1). A smaller number of inverters leads to a higher oscillation frequency ( $f_{osc}$ ). Taking all the parameters into account, the RVCO structure is the best choice for being fabricated in a-Si technology. In the RVCO, the first stage's bias current is controlled by the input voltage at the gate of the Load1 TFT (see Figure 1). The rising edge at node  $V_I$  propagates through nodes  $V_2$  and  $V_3$  to return inverted after a delay of  $3t_p$ . For a general case of N stages,  $180^\circ$  of phase shift is provided by the chain and sufficient gain (the overall gain >1) should be provided at  $f_{osc}$ . The gain of each stage should be greater than 1 to ensure that the oscillation will not get damped. As seen in Figure 1, each stage's load is an active load and therefore, the gain of each stage of the oscillator can be derived as follows,

$$Gain = \left| \frac{V_o}{V_{in}} \right| = \sqrt{\frac{\left(\frac{W}{L}\right)_{Drive}}{\left(\frac{W}{L}\right)_{Load}}} > 1 \tag{6}$$

The  $f_{osc}$  can be derived once the propagation delay  $t_p$  of each stage is known.  $t_{pHL}$  is the time it takes for the output to reach from the maximum value to 50% of its minimum and similarly for  $t_{pLH}$ . The charge-discharge time for an RC network from maximum to 50% is 0.69RC. For simplicity we can assume that both rise and fall times are equal. Therefore the propagation delay ( $t_p = t_{pHL} = t_{pLH}$ ) is as follows,

$$t_P = \frac{0.69C_P}{g_{m-Load}} \tag{7}$$

where  $C_P$  is the effective capacitance at each node (Figure 16) and  $g_{m\text{-}load}$  is the load TFT's transconductance. This total capacitance can be calculated as follows. The capacitor  $C_{drive}$  is the overlap capacitor between gate and source (or drain) of the drive TFT and  $C_{load}$  is the overlap capacitor between gate and source (or drain) of the load TFT. Note that the gain of each stage is assumed to be around 2, therefore by averaging the node capacitance of the positive and negative cycles for each stage and using the Miller effect, we estimate the node capacitance. Another assumption is that the  $C_{drive}$  is much bigger than  $C_{load}$  and therefore,  $C_{load} + C_{drive} \sim C_{drive}$ ,

$$C_P = \frac{3}{2}C_{gs-drive} + C_{gs-Load} \tag{8}$$

Figure 16. Positive cycle in each inverter stage (a), Negative cycle in each inverter stage (b).

So, the frequency of oscillation can be written as,

$$f_{osc} = \frac{1}{2Nt_P} \tag{9}$$

We can consider two states for each stage: positive and negative. In the positive state the drive TFT is ON and in the negative state the drive TFT is OFF. The small signal circuit models for both states are shown in Figure 16. Using expressions for  $f_{osc}$  and  $t_P$ , the frequency-voltage gain ( $\Delta f_{osc}$ ) can be calculated as follows,

$$\Delta f_{osc} = \frac{\Delta g_{m-Load}}{6 \times 0.69C_P} = \frac{\mu C_{ox}(W/L)_{Load} \Delta V_{pix}}{4.14C_P}$$

(10)

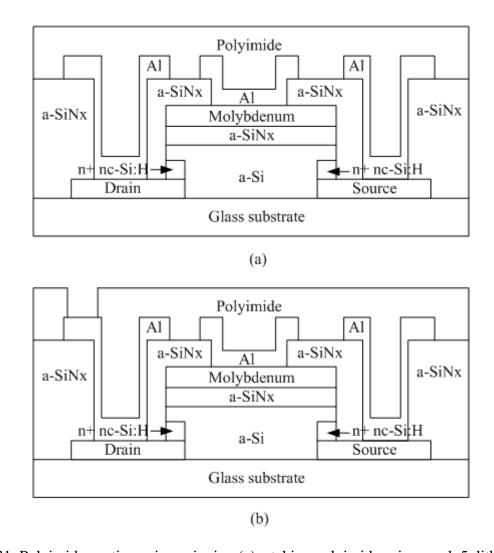

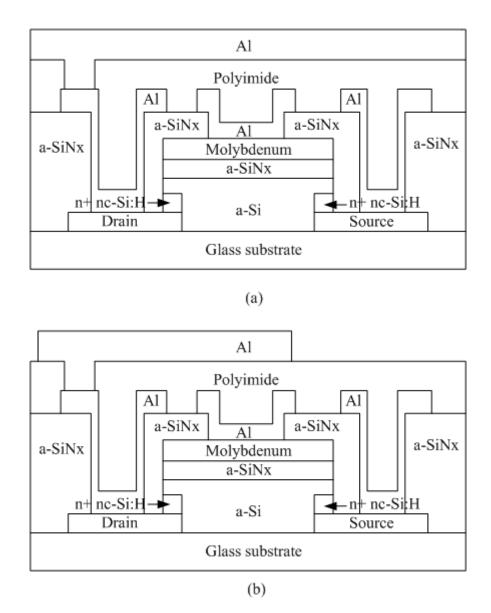

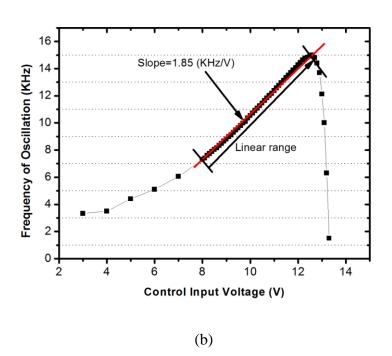

Figure 17 (a) shows the in-house fabricated pixel using large size TFTs just for proof of concept. This architecture, due to its low frequency-voltage gain (90 kHz/V), is not suitable for phase noise and metastability tests.  $((W/L)_{load1}=(W/L)_{load2}=(W/L)_{load3}=50\mu\text{m}/50\mu\text{m},$   $(W/L)_{drive1}=(W/L)_{drive2}=(W/L)_{drive3}=300\mu\text{m}/50\mu\text{m})$  Figure 17 (b) shows the in-house fabricated RVCO pixel excluding the reset TFT using smaller TFT sizing to get a high enough frequency-voltage gain (1.85 kHz/V). This pixel has been used for all the measurements for the single RVCO pixel.  $((W/L)_{load1}=(W/L)_{load2}=(W/L)_{load3}=10\mu\text{m}/10\mu\text{m}, (W/L)_{drive1}=(W/L)_{drive2}=(W/L)_{drive3}=60\mu\text{m}/10\mu\text{m})$

There are three modes of operation for each pixel. 1) **Reset mode:** In this mode the reset TFT is on and the RVCO is off (which reduces inter-pixel crosstalk), resulting in the input node being reset to  $V_{pix} = (V_{in} - V_{t-reset})$ , where  $V_{t-reset}$  is the threshold voltage of the reset TFT. 2) **Integration mode:** In this mode the reset TFT and the RVCO are both off and the detector accumulates the signal on the input capacitor at the gate of Load1 TFT. This brings about a change in the input voltage. 3) **Readout mode:** In this mode the VCO will be turned on and the

reset TFT is kept off. This allows the circuit to start oscillating with respect to the input voltage  $(V_{\text{pix}})$ . The operation of the pixel is discussed in the next chapter.

(a)

Figure 17. In-house fabricated RVCO pixel with bigger size TFTs(a), with smaller size TFTs (b).

# **4 RVCO Structure and Operation**

### **4.1 RVCO Pixel Structure and Operation**

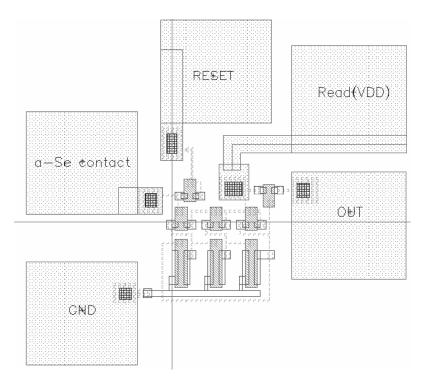

AS shown in the previous chapter, the RVCO is the best option to be fabricated in large area in a-Si technology. The architecture of the RVCO single pixel is shown in Figure 1. As it has been discussed in the previous chapters, the core of this pixel is a 3-stage ring voltage controlled oscillator. There is another TFT used for resetting the pixel in each readout frame. Also, an on-pixel buffer (common drain amplifier) is used at the output of each pixel. Suppose an RVCO pixel is used in an array. This buffer eliminates the loading effect of the readout line. Otherwise, the loading effect of the line would change the frequency of oscillation of the pixel. This buffer also eliminates any noise sources on the readout line affecting the pixel operation. This is because of the gate oxide isolation of the buffer TFT. In other words, the gate oxide of the buffer TFT, doesn't allow any electronic noise presented in the drain source current of it to be transferred to the gate of this TFT. Thus the noise in the readout line doesn't affect the input referred electronic noise of the pixel. Figure 18 (a) shows the pixel architecture along with its layout. Timing of the RVCO pixel operation is given in Figure 18 (b). As it can be seen from the layout (Figure 18 (a)), there are two different areas in the layout. One is the passive area which

has the RVCO TFTs for reading out the X-ray generated charge, and one is the active area which is the bottom-electrode connection for the detector layer which is a-Se in our case.

Figure 18. RVCO pixel architecture and layout (a), Timing diagram of the RVCO pixel.

### 4.1.1 RVCO single pixel design

In designing an RVCO single pixel, some design requirements have to be met. These requirements are as follows: noise, power consumption, fringing effect, tuning range, pixel area, and frequency of oscillations [6].

Input referred electronic noise has to be very low and to achieve such low noise we have to consider some requirements. The electronic noise sources in the RVCO pixel are: data line noise, phase noise in the RVCO pixel and reset noise in the reset switch capacitor configuration used for resetting the pixel. The noise simulation and measurements will be discussed in future chapters. Each of these noise sources are taken into account in the design of the RVCO pixel. Reset noise and data line noise sources are eliminated by use of techniques proposed in future chapters and use of the on-pixel buffer, respectively.

Power consumption is another important point in designing an RVCO pixel. Power consumption in an array of RVCOs causes the flat panel to heat up and therefore causes some inconsistency in the array's behavior such as  $V_t$  shift and other problems. In this design the power consumption is diminished by using the timing pattern shown in Figure 18 (b). In this timing scheme the pixel is only operating when the output of the pixel has to be readout. Otherwise, the pixel is kept OFF by applying 0 V for the read signal.

Fringing effect is caused by overlapping function of the neighboring pixels in an array. If there are so many neighboring pixels oscillating at the same time with different oscillation frequencies, then different frequency of oscillations might interfere with each other. This issue is addressed by the timing scheme used for the pixel readout shown in Figure 18 (b). Turning ON each pixel only for the readout period and keeping it OFF for the rest of the frame eliminates fringing effect.

Tuning range is another important issue in designing the RVCO pixel. In an array of RVCO pixels each pixel is reset to a value. This value should be picked wisely, otherwise the pixel will not oscillate or the output response of the pixel will not be linear. This issue is addressed by resetting each pixel to the voltage in the middle of the linear range of the

frequency-voltage plot plus the threshold voltage of the reset TFT. This plot is attained by characterising the array. Another important issue is that after resetting the pixel, it is time for integration of the X-ray incoming signal. This signal should not saturate the pixel which doesn't for this design. These will be discussed further in future chapters.

Pixel area is determined by the application. In this thesis the target application is protein crystallography and the area needed for each pixel is given by protein crystallography requirements. This requirement is addressed in this design and will be discussed further in the future chapters.

Frequency of oscillation is the most important component in designing the RVCO pixel. This frequency should be high enough to extract the signal from the output data easily and also to get a high signal to noise ratio. For a-Si technology which is used in this research, frequencies up to some hundred kHz are achievable (in the industry standard fabrication). However, frequencies in the range of some kHz are sufficient enough to meet all the requirements.

The specific design constraints and results of the single pixel RVCO will be given in future chapters.

### 4.2 RVCO Array Structure and Operation

The array structure is nearly the same as the passive pixel sensor (PPS) [1][2], and active pixel sensor (APS) [3] array structures. This architecture consists of overlapping lines between the pixels for controlling the pixels and reading the data out of them. Each RVCO consists of a core and two extra TFTs (Figure 18 (a)). The six TFTs in the middle of the single pixel (Figure 18 (a)) make a three stage RVCO. The single TFT on the top left hand side of the RVCO in

Figure 18 (a) is used to reset the input of the pixel after each readout. The single TFT on the top right hand side of the RVCO in Figure 18 (a) is nothing but a common drain amplifier to isolate the output of the RVCO from the off-panel circuit. As it has been discussed in the previous chapters, this is to reduce the fix pattern noise and to omit the loading effect at the output of the RVCO. In other words, it eliminates any change in the frequency of oscillation of the pixel due to loading effect. Also, it isolates the pixel from the off-panel readout circuitry which cancels any noise effects from the output to be transferred into the pixel (This is due to the gate oxide isolation of the common drain TFT). Therefore, this cancels out any change in the frequency of oscillation of the pixel due to the noise sources from the off-panel readout circuitry.

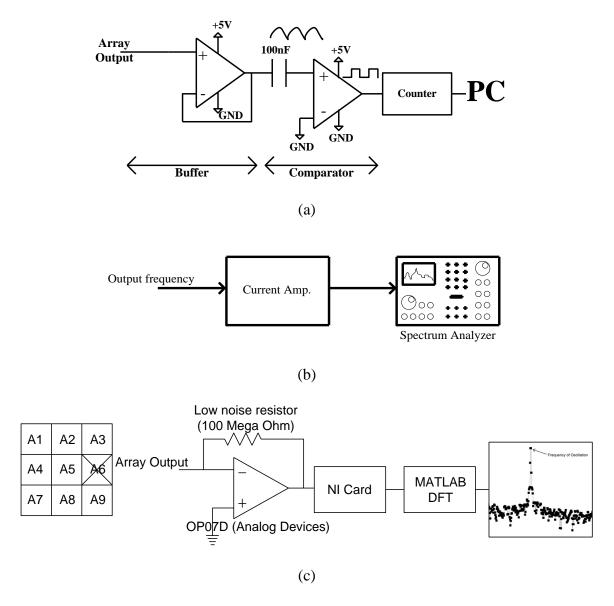

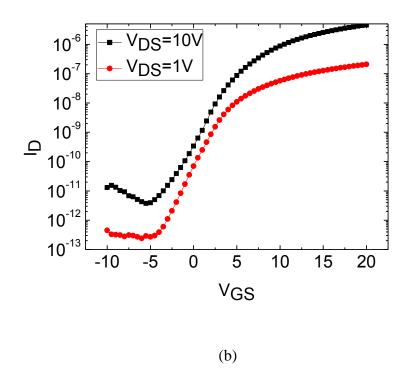

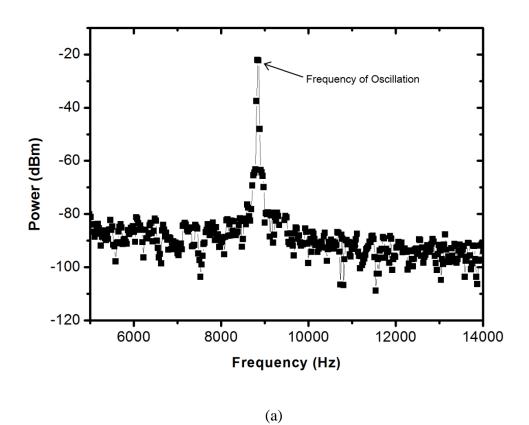

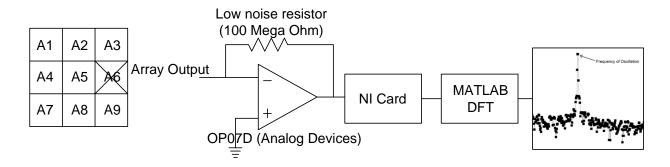

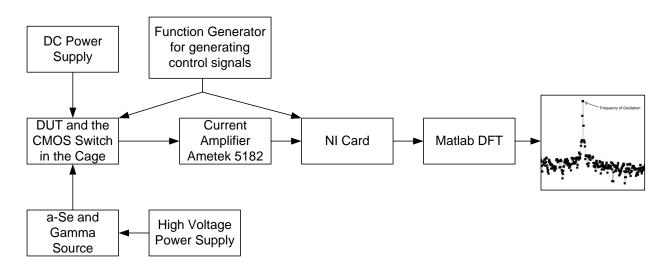

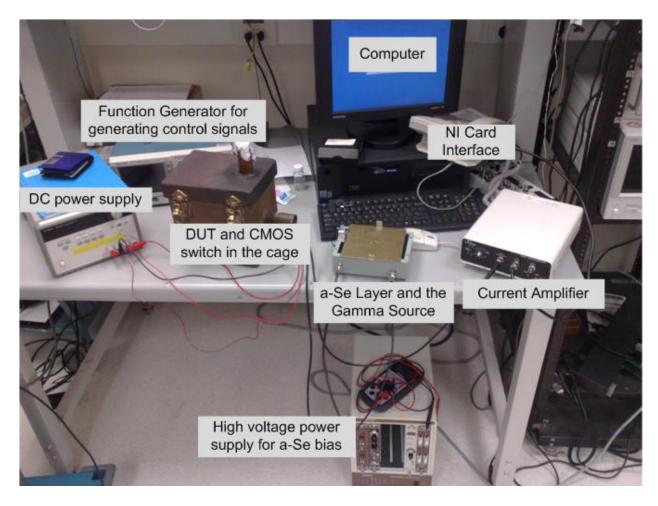

The timing diagram and a simple 2×2 array structure of RVCOs are shown in Figure 19. The readout is done in a traditional row column addressing way. Each column output signal of the array is connected to an off-panel readout circuit. Off-panel readout circuit architectures in Figure 20 (b) and (c) are used in this research for ease of measurements. Figure 20 (a) shows a sample off-panel circuit structure that has to be used for industrial level readout. The circuit in Figure 20 (a) consists of a buffer followed by a comparator and a counter. Note that the 100nF capacitor is used to eliminate the DC component of the signal. This architecture is proposed to be used in industrial level readout. The circuit in Figure 20 (b) consists of a current amplifier followed by spectrum analyzer. This circuit is only used for single pixel testing and testing the pixels one by one in an array to make sure all of them are functioning. The circuit shown in Figure 20 (c) is a trans-impedance stage (current amplifier) followed by NI card for data collection. Matlab is used for DFT (Discrete Fourier Transform) implementation and quantifying the output spectrum in dBm. For simplicity of measurements, the readout is done for each row at a time. For example, the testing of the first row is done, then the second row, and so on.

|        | Reset | Integration | Readout | Reset | Integration | Readout | Voltage Levels         |

|--------|-------|-------------|---------|-------|-------------|---------|------------------------|

| Read1  |       |             |         |       |             |         | 0 to 25 V              |

| Reset1 |       |             |         |       |             |         | 0 to V <sub>in</sub> * |

| Read2  |       |             |         |       |             |         | 0 to 25 V              |

| Reset2 |       |             |         |       |             |         | 0 to V <sub>in</sub> * |

|        |       |             |         | (b)   |             |         |                        |

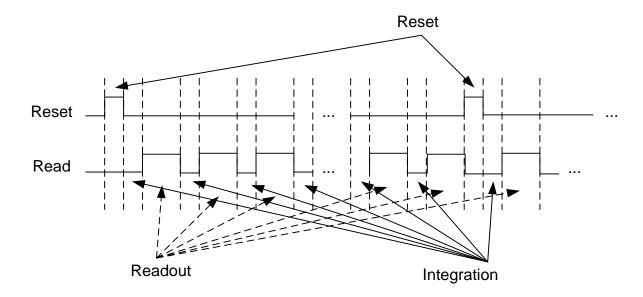

Figure 19. Schematic of a 2 by 2 array (a), operation of the array (b) ( $V_{dd}$ =25 V). Read and Reset signals are controlled row by row and the readout is done column by column (Vin is the middle voltage of the linear range of the frequency-voltage plot plus the threshold voltage of the reset TFT).

There are three modes of operation for each pixel. 1) **Reset mode:** In this mode the reset TFT is on and the RVCO is off (which reduces the fringing effect), resulting in the input node to reset to  $V_{pix} = (V_{in} - V_{t-reset})$ , where  $V_{t-reset}$  is the threshold voltage of the reset TFT. 2)

**Integration mode:** In this mode the reset TFT and the RVCO are both off and the detector accumulates the signal in the input capacitor. This brings about a slight change in the input voltage. 3) **Readout mode:** In this mode the VCO will be turned on and the reset TFT is kept off. This allows the circuit to start oscillating with respect to the input voltage.

Figure 20. The different readout circuits used for RVCO pixel and array readout.

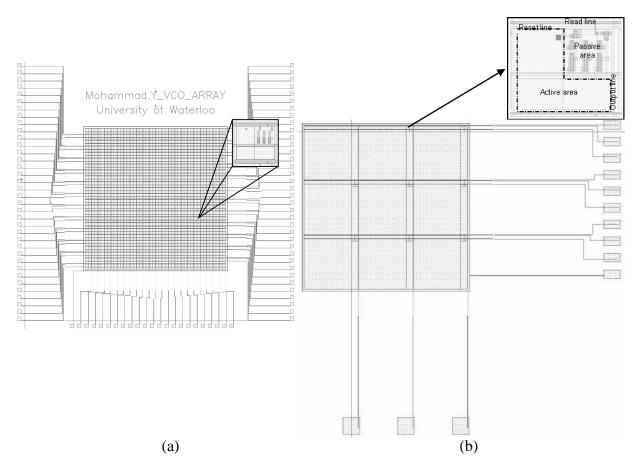

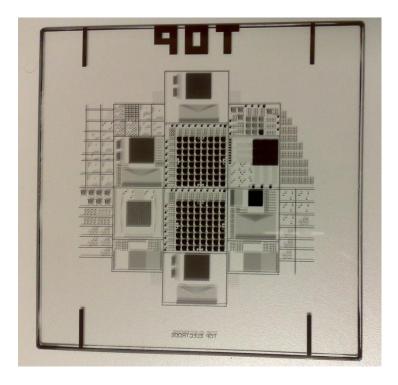

The layout of the 3 by 3 and 24 by 21 arrays fabricated in-house at the University of Waterloo are given in Figure 21. Only the 3 by 3 array is tested in this research. The 24 by 21 array was accidentally cut through in the dicing process. As it can be seen, the 3 by 3 array has a huge active area compared to the 24 by 21 array. Both of these arrays are 1 cm<sup>2</sup> and therefore, the 3 by 3 array has a huge active area for each pixel. The passive area sizes are the same for both of the arrays.

Figure 21. Layout of the 24 by 21 RVCO array (a) and 3 by 3 array (b).

### 4.3 Ultra Low Noise RVCO Structure and Operation

The ultra low noise RVCO pixel architecture is based on the idea of cancelling the reset noise in the pixel as given in [49]. As it was discussed before, the major noise sources in the RVCO are: data line noise which includes all the noise sources in the data line plus the noise sources in the off-panel readout circuit. This noise is cancelled out by use of the on-panel buffer as the details were discussed before. Phase noise in the RVCO is the most important noise source in the RVCO pixel. This noise will be thoroughly analyzed (simulated and measured) in the future chapters. Jitter in the RVCO is another noise source which will be discussed in the future chapters. The analysis done for the jitter shows that this noise source can be ignored. This is because of the parameters used for RVCO design and the way the pixel is readout (timing). Reset noise at the input capacitor of the pixel is the last noise source in the RVCO pixel. However, reset noise is a major component of the noise at the input of the pixel.

Reset noise is around 125 electrons on a 200 fF capacitor ( $\sqrt{\frac{kT}{c}}$ ). However, there are ways to eliminate this noise. One way is to reset the pixel after every 100 frames. This results in no reset noise in 99 frames and we only have noise in 1 frame and the data for that frame can be ignored. We can do this since we have a slight change in the frequency of oscillation in each frame; in other words, the amount of voltage change on the input capacitor after each frame is very small and therefore even after 100 frames, the input capacitor is not going to be charged up to a value that causes the RVCO to work outside the linear range. The VCO architecture is aimed at low incident X-ray fluence protein crystallography (6-20 keV X-ray photons); therefore, the maximum change for a single 20 keV photon in the voltage at the input capacitor (of 200 fF) is expected to be around 320 uV (assuming an X-ray to charge conversion gain of 50 eV per

electron hole pair yielding on average 400 electron hole pairs created for a 20 keV photon in a selenium X-ray detector) during each frame. Moreover, the dark current of the amorphous selenium detector in 33 us period (integration time) for one frame is changing the voltage on the input capacitor (of 200 fF) by 26.5 mV (using a simple formula this can be calculated, It=CV, where I is the current, C is the input capacitor, t is the integration time and V is the change in the input voltage). During the reset period (which can be set to occur after every 100 frames), the voltage of the input capacitor can be designed to reach the middle of the linear range of the frequency-voltage characteristic of the RVCO. This means after 100 frames, even if the input signal is maximum for all the frames, the amount of change in the input voltage of the capacitor is as small as  $2.68 \ V \ (100 \times (26.5 \ mV + 320 \ uV))$ ). The RVCO pixel is designed to work in the linear range for a span of 6 volts. Therefore, the RVCO pixel, even with  $2.68 \ V$  change in the input voltage, definitely works in the linear range.

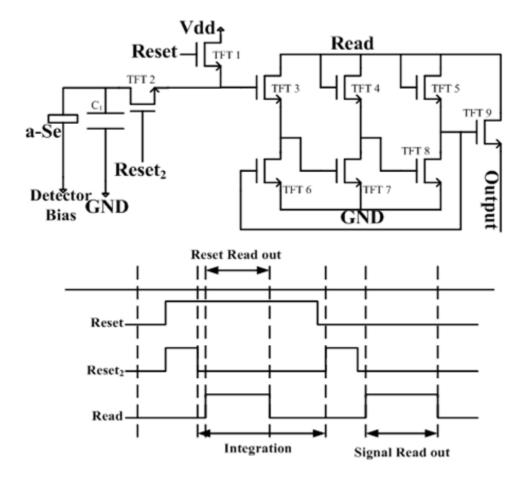

Another way to address the reset noise and cancel it out is to use the architecture used in Figure 22. In this figure the RVCO pixel is on the right hand side and a switch cap configuration is connected to it, which is shown on the left hand side. The timing of this pixel architecture is shown in Figure 22 as well. The pixel operates as follows: First Reset and Reset<sub>2</sub> signals are pulsed, which results in the  $C_1$  to reset. Then the Reset<sub>2</sub> signal is set to 0 V which isolates the detector (a-Se) and  $C_1$  from the RVCO pixel. The integration starts a bit after setting the Reset<sub>2</sub> signal to 0 V. In the meantime, Reset signal is kept high to keep the input of the RVCO pixel (gate of TFT 3) at the reset value. Before setting the Reset signal to 0 V, the Read signal is pulsed resulting in the readout of the reset value. Therefore, the reset value is sampled which includes the Reset noise. Then the Reset signal is set to 0 V and after the integration period is over, the Reset<sub>2</sub> signal is pulsed. This transfers the X-ray generated data on the  $C_1$  to the

capacitor at the gate of TFT 3 (which is the gate capacitor of TFT 3). Then the Read signal is pulsed again and the signal is read. This signal is the sum of the reset value and the X-ray generated signal. Thus by subtracting this signal by the reset value readout at the first readout period, the reset noise as well as the threshold variations in the reset and input transistors are eliminated.

Figure 22. Ultra low noise RVCO structure and timing diagram.

Correlated Double Sampling (CDS) technique can be used as well. In CDS technique, the original RVCO pixel shown in Figure 1 is used. First the RVCO is reset and the reset voltage is readout and then the X-ray builds up a signal on the input capacitor and the signal is readout again. But, the problem is the readout time of the RVCO. If a tiny difference in the frequency of

oscillation is meant to be measured, a long readout time will be required which causes the CDS not to be a true CDS. A true CDS needs the readouts to be done so close to each other that they are correlated and the subtraction of the readouts eliminates the reset noise. However, this technique is never getting rid of the reset noise and the fixed pattern noise completely. In the case of long readouts, the readouts are so far away from each other in terms of time. Therefore, CDS results in increasing the reset noise by a factor of  $\sqrt{2}$  [49].

Hence the only way to cancel out the reset noise and the fixed pattern noise due to the  $V_t$  (threshold voltage) change of the reset and input TFTs is the way used in Figure 22.

Therefore in an ultra low noise pixel architecture the only important noise source is the phase noise, since all other noise sources are canceled out. In the future chapters, this noise will be discussed in detail and input referred electronic noise will be simulated and measured.

# **5 Fabrication Process**

This process took most of the time for this research. Fabrication is one of the most important steps in implementing a device. This is because a slight error in the fabrication process might cause the whole design to fail. For this research, 10 fabrication runs were done. 6 of these runs failed due to design errors, layout errors or fabrication errors. The fabrication process used for this research is a top gate 6-mask a-Si TFT fabrication process (top gate is used for ease of fabrication, as well as performance). Each step of the process is characterized and then used in the actual TFT fabrication process. The actual fabrication process is a 4 day to a week run based on how each step goes and how the facility operates at the time. The fabrication process is shown in this chapter step by step.

The fabrication steps are as follows: 1) a 100-nm Chromium thin film was prepared by sputtering, followed by a 50-nm heavily doped nanocrystalline thin film derived by Plasma Enhanced Chemical Vapor Deposition (PECVD). The double layers were patterned through the first mask for source and drain contacts of the top-gate TFT on a carefully cleaned Corning 1737 glass substrate; 2) amorphous silicon, silicon nitride, and Molybdenum thin films were deposited by PECVD and sputtering consecutively. The triple layers were then patterned and etched though the second mask to define channel and gate of the TFT. In the meantime, the bottom electrode of the storage capacitor was also formed using the same mask; 3) a 300-nm silicon nitride thin film as the dielectric layer of the storage capacitor was deposited by PECVD; 4) contact holes were

opened by the third mask photolithography and wet chemical etching to expose the gate of the TFT for the interconnect metal; 5) a 500-nm Aluminum layer was sputtered as the interconnect metal as well as the top electrode for the storage capacitor and patterned by the fourth mask photolithography; 6) a 2-µm low-k polyimide dielectric material was spin coated as an isolation layer. A via was opened through the fifth mask and Chromium film was used as the dry etching stop layer; 7) Finally, a 1-µm Aluminum film was deposited by sputtering and defined for the bottom electrode contact of the a-Se layer though the sixth mask.

In the following sub chapters each mask is discussed thoroughly.

#### 5.1 Mask 1

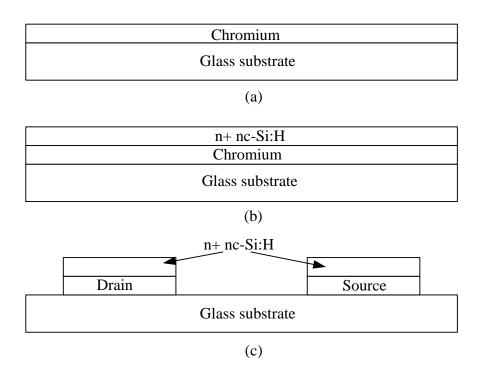

After deposition of a 100-nm Chromium thin film by sputtering followed by a 50-nm heavily doped nanocrystalline thin film (n+ nc-Si:H) deposited by Plasma Enhanced Chemical Vapor Deposition (PECVD), the first mask was used to form the drain and source contacts of the TFTs. n+ nc-Si:H layer was used to decrease the contact resistance between the metal and the a-Si layer. After lithography the n+ nc-Si:H was etched by Reactive Ion Etching (RIE) and the chromium is etched using chromium etchant. These processes are shown in Figure 23.

As it can be seen from Figure 23, mask 1 is used to etch n+ nc-Si:H and Chromium. Before the next step of fabrication (which is the double layer deposition), a few seconds of Buffered HF (BHF) (or 2% HF if exercise extreme care) dip will be required. This etches away the oxide formed on top the n+ nc-Si:H layer. The oxide on top of the n+ nc-Si:H layer increases the contact resistance of the fabricated TFTs resulting in low quality TFTs. This step has to be done with extreme care since HF is a dangerous acid.

Note that drain source contact metals can be a wide variety of metals. Chromium is picked in this case to achieve a higher performance and ease of fabrication. Other metals that can be sputtered in G2N lab at the University of Waterloo are Aluminum and Molybdenum. Figure 24 shows the mask 1 used for this fabrication process.

Figure 23. Chromium deposition (a), n+ nc-Si:H layer deposition (b), using mask 1 and etching Chromium and n+ nc-Si:H layer to form drain and source contacts (c).

Figure 24. Mask 1 used for this fabrication process.

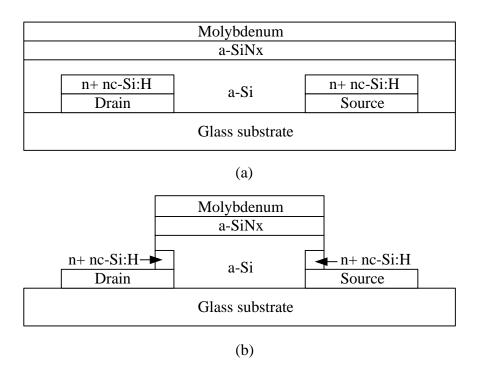

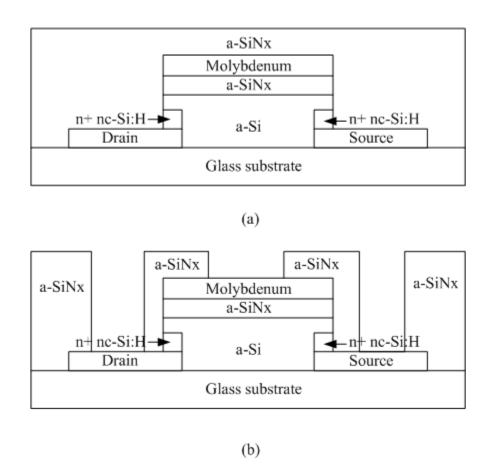

#### 5.2 Mask 2

After deposition of amorphous silicon, silicon nitride (a-SiN<sub>x</sub>), and Molybdenum thin films by PECVD and sputtering consecutively. Mask 2 is used to etch a-Si, a-SiN<sub>x</sub> and Molybdenum. This forms the channel and the gate contact of the TFTs. Moreover, this step patterns the bottom electrode of the pixel capacitor (storage capacitor), if there is any. Etching is done by PAN and RIE for Molybdenum and double layer (a-Si and a-SiN<sub>x</sub>), consecutively.

Figure 25 shows these processes step by step. Note that any other metal can be used for the gate contact. In this fabrication run Molybdenum is used to increase the performance of the TFTs.

Figure 25. a-Si, a-Si $N_x$  and Molybdenum deposition (a), Using mask 2 and etching n+ nc-Si:H a-Si, a-Si $N_x$  and Molybdenum (b).

Figure 26 shows mask 2 used for this fabrication process.

Figure 26. Mask 2 used for this fabrication process.

# 5.3 Mask 3

Then, a 300-nm silicon nitride thin film is deposited by PECVD. This a-SiN $_x$  layer is used as the dielectric for the storage capacitor on the pixel, if there is any. After that contact holes are opened using mask 3, lithography and wet etch. This exposes the gate, source and drain metals for the interconnecting metal. Figure 27 shows these processes step by step. Figure 28 shows mask 3 used for this fabrication process.

Figure 27. a-SiN<sub>x</sub> deposition (a), opening via for interconnecting metal using mask 3 (b).

Figure 28. Mask 3 used for this fabrication process.

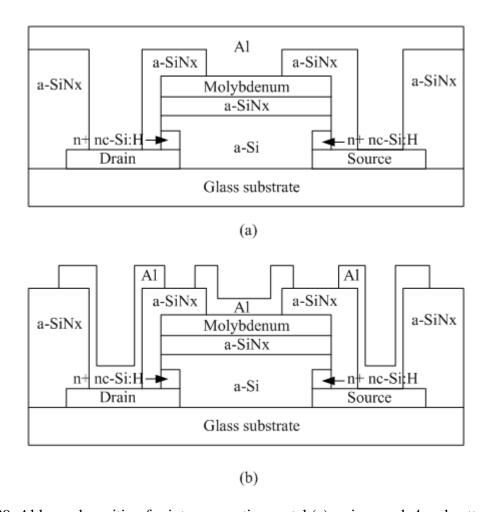

# 5.4 Mask 4

Next a 500-nm Aluminum layer is sputtered as the interconnecting metal. This metal forms the top electrode for the storage capacitor (if there is any) as well. Then, this layer is patterned using mask 4, lithography and PAN etching to etch Aluminum. These fabrication processes are shown in Figure 29 step by step. Figure 30 shows mask 4 used for this fabrication process.

Figure 29. Al layer deposition for interconnecting metal (a), using mask 4 and patterning the interconnecting metal (b).

Figure 30. Mask 4 used for this fabrication process.

# 5.5 Mask 5

Then a 2-µm low-k polyimide dielectric material is spin coated as an isolation layer. After that a via is opened using mask 5. This via exposes the interconnecting metal for the bottom electrode connection of the a-Se layer (detector layer). Note that Chromium film was used as the dry etching stop layer. These fabrication processes are shown in Figure 31 step by step. Figure 32 shows mask 5 used for this fabrication process.

Figure 31. Polyimide coating using spinning (a), etching polyimide using mask 5, lithography and RIE (b).

Figure 32. Mask 5 used for this fabrication process.

# 5.6 Mask 6

Lastly a 1-µm Aluminum film is deposited by sputtering. Then it is patterned using mask 6, lithography and PAN etching. These fabrication processes are shown in Figure 33 step by step. Figure 34 shows mask 6 used for this fabrication process.

Figure 33. Al sputtering for the bottom electrode contact of a-Se (a), Al layer patterning using mask 6 (b).

Figure 34. Mask 6 used for this fabrication process.

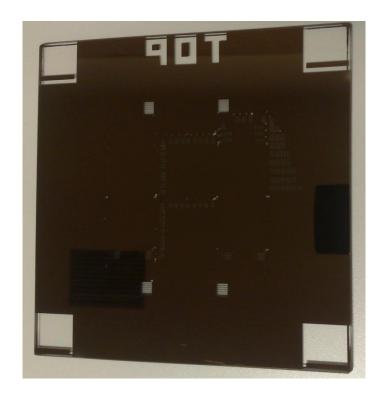

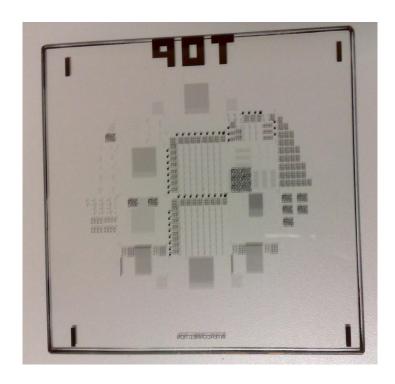

# **5.7 In-House Fabricated Sample**

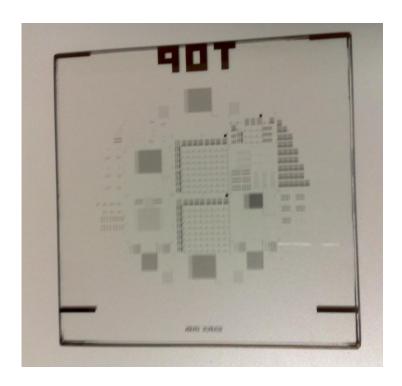

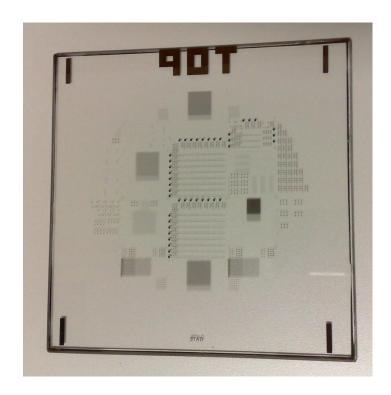

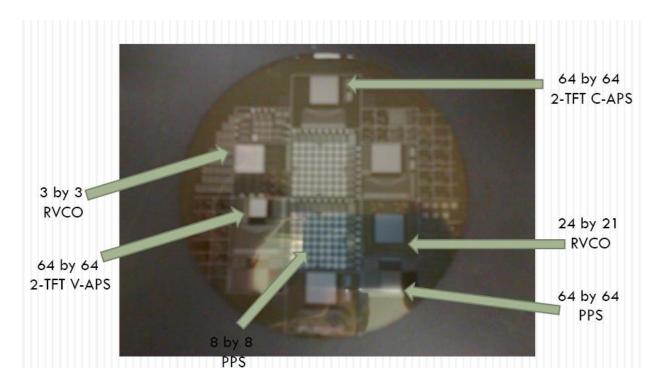

For this process a number of designs are fabricated on the same run. As it can be seen in Figure 35, different structures have been implemented on the same run. Therefore, the layout includes the layout of all of the different designs. Figure 35 shows the final result of the in-house fabricated TFT process.

Figure 35. The in-house fabricated TFT process in University of Waterloo.

# **5.8 Single TFT Results**

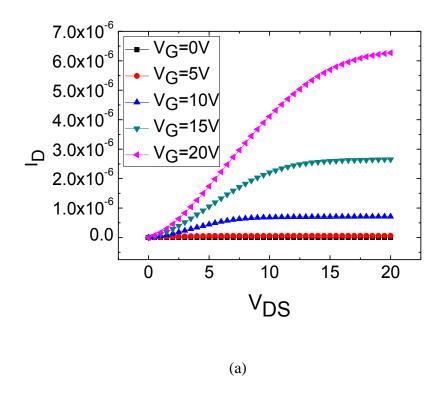

A single TFT characteristics of the in-house fabricated process at the University of Waterloo is shown in Figure 36. From these graphs, the simulation and measurement parameters are extracted, such as mobility of the TFTs, threshold voltage of the TFTs and etc.

Figure 36. Transfer (a), and Output characteristics of single in-house fabricated TFT (W/L= $500\mu m/50 \mu m$ ). This TFT was fabricated in the same run as the RVCO array (b).

# **5.9 Fabrication Conditions**

Table I shows the fabrication conditions for this TFT run.

Table I. Fabrication conditions for in-house fabricated TFT process at the University of Waterloo.