# Power Analysis of Sub-threshold Logics for Security Applications

by

Farhad Haghighizadeh

A thesis

presented to the University of Waterloo in fulfillment of the thesis requirement for the degree of Master of Applied Science

in

**Electrical and Computer Engineering**

Waterloo, Ontario, Canada, 2012

©Farhad Haghighizadeh 2012

### **AUTHOR'S DECLARATION**

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### **Abstract**

Requirements of ultra-low power for many portable devices have drawn increased attention to digital sub-threshold logic design. Major reductions in power consumption and frequency of operation degradation due to the exponential decrease of the drain current in the sub-threshold region has made this logic an excellent choice, particularly for ultra-low power applications where performance is not the primary concern. Examples include RFID, wireless sensor networks and biomedical implantable devices. Along with energy consumption, security is another compelling requirement for these applications. Power analysis attacks, such as Correlation Power Analysis (CPA), are a powerful type of side channel attacks that are capable of performing a non-invasive attack with minimum equipment. As such, they present a serious threat to devices with secret information inside. This research analyzes sub-threshold logics from a previously unexplored perspective, side channel information leakage.

Various transistor level and RTL circuits are implemented in the sub-threshold region as well as in the strong inversion region (normally the standard region of operation) using a 65 nm process. Measures, such as Difference of Mean Energies (DME), Normalized Energy Deviation (NED) and Normalized Standard Deviation (NSD) are employed to evaluate the implemented architectures. A CPA attack is also performed on more complex designs and the obtained correlation coefficients are used to compare sub-threshold and strong inversion logics.

This research demonstrates that sub-threshold does not only increase the security against side channel attacks, but can also decrease the amount of leaked information. This research also shows that a circuit operating at sub-threshold consumes considerably less energy than the same circuit operating in strong inversion and the level of its instantaneous power consumption is significantly lower. Therefore, the noise power required to cover the secret information decreases and the attack may be dramatically more difficult due to major increase in the number of required power traces and run time. Thus, this research is important for identifying sub-threshold as a future viable technology for secure embedded applications.

#### Acknowledgements

I would like to express my most sincere thanks and deepest gratitude to my parents, Zohreh Amini and Hossein Haghighizadeh, for their infinite love and continuous support and dedication. I would never have had the chance to follow my dreams without their support. To them, I owe my entire achievements. I would also like to thank my grandma, Monir Naseri, and my brother, Ali Haghighizadeh, for their unconditional love and inspiration.

I would like to thank my supervisor, Prof. Cathy Gebotys, for her guidance, kind support and encouragement throughout my graduate studies. This thesis would have not been possible without her help and support.

My thanks and appreciation also go to Dr. Amir Khatibzadeh for his invaluable help throughout this research.

As well, I am grateful to the administrative and technical staff of the University of Waterloo, especially Phil Regier, for his assistance with the tools.

Additionally, I would like to thank my colleagues in the Laboratory for Side Channel Security of Embedded Systems at the University of Waterloo, including Dr. Marcio Juliato, Dr. Edgar Mateos Santillan, Masoumeh Dadjou and Dr. Patrick Longa for their friendship and encouragement.

Last but not least, I wish like to thank all of my dear friends, Alborz Rezazadeh, Rozhin Yousefi, Mohammadreza Fakhari Moghaddam Arani and Sasan Taghizadeh who enriched my life beyond my studies. I have been lucky to have such good friends by my side.

### To my parents

for their unconditional love, support and encouragement

### **Table of Contents**

| AUTHOR'S DECLARATION                                                    | ii  |

|-------------------------------------------------------------------------|-----|

| Abstract                                                                | iii |

| Acknowledgements                                                        | iv  |

| Dedication                                                              | v   |

| Table of Contents                                                       | vi  |

| List of Figures                                                         | ix  |

| List of Tables                                                          | xii |

| Chapter 1 Introduction                                                  | 1   |

| 1.1 Objectives and Motivations                                          | 1   |

| 1.2 Thesis Overview                                                     | 2   |

| Chapter 2 Background and Previous Research                              | 3   |

| 2.1 Digital Sub-threshold Logic                                         | 3   |

| 2.1.1 MOS Transistor Model for Sub-threshold Operation                  | 4   |

| 2.1.2 MOS Power Model for Sub-threshold Operation                       | 8   |

| 2.2 Side Channel Analysis Attacks                                       | 9   |

| 2.2.1 Overview of Simple Power Analysis and Differential Power Analysis | 10  |

| 2.2.2 Correlation Power Analysis                                        | 10  |

| 2.2.3 Measures for Side Channel information leakage                     | 12  |

| 2.2.4 Side Channel Resistant Logics                                     | 13  |

| 2.3 Previous Side Channel Research of Sub-threshold Circuits            | 17  |

| Chapter 3 Sub-threshold Circuits and Design Methodology                 | 19  |

| 3.1 Design Challenges at Sub-threshold                                  | 19  |

| 3.2 Transistor Level Design                                             | 20  |

| 3.2.1 Inverter Operation in Sub-threshold Region                        | 21  |

| 3.2.2 NAND Gate Operation in Sub-threshold Region                       | 24  |

| 3.2.3 NOR Gate Operation in Sub-threshold Region                        | 25  |

| 3.2.4 XOR Gate Operation in Sub-threshold Region.                       | 25  |

|    | 3.2.5 Parallel XORs                                                           | 26 |

|----|-------------------------------------------------------------------------------|----|

|    | 3.3 RTL Design                                                                | 27 |

|    | 3.3.1 Sub-threshold Digital Design Flow                                       | 27 |

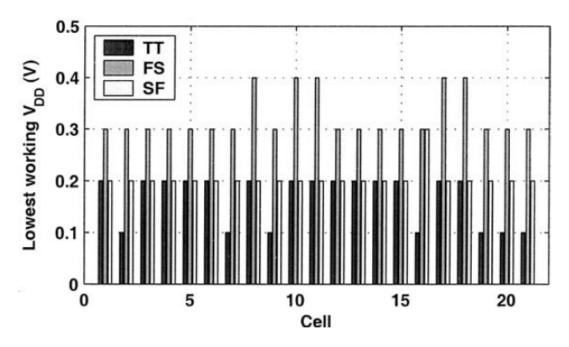

|    | 3.3.2 Standard Cell Library Performance in Sub-threshold                      | 31 |

|    | 3.3.3 AES Crypto-Processor                                                    | 32 |

|    | 3.3.4 S-Box Block                                                             | 34 |

| Cl | hapter 4 Side Channel Information Leakage Measurements and Analysis           | 35 |

|    | 4.1 Difference of Mean Energies (DME)                                         | 35 |

|    | 4.2 Frequency of Observation                                                  | 37 |

|    | 4.3 Normalized Energy Deviation (NED) and Normalized Standard Deviation (NSD) | 39 |

|    | 4.4 Correlation Power Analysis (CPA)                                          | 41 |

|    | 4.4.1 Power Consumption Matrix Acquiring                                      | 41 |

|    | 4.4.2 Predicted Power Consumption Matrix Generation                           | 42 |

|    | 4.4.3 Correlation Matrix Generation                                           | 43 |

| Cl | hapter 5 Simulation Results                                                   | 46 |

|    | 5.1 XOR Gate Analysis with DME Measure                                        | 46 |

|    | 5.1.1 Power Waveforms at Sub-threshold and Strong Inversion                   | 46 |

|    | 5.1.2 DME Signals for Fixed Keys                                              | 54 |

|    | 5.1.3 DME Signal for Fixed Data Transitions                                   | 56 |

|    | 5.2 Parallel XORs Architecture Analysis with DME Measure                      | 58 |

|    | 5.3 NAND, NOR and XOR Gates Analysis with Frequency of Observation Measure    | 59 |

|    | 5.3.1 NAND Gate                                                               | 60 |

|    | 5.3.2 NOR Gate                                                                | 62 |

|    | 5.3.3 XOR Gate                                                                | 65 |

|    | 5.4 NAND, NOR and XOR Gates Analysis with NED and NSD Measures                | 67 |

|    | 5.5 Parallel XORs Architecture Analysis with CPA Measure                      | 67 |

|    | 5.6 Correlation Power Analysis Attack                                         | 72 |

|    | 5.6.1 S-Box Analysis with CPA Measure                                         | 73 |

|    | 5.6.2 AES Analysis with CPA Measure                                           | 74 |

| Chapter 6 Conclusions and Future Works                              | 76 |

|---------------------------------------------------------------------|----|

| 6.1 Summary and Discussion                                          | 76 |

| 6.2 Conclusions and Future Works                                    | 77 |

| Appendix A Encounter Library Characterizer's Issues                 | 79 |

| Appendix B MATLAB Code for Correlation Power Analysis Attack on AES | 80 |

| Bibliography                                                        | 84 |

## **List of Figures**

| 1    | Figure 2.1: Normalized energy per operation and normalized delay of a digital circuit as a func        | tion |

|------|--------------------------------------------------------------------------------------------------------|------|

| of V | /DD [1]                                                                                                | 4    |

| 1    | Figure 2.2: Cross section view and symbol of an n-channel MOS transistor                               | 5    |

| 1    | Figure 2.3: Modes of operation of a MOS transistor                                                     | 5    |

| ]    | Figure 2.4: $I_D$ versus $V_{GS}$ for a MOS transistor in 0.18µm process with nominal $V_{DD}$ of 1.8V | 7    |

| 1    | Figure 2.5: $I_D$ versus $V_{DS}$ for three values of $V_{GS}$ in a 0.18 $\mu$ m process               | 8    |

| 1    | Figure 2.6: Output transitions in a static complementary CMOS logic                                    | 13   |

| 1    | Figure 2.7: Power characteristics of Differential and Dynamic logics in the form of truth table        | 14   |

| ]    | Figure 2.8: Generic n-gate SABL logic                                                                  | 15   |

| I    | Figure 2.10: WDDL NAND, NOR and XOR gates                                                              | 16   |

| 1    | Figure 2.11: WDDL pre-charge circuit                                                                   | 17   |

| 1    | Figure 2.12: Analysis of a secure circuit resistivity toward power analysis attacks                    | 18   |

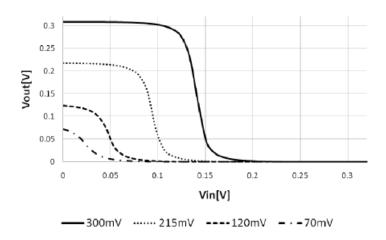

| I    | Figure 3.1: VTC as a function of supply voltage                                                        | 20   |

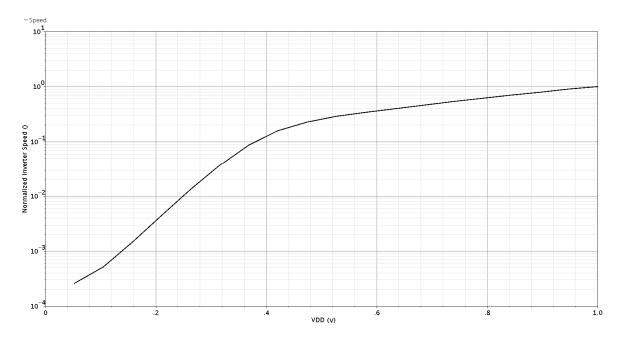

| 1    | Figure 3.3: Normalized inverter speed versus supply voltage                                            | 22   |

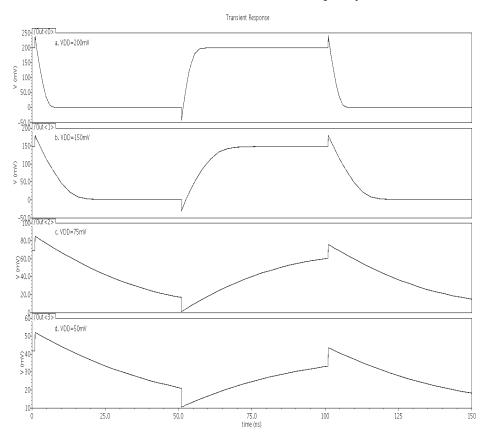

| ]    | Figure 3.4: Inverter output at the frequency of 10 MHz and various supply                              | 23   |

| 1    | Figure 3.5: Inverter output for the supply voltage of 150 mV and various frequencies                   | 24   |

| 1    | Figure 3.6: Static CMOS XOR architecture.                                                              | 26   |

| ]    | Figure 3.7: Parallel XORs architecture.                                                                | 26   |

| 1    | Figure 3.8: Sub-threshold RTL design flow.                                                             | 28   |

| ]    | Figure 3.9: Standard cell functionality in synthesized FIR filter                                      | 32   |

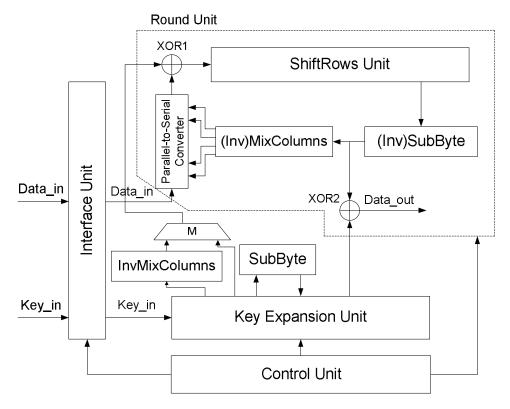

| 1    | Figure 3.10: High-level architecture of the AES crypto-processor.                                      | 33   |

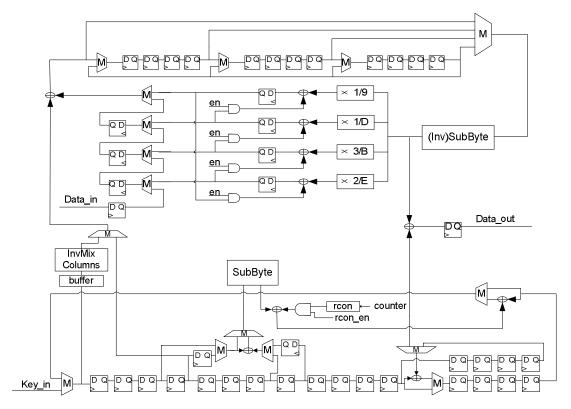

| 1    | Figure 3.11: AES core data path.                                                                       | 34   |

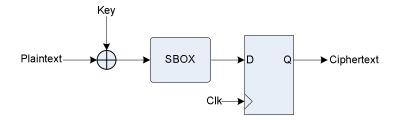

| ]    | Figure 3.12: S-Box test architecture for attack.                                                       | 34   |

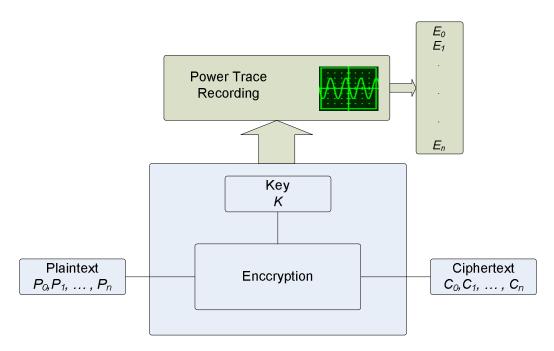

| 1    | Figure 4.1: Crypto-system with fixed key and <i>n</i> different plaintexts                             | 36   |

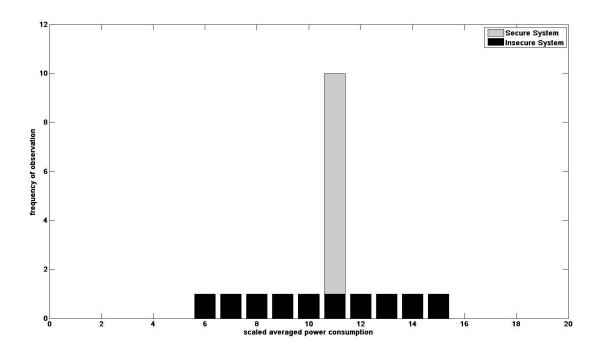

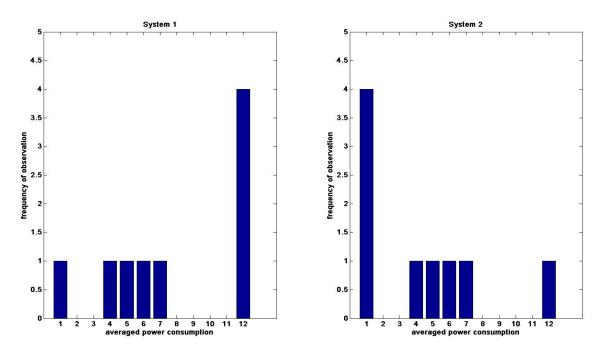

| 1    | Figure 4.2: Frequency of observation, secure system vs. insecure system.                               | 38   |

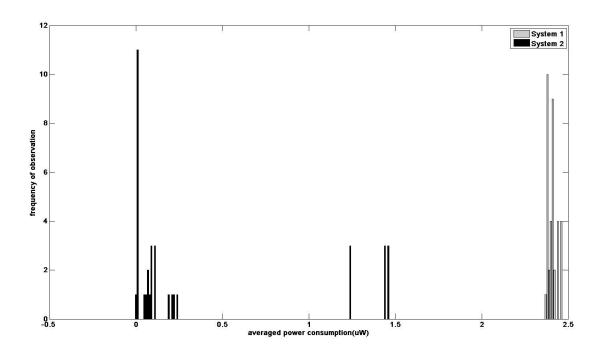

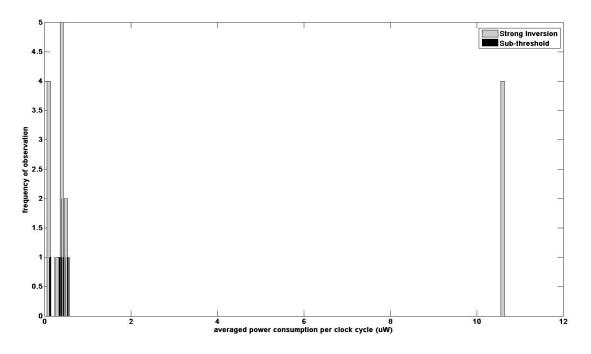

| 1    | Figure 4.3: Comparison between frequencies of observation of two real systems.                         | 38   |

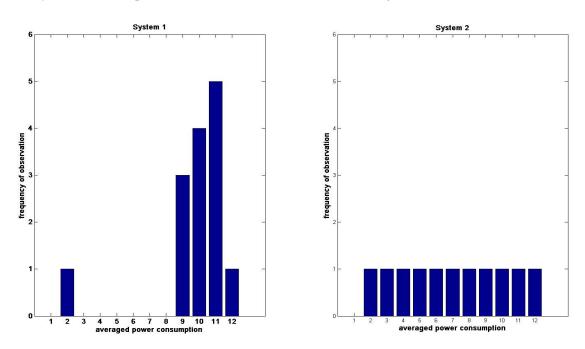

| I    | Figure 4.4: Systems with same NED value but different levels of security                               | 39   |

| 1    | Figure 4.5: Systems with same level of security but different values of NSD                            | 40   |

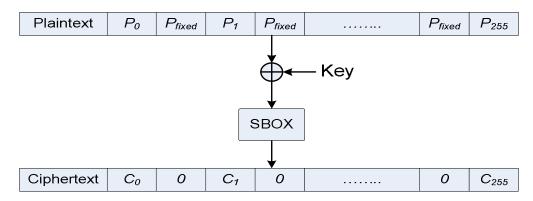

| I    | Figure 4.6: S-Box testbench for generating power traces                                                | 41   |

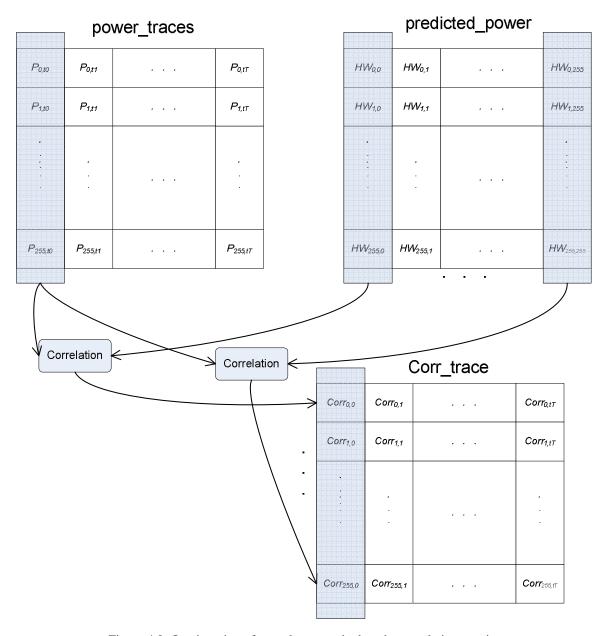

| I    | Figure 4.7: Power traces matrix generated from simulation.                                             | 42   |

| 1    | Figure 4.8: One iteration of outer loop to calculate the correlation matrix.                           | 44   |

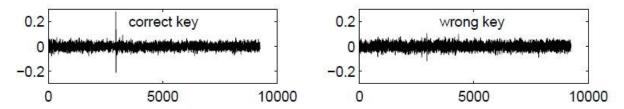

| 1    | Figure 4.9: Correlation traces for correct key and an example of a wrong key in a CPA attack of        | on a |

| DE:  | S operation                                                                                            | 45   |

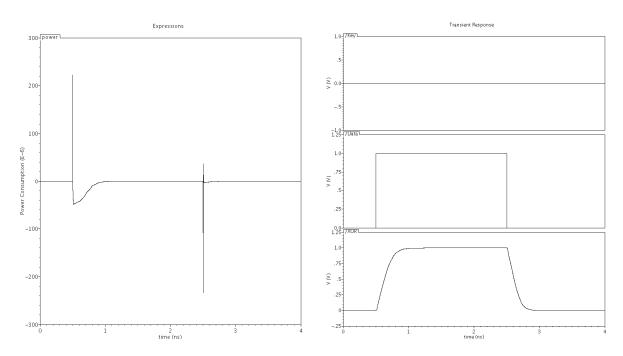

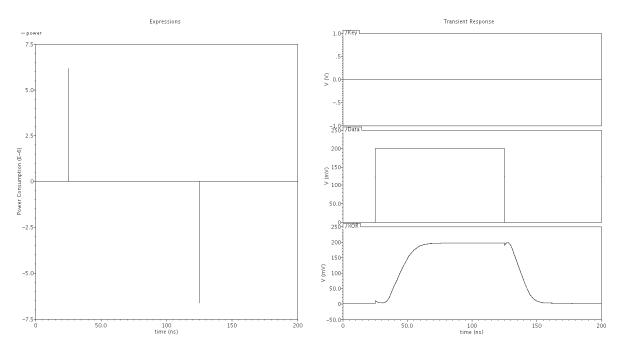

|      | Figure 5.1: Strong inversion power waveform for XOR circuit, with plots of key, input data             |      |

|      | put data for $Key=0$ and $Data=0->1->0$ .                                                              |      |

| 1    | Figure 5.2: Strong inversion power waveform for XOR circuit, with plots of key, input data             | and  |

|      | put data for Key=0 and Data=1->0->1.                                                                   |      |

|      | Figure 5.3: Strong inversion power waveform for XOR circuit, with plots of key, input data             |      |

| outp | put data for $Key=1$ and $Data=0->1->0$ .                                                              | 48   |

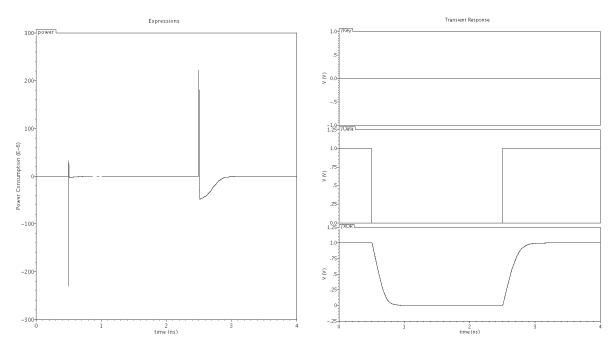

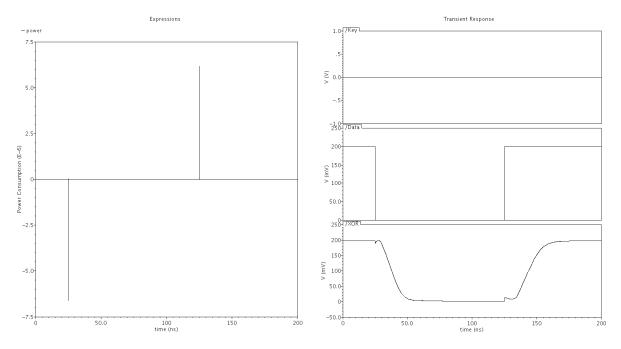

| Figure 5.4: Strong inversion power waveform for XOR circuit, with plots of key, input data and            |

|-----------------------------------------------------------------------------------------------------------|

| output data for $Key=1$ and $Data=1->0->1$                                                                |

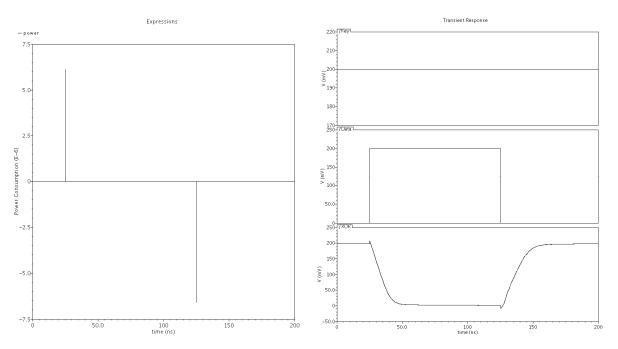

| Figure 5.5: Sub-threshold power waveform for XOR circuit, with plots of key, input data and               |

| output data for $Key=0$ and $Data=0->1->0$                                                                |

| Figure 5.6: Sub-threshold power waveform for XOR circuit, with plots of key, input data and               |

| output data for Key=0 and Data=1->0->150                                                                  |

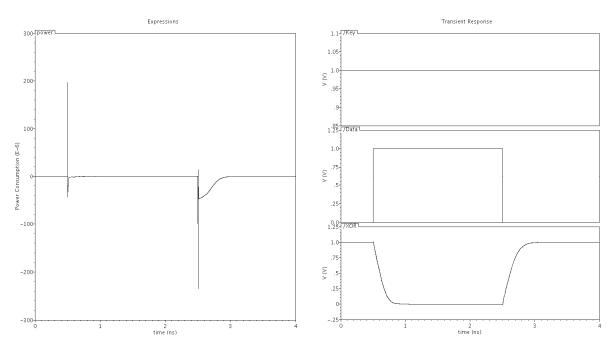

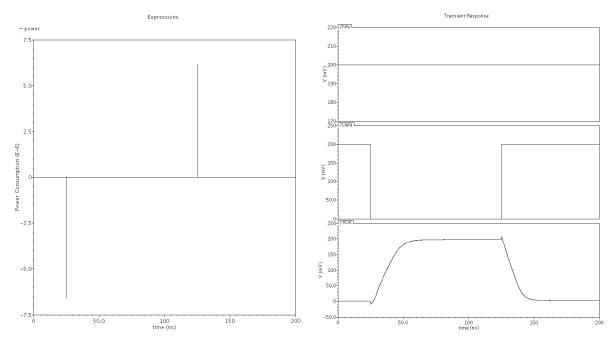

| Figure 5.7: Sub-threshold power waveform for XOR circuit, with plots of key, input data and               |

| output data for Key=1 and Data=0->1->050                                                                  |

| Figure 5.8: Sub-threshold power waveform for XOR circuit, with plots of key, input data and               |

| output data for $Key=1$ and $Data=1->0->1$                                                                |

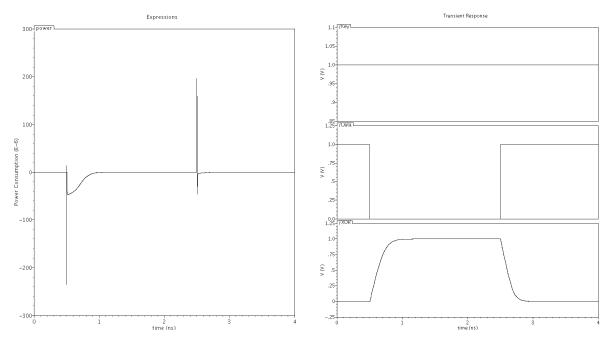

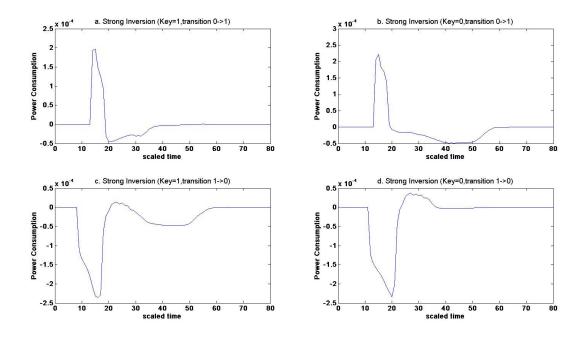

| Figure 5.9: A Closer look at power spikes for strong inversion for a) key=1, 0-1 transition by            |

| key=0, 0-1 transition c) $key=1$ , 1-0 transition d) $key=0$ , 1-0 transition                             |

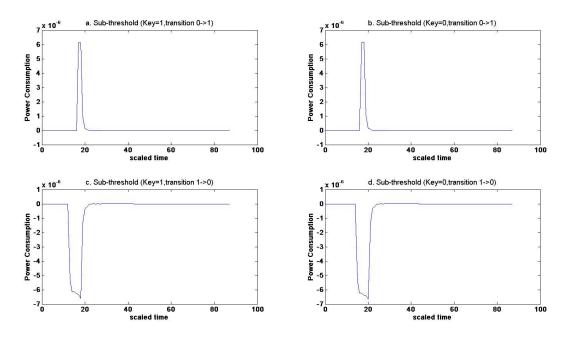

| Figure 5.10: A Closer look at power spikes for sub-threshold for a) $key=1$ , 0-1 transition b) $key=0$ , |

| 0-1 transition c) $key=1$ , 1-0 transition d) $key=0$ , 1-0 transition                                    |

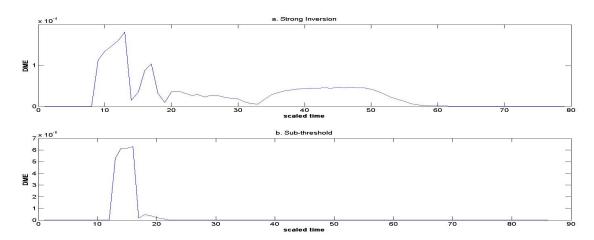

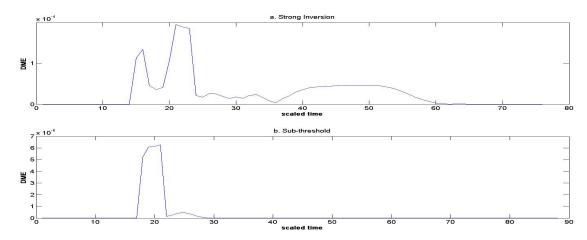

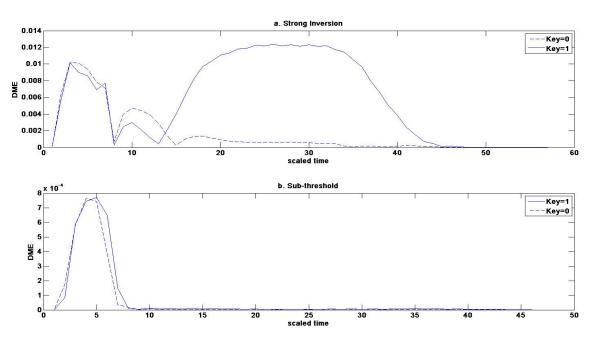

| Figure 5.11: DME0 signals for Key=0 and Data=0->1->0 for both strong Inversion and sub-                   |

| threshold54                                                                                               |

| Figure 5.12: DME0 signals for $Key=0$ and $Data=1->0->1$ for both strong Inversion and sub-               |

| threshold                                                                                                 |

| Figure 5.13: DME1 signals for $Key=1$ and $Data=0->1->0$ for both strong Inversion and sub-               |

| threshold                                                                                                 |

| Figure 5.14: DME1 signals for $Key=1$ and $Data=1->0->1$ for both strong Inversion and sub-               |

| threshold                                                                                                 |

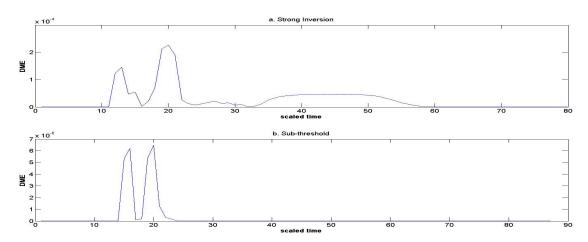

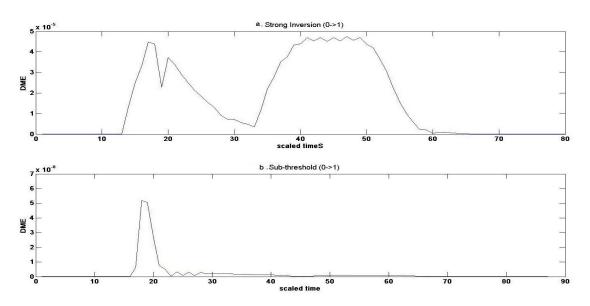

| Figure 5.15: DME signals for $Data = 0 \rightarrow 1$ for both Strong Inversion and Sub-threshold57       |

| Figure 5.16: DME signals for $Data = 1 \rightarrow 0$ for both Strong Inversion and Sub-threshold57       |

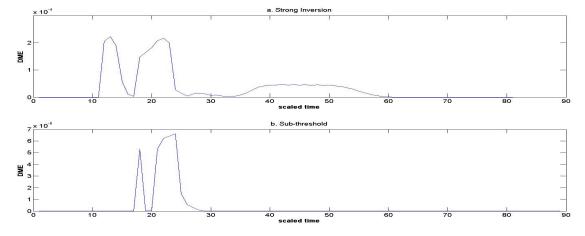

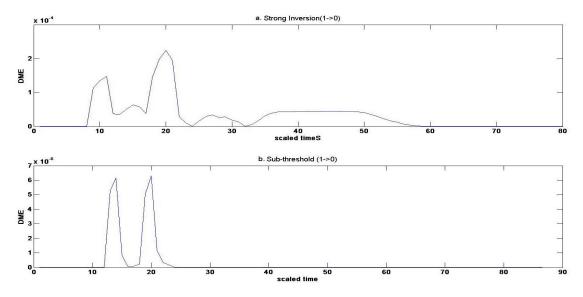

| Figure 5.17: DME signals for parallel XORs architecture for both Strong Inversion and Sub-                |

| threshold                                                                                                 |

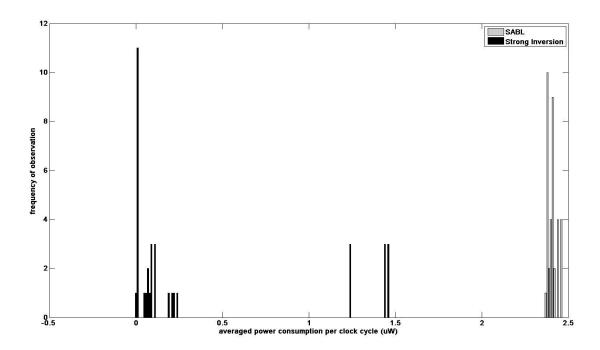

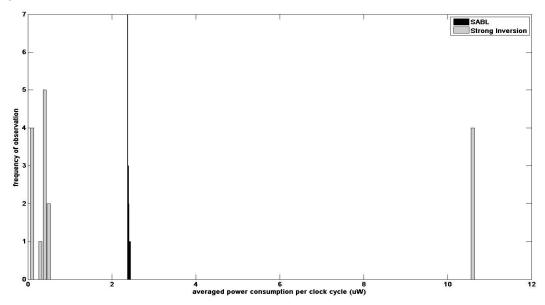

| Figure 5.18: SABL vs. strong inversion for the number of observed energies per cycle (NAND). 60           |

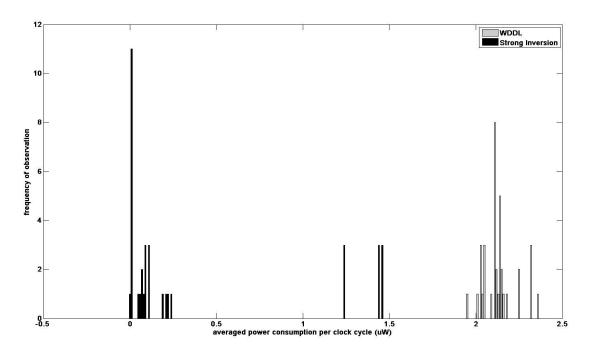

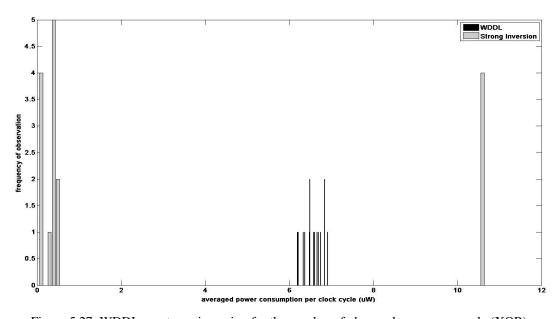

| Figure 5.19: WDDL vs. strong inversion for the number of observed energy per cycle (NAND). 61             |

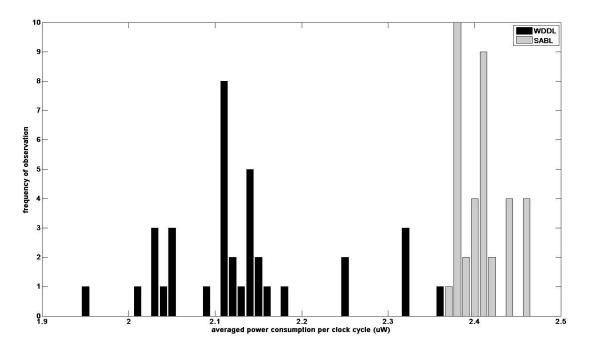

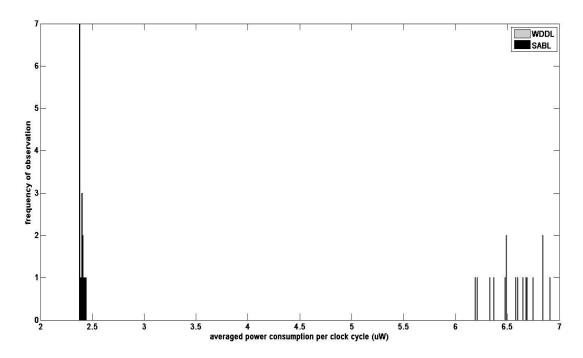

| Figure 5.20: SABL vs. WDDL for the number of observed energy per cycle (NAND)61                           |

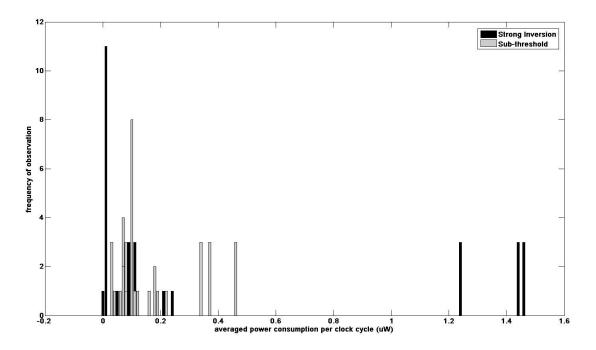

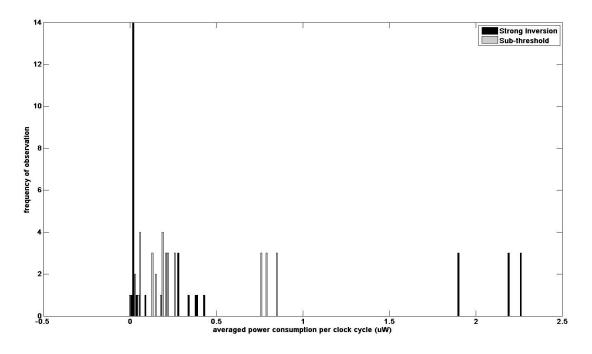

| Figure 5.21: Strong inversion vs. sub-threshold for the number of observed energy per cycle               |

| (NAND)                                                                                                    |

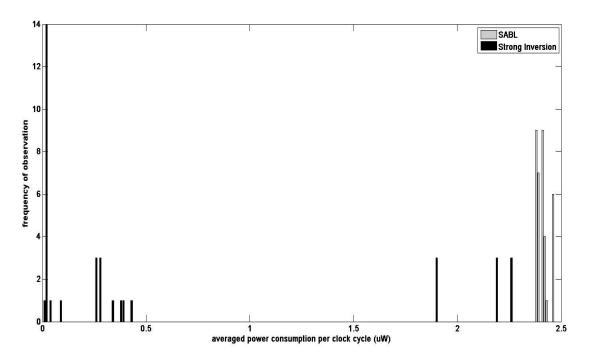

| Figure 5.22: SABL vs. strong inversion for the number of observed energy per cycle (NOR)63                |

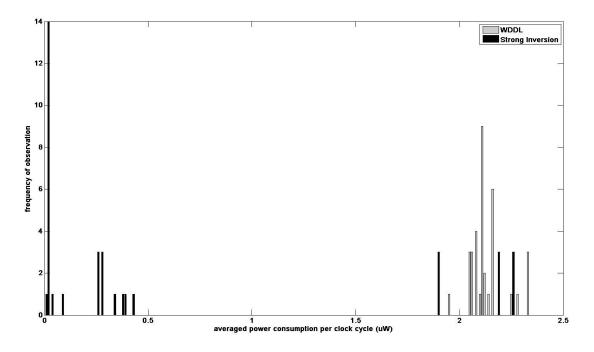

| Figure 5.23: WDDL vs. strong inversion for the number of observed energy per cycle (NOR)63                |

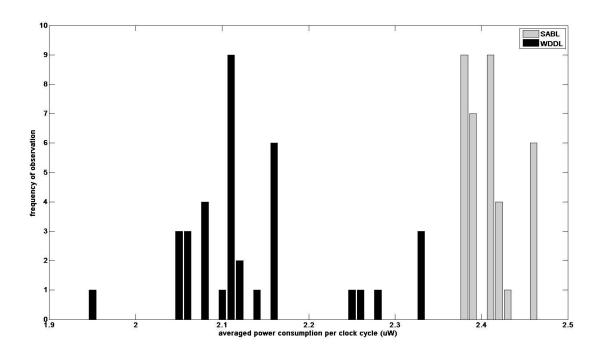

| Figure 5.24: SABL vs. WDDL for the number of observed energy per cycle (NOR)64                            |

| Figure 5.25: Strong inversion vs. sub-threshold for the number of observed energy per cycle               |

| (NOR)64                                                                                                   |

| Figure 5.26: SABL vs. strong inversion for the number of observed energy per cycle (XOR)65                |

| Figure 5.27: WDDL vs. strong inversion for the number of observed energy per cycle (XOR)65                |

| Figure 5.28: SABL vs. WDDL for the number of observed energy per cycle (XOR)66                            |

| Figure 5.29: Strong inversion vs. sub-threshold for the number of observed energy per cycle               |

| (XOR)66                                                                                                   |

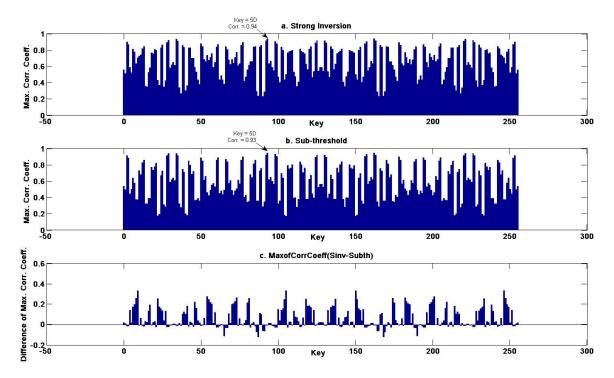

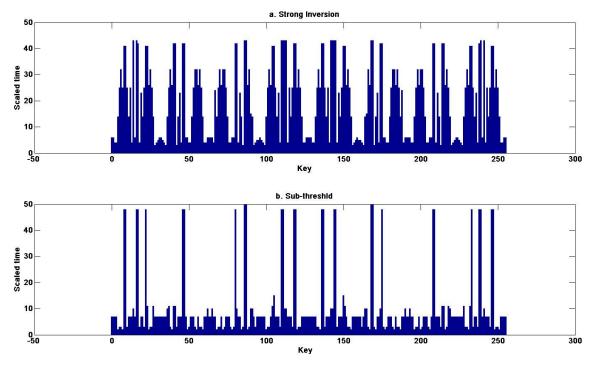

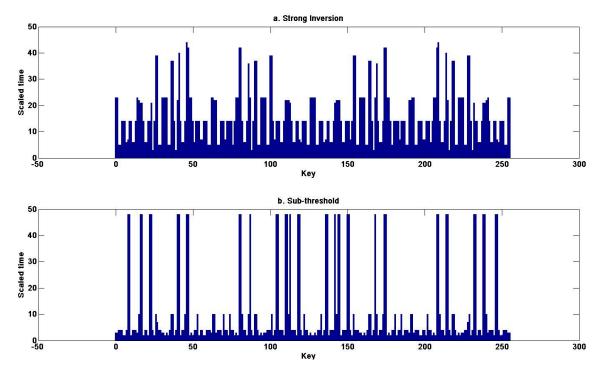

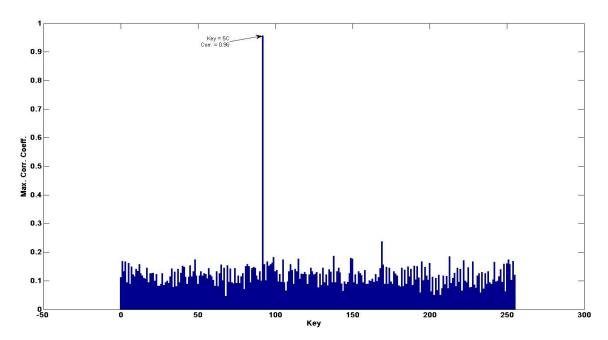

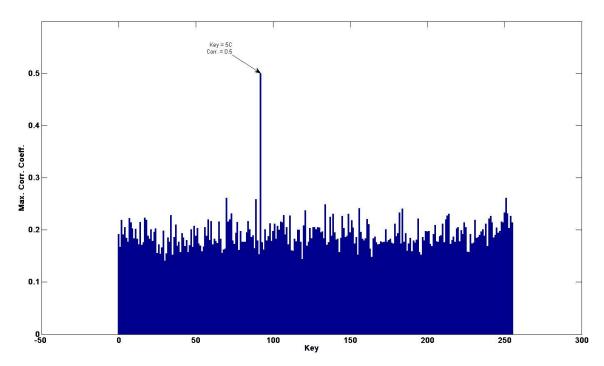

| Figure 5.30: Maximum Correlation Coefficients for <i>correct key</i> = $5D$ , for strong | Inversion, sub- |

|------------------------------------------------------------------------------------------|-----------------|

| threshold and the difference of strong inversion and sub-threshold                       | 68              |

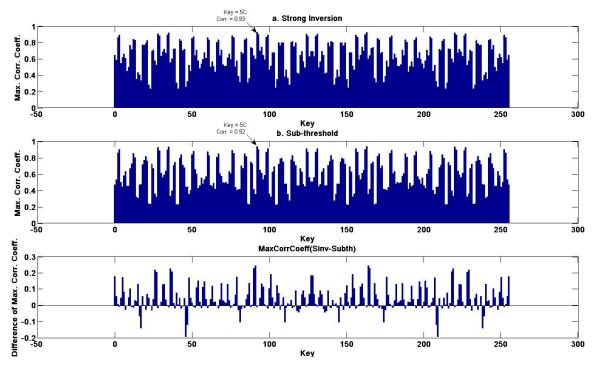

| Figure 5.31: Maximum Correlation Coefficients for correct key = 5C, for strong           | Inversion sub-  |

| threshold and the difference of strong inversion and sub-threshold                       | 69              |

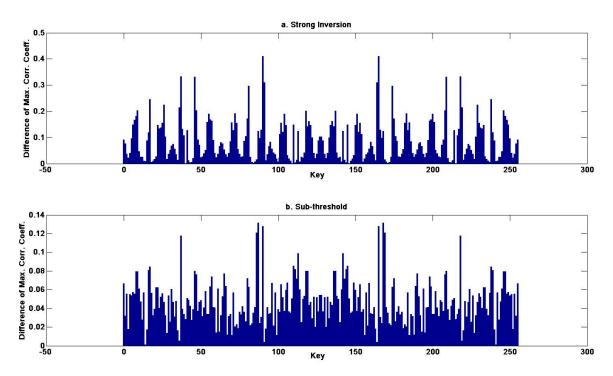

| Figure 5.32: Difference of Max_Corr_Coeff traces for Key=5C and Key=5D,                  | for both strong |

| Inversion and sub-threshold.                                                             | 70              |

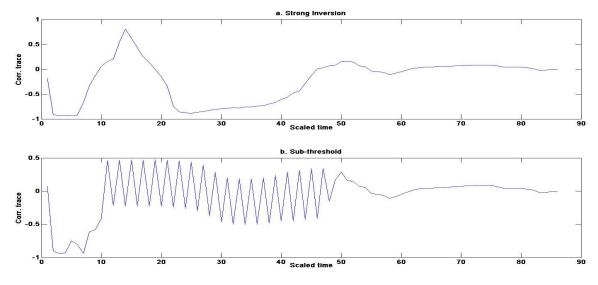

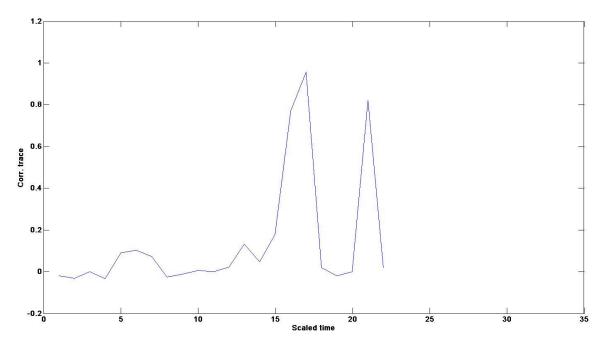

| Figure 5.33: Correlation coefficient traces corresponding to the correct key, 5D,        | for both strong |

| Inversion and sub-threshold.                                                             | 70              |

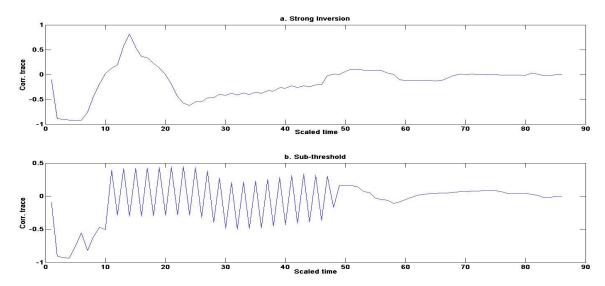

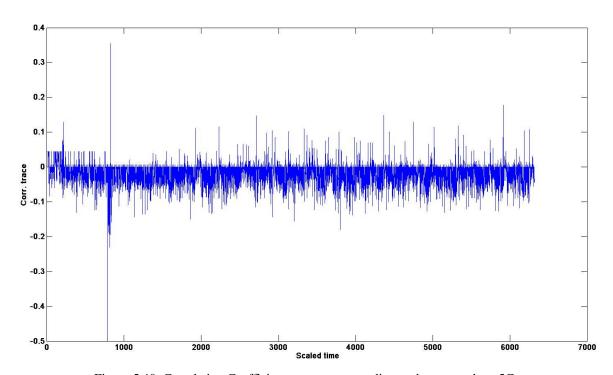

| Figure 5.34: Correlation coefficient traces corresponding to the correct key, 5C,        | for both strong |

| Inversion and sub-threshold.                                                             | 71              |

| Figure 5.35: Time of occurring correlation for each key guess and correct key            | of 5D, for both |

| strong Inversion and sub-threshold.                                                      | 71              |

| Figure 5.36: Time of occurring correlation for each key guess and correct key            | of 5C, for both |

| strong Inversion and sub-threshold.                                                      | 72              |

| Figure 5.37: Maximum Correlation Coefficients for <i>correct key</i> = 5C                |                 |

| Figure 5.38: Correlation coefficient trace corresponding to the correct key, 5C          | 74              |

| Figure 5.39: Maximum Correlation Coefficients for <i>correct key</i> = 5C                | 75              |

| Figure 5.40: Correlation Coefficient trace corresponding to the correct key, 5C          | 75              |

### **List of Tables**

| Table 3.1: Characteristics of a static CMOS NAND gate in sub-threshold.25Table 3.2: Characteristics of a static CMOS NOR gate in sub-threshold.25Table 3.3: Characteristics of a static CMOS XOR gate in sub-threshold.25Table 5.1: Averaged power values for strong inversion.53Table 5.2: Averaged power values for sub-threshold.53Table 5.3: PeakRatio for strong inversion and sub-threshold in various cases.56Table 5.4: Testbench.59Table 5.5: NED and NSD values for NAND, NOR and XOR gates.67 | Table 2.1: Summary of characteristics for side channel resistant logics             | 13 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|----|

| Table 3.3: Characteristics of a static CMOS XOR gate in sub-threshold.25Table 5.1: Averaged power values for strong inversion.53Table 5.2: Averaged power values for sub-threshold.53Table 5.3: PeakRatio for strong inversion and sub-threshold in various cases.56Table 5.4: Testbench.59                                                                                                                                                                                                              | Table 3.1: Characteristics of a static CMOS NAND gate in sub-threshold              | 25 |

| Table 5.1: Averaged power values for strong inversion53Table 5.2: Averaged power values for sub-threshold53Table 5.3: PeakRatio for strong inversion and sub-threshold in various cases56Table 5.4: Testbench59                                                                                                                                                                                                                                                                                          | Table 3.2: Characteristics of a static CMOS NOR gate in sub-threshold               | 25 |

| Table 5.2: Averaged power values for sub-threshold53Table 5.3: PeakRatio for strong inversion and sub-threshold in various cases56Table 5.4: Testbench59                                                                                                                                                                                                                                                                                                                                                 | Table 3.3: Characteristics of a static CMOS XOR gate in sub-threshold               | 25 |

| Table 5.3: <i>PeakRatio</i> for strong inversion and sub-threshold in various cases                                                                                                                                                                                                                                                                                                                                                                                                                      | Table 5.1: Averaged power values for strong inversion                               | 53 |

| Table 5.4: Testbench                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Table 5.2: Averaged power values for sub-threshold                                  | 53 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Table 5.3: <i>PeakRatio</i> for strong inversion and sub-threshold in various cases | 56 |

| Table 5.5: NED and NSD values for NAND, NOR and XOR gates                                                                                                                                                                                                                                                                                                                                                                                                                                                | Table 5.4: Testbench                                                                | 59 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Table 5.5: NED and NSD values for NAND, NOR and XOR gates                           | 67 |

## Chapter 1 Introduction

#### 1.1 Objectives and Motivations

In the mid 1990's, power consumption limitations, especially for portable devices commenced a new era in sub-threshold circuit design. Specifically, all the transistors in a sub-threshold circuit operate in sub-threshold region. Applying a power supply voltage less than the threshold voltage of the MOS transistor ensures this functionality. The drain current of an MOS transistors illustrate an exponential dependence on the gate voltage in the sub-threshold region in contrast to the linear/quadratic dependency in the standard region of operation, also known as strong inversion.

This exponential decrease of drain current with the gate voltage causes a major reduction in power consumption; however, it also degrades the frequency of operation. Therefore, sub-threshold logics are an excellent choice for ultra-low power applications where performance is not the primary concern. Despite the research efforts into sub-threshold circuits, sub-threshold chips have not yet been commercially available [1]. Some recent commercial chips utilize near-threshold circuitry [2] but sub-threshold design and chips remain in academic and industrial labs. Some examples of research applications of sub-threshold include RFID[3], wireless sensor networks, biomedical implantable devices[4], and others [5][6][7]. Clearly security is an important aspect in these applications, yet limited research has been done in this area.

Side channel analysis attacks utilizing the power measurement of circuits were published in 1999 [8]. These attacks exploit the secret information of cryptographic devices by observing physical characteristics of the device, such as power consumption [8], electromagnetic radiation [9] and run time [10]. Power analysis attacks such as differential power analysis (DPA) and correlation power analysis (CPA) are an important type of side channel analysis attack. Instantaneous power consumption of a cryptographic device is recorded during its operation and subsequent analysis may reveal the secret information by exploiting the dependency of power consumption on the handled data within the device. In general the attacker does not need to know detailed information about the implementation of the cryptographic device in order to launch the attack. Hence, their capability to perform a non-invasive attack with minimum equipment and implementation knowledge has made them a serious threat for cryptographic devices.

Security is a compelling requirement for most applications in which sub-threshold operation is necessary. A crypto-processor is a common component in many devices. Thus it is important to secure the secret key of crypto-processors against power analysis attacks, especially DPA and CPA attacks. However, side channel analysis of this logic scheme is generally an unexplored aspect. Previous research has either not launched a CPA on sub-threshold or focused on only a smaller sub-circuit of a standardized cipher, known as AES [11].

The ultimate objective of this thesis is to study the estimated power analysis of a sub-threshold circuit. However, other side channel information leakage measures, such as difference of mean energies (DME), frequency of observation, normalized energy deviation (NED) and normalized standard deviation (NSD) are also used for comparison purposes. Simple architectures are

implemented at the transistor level and an AES core is implemented at the register transfer level. An application-specific integrated circuits (ASIC) design methodology for sub-threshold design is used to implement and study such architectures. Preliminary simulations demonstrate the reduction of power consumption correlation with input data by lowering the supply voltage. In light of the above mentioned concerns, motivations and desirable preliminary results, a detailed study on the power analysis of sub-threshold logics is performed.

In the first step, a power consumption analysis of an exclusive-or (XOR) gate is performed using DME measure to provide insight into the side channel information behavior in the sub-threshold region. Further investigation on basic gates is performed by analyzing averaged power consumption of NAND, NOR and XOR gates in various transitions by means of frequency of observation, NED and NSD measures. A final architecture designed at the transistor level, named parallel XORs is analyzed with DME and CPA measures. Afterward, measurements move to a more complex architecture, an important component of AES, the S-Box, and a crypto-AES processor. Correlation power analysis is performed on power consumption traces obtained from electronic design automation (EDA) tools. The challenges involved in a register transfer level (RTL) design for a sub-threshold operation are also described.

There is no default judgment about the side channel security of circuits operating at sub-threshold in this thesis. Moreover the purpose is not to prove that sub-threshold logic is either more secure or less secure, but to study the side channel information leakage in that region and compare it to strong inversion as the standard region of operation.

#### 1.2 Thesis Overview

The thesis is organized as follows. Chapter 2 presents a literature survey on sub-threshold logics, side channel attacks and side channel resistant logics followed by an overview of previous research proposed on side channel analysis of sub-threshold logics. Methodologies used for sub-threshold circuits design is described in Chapter 3 which starts with an explanation of transistor level design and continues with details of RTL level design and digital ASIC design flow for sub-threshold. Chapter 4 introduces power analysis metrics used to evaluate the architectures proposed in Chapter 3. Simulation results and information leakage comparisons between strong inversion, sub-threshold and two side channel resistant logics is presented in Chapter 5. Finally, Chapter 6 summarizes and concludes the thesis and provides recommendations for future work.

## Chapter 2 Background and Previous Research

The main components of this research are digital sub-threshold logic and side channel analysis. In this chapter, background information required to understand later chapters is described. The first section explains the behavior of a transistor operating in a sub-threshold region and introduces current and power models of a transistor at sub-threshold. Side channel analysis attacks are explained in section 2.2, which begins with a brief review of simple power analysis and differential power analysis. The section continues with a correlation power analysis introduction and ends with a discussion on side channel analysis measures and proposed side channel resistant logics. Previous research work accomplished in the area of side channel analysis of sub-threshold circuits is investigated in the final section of this chapter.

#### 2.1 Digital Sub-threshold Logic

In the mid 1960's, microwatt power consumption limitations of electronic watches drew attention to an unexplored aspect of newly proposed CMOS technology- the sub-threshold current. In 1972, Barron [12] presented a model that showed the exponential dependent of the sub-threshold current on the surface voltage, but did not propose any simple relationship with the gate voltage [13]. In the same year, Swanson and Meindl [14] explained the relationship between surface voltage and gate voltage. They applied their model to find the transfer characteristic of a CMOS inverter in weak inversion and for the first time showed that CMOS logic circuits can operate at a supply voltage as low as 8kT/q [13].

Despite all of the research undertaken since the mid 1960's, the application of sub-threshold circuits was completely ignored until the mid 1990's, when power consumption limitations especially for portable devices initiated a new era in sub-threshold circuit design.

A sub-threshold circuit is defined as a circuit in which all of the transistors operate in the sub-threshold region. Applying a power supply voltage less than the threshold of the MOS transistor ensures this functionality. Nowadays, sub-threshold CMOS logic has made its way into applications for which energy consumption is the key-metrics. The exponential relationship between the drain current and the gate to source voltage of an MOS transistor in the sub-threshold region gives an exponential reduction in power consumption, but also exponentially increases the delay [15].

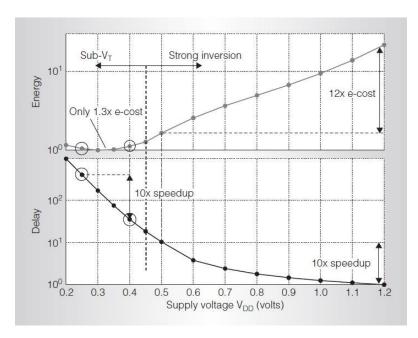

Several research projects have tried to find the minimum energy point at which the energy consumption of a circuit is less than any other point of the parameter space [16-20]. Calhoun shows in [17] that the minimum energy operation occurs in the sub-threshold region and [19] proposes an analytical solution to find the optimum power supply voltage,  $V_{DD}$ , and threshold voltage,  $V_T$ , to minimize energy for a given frequency in the sub-threshold region. Figure 2.1 shows the energy per operation and delay as a function of  $V_{DD}$ . The minimum energy point, quadratic decrease in energy

and exponential increase in delay can be observed in this figure. Choosing the operating point in a circuit is a trade-off between energy and delay that can also be observed in Figure 2.1. One can see that sub-threshold circuits minimize energy consumption at a cost of slower speed.

Figure 2.1: Normalized energy per operation (top) and normalized delay (bottom) of a digital circuit as a function of VDD [1].

This section starts with a description of a transistor model at sub-threshold voltage and then provides a power consumption model based on the presented transistor model.

#### 2.1.1 MOS Transistor Model for Sub-threshold Operation

Analyzing a circuit in a sub-threshold region requires an accurate MOS transistor model adapted for low-voltage and low-current applications. In 1995, Enz, Krummenacher and Vittoz presented a fully analytical MOS transistor model dedicated to the design and analysis of low-voltage and low-current analog circuits, known as EKV [21].

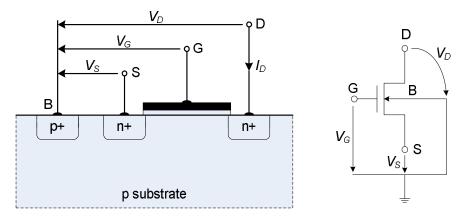

Figure 2.2 shows the cross section view and symbol of an n-channel MOS transistor. The value of drain and source voltages with respect to the pinch-off voltage divides the operation modes of the MOS transistor into four modes: conduction (strong inversion), blocked (weak inversion), forward saturation and reverse saturation. The pinch-off voltage,  $V_P$ , is the gate to source voltage for which the channel width is reduced to zero.

Figure 2.2: Cross section view and symbol of an n-channel MOS transistor

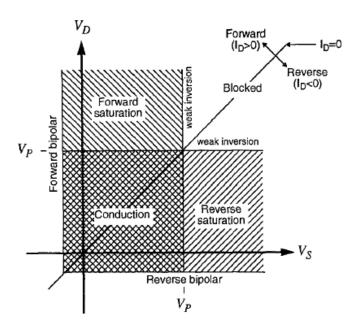

Figure 2.3 illustrates the aforementioned modes. If  $V_D$  and  $V_S$  are both less than  $V_P$ , the channel is in strong inversion and the transistor works in conduction mode. Either forward saturation or reverse saturation occurs, depending on the sign of  $V_D - V_S$ , when the channel is pinched-off from the drain end or source end, respectively. If both  $V_D$  and  $V_S$  are larger than  $V_P$ , the whole channel is pinched off and the device operates in blocked mode. If either of  $V_D$  or  $V_S$  is still close to the pinch-off voltage, the device is weakly inverted.

Figure 2.3: Modes of operation of a MOS transistor [21].

According to the EKV model, the drain current can be decomposed into a forward current,  $I_F$ , which depends only on the difference voltage  $V_P - V_S$ , and a reverse current,  $I_R$ , which depends only on  $V_P - V_D$ . Expression 2.1 shows the equation for  $I_D$ . Equations 2.2 and 2.3 evaluate the expressions for the forward and reverse currents in strong inversion and weak inversion, respectively. Derivations of these formulas can be found in [21].

$$I_D = I_F - I_R \tag{2.1}$$

$$I_{F} = \begin{cases} \frac{n \beta}{2} (V_{P} - V_{S})^{2} & for: V_{S} < V_{P} \\ 0 & for: V_{S} \ge V_{P} \end{cases}$$

(2.2)

$$I_R = \begin{cases} \frac{n \beta}{2} (V_P - V_D)^2 & for: V_D < V_P \\ 0 & for: V_D \ge V_P \end{cases}$$

$$I_F = K_W \beta V_{th}^2 e^{\frac{V_P - V_S}{V_{th}}}$$

(2.3)

$$I_R = K_w \beta V_{th}^2 e^{\frac{V_P - V_D}{V_{th}}}$$

where:

$$\beta = \mu_n C'_{ox} \frac{W}{L} \tag{2.4}$$

$$n = 1 + \frac{c_d}{c_{ox}}$$

, n is called the sub-threshold slope factor (2.5)

$$K_w = (n-1) e^{\frac{\Psi_0 - 2\Phi_F}{V_{th}}}$$

(2.6)

Other parameters include  $\mu_n$  is the mobility of electrons,  $C_{ox}$  is the gate oxide capacitance per unit area, W is the width and L is the length of transistor. Also,  $V_{th}$  is the thermodynamic voltage of MOS transistor,  $\Psi_0$  is the surface potential constant, and  $\Phi_F$  is the Fermi potential. Their expressions and definitions are not important for this work and can be found in [21].

An accurate model like EKV is necessary for careful analysis of analog circuits or gate level circuit design, especially when the circuit operates at the weak inversion edge. However, more basic models exist which are able to propose a reasonable estimate of circuit behavior. Since, in the subthreshold region, the sub-threshold current (which is a diffusion current) dominates other components of the drain current, such as gate leakage and Gate-Induced Drain Leakage (GIDL), the total drain current can be equated to the sub-threshold current. Equation 2.7 represents this model of a sub-threshold current [13].

$$I_D = I_0 e^{\frac{V_{GS} - V_T}{nV_{th}}} \tag{2.7}$$

where  $V_T$  is the threshold voltage of MOS transistor and  $I_0$  is the drain current when  $V_{GS} = V_T$ , as given in Equation 2.8:

$$I_0 = \beta (n-1) V_{th}^2$$

(2.8)

To model low  $V_{DS}$  roll-off and Drain-Induced Barrier Lowering (DIBL), Equation 2.7 can be upgraded to Equation 2.9.

$$I_D = I_0 e^{\frac{V_{GS} - V_T + \eta V_{DS}}{nV_{th}}} (1 - e^{\frac{-V_{DS}}{V_{th}}})$$

(2.9)

shere,  $\eta$  is the DIBL coefficient. The sub-threshold current derivation can be found in [22].

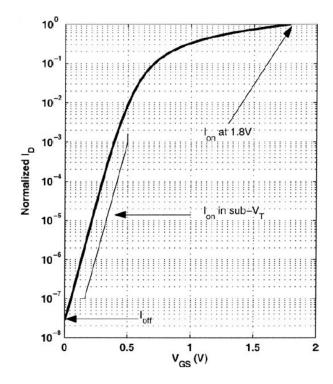

Figure 2.4 shows the drain current versus the gate to source voltage. As Equation 2.9 predicts and Figure 2.4 represents, the drain current,  $I_D$ , varies exponentially with  $V_{GS}$  in the sub-threshold region. As will be mentioned later, this exponential relationship in the sub-threshold region causes an exponential reduction in power consumption.

Figure 2.4:  $I_D$  versus  $V_{GS}$  for a MOS transistor in 0.18µm process with nominal  $V_{DD}$  of 1.8V [13].

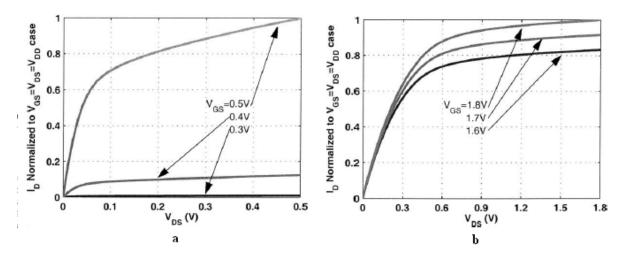

Figure 2.5 compares the variation of  $I_D$  with respect to  $V_{DS}$  in strong inversion against a subthreshold. Sub-threshold curves show the exponential dependence on  $V_{GS}$ , but they appear quite

similar to the strong inversion curves in their shape. The quasi-linear region comes from the roll-off of the current at low  $V_{DS}$ . Unlike strong inversion, the onset of this roll-off depends only on  $V_{DS}$  and not on  $V_{GS}$ . In strong inversion, the  $V_{DS}$  dependence on the velocity saturation region results from channel length modulation and is commonly modeled with the early voltage. Early voltage is the voltage where a tangent to  $I_D$ - $V_{DS}$  curve intercepts the voltage axis. In sub-threshold, the  $V_{DS}$  dependence in the quasi-saturation region results from DIBL and can be modeled with a DIBL coefficient.

Figure 2.5:  $I_D$  versus  $V_{DS}$  for three values of  $V_{GS}$  in a 0.18µm process. a. sub-threshold, b. strong inversion [13].

#### 2.1.2 MOS Power Model for Sub-threshold Operation

The total power consumption of a digital circuit is the sum of its dynamic, static and short-circuit power, as given in Equation 2.10 [23].

$$P_{total} = P_{Dynamic} + P_{Static} + P_{Short-Circuit}$$

(2.10)

The dynamic power is evaluated by Equation 2.11.

$$P_{Dvnamic} = \alpha \times f \times C_{eff} \times V_{DD}^{2}$$

(2.11)

Where  $\alpha$  is activity factor, f is the switching frequency and  $C_{eff}$  is the effective capacitance.

Decreasing  $V_{DD}$ , lowers the dynamic power quadratically. Therefore, a circuit operating in the subthreshold region consumes much less power than the same circuit in strong inversion with an identical activity factor and frequency. For instance, in 65 nm technology with a  $V_{DD}$  of 0.9 V, a 95% reduction in dynamic power results by moving the  $V_{DD}$  to 0.2 V.

Static or leakage power is the power consumed by the system while in steady state and is given by Equation 2.12.

$$P_{Static} = I_{Leakage} \times V_{DD} \tag{2.12}$$

With lower supply voltage during sub-threshold operation,  $V_{DS}$  is less than the  $V_{DS}$  in strong inversion which results in lower leakage current and therefore lower leakage power. Depending on the technology and  $V_{DD}$  scaling, the leakage power is reduced by 4 to 90 times [23]. Since the frequency is lower in sub-threshold operation, leakage power is integrated over a larger time, which makes the leakage energy increase in the sub-threshold region. Thus, dynamic energy, which is the dominant portion of the total energy in strong inversion is no longer dominant at sub-threshold. In fact, it is even less than the leakage energy close to the minimum energy point [19].

Short circuit power is the power dissipated by the short circuit that flows directly between  $V_{DD}$  and  $V_{SS}$  during a switching transition. Short circuit power is shown in Equation 2.13.

$$P_{Short-Circuit} = I_{Short-Circuit} \times V_{DD}$$

(2.13)

Due to slower operation at sub-threshold, the period of short circuit in CMOS cells is increased. Even so, the short circuit power is a factor of the supply voltage, and thus is reduced [23].

#### 2.2 Side Channel Analysis Attacks

Secret information hidden in cryptographic devices can be extracted by passive observation of the device's functional behavior or active manipulation of the device to behave abnormally and extract secret information from the intentional abnormality. The first category is generally referred to as side channel attacks (SCA), and the latter as fault injection attacks.

Side channel attacks break a cryptographic device by exploiting information from the physical characteristics of the device, such as power consumption [8], electromagnetic radiation [9] and run time [10]. Recording many samples of instantaneous power consumption (known as a power trace) of a device and analyzing it to exploit secret information, such as a key, is called a power analysis attack.

Power analysis of side channel signals from smartcards was first presented in 1999 by Kocher et al. [8] on a DES algorithm. Instantaneous power consumption of a cryptographic device normally depends on the data it processes and the operation it performs. Power analysis attacks are based on exploiting these dependencies, and various methodologies are introduced to achieve this goal. Simple power analysis (SPA), differential power analysis (DPA) and correlation power analysis (CPA) are the most common types of power analysis methodologies.

This section reviews SPA and DPA as the first proposed methods of power analysis attack. It then provides a brief introduction to CPA, as the method used in this research. Next, measures for analyzing the side channel information leakage are briefly listed. Finally, a few of the side channel resistant logics presented thus far will be introduced and SABL and WDDL (the ones which are employed in this research for comparison) are explained.

#### 2.2.1 Overview of Simple Power Analysis and Differential Power Analysis

SPA attacks exploit information by simply measuring the instantaneous power consumption of a device and correlating its fluctuations with the different rounds of cryptographic algorithms or operations and key values. In other words, an attacker tries to find the key by directly interpreting the single available trace to find patterns or matched templates. On the other hand, DPA attacks extract the key by performing statistical analysis on a large number of power traces to find out how power consumption, at fixed moments in time, depends on the processed data. DPA attacks are thus based on the data dependency of power traces [24].

While SPA attacks require detailed knowledge about the implementation of the cryptographic algorithm, DPA attacks only need to know the algorithm itself. Although several SPA attacks on algorithms like AES have been reported [25, 26], it is much easier to prevent the threat of these attacks compared to DPA attacks. However, SPA is the sole possible method when only one power trace is available. DPA attacks require a large number of traces and their runtime is significantly longer than that of SPA's.

DPA works based on the difference between power consumption of 0 to 1 and 1 to 0 transitions. It collects N power traces corresponding to N plaintexts,  $P_i$  (i = 1 ... N), and chooses a selection function, f, which operates on  $P_i$ ,  $K_s$  (the guess key), and bit f, the examined bit (e.g. a bit of the S-Box output). The output of the selection function can be either 0 or 1. The next step is to compute a differential trace  $\Delta_f(b)$ , which is the difference between the average of traces with f equals 1 and with f equals 0. Expression 2.14 summarizes the described methodology.  $W(P_i)$  is the power trace corresponding to the plaintext  $P_i$ .

$$\Delta_f(b) = \frac{\sum_{i=1}^N f(P_i, b, K_S) W(P_i)}{\sum_{i=1}^N f(P_i, b, K_S)} - \frac{\sum_{i=1}^N (1 - f(P_i, b, K_S)) W(P_i)}{\sum_{i=1}^N (1 - f(P_i, b, K_S))}$$

(2.14)

If calculated bits during the cryptographic algorithm are uniformly distributed and the number of power traces are sufficient,  $\Delta_f$  (b) corresponding to a wrong  $K_s$  will be zero. Thus, the only  $\Delta_f$ (b) which gives the value of nonzero reveals the correct key [27].

In order to enhance DPA, extended attacks, such as higher order DPA (HO-DPA) [8, 28], multi-bit DPA [29, 30] and correlation power analysis (CPA) [31, 32], are proposed. The difference between these methods is mainly in the complexity of the statistical analysis. Correlation power analysis, as an effective and commonly used approach, is chosen as the attack methodology in this research.

#### 2.2.2 Correlation Power Analysis

Correlation power analysis (CPA) attacks are based on the correlation between the power consumption of the cryptographic device and the Hamming weight or Hamming distance of the handled data. In power analysis attacks, it is necessary to have a power model that maps data values processed by the device to the power consumption traces. Specifically, in a DPA attack, the selection function performs the required mapping, which assumes dissimilar power consumption for 0 to 1 and

1 to 0 transitions. However, the power models used in CPA, Hamming weight [33] and Hamming distance [31] assume that 0 to 1 and 1 to 0 transitions contribute equally to power consumption and that 0 to 0 and 1 to 1 transitions also lead to the same power consumption. It is assumed in CPA that information leakage through power consumption depends on the number of bits switching from one state to another at a given time, not the type of transition.

The Hamming weight of a vector input  $v_0$ ,  $HW(v_0)$ , is defined as the number of set bits in  $v_0$ , and it is assumed that the power consumption is proportional to  $HW(v_0)$ . The Hamming distance of two vector inputs  $v_0$  and  $v_1$ ,  $HD(v_0, v_1)$ , is the number of flipping bits to go from  $v_0$  to  $v_1$ . In a Hamming distance model, the power consumption of the device is modeled with the number of bits switching from one state to either its preceding or succeeding state, while in a Hamming weight model the knowledge of the current state is sufficient. Therefore, a Hamming distance model requires more details of the device and may not be possible to mount in all applications.

Brier et al. proposed a model for power consumption based on the Hamming distance model in [31]. The Brier's model can be seen in Expression 2.15.

$$W = a HD(D,R) + b (2.15)$$

This model assumes a linear relationship between power consumption, W, and the Hamming distance between D, a uniform random variable, and a reference state, R. This model only represents the data-dependent part of power consumption, which does not seem unrealistic because the majority of a cell's power is consumed within the bus lines [31]. Constant b models enclose offsets, time-dependent components, and noise.

The correlation factor  $\rho_{WH}$  between power consumption and the Hamming distance can be calculated as follows:

$$\rho_{WH} = \frac{cov(W,H)}{\sigma_W \sigma_H} \tag{2.16}$$

where  $\sigma^2$  is variance, we have:

$$\sigma_W^2 = a^2 \sigma_H^2 + \sigma_b^2 \tag{2.17}$$

So, expression 2.15 can be further simplified to expression 2.18.

$$\rho_{WH} = \frac{a\sigma_H}{\sigma_W} = \frac{a\sigma_H}{\sqrt{a^2\sigma_H^2 + \sigma_b^2}} = \frac{a\sqrt{m}}{\sqrt{ma^2 + 4\sigma_b^2}}$$

(2.18)

where m is the number of bits in D as a uniform random variable and m/2 is the mean and m/4 is the variance of HD(D+R) as a uniform random variable. The correlation factor is a value between -1 and +1, which  $\pm 1$  means perfect correlation and the sign depends on the linear gain, a.

Expression 2.18 shows that a minimized noise variance,  $\sigma_b^2$ , maximizes the correlation factor, which helps to determine the reference state, R. The process is to scan all possible values of R and rank them by the correlation factor. The one with the maximum correlation factor is the correct reference value.

The above claim is proved in [31]. Suppose a correct reference, R, and an incorrect guess of the reference value, R', which has k bits different from R. This would give, HD(R+R')=k. Since b is independent from other variables, the correlation factor is:

$$\rho_{WH'} = \frac{cov(aH+b,H')}{\sigma_W \sigma_{'H}} = \frac{a}{\sigma_W} \frac{cov(H,H')}{\sigma_{'H}} = \rho_{WH} \rho_{HH'} = \rho_{WH} \frac{m-2k}{m}$$

(2.19)

Expression 2.19 shows that even a 1 bit difference between R and R' reduces the correlation factor by 1/4.

In summary, in order to perform a CPA attack, a power model based on the Hamming weight or Hamming distance must first be chosen. In the next step, the device needs to be run with all possible values of a reference state or input plaintext, and a power consumption trace has to be measured. In the final step, the correlation factors between the predetermined values from the power model and measured power traces are calculated and the maximum correlation factor corresponds with the correct key of the device.

#### 2.2.3 Measures for Side Channel information leakage

Various measures exist to evaluate side channel information leakage of cryptographic devices. CPA can be considered as an effective and accurate measure that not only reveals the secret key but also analyzes the amount of information leakage using obtained correlation coefficients. Other than CPA, simpler measures are also introduced that can be employed to study the data and operation dependency of instantaneous or averaged power consumption of a device. The following paragraph gives a brief overview of some of most commonly used measures which will be discussed in further detail in Chapter 4.

Difference of mean energies (DME), suggested by [34], is a measure which highlights the difference between power traces that process 1 compared to those that process 0. The frequency of observation measure used in [35] visualizes the closeness of average power consumption values for all possible inputs. This measure is based on the fact that attacking a system whose average power consumption values for various combinations of inputs are aggregated in a small range requires more effort and sample traces than a system with a wider range of averaged power consumption values. Normalized energy deviation (NED) and normalized standard deviation (NSD), first used by [35], form another type of measure that provides a simple yet effective security evaluation for many logic schemes. They quantize the previous measure, frequency of observation, and determine the dispersion of averaged power consumption values of a cryptographic device for various data transitions.

#### 2.2.4 Side Channel Resistant Logics

The important key to designing a secure cryptographic device is to eliminate data dependency and operation dependency of power consumption. A device which consumes constant energy in all clock cycles of an operation can be a perfectly secured design. A circuit with constant energy consumption and power trace for all types of transitions-0 to 1, 1 to 0, 1 to 1 and 0 to 0-satisfies our desired goal.

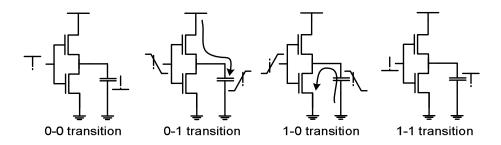

Figure 2.6 shows an Inverter in Static Complementary CMOS logic (scCMOS), which is the default logic scheme available in existing standard cell libraries. This cell consumes power from the power supply only during 0 to 1 and 1 to 0 transitions. Since the load capacitance is different in these two cases, the consumed power during these two transitions is different. No power is consumed during 0 to 0 and 1 to 1 transitions. Thus, this logic scheme leaks high amounts of information. A secure logic scheme must have output switching independent of input switching as well as constant load capacitance for all transitions [35].

Figure 2.6: Output transitions in a static complementary CMOS logic [35].

Various logics are proposed to provide the above characteristic. Sense Amplifier Based Logic (SABL) [35], Wave Dynamic Differential Logic (WDDL) [36], Dynamic Current Mode Logic (DyCML) [37], Low-Swing Current Mode Logic (LSCML) [38] and Masked Dual-Rail Pre-charge Logic (MDPL) [39] are examples of the presented logics. Mace et al. summarizes the characteristics of mentioned logics in [40], as shown in Table 2.1.

| Logic styles | Dual-Rail | Masked | Pre-Charged | Standard Cell |

|--------------|-----------|--------|-------------|---------------|

| CMOS         |           |        |             | ✓             |

| SABL         | ✓         |        | ✓           |               |

| WDDL         | ✓         |        | ✓           | ✓             |

| DyCML        | ✓         |        | ✓           |               |

| LSCML        | ✓         |        | ✓           |               |

| MDPL         | ✓         | ✓      | ✓           | ✓             |

Table 2.1: Summary of characteristics for side channel resistant logics [40].

According to Table 2.1, all side channel resistant logics are dual-rail and pre-charged. SABL, DyCML and LSCML are full custom logic styles, while WDDL and MDPL are compatible with standard cell libraries. In this research, SABL and WDDL are chosen for study and comparison. Following is a brief overview of these two logic schemes.

Figure 2.7.a illustrates a differential network. This network provides true and false values of the output signal with the help of De-Morgan's law. De-Morgan's law generates a false output using false inputs. The truth table of this network is shown in Figure 2.7.a. Since both *out* and *out*' signals flip in each transition of 1 to 0 and 0 to 1, the total power consumption of this differential network is the same for 1 to 0 and 0 to 1.

Figure 2.7.b demonstrates a dynamic network. Here, the clock period is divided into two phases: pre-charge and evaluation. In the first phase, the output signal is pre-charged to the pre-charge value. In the latter phase, output is evaluated based on inputs. This modification in the circuit makes the output flip in 0 to 0 and 1 to 1 transitions; hence, it always consumes power. As the truth table of Figure 2.7.b demonstrates, power consumption for 0 to 1 and 1 to 1 transitions are identical, as is power for 0 to 0 and 1 to 0.

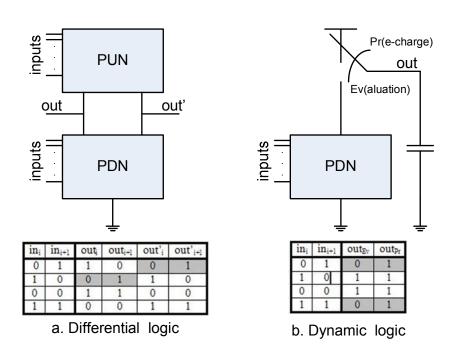

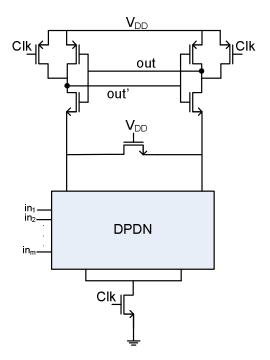

Combining differential and dynamic schemes into one dynamic and differential logic scheme provides almost the same power consumption for all clock cycles. SABL and WDDL are two dynamic and differential logics. The implementation of NAND, NOR and XOR gates in these two schemes is explained in the following sections.

Figure 2.7: Power characteristics in the form of a truth table for a) Differential logic b) Dynamic logic [35].

#### 2.2.4.1 SABL

A generic n-gate in SABL logic is shown in Figure 2.8. The differential pull-down network along with the output pre-charge circuit provides the same power consumption for all transitions. SABL is also designed to have a constant load capacitance for all transitions. Implemented NAND, NOR and XOR gates in the SABL logic scheme are shown in Figure 2.9. DPDN is designed such that the conducting path in all possible paths has the same resistance, which is ensured by having the same number of identical transistors in each conducting path of the DPDN network [24].

SABL logic can only be used in custom design. It is impossible to use standard cell libraries and available digital design tools to design a SABL circuit. This issue, together with the significantly large power consumption caused by almost doubling the total number of transistors, is a major drawback of this logic scheme.

Figure 2.8: Generic n-gate SABL logic [35].

Figure 2.9: SABL gates a) NAND b) NOR b) XOR.

#### 2.2.4.2 WDDL

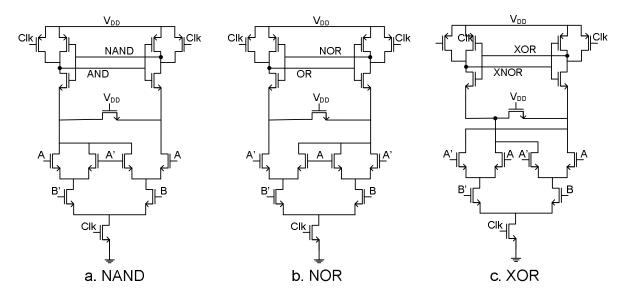

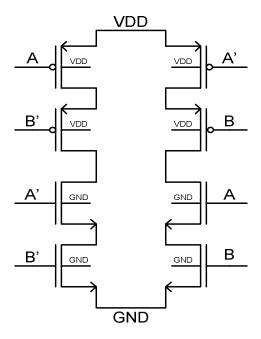

Figure 2.10 represents NAND, NOR and XOR gates in a WDDL logic scheme. The first difference between WDDL and SABL is that available standard cell libraries can be employed in designing a circuit in WDDL logic. Therefore, this logic scheme provides the capability of an RTL design of a secure circuit in WDDL logic, using the available digital design tools.

Figure 2.10: WDDL gates a) NAND b) NOR c) XOR.

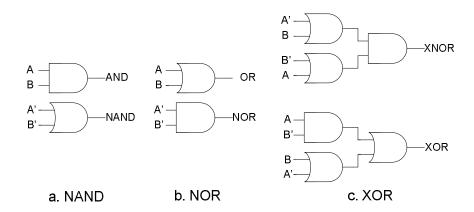

The second difference is the pre-charging methodology. Figure 2.11 shows the pre-charge circuit for combinatorial WDDL gates. In WDDL, inputs are pre-charged and the pre-charge signals at inputs ripple all the way through the combinatorial circuit to the output, where they pre-charge the output. Having a pre-charge circuit for the inputs eliminates the necessity of having this circuit for all gates. Hence, the area and power consumption of a WDDL gate is lower than the area and power consumption of the same gate in SABL logic.

Figure 2.11: WDDL pre-charge circuit [36].

#### 2.3 Previous Side Channel Research of Sub-threshold Circuits

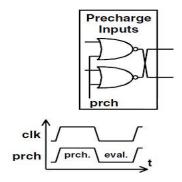

Extensive research has been carried out in the area of sub-threshold circuits. However, side channel information leakage of this logic scheme is still relatively unexplored. To the best of our knowledge, only three papers, [41-43], all published in 2008, have focused on studying information leakage of sub-threshold against differential power analysis attacks.

Alstad and Aunet implemented a static CMOS 8-bit ripple carry adder in [41] and a compact 4-staged pipelined and asynchronous S-Box in [42]. Both circuits were simulated at the transistor level using 90 nm CMOS technology. They used normalized standard deviation of the supply current as the measure of security and claimed that sub-threshold operation reduces the standard deviation with a factor of 2500. Normalized standard deviation was introduced in section 2.2.3. It is not a very strong measure of security especially when it is used individually and it will be discussed in more detail later in Chapter 4.

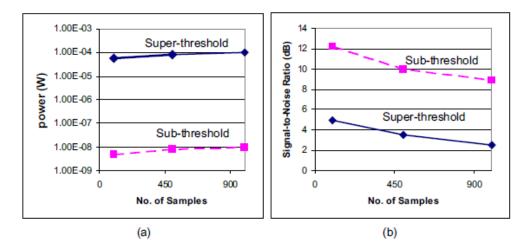

Haider and Nazhandali mounted a DPA attack on an S-Box in which SPICE-level simulation is performed on a transistor level design implemented in 45 nm technology [43]. Their focus is on the signal-to-noise ratio (SNR) of the sub-threshold circuit versus strong inversion. Figure 2.12 represents their simulation results, showing in part "a" the minimum average noise power that hides the secret key and defeats the DPA attack. According to their results, there are four orders of magnitude difference between the noise power required to cover the secret in sub-threshold and strong inversion. Figure 2.12.b demonstrates the SNR at which a DPA attack can be successful. Larger values of SNR

for sub-threshold mean that less noise is needed to cover the secret information at sub-threshold compared to strong inversion.

Figure 2.12: Analysis of a secure circuit resistivity toward power analysis attacks [43].

In summary, side channel analysis of sub-threshold circuits has been previously studied in three papers, in which normalized standard deviation and signal-to-noise ratio of a transistor level AES S-Box and an 8-bit ripple carry adder are the main focus. However, further studies on sub-threshold logics are required. A closer look into instantaneous power consumption of a circuit operating in a sub-threshold region can demonstrate the information leakage behavior of this logic scheme. Moreover, correlation power analysis attack is also a serious threat that sub-threshold logics vulnerability against this attack needs to be studied. Finally, side channel analysis of register transfer level implementation of sub-threshold circuits is another unexplored aspect of this logic that is considered in this research.

The next chapter will study the circuits used for power analysis in this research and propose the design methodology for sub-threshold circuit in both transistor level and RTL.

## Chapter 3 Sub-threshold Circuits and Design Methodology

This chapter discusses the methodology and challenges of designing a circuit for sub-threshold operation. In section 3.1 a list of challenges which a designer will confront in designing a circuit for sub-threshold operation is presented. In section 3.2, which focuses on transistor level design, the characteristics of an inverter gate at sub-threshold provide a basis for transistor level design which is used in the subsequent design of other gates, such as NAND, NOR and XOR. Afterwards, register transfer level design is presented in section 3.3. The digital design flow of a sub-threshold circuit is explained in that section followed by a performance analysis of standard cell libraries and the Advanced Encryption Standard (AES) crypto-processor used in this research.

#### 3.1 Design Challenges at Sub-threshold

While a circuit operating in sub-threshold region consumes little power, low current level and an exponential dependence of current to voltage introduce a group of deficiencies and challenges which need to be considered by designers. This section briefly describes some of the more important design challenges.

#### 1. Performance

The weak current flow in sub-threshold circuits results in longer delays due to the longer time required to charge and discharge capacitances in the circuit. As mentioned earlier in this section, there is a trade-off in choosing the value of  $V_{DD}$  between delay and energy. Choosing the value of  $V_{DD}$  higher than corresponding value for minimum energy point can benefit the performance at only a slight cost in energy.

#### 2. Minimum Operational Voltage

The supply voltage of 3-4  $V_{th}$  ( $V_{th}$ , the thermal voltage equal to kt/q) is the minimum possible  $V_{DD}$  for circuits operating at sub-threshold [23]. The Voltage Transfer Characteristic (VTC) of a minimum-sized inverter at 25°C in a 65 nm TSMC process is sketched for different values of supply voltage in Figure 3.1.

#### 3. Variability

Exponential *I-V* characteristics in a sub-threshold region can cause a large variance in transistor behavior, including process, voltage and temperature variability. Hence, a designer needs to use effective techniques to design more robust and reliable circuits [23, 44].

Figure 3.1: VTC as a function of supply voltage [23]

#### 4. Device Optimization

Devices optimized for strong inversion may not give optimal results for sub-threshold operation. The optimization of devices for sub-threshold operation can thus help to achieve higher frequencies [44].

#### 5. Robustness of logic families

Low  $V_{DD}$  results in a reduced  $I_{ON}/I_{OFF}$  ratio that can reduce robustness. Static CMOS gates function correctly at sub-threshold; however, other logic families may suffer from variations due to low  $I_{ON}/I_{OFF}$  ratio [44].

#### 6. Standard Cell Libraries

The simulation and synthesis of sub-threshold circuits is a great challenge due to the unavailability of standard cell libraries designed specifically for sub-threshold operation. Current standard cell libraries are characterized for a specific voltage which is in the strong inversion region. Thus, the synthesis of circuits at sub-threshold requires re-characterization and modification of libraries.

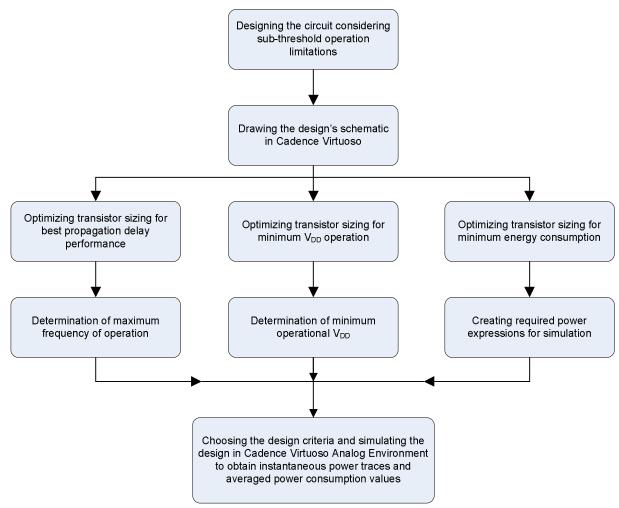

#### 3.2 Transistor Level Design

This section describes the design methodology for transistor level sub-threshold circuits. An exponential dependency of the drain current on  $V_{DS}$  alters the transistor's behavior and introduces a new design methodology. This section studies the characteristics of an inverter circuit (e.g. sizing, speed, frequency of operation and minimum operational voltage) to provide a general idea of a transistor level circuit in a sub-threshold region. The section also provide a design explanation of the most important components of every digital circuit (NAND, NOR and XOR gates). All implementations and simulations are performed in Cadence Virtuoso Analog Environment using 65 nm TSMC technology. The transistor level design flow used in this research is shown in Figure 3.2.

Figure 3.2: Sub-threshold transistor level design flow.

#### 3.2.1 Inverter Operation in Sub-threshold Region

The first design element to be discussed is transistor sizing which can be studied from three points of view. One is, the ratio of PMOS width to NMOS width, at which the circuit operates with the minimum  $V_{DD}$ . The ratio  $W_P/W_N$  that obtains the same current for both PMOS and NMOS transistors provides the minimum  $V_{DD}$  operation. Reference [13] suggests the value of 12 for  $W_P/W_N$  to achieve the minimum voltage of 50 mV. However, based on the available transistor model for this research, which is the general purpose model of the 65 nm TSMC process, a lower  $W_P/W_N$  value gives better functionality in sub-threshold voltages. Therefore, a minimum supply voltage operation occurs for the equal width size of PMOS and NMOS.

The next factor that impacts sizing is the propagation delay. Based on experiments done in this research on inverters for different sub-threshold voltages in the range of 0.1 V to 0.3 V, the ratio of 2.7 was observed as the best ratio of  $W_P/W_N$  to provide equal rising and falling propagation delay. Inverter sizing to achieve the minimum energy is the last criterion that occurs with minimum transistor sizing. Hence, the smallest sized NMOS transistor should be chosen and, depending on the application the ratio of PMOS to NMOS transistor can be set.

The inverter delay in both strong inversion and sub-threshold, in case of symmetrical PMOS and NMOS transistors is given by Equations 3.1 and 3.2, respectively [13].

$$t_{d} = \frac{K C_g V_{DD}}{(V_{DD} - V_T)^{\alpha}} \tag{3.1}$$

$$t_{d,sub} = \frac{K C_g V_{DD}}{I_o exp\left(\frac{V_{DD} - V_T}{n V_{th}}\right)}$$

(3.2)

As Equation 3.2 presents, an exponential decrease of  $I_{on}$  in the sub-threshold region leads to an exponential dependency of delay on  $V_{DD}$ , which is a stronger dependency compared to the strong inversion delay presented in Equation 3.1. Figure 3.3 shows the normalized inverter speed across the full range of supply voltage. The inverter speed degrades slowly in strong inversion and drops fast for  $V_{DD}$  below 0.4 V.

Figure 3.3: Normalized inverter speed versus supply voltage.

Taking into consideration the minimum size for an NMOS transistor and the value of 2 for  $W_P/W_N$ , the inverter is tested for various supply voltages in the sub-threshold region. The output voltage of the inverter for  $V_{DD} = 200$  mV, 150 mV, 75 mV and 50 mV is shown in Figure 3.4. For supply voltages of 200 mV and 150 mV, the circuit maintains a full 10% - 90% output swing. Although this swing is degraded for  $V_{DD} = 75$  mV, the output voltage still covers the 10% - 90% swing. From a supply voltage of 60 mV, the output swing degrades drastically and the inverter can no longer be considered operational. The degraded output swing of the inverter for a supply voltage of 50 mV can be observed in Figure 3.4.d. Therefore, the minimum operational voltage using the available models in this research is 60mV.

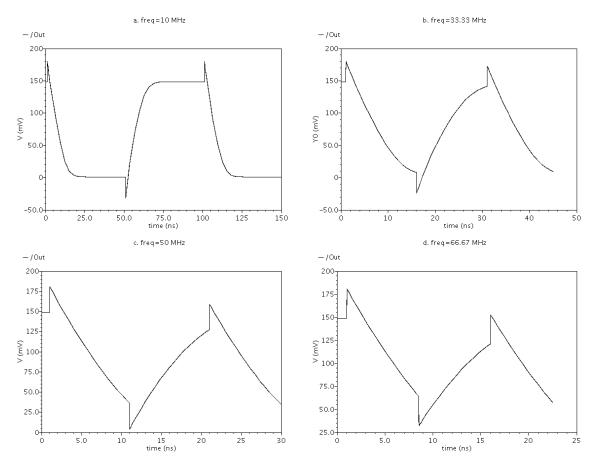

Now that the sizing, speed and minimum operational voltage are determined, the maximum frequency of operation can be obtained. The output voltages of the inverter for the frequencies of 10 MHz, 33.33 MHz, 50 MHz and 66.67 MHz are shown in Figure 3.5. The operational voltage is 150 mV. We can observe that the output voltage swing starts to degrade from 50 MHz and then cannot maintain the 10% - 90% swing at a frequency of 66.67 MHz (the period of 15 ns). Thus we can see that, the limited range of operational frequency is a significant drawback of sub-threshold circuits. Based on the available models in this research, the maximum frequency is around 70 MHz.

Figure 3.4: Inverter output at the frequency of 10 MHz and supply voltages of a)  $V_{DD} = 200 \text{ mV}$ , b)  $V_{DD} = 150 \text{ mV}$ , c)  $V_{DD} = 75 \text{ mV}$  and d)  $V_{DD} = 50 \text{ mV}$ .

Figure 3.5: Inverter output for the supply voltage of 150 mV and frequencies of a) f = 10 MHz, b) f = 33.33 MHz, c) f = 50 MHz and d) f = 66.67 MHz.

#### 3.2.2 NAND Gate Operation in Sub-threshold Region

The architecture of the NAND gate is the same as the static CMOS architecture for strong inversion NAND gate, the only difference being the transistor sizing. In strong inversion, it is better to set the  $W_P/W_N$  ratio around two to equalize the low-to-high and high-to-low propagation delays. However, as mentioned in the previous section, this ratio has to be one to achieve the minimum operational voltage.

Table 3.1 summarizes the characteristics of the NAND gate in the sub-threshold region. The minimum  $V_{DD}$  at the frequency of 10 MHz is 100 mV, and the maximum frequencies of operation at voltages of 200 mV and 150 mV are 125 MHz and 40 MHz, respectively. The drastic decrease in speed with the reduction of the supply voltage can be observed in these results.

| Minimum supply voltage @ 10 MHz | 100 mV  |

|---------------------------------|---------|

| Maximum frequency @ 200 mV      | 125 MHz |

| Maximum frequency @ 150 mV      | 40 MHz  |

Table 3.1: Characteristics of a static CMOS NAND gate in sub-threshold.

#### 3.2.3 NOR Gate Operation in Sub-threshold Region

Similar to a NAND gate, the architecture of a NOR gate in sub-threshold region is the same as a static CMOS NOR gate in strong inversion, transistor sizing being the only difference. The ratio of PMOS to NMOS width is minimized to obtain the minimum operational voltage.

Table 3.2 summarizes the characteristics of a NOR gate in sub-threshold region. Maximum frequencies at 200 mV and 150 mV remain the same as for a NAND gate. However, the minimum supply voltage is a bit higher than for a NAND gate and occurs at 120 mV.

| Minimum supply voltage @ 10 MHz | 120 mV  |

|---------------------------------|---------|

| Maximum frequency @ 200 mV      | 125 MHz |

| Maximum frequency @ 150 mV      | 40 MHz  |

Table 3.2: Characteristics of a static CMOS NOR gate in sub-threshold.

#### 3.2.4 XOR Gate Operation in Sub-threshold Region

The XOR architecture used in this research is shown in Figure 3.6. Eight transistors are used to form the XOR gate. Following the aforementioned rule for  $W_P/W_N$ , this ratio is set to minimum. Table 3.3 provides an overview of the XOR gate characteristics. Since this gate includes more transistors than the previous two gates and has a more complex architecture, the output voltage swing starts to drop sooner. The minimum supply voltage at which the 10% - 90% output swing is achieved is 130 mV. The maximum frequency at supply voltage of 200 mV is 90 MHz, which decreases to 40 MHz for a supply voltage of 150 mV.

| Minimum supply voltage @ 10 MHz | 130 mV |

|---------------------------------|--------|

| Maximum frequency @ 200 mV      | 90 MHz |

| Maximum frequency @ 150 mV      | 40 MHz |

Table 3.3: Characteristics of a static CMOS XOR gate in sub-threshold.

Figure 3.6: Static CMOS XOR architecture.

#### 3.2.5 Parallel XORs

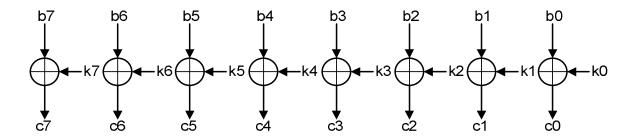

Since XOR is one of the most important components of a cryptographic hardware, further investigations on this specific gate are provided. In addition to a single XOR, another architecture which is used in this research for side channel analysis is a set of eight parallel XOR gates that takes an 8-bit input and produces an 8-bit output using an 8-bit key. This architecture is shown in Figure 3.7. Differential and correlation analysis of this gate is presented in Chapter 5.

Figure 3.7: Parallel XORs architecture.

## 3.3 RTL Design

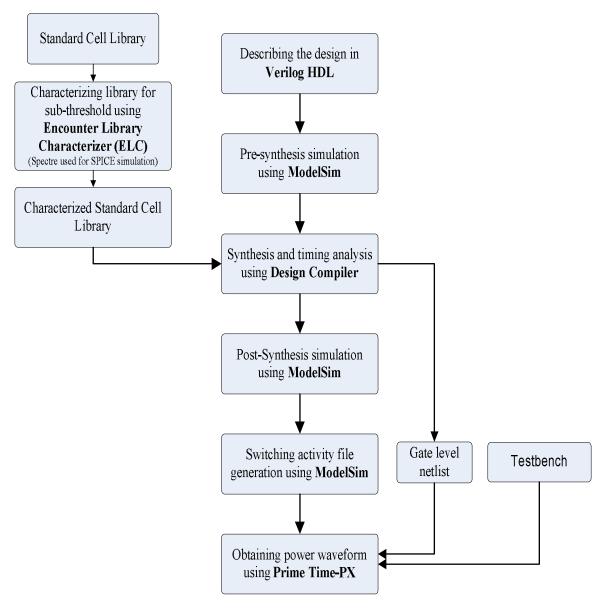

Designing a complete crypto-processor for encryption algorithms, such as AES, at the transistor level that includes thousands of transistors requires an enormous effort. Computer Aided Design (CAD) tools have reduced both the design effort and time required for large designs. The design flow starts by describing the architecture using an HDL language, such as Verilog HDL. After simulating and verifying the functionality of the design, RTL design is synthesized to a gate level design using a logic-synthesis tool like Synopsys Design Compiler. The logic-synthesis tool utilizes a standard cell library to synthesize an RTL circuit into a gate level circuit and also provides timing information. The next step is post-synthesis simulation and timing analysis. Depending on the application, power measurements can be performed using a switching activity file and the gate level netlist. The last step involves placement, routing and post-layout simulation.

Sub-threshold digital design flow, including the details on the tools, is discussed in section 3.3.1, followed by a discussion of the performance of standard cell libraries at a sub-threshold voltage in section 3.3.2. AES and S-Box architectures used in this research are explained in last two sections.

#### 3.3.1 Sub-threshold Digital Design Flow