# Methods for Reducing Monitoring Overhead in Runtime Verification

by

Chun Wah Wallace Wu

A thesis

presented to the University of Waterloo

in fulfillment of the

thesis requirement for the degree of

Master of Applied Science

in

Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2013

© Chun Wah Wallace Wu 2013

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### Abstract

Runtime verification is a lightweight technique that serves to complement existing approaches, such as formal methods and testing, to ensure system correctness. In runtime verification, monitors are synthesized to check a system at run time against a set of properties the system is expected to satisfy. Runtime verification may be used to determine software faults before and after system deployment. The monitor(s) can be synthesized to notify, steer and/or perform system recovery from detected software faults at run time.

The research and proposed methods presented in this thesis aim to reduce the monitoring overhead of runtime verification in terms of memory and execution time by leveraging time-triggered techniques for monitoring system events. Traditionally, runtime verification frameworks employ event-triggered monitors, where the invocation of the monitor occurs after every system event. Because systems events can be sporadic or bursty in nature, event-triggered monitoring behaviour is difficult to predict. Time-triggered monitors, on the other hand, periodically preempt and process system events, making monitoring behaviour predictable. However, software system state reconstruction is not guaranteed (i.e., missed state changes/events between samples).

The first part of this thesis analyzes three heuristics that efficiently solve the NP-complete problem of minimizing the amount of memory required to store system state changes to guarantee accurate state reconstruction. The experimental results demonstrate that adopting near-optimal algorithms do not greatly change the memory consumption and execution time of monitored programs; hence, NP-completeness is likely not an obstacle for time-triggered runtime verification. The second part of this thesis introduces a novel runtime verification technique called *hybrid runtime verification*. Hybrid runtime verification enables the monitor to toggle between event- and time-triggered modes of operation. The aim of this approach is to reduce the overall runtime monitoring overhead with respect to execution time. Minimizing the execution time overhead by employing hybrid runtime verification is not in NP. An integer linear programming heuristic is formulated to determine near-optimal hybrid monitoring schemes. Experimental results show that the heuristic typically selects monitoring schemes that are equal to or better than naïvely selecting exclusively one operation mode for monitoring.

#### Acknowledgements

I would like extend my greatest appreciation and gratitude to my family. Thank you for continually supporting my dreams and aspirations, for your words of advice and wisdom, and for your love. I am truly blessed by God to have such a great and loving family.

Words cannot describe how grateful I am for the love of my life, Noreen Wong, for being in my life. Thank you for always being there for me throughout all of the joys and challenges that I experienced throughout my graduate studies. I cannot thank you enough for your presence, comforting words, and love.

My graduate studies would not have been possible without the great mentorship, guidance, and support of Dr. Sebastian Fischmeister, my supervisor, and Dr. Borzoo Bonakdarpour. I sincerely thank you both for the opportunity and privilege of learning and conducting research with both of you. I would also like to extend my thanks to Dr. Derek Rayside for providing me an exciting opportunity to collaborate and develop new lab content for the undergraduate course in E&CE 351 (Compilers) and for his mentorship.

I would like to thank all of the members of the Real-Time Embedded Software Group for making the past two years on campus memorable. It was a pleasure to work on research projects with Shay Berkovich, Deepak Kumar, and Samaneh Navabpour. Hany Kashif and Johnson Thomas, thanks for being such great officemates.

I am also truly grateful for all of my friends' support. Thank you Amanda Cheung, Kathryn Cheung, Irina Choi, Jasmine Choi, Nathan Chung, Esther Lee, Heidi Wu, and Joanna Wu, for many years of incredible and supportive friendship. Yuki Cheung, Kenneth Lam, Henry Pang, Alice Tsang, Ronald Wan, Abraham Wong, Lily Wong, Osman Wong, and Jeffrey Woo, thank you for bringing lots of laughter and priceless memories throughout my undergraduate and graduate studies. Thank you Pastor Timothy Wai for your continual prayer, support, and mentorship, in my spiritual walk with God. Thank you all for everything.

My research and graduate studies were funded by scholarships from Natural Sciences and Engineering Research Council of Canada (NSERC) and Ontario Student Assistance Program (OSAP). I greatly appreciate the financial support NSERC and OSAP provided me over the past two years.

With kind permission of Springer Science and Business Media, Chapters 3 and 4 of this thesis were adopted from a publication that I co-authored: "Efficient Techniques for Near-Optimal Instrumentation in Time-Triggered Runtime Verification," in Runtime Verification, ser. Lecture Notes in Computer Science, vol. 7186, pp. 208 – 222.

#### Dedication

This thesis is dedicated to my family: Matthew, Wendy, and Joshua Wu, and to the love of my life, Noreen Wong, for their endless love, care, support, and encouragement throughout my studies.

# Table of Contents

| Li                                      | st of | Tables                                              | X  |

|-----------------------------------------|-------|-----------------------------------------------------|----|

| Li                                      | st of | Figures                                             | xi |

| 1                                       | Inti  | roduction                                           | 1  |

|                                         | 1.1   | Summary of Contributions                            | 5  |

|                                         | 1.2   | Outline                                             | 5  |

| <b>2</b>                                | Rel   | ated Work                                           | 7  |

|                                         | 2.1   | Reducing Runtime Verification Overhead              | 8  |

|                                         | 2.2   | Time-triggered Runtime Verification                 | 9  |

| 3                                       | Pre   | liminaries                                          | 12 |

|                                         | 3.1   | Checking System Properties at Run Time              | 12 |

|                                         | 3.2   | Control-flow Analysis                               | 13 |

| 3.3 Time-triggered Runtime Verification |       | Time-triggered Runtime Verification                 | 14 |

|                                         |       | 3.3.1 Transforming Control-flow Graphs              | 14 |

|                                         |       | 3.3.2 Determining the Longest Sampling Period (LSP) | 17 |

|                                         |       | 3.3.3 Increasing the Longest Sampling Period        | 18 |

| 4 | Heu | ıristics                        | for Time-triggered Runtime Monitoring                        | 20 |

|---|-----|---------------------------------|--------------------------------------------------------------|----|

|   | 4.1 | Introd                          | uction                                                       | 20 |

|   | 4.2 | Optim                           | izing Memory Overhead in Time-triggered Runtime Verification | 23 |

|   |     | 4.2.1                           | Integer Linear Programming                                   | 23 |

|   |     | 4.2.2                           | Integer Linear Programming Model                             | 23 |

|   | 4.3 | Heuris                          | etics                                                        | 26 |

|   |     | 4.3.1                           | Heuristic 1: Greedy Heuristic                                | 29 |

|   |     | 4.3.2                           | Heuristic 2: Minimum Vertex Cover Heuristic                  | 32 |

|   |     | 4.3.3                           | Heuristic 3: Genetic Algorithm                               | 36 |

|   | 4.4 | Experi                          | imental Results                                              | 39 |

|   |     | 4.4.1                           | Performance of Heuristics                                    | 40 |

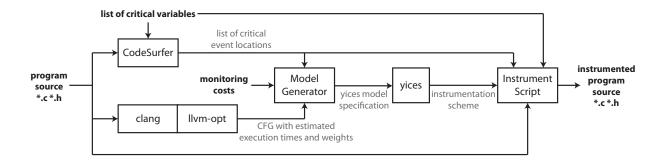

|   |     | 4.4.2                           | Analysis of Instrumentation Overhead                         | 42 |

|   | 4.5 | Conclu                          | iding Remarks                                                | 46 |

| 5 | Hyl | orid Rı                         | untime Monitoring                                            | 47 |

|   | 5.1 | Introd                          | uction                                                       | 47 |

|   | 5.2 | 5.2 Hybrid Runtime Verification |                                                              | 50 |

|   |     | 5.2.1                           | Overhead Runtime Costs                                       | 51 |

|   |     | 5.2.2                           | Utilizing Integer Linear Programming as a Heuristic          | 52 |

|   | 5.3 | Impler                          | mentation and Experimental Results                           | 57 |

|   |     | 5.3.1                           | Experimental Setup                                           | 57 |

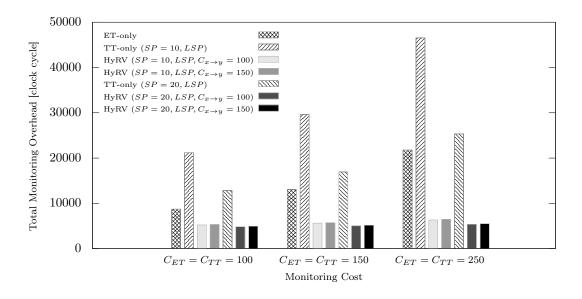

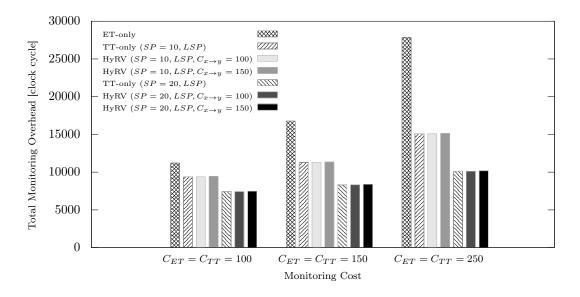

|   |     | 5.3.2                           | Experimental Results                                         | 58 |

|   | 5.4 | Conclu                          | iding Remarks                                                | 63 |

| б | Cor | clusio                          | ns                                                           | 64 |

| 7   | Future Work | 65 |

|-----|-------------|----|

|     |             |    |

| Ref | eferences   | 67 |

# List of Tables

| 4.1 | Performance of different optimization techniques | 41 |

|-----|--------------------------------------------------|----|

| 5.1 | Monitor cost configurations                      | 59 |

# List of Figures

| 1.1 | Overview of established runtime verification approaches                                                | 3  |

|-----|--------------------------------------------------------------------------------------------------------|----|

| 3.1 | A simple C program                                                                                     | 14 |

| 3.2 | Steps for obtaining optimized instrumentation and longest sampling period.                             | 15 |

| 3.3 | Illustrating redundant samples in time-triggered runtime verification                                  | 18 |

| 4.1 | Memory usage vs. sampling period period                                                                | 21 |

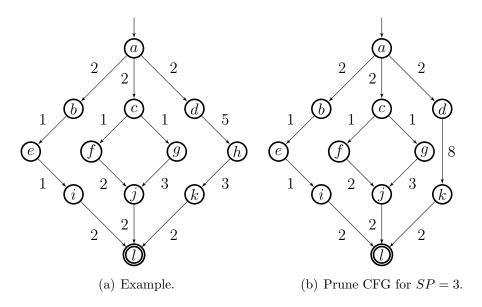

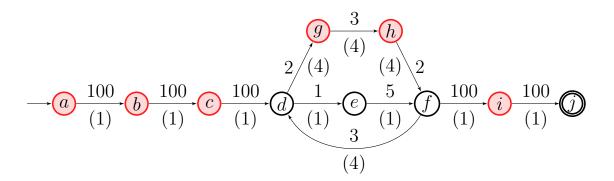

| 4.2 | CFG used for illustrating heuristics                                                                   | 28 |

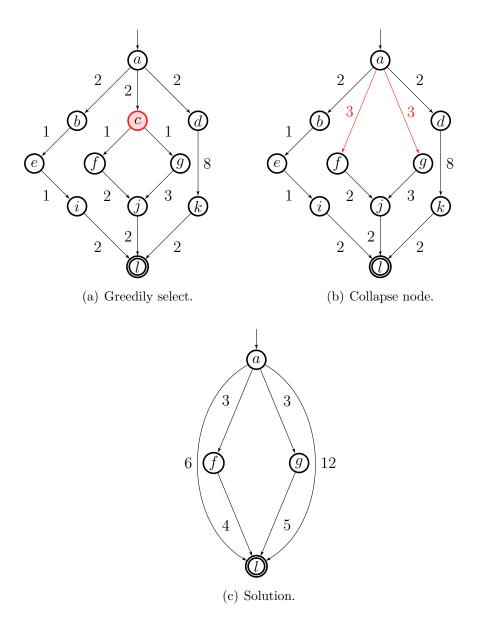

| 4.3 | Illustrations of Heuristic 1                                                                           | 31 |

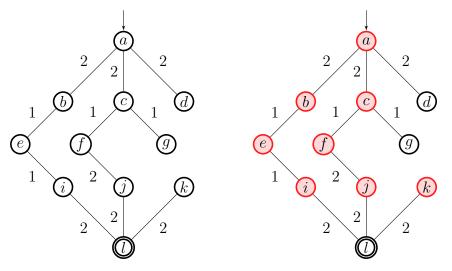

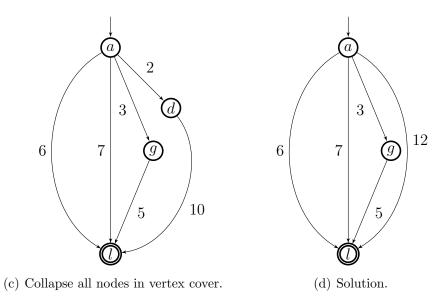

| 4.4 | Illustrations of Heuristic 2                                                                           | 35 |

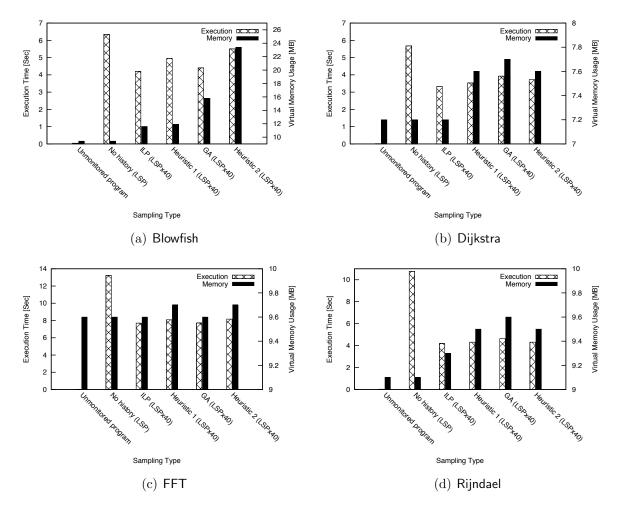

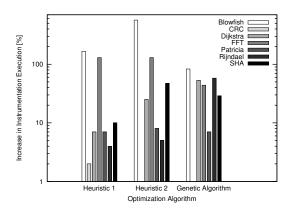

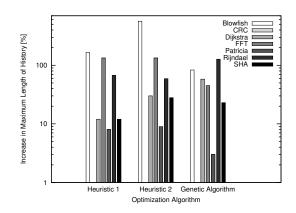

| 4.5 | The impact of different instrumentation schemes on memory usage and total execution time               | 43 |

| 4.6 | The impact of sub-optimal solutions on execution of instructions to build history and its maximum size | 45 |

| 5.1 | Comparing different methods of monitoring                                                              | 48 |

| 5.2 | CFG used for illustrating ILP model                                                                    | 56 |

| 5.3 | HyRV instrumentation toolchain for C applications                                                      | 58 |

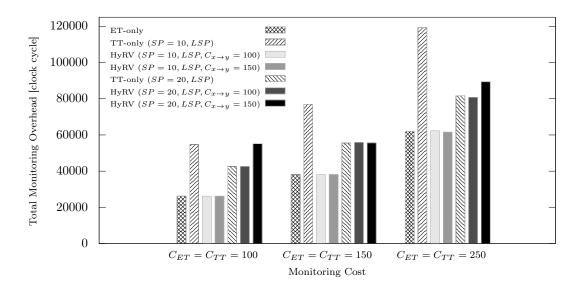

| 5.4 | Monitoring overhead of crc for three monitoring modes under all cost configurations.                   | 60 |

| 5.5 | Monitoring overhead of insertsort for three monitoring modes under all cost configurations | 61 |

|-----|--------------------------------------------------------------------------------------------|----|

|     | Monitoring overhead of fir for three monitoring modes under all cost configurations        | 65 |

# Chapter 1

## Introduction

Software is ubiquitous in many applications and the versatility of software has promoted a rapid growth of complex software systems. Verifying software systems' correctness poses a significant and important challenge to address. In a relatively recent National Institute of Standards and Technology (NIST) report, it is estimated that \$59.6 billion are lost every year from software errors [1]. In a more recent article, Charette highlights some incidents that attribute huge monetary losses due to software failures [2]. For example, Inland Revenue (from the United Kingdom) experienced a \$3.45 billion tax-credit overpayment that were attributed to software errors in 2004-2005. Software failures are not limited to monetary consequences. There are millions of lines of code in modern aircrafts and vehicles. The F-35 Joint Strike Fighter and Boeing's 787 Dreamliner require the use of 5.7 and 6.5 million lines of code, respectively; premium-class automobiles also require software systems to that scale and the complexity of such systems are growing extremely fast [3]. Ensuring software correctness is of utmost importance in these applications because software failures may endanger the safety of the people operating and using them.

In computing systems, *correctness* refers to the assertion that the system satisfies its specification; verification is a way to check for such an assertion [4]. There are traditionally three main verification techniques that are applied in the software domain: theorem proving, model checking, and software testing. All three types of techniques have strengths and weaknesses when they are applied to software systems design and development.

Theorem proving generally involves finding a proof from a set of axioms after express-

ing the system and its properties in some form of mathematical logic. State-of-the-art theorem provers can provide some automation, but typically requires a significant amount of manual effort/interaction to prove the correctness of the system model with respect to its properties [5,6]. Theorem proving is able to cope with an infinite search space.

Model checking [7] on the other hand automates the process of proving the satisfiability of system properties by conducting an exhaustive search on an abstract model that is representative of the system. This search is computationally expensive; it suffers from the state-explosion problem [8]. Binary decision diagrams [9], reduced ordered binary decision diagrams [10] and bounded model checking [11] are some techniques that were developed and applied to make model checking more efficient. However, these techniques are still constrained by the state-explosion problem and become intractable for larger models.

Software testing covers a wide range of diverse methods that are generally incomplete and mainly test for the presence of bugs while verification techniques tests for the absence of bugs [6]. Software testing does not usually provide very high confidence about the correctness of a system, as it only checks for the presence of defects under specific conditions.

Runtime verification [6,12–17] is an emerging lightweight verification technique, where a monitor dynamically checks a system under inspection at run time with respect to the system's specification. Runtime verification complements exhaustive verification methods, such as model checking and theorem proving, as well as incomplete solutions, such as testing and debugging. Runtime verification adopts a high degree of rigour like model checking and theorem proving, but trades off some of the rigour and completeness for practicality and efficiency that is inherent in most online software testing methods and approaches.

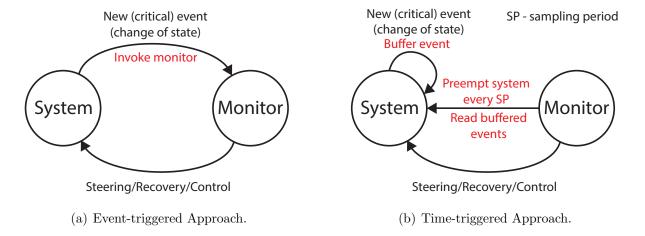

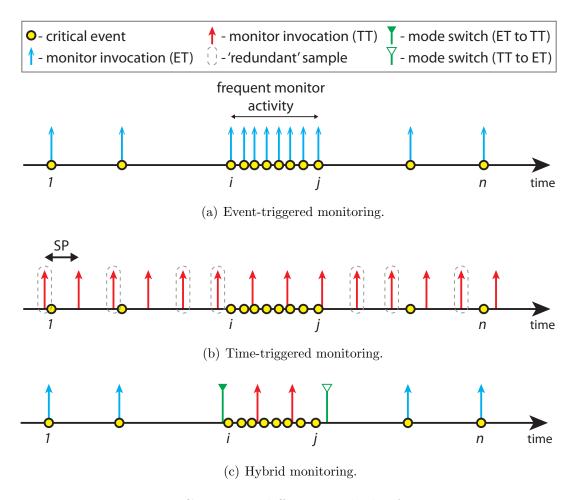

Most techniques in the literature of runtime verification employ monitors that are *event-triggered*. In event-triggered runtime verification, the system under scrutiny is modified to invoke the monitor every time a *critical event* occurs at run time. A *critical event* refers to a change in the program state that may influence the verdict (i.e., the truthfulness) of one or more properties that the system must/should satisfy. Figure 1.1(a) illustrates how a system and an event-triggered monitor would interact.

In recent years, there has been an increasing level of interest in exploring *time-triggered* approaches for runtime verification [18–22]. In time-triggered runtime verification, the

Figure 1.1: Overview of established runtime verification approaches.

monitor typically preempts the system under scrutiny periodically at run time to evaluate the properties of interest. Once the monitor is finished checking the set of system properties, it relinquishes control to the system. The monitoring correctness is a primary concern in time-triggered runtime verification because the monitor may miss critical events between two consecutive samples. One approach to tackle this issue is to buffer critical events into auxiliary memory and have the monitor read the event buffer when it samples the program [18]; other approaches are discussed in Chapter 2. The behaviour of the system and the monitor is illustrated in Figure 1.1(b).

Determining the periodicity of the monitor is dependent on the available computational resources and the maximum tolerable latency allowed for the system to detect and report any system property violation. The time from which a property violation occurs to the time the monitor detects the violation is known as the *detection latency*.

Time-triggered runtime verification is advantageous in certain aspects. First, time-triggered monitors have predictable behaviour and incur predictable overhead. Secondly, time-triggered monitors can potentially reduce the amount of incurred runtime monitoring overhead when the sampling period is increased (or the sampling frequency is decreased).

The deployment of runtime monitors for software systems requires an in-depth understanding of the inherent trade-off between execution time and memory overhead. From the observations made in [18,19], the monitoring overhead with respect to execution time can decrease if the monitor and the system can increase the amount of memory used at run time (or even after, if offline verification is considered). The reverse also holds; if the available memory resources decrease, then the monitor will likely incur greater overhead with respect to execution time.

The work that is presented in this thesis tackles memory overhead and execution time overhead separately in two different ways. The first part of the thesis (see Chapter 4) focuses on making time-triggered runtime verification applicable to larger scale systems by tackling the NP-complete problem of determining the optimal instrumentation scheme that would yield in the lowest amount of auxiliary memory required to preserve correctness in monitoring. The second part of the thesis (see Chapter 5) presents a novel approach, known as hybrid runtime verification, that aims to minimize the amount of time spent in executing verification procedures at run time by combining the advantages of both event-and time-triggered monitoring; hybrid runtime verification is particularly effective when the system encounters both sporadic and bursty critical events at run time.

The approach that one should take highly depends on the nature of the system, the available resources, and the set of properties it should satisfy. For hard real-time systems, predictable monitoring is very important. This is because bursty critical events may cause extremely high monitoring overhead and make the monitor's behaviour hard to predict. As a result, the monitor may cause the system to violate a timing constraint. This would be difficult to debug if the unmonitored system initially satisfies the detected timing violation. Thus, hard-to-predict monitoring behaviour is undesirable. Another benefit of having predictable monitoring for such systems is that the monitors activity can be included in offline schedule computation and verification; this enables designers to check before deployment that timing guarantees will likely not be violated from the added checking at run time. For systems that do not have hard timing deadlines and do not impose tight memory constraints, increasing the efficiency in executing the monitored system with respect to time is beneficial.

## 1.1 Summary of Contributions

The main contributions that are presented in thesis are twofold:

- 1. Minimizing the number of locations where events must be buffered in time-triggered runtime verification given some target sampling period is NP-complete [18]. Solving for the optimal solution is intractable for programs with a large number of critical events, even with state-of-the-art solvers. The first part of this thesis introduces three polynomial-time heuristics that aim to scale the applicability of time-triggered runtime verification and shows that the heuristics provide reasonable sub-optimal instrumentation schemes. This work resulted in a publication to the International Conference on Runtime Verification in 2011 [19].

- 2. Time-triggered runtime verification may reduce the monitoring overhead as the sampling period is increased; however, the monitor can sometimes sample without doing any meaningful work. The second part of this thesis introduces hybrid runtime verification, which aims to exploit the benefits of both event- and time-triggered runtime monitoring to reduce the overall monitoring overhead with respect to execution time. This involves solving an optimization problem that is already difficult to solve for a linear execution trace. To cope with the complexity of the optimization problem, a heuristic is presented that reasonably models the optimization problem. The experimental results demonstrate that the heuristic generally produces monitoring schemes that are equal or better than the most efficient way of monitoring a program using an event- or time-triggered monitor.

#### 1.2 Outline

The rest of the thesis is organized as follows. Chapter 2 presents related work in the literature on methods of improving the efficiency and feasibility of runtime verification. Chapter 3 formally defines and describes all common terminology and concepts that are used in Chapters 4 and 5. Then, Chapter 4 presents three polynomial- time and space heuristics that trade-off optimality for scalability of time-triggered runtime verification.

Some of the secondary observations made in Chapter 4 motivate the work presented in Chapter 5. Chapter 5 explores a novel approach, known as hybrid runtime verification, which attempts to leverage the benefits of both event- and time-triggered monitoring techniques to reduce the runtime monitoring overhead. Chapter 6 summarizes the key findings of the work presented in Chapters 4 and 5. Finally, Chapter 7 describes some future research directions and ideas that may extend the work presented in this thesis.

## Chapter 2

## Related Work

Existing work and literature on runtime verification and monitoring is presented and discussed in this chapter. Most of the work cited in this chapter pertain to methods and techniques that are used to make monitors for runtime verification more efficient.

In classic runtime verification [13, 23, 24], a system is composed with an external observer, called the monitor. Monitors in runtime verification are typically automatically synthesized from one or more properties that the system should satisfy [14]; the monitor routinely checks the system against these properties and is responsible for detecting property violations at run time. Most work in the literature of runtime verification adopts and uses *event-triggered* monitors [25], where every critical change in the state of the system causes a direct invocation of the monitor for analysis.

Runtime verification has mostly been studied in the context of linear temporal logic (LTL) properties [17, 24, 26–28] and, in particular, safety properties [29, 30]. Other languages and frameworks have also been developed for facilitating specification of temporal properties [31–33]. [34] considered runtime verification of  $\omega$ -languages. In [35], the authors address runtime verification of safety-progress [36, 37] properties.

**Organization.** The rest of this chapter describes some recently published work that address the challenges in making runtime verification applicable and feasible to more software systems. Section 2.1 presents recent literature that address the issue of reducing the overhead cost of monitoring in runtime verification. Section 2.2 focuses on surveying literature where authors employ time-triggered techniques for runtime verification.

### 2.1 Reducing Runtime Verification Overhead

Dwyer et al. [38] aim to dynamically adjust the runtime monitoring scheme by incorporating the semantics of the system properties of interest and the program state to reduce the number of monitor invocations at run time. The decision to skip or execute instrumentation code is done at run time. Their framework, known as Adaptive Online Program Analysis (AOPA), guarantees that the monitor will correctly detect property violations and empirically observe that the monitoring overhead is reduced because of the optimizations performed on both monitor synthesis and program instrumentation. AOPA runs within Java; the dynamic behaviour of the monitored system is controlled within a Java virtual machine. The authors choose to have the monitors verify the properties online to further reduce the overhead costs of post-processing potentially very large buffers offline.

Barringer et al. [39] demonstrate that a large set of logics used to express safety and liveliness system properties may be expressed using their unifying logic known as EAGLE. They further show that the monitors that are synthesized from properties expressed in EAGLE logic do not require storing the execution trace, which reduces monitoring overhead with respect to memory.

Bodden et al. [40] describes an approach that reduces the monitoring overhead by statically analyzing the program under scrutiny along with its corresponding tracematches to eliminate critical events that need not be monitored. A tracematch defines a runtime monitor using a regular expression over an alphabet of critical events in the program. The monitoring technique that they base their method on is aspect-oriented programming (AspectJ). The potential reduction of tracematches occurs in three stages, so that the user has control over the precision of the reduction; each subsequent stage in their procedure increases in computational complexity.

Bodden et al. [41] present two partitioning schemes that alleviate runtime monitoring overhead of widely used and deployed large scale systems. The partitioning schemes distribute the monitoring workload across all of the deployed systems; each instance either will monitor regions of the program or will temporally toggle the monitor so that the overhead is not noticeable (approx. 5% overhead). In this work, the schemes that the authors present ensures that no false positives are reported (but the monitors may report false negatives), thereby making the debugging information easier to use.

Huang et al. [42] introduced a rigorous non-linear feedback controller for the monitor and the monitored program so that the monitor does not cause overload situations. Overload situations are caused by bursts of critical instructions that are monitored over a short period of time. Software monitoring with controllable overhead (SMCO) strives to maintain the monitoring overhead below the design threshold (or reference). The feedback controller controls whether the program will be monitored or not. When the monitor approaches or exceeds the target overhead, the monitor is effectively switched off by executing the original of the program. When the monitoring overhead is less than the target overhead, the monitor is invoked by the program executing the instrumented version.

The authors aim to reduce the overhead (with respect to time) incurred from toggling on and off the monitor by making a copy of the the original source code and instrumenting the copy. The monitored program inserts guards at the beginning of function calls to determine whether the un-instrumented or instrumented copy of the program will execute.

While SMCO effectively controls the monitoring overhead, it does not guarantee that all properties are correctly monitored because in overload situations, the monitor is turned off and does not process any critical events that are generated from the program being scrutinized. Since the monitoring accuracy is not 100%, this approach is unsuitable for applications that require all violations to be detected. Furthermore, the authors assume 'infinite' application memory space and double the size of the source code of the program being monitored. In memory-constrained systems, this approach may be infeasible.

Zhu et al. [43] present a hard real-time runtime monitoring solution. They bound the latency of error detection by performing schedulability analysis on the monitor's execution time requirements (i.e. monitoring budget) and its overhead with the real-time schedule of the system that is being scrutinized. Although real-time tasks are assumed to be periodic, the release of critical events (also known as PVEs in [43]) are aperiodic. The main goal of this work is on time-aware instrumentation.

### 2.2 Time-triggered Runtime Verification

Pike et al. [21] proposed an embedded domain-specific language in Haskell, known as *Copilot*, that compiles into small constant-time and constant-space C monitors that may

be used in time-sensitive software systems (i.e. hard real-time). The monitors that are generated using Copilot periodically sample the program state to verify system properties. The authors of [21] do not consider missing state changes that result from sampling because within a hard real-time context, the monitor and program are assumed to share a global sense of time and a static periodic schedule. The monitors synthesized using Copilot are conservative in that they will report false positives (of system property violations), true positives and true negatives, but not false negatives.

While the work in [21] is suitable specifically for hard real-time applications, it is difficult to apply this work to soft-RT or non-RT applications. The rigour and predictability of real-time systems allowed the authors to synthesize correctly functioning monitors. However, the periodicity and predictability of real-time systems does not hold for other types of systems, so the monitor's correctness is not guaranteed in other applications. Furthermore, Copilot synthesized monitors are only capable of monitoring global variables, which may encourage poorly encapsulated (and difficult to manage) code. This may cause issues in software maintainability for large-scale software systems.

Stoller et al. [22] present a technique called runtime verification with state estimation (RVSE), which aims to cope with the pitfalls of time-triggered runtime verification with respect to program correctness by utilizing a hidden Markov model of the monitored program to estimate missing program states incurred from sampling-induced gaps. The state estimation of the hidden Markov model determines the probability of a state sequence given an observed sequence, which can then be used to infer the probability that a system property is satisfied by an execution of the program.

The monitor's correctness is not guaranteed because this method utilizes state estimation. This technique may be useful in determining potential system property violation (useful bug reporting), but cannot be deployed in systems that require the monitor to report all violations confidently.

Bartocci et al. [44] extends the work of [22] and [42] by combining the two approaches together to form a more complete monitoring framework with controllable overhead. Specifically, the authors of [44] leverage RVSE to infer the likelihood of property satisfaction/violation whenever the monitor is temporarily disabled for overhead control purposes. They also extend the theory behind RVSE and introduce techniques that can predict the *critical-ity level* of a system property, which is a function of the expected distance to the violation

of the property. The criticality levels of system properties of interest can then determine the allocation of the available monitoring resources. While [44] improves the usability and usefulness of [42], this runtime verification framework does not guarantee correct state reconstruction.

Another approach to time-triggered runtime verification was presented by Bonakdarpour et al. [18], where the correctness of the monitor and the verification process is achieved by determining the longest possible sampling period of the monitor (without instrumentation). The authors consider buffering critical events into auxiliary memory as a viable way to increase the sampling period while preserving correct program state reconstruction. Extending the longest sampling period involves solving an NP-complete optimization problem that aims at minimizing the size of auxiliary memory required for the monitor to correctly reconstruct all program state sequences at run time. The majority of the work presented in the remaining chapters of this thesis extends this particular approach.

Navabpour et al. [20] propose methods of time-triggered runtime verification that utilize symbolic execution [45] to predict the set of all feasible paths of the system prior to run time. From the set of predicted paths, the longest sampling period is computed. At run time, the monitor will adjust its sampling period based on the path that is taken by the program. The authors observe that some execution paths contain unevenly distributed critical events; to further refine this monitoring technique, they consider determining code regions within each path and assign the monitor to vary the sampling period depending on the code region. This path-aware approach for time-triggered runtime verification aims to reduce the amount of runtime monitoring overhead incurred from sampling by enabling the monitor to adapt to local sampling periods rather than a global sampling period. Global sampling periods do not efficiently use the available monitoring resources.

## Chapter 3

## **Preliminaries**

In this chapter, the common terms and concepts used throughout the subsequent chapters are defined and explained. Section 3.1 introduces terms and symbols that are used in the definitions presented in the rest of the chapter. Section 3.2 explains some basic concepts in control-flow analysis that is required for determining correct monitoring behaviour in time-triggered runtime verification. Section 3.3 formally describes how control-flow analysis is used to determine a 'safe' sampling period for runtime verification and how the sampling period can be effectively increased to reduce the monitoring activity.

## 3.1 Checking System Properties at Run Time

Runtime verification consists of a monitor and a program/system under inspection. The monitor is typically synthesized from one or more properties that the system should satisfy and runs in parallel with the system at run time. The program invokes the monitor whenever it executes an event that may change the logical result of one or more properties in event-triggered runtime verification. In time-triggered runtime verification, the monitor interrupts the program execution at regular time intervals to observe the state(s) of the program and check the set of properties the system is expected to satisfy.

The state of the program is determined by evaluating the value of a set of variables being monitored. Formally, let P be a program and  $\Pi$  be a logical property (e.g., in LTL),

where P is expected to satisfy  $\Pi$ . Let  $\mathcal{V}_{\Pi}$  denote the set of variables that participate in  $\Pi$ . Let a *critical event* be a change of any variable in  $\mathcal{V}_{\Pi}$ .

In event-triggered runtime verification, the instrumented version of P will call/invoke the monitor to evaluate  $\Pi$  whenever P encounters a critical event. Invoking the monitor every time that some variable in  $\mathcal{V}_{\Pi}$  changes guarantees correct program state reconstruction at run time.

In time-triggered runtime verification, a monitor reads the value of variables in  $\mathcal{V}_{\Pi}$  at a fixed sampling frequency and evaluates  $\Pi$ . Accurate program state reconstruction of P between two consecutive samples is the main challenge in using this mechanism; e.g., if more than one critical event occurs between two consecutive samples, then the monitor may fail to detect violations of  $\Pi$ . The monitor must sample at a 'safe' rate to facilitate correct program state reconstruction of P, typically determined by applying control-flow analysis [18–20].

## 3.2 Control-flow Analysis

In control-flow analysis, control-flow graphs are used to represent the program P. Definition 1 formally defines what a control-flow is and what it represents:

**Definition 1** The control-flow graph (CFG) of a program P is a weighted directed simple graph  $CFG_P = \langle V, v^0, A, w \rangle$ , where:

- ullet V: is a set of vertices, each representing a basic block of P.

- $v^0$ : is the initial vertex with in-degree 0, which represents the initial basic block of P.

- A: is a set of arcs (u, v), where  $u, v \in V$ . An arc (u, v) exists in A if and only if the execution of basic block u immediately leads to the execution of basic block v.

- w: is a function w: A → N, which defines a weight for each arc in A. The weight

of an arc represents the best-case execution time (BCET) of the source basic block.

The best-case execution times are expressed in terms of the number of clock cycles

required to execute the basic blocks.

```

1  scanf("%d", &a);

2  if ( a % 2 == 0 ) {

3    printf("%d is even", a);

4  } else {

5       b = a / 2;

6       c = a / 2 + 1;

7    printf("%d is odd", a);

8  }

9  d = b + c;

10  end program

```

Figure 3.1: A simple C program.

A basic block in control-flow analysis represents a linear sequence of instructions in a program P without any jumps or jump targets (i.e., goto statements in C). In other words, only the last instruction in a basic block can be a branching statement. A critical basic block is a basic block that contains one or more critical events/instructions.

Control-flow graphs are used in time-triggered runtime verification to determine the maximum sampling period that the monitor can operate with while preserving correct program state reconstruction for checking the set of system properties. The next subsection describes the operations and procedures used to determine the sampling period.

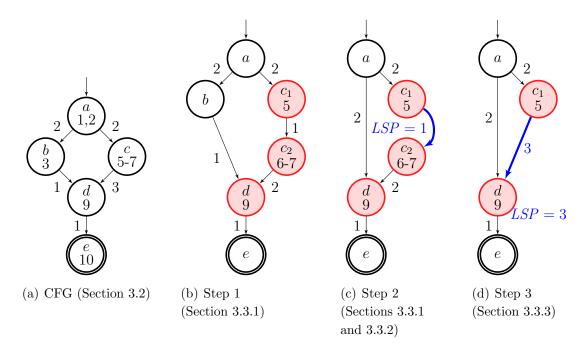

Consider the C program in Figure 3.1. Figure 3.2(a) shows the resulting control-flow graph of the C program. The arc weights in the control-flow graph are computed based on the assumption that the BCET of each line of code is one time unit. Vertices of the graph in Figure 3.2(a) list the corresponding line numbers of the C program in Figure 3.1.

### 3.3 Time-triggered Runtime Verification

### 3.3.1 Transforming Control-flow Graphs

The control-flow graph of P must go through several transformations to identify the maximum possible period that a monitor may sample P with while guaranteeing accurate program state reconstruction.

Let  $CFG_P = \langle V, v^0, A, w \rangle$  be a control-flow graph represent to the program P. The first procedure to perform on  $CFG_P$  is to determine the *critical vertices*. A *critical vertex* is a

Figure 3.2: Steps for obtaining optimized instrumentation and longest sampling period.

vertex  $v \in V$  that represents a critical basic block (i.e., the basic block contains instructions that change one or more variables in  $\mathcal{V}_{\Pi}$ ). For a critical basic block/vertex that contain more than one critical instruction, the vertex must be split into multiple vertices, where each vertex represents a critical basic block with exactly one critical event/instruction. Revisiting the program shown in Figure 3.1, if variables b, c, and d are in  $\mathcal{V}_{\Pi}$ , then lines 5, 6 and 9 are critical instructions. Since instructions in lines 5 and 6 are critical and they both reside in basic block c, c will be split into  $c_1$  and  $c_2$  as shown in Figure 3.2(b); the highlighted vertices in the figure denote the critical basic blocks.

After ensuring that each critical vertices in the control-flow graph contain exactly one critical instruction, the graph is transformed into a *critical control-flow graph*. A critical control-flow graph has the following characteristics:

- The initial vertex is non-critical.

- The graph may possible contain a non-critical vertex with out-degree zero (i.e., if the program terminates).

• All other vertices in the graph are critical vertices. Figure 3.2(c) shows the corresponding critical control-flow graph of Figure 3.2(b).

The function T(CFG, v) is defined to facilitate the transformation of a control-flow graph into a critical control-flow graph. The inputs of T are the current control-flow graph, CFG, and a non-critical vertex  $v \in V$  that should be removed from CFG, where V is the set of vertices in CFG. T(CFG, v) is only applicable when  $v \in V \setminus \{v^0\}$  and the out-degree of v is positive. The output of T(CFG, v) is a modified control-flow graph,  $CFG' = \langle V', v^0, A', w' \rangle$ , and is obtained by the following ordered steps:

- 1. Let A'' be the set  $A \cup \{(u_1, u_2) | (u_1, v), (v, u_2) \in A\}$ . Observe that if an arc  $(u_1, u_2) \in A$ , then A'' will contain parallel arcs (such arcs can be distinguished by a simple indexing or renaming scheme). Parallel arcs are eliminated in Step 3.

- 2. For each arc  $(u_1, u_2) \in A''$ ,

$$w'(u_1, u_2) = \begin{cases} w(u_1, u_2) & \text{if } (u_1, u_2) \in A \\ w(u_1, v) + w(v, u_2) & \text{if } (u_1, u_2) \in A'' \setminus A \end{cases}$$

(3.1)

- 3. If there exist parallel arcs from vertex  $u_1$  to  $u_2$ , only include the arc with minimum weight in A''.

- 4. Finally, the set of arcs and vertices are updated:

$$A' = A'' \setminus \{(u_1, v), (v, u_2) \mid u_1, u_2 \in V\}$$

(3.2)

$$V' = V \setminus \{v\} \tag{3.3}$$

**Special Case:** If u and v are two non-critical vertices and  $(u, v), (v, u) \in A$ , then removing one of the vertices, e.g., u, results in the self-loop (v, v). This self-loop may safely be removed. A loop that does not contain critical instructions does not affect the sampling period.

Applying T(CFG, v) on all non-critical vertices  $V \setminus \{v^0\}$  with positive out-degrees in  $CFG_P$  results in the critical control-flow graph of P. For the example program in Figure 3.1, the corresponding critical control-flow graph obtained by first ensuring that all critical vertices contain exactly one critical instruction followed by applying the transform T(CFG, v) is shown in Figure 3.2(c).

#### 3.3.2 Determining the Longest Sampling Period (LSP)

The longest sampling period (LSP) is the maximum sampling period the monitor can sample with and preserve correct program state reconstruction. In other words, the longest sampling period is the minimum timespan between two successive changes of any two variables in  $\mathcal{V}_{\Pi}$  (i.e., the minimum distance between all pairs of critical vertices). The longest sampling period may be computed using either the control-flow graph or critical control-flow graph of a program P. Definition 2 formally defines the longest sampling period using both types of control-flow graphs.

**Definition 2** Let  $CFG_P = \langle V, v^0, A, w \rangle$  be the control-flow graph of a program P such that each critical vertex contains exactly one critical event/instruction. Let  $V_c \subseteq V$  be the set of vertices that correspond to critical basic blocks of  $CFG_P$ ; and  $\Pi_c$  be the set of paths  $\langle v_h \to v_{h+1} \to \cdots \to v_{k-1} \to v_k \rangle$  in CFG such that  $v_h, v_k \in V_c$  and  $v_{h+1}, \ldots, v_{k-1} \in V \setminus V_c$ . The longest sampling period (LSP) for  $CFG_P$  is

$$LSP_{CFG_P} = \min_{\pi \in \Pi_c} \left\{ \sum_{\substack{(v_i, v_j) \in A \\ v_i, v_j \in \pi}} w(v_i, v_j) \right\}$$

(3.4)

Alternatively, apply the transformation function T(CFG, v) to  $CFG_P$  on the applicable non-critical vertices to create the critical control-flow graph of P,  $CFG'_P = \langle V, v^0, A, w \rangle$ . Again, let  $V_c \subseteq V$  be the set of critical vertices in  $CFG'_P$ . The longest sampling period (LSP) for  $CFG'_P$  is

$$LSP_{CFG'_{P}} = \min\{w(v_{1}, v_{2}) | (v_{1}, v_{2}) \in A \land v_{1} \in V_{c}\}$$

(3.5)

Recall that the critical control-flow graph of the program in Figure 3.1 is shown in Figure 3.2(c). The arc weights  $w(c_1, c_2) = 1$  and  $w(c_2, d) = 2$  are the possible values of the longest sampling period for this program. Therefore, by Definition 2, the longest sampling period for the program is 1. In other words, if the monitor samples this program with a periodicity of 1, all potential property violations can be detected.

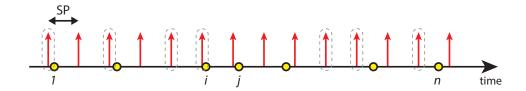

Figure 3.3: Illustrating redundant samples in time-triggered runtime verification.

#### 3.3.3 Increasing the Longest Sampling Period

While sampling at the longest sampling period computed from the critical control-flow graph guarantees correct program state reconstruction, it may impose a significant amount of monitoring overhead. Consider the execution trace shown in Figure 3.3, where the critical events are marked on the timeline as circles. Assume that the timespan between events i and j ultimately determines the longest sampling period. The monitor must sample with this sampling period (or smaller) to preserve correct program state reconstruction. To minimize the monitoring overhead, the monitor should sample with the longest sampling period (i.e., to minimize total number of samples at run time). Figure 3.3 illustrates when the monitor would sample the program with the longest sampling periodThe dotted ovals around some of the arrows (i.e. samples taken by the monitor) are samples where the monitor does not do any meaningful work because no critical events occurred during those sampling periods. Such samples are called redundant samples.

To reduce the number of redundant samples, the sampling period must be increased. To preserve the correctness in monitoring and program state reconstruction while increasing the sampling period, another graph transformation function is defined. This function is known as the *instrumenting transformation*. Let IT(CFG, v) be the instrumenting transform function. This function may be applied to critical vertices in the critical control-flow graph,  $CFG'_P$ . IT(CFG, v) consists of the following ordered steps:

- 1. Let  $(u, v) \in A$ , where v is a critical vertex. Apply transformation  $T(CFG'_P, v)$ .

- 2. Append an instruction  $i': a' \to a$  to the sequence of instructions corresponding to basic block u, where a' is an auxiliary memory location. The instructions of basic block u is now  $inst_u = inst_u \langle i, i' \rangle$ .

Note that adding the extra instruction i' does not affect the calculation of the sampling period. This is because adding instrumentation only increases the best case execution time of a basic block. By maintaining the calculated sampling period, no critical instruction is overlooked.

Unlike non-critical vertices, the issue of loops involving critical vertices need to be handled differently. Suppose that u and v are critical vertices and  $(u,v),(v,u) \in A$ . Consider removing u. This results in a self-loop (v,v), where w(v,v) = w(u,v) + w(v,u). The loop iterates an unknown number of times at run time, so it is difficult to determine the upper bound on the size of auxiliary memory required to collapse vertex v. To ensure correctness, the transformation IT is forbidden for critical vertices that have self-loops.

Figure 3.2(d) illustrates this instrumenting transformation on critical vertex  $c_2$ . Applying T(CFG, v) with  $v = c_2$ , the resulting graph returned removes  $c_2$  and an arc is added directly between vertices  $c_1$  and d, with the sum of weights of arcs  $(c_1, c_2)$  and  $(c_2, d)$  in the previous graph (see Figure 3.2(c)). The second step of the transformation inserts an instruction to save the critical event that is in  $c_2$ , thereby effectively increasing the longest sampling period to 3.

The maximum violation detection latency (i.e., the time elapsed between the occurrence of a property violation and the detection of the violation) of  $\Pi$ , the availability of auxiliary memory and other system constraints limit the number of times IT(CFG, v) can be applied to increase the longest sampling period.

## Chapter 4

# Heuristics for Time-triggered Runtime Monitoring

#### 4.1 Introduction

In the literature, deploying monitors for runtime verification involves instrumenting the program under inspection, so that upon occurrence of events (e.g., change in a variable's value) that may change the truthfulness of a property, the monitor is called to (re-)evaluate the property; this method is known as event-triggered runtime verification, because each change prompts a re-evaluation. Event-triggered runtime verification suffers from two drawbacks: (1) unpredictable overhead, and (2) possible bursts of events at run time. These defects can lead to undesirable transient overload situations in time-sensitive systems such as real-time embedded safety-critical systems. To address these issues, Bonakdarpour et al. introduced a notion of time-triggered runtime verification [18], where a monitor runs in parallel with the program and samples the program state periodically to evaluate a set of system properties.

The main challenge in time-triggered runtime verification is to guarantee accurate program state reconstruction when the monitor samples the program. [18] introduced an optimization problem where the objective is to find the minimum number of critical events that need to be buffered for a given sampling period. Consequently, the time-triggered

Figure 4.1: Memory usage vs. sampling period [18].

monitor can successfully reconstruct the state of the program between two successive samples using the buffering scheme returned by solving the optimization problem. [18] proved that this optimization problem is NP-complete and proposed a transformation of this problem to an instance of the *integer linear programming* (ILP) problem, which is described in Section 4.2. Transforming this problem enables the capability of employing powerful ILP-solvers to identify the minimum buffer size and instrumentation instructions for state reconstruction. It is possible to solve the corresponding ILP model for some applications, but for larger applications, the complexity of the problem poses a serious stumbling block.

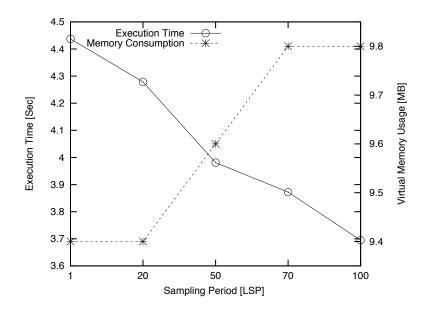

The intractability of the optimization problem prompted an investigation of applying efficient (i.e., polynomial-time) heuristics to identify near-optimal solutions for the optimization problem. In [18], the authors observed that the impact of increasing the monitor's sampling period significantly reduced the overall execution time of the monitored program with a very small (almost negligible) increase in runtime memory usage of the monitored program. Figure 4.1, taken from [18], shows the total execution time and memory usage of blowfish, a benchmark program from MiBench [46], for target sampling periods of 1, 20, 50, 70, and 100 times the LSP. When the target sampling period is increased to  $100 \times LSP$ , the monitored program's memory usage only increased by 4%. Other experimental data

in [18] show similar patterns in the results. This observation suggests that nearly optimal solutions to the optimization problem are likely sufficiently effective.

With this motivation, three polynomial-time heuristics were developed to find near-optimal solutions to the optimization problem defined in [18]. All three heuristics are over-approximations and, hence, sound (they do not cause overlooking of events to be monitored). The first heuristic is a greedy algorithm that aims at instrumenting variables that participate in many execution branches. The second heuristic is based on a 2-approximation algorithm for solving the minimum vertex cover problem. Intuitively, this heuristic instruments variables that are likely to cover all cases where variable updates occur within time intervals less than the target sampling period. The third heuristic is a genetic algorithm, an evolutionary heuristic where the evolution of the population aims to minimize the number of variables that need to be instrumented and buffered.

The collected experimental data show that these three heuristics are significantly faster than the ILP-based solution described in [18]. More importantly, the solutions returned by all three algorithms lead to a negligible increase in instrumentation overhead and total memory usage at run time as well as negligible increase in the total execution time of the monitored program. Also, the experimental data show that extra instrumentation instructions are evenly distributed between samples. Moreover, the genetic algorithm generally produces instrumentation schemes closest to the optimal solution as compared to the other heuristics. The experimental results empirically suggest that the NP-completeness of the optimization problem is not an obstacle when applying time-triggered runtime verification in practice.

Organization. The rest of this chapter is organized as follows. Section 4.2 summarizes the integer linear programming model used by Bonakdarpour et al. in [18]. Section 4.3 describes and illustrates the three heuristics, which include the greedy and minimum vertex-cover heuristics, as well as the genetic algorithm. Experimental results are presented and analyzed in Section 4.4. Section 4.5 finishes the chapter with some concluding remarks.

# 4.2 Optimizing Memory Overhead in Time-triggered Runtime Verification

Given a critical control-flow graph, the goal of [18] is to optimize two factors through a set of IT(CFG, v) transformations: (1) minimizing auxiliary memory, and (2) maximizing sampling period. Bonakdarpour et al. showed that this optimization problem is NP-complete [18]. The remainder of this section is organized as follows. Section 4.2.1 briefly states the integer linear programming problem in its general form. After that, Section 4.2.2 describes the integer linear programming model used by the authors in [18] to solve the optimization problem. Chapter 4 extends this work by exploring more efficient algorithms to compute near-optimal solutions for this problem.

#### 4.2.1 Integer Linear Programming

The integer linear programming (ILP) problem is of the form:

$$\begin{cases}

\text{Minimize} & c.\mathbf{z} \\

\text{Subject to} & A.\mathbf{z} \ge \mathbf{b}

\end{cases}$$

(4.1)

where A (a rational  $m \times n$  matrix), c (a rational n-vector) and  $\mathbf{b}$  (a rational m-vector) are given, and  $\mathbf{z}$  is an n-vector of integers to be determined. In other words, solving this problem involves finding the minimum of a linear function over a feasible set defined by a finite number of linear constraints. It can be shown that a problem with linear equalities and inequalities can always be put in the above form, implying that this formulation is more general than it might look.

### 4.2.2 Integer Linear Programming Model

Let  $CFG'_P = \langle V, v^0, A, w \rangle$  be the critical control-flow graph of a program P. In the ILP mapping of the optimization problem, the following sets of integer variables are defined:

- $\mathbf{x} = \{x_v | v \in V\}$ , where  $x_v$  is a binary integer variable.  $x_v \in \{0, 1\}$ . If  $x_v = 1$ , then v is removed from V and the critical event in the basic block corresponding to v is buffered as history in auxiliary memory. If  $x_v = 0$ , then v remains in V and no instrumentation is required to save the critical event in the basic block corresponding to v in auxiliary memory.

- $\mathbf{a} = \{a_v | v \in V\}$ , where  $a_v$  are integer variables that represent the weight of arcs originating from vertex v.

- $\mathbf{y} = \{y_v, y_v' | v \in V\}$  are choice variables, where  $y_v$  and  $y_v'$  are integer variables. The use of choice variables are described later.

#### 4.2.2.1 Objective Function

The *objective function* of this ILP model is:

$$\min \sum_{v \in V} x_v \tag{4.2}$$

Minimizing Equation 4.2 will minimize the set of vertices removed from  $CFG'_P$ . The set of vertices removed indicate the critical events in the program P that must be instrumented to save the event into auxiliary memory to increase the effective longest sampling period while preserving the correctness of program state reconstruction.

#### 4.2.2.2 Initial Basic Block Constraints

The initial basic block has several unique constraints. The vertex  $v^0$  corresponds to the initial basic block in the program P. The following constraints are imposed on  $v^0$ .

$$x_{v^0} = 0 \tag{4.3}$$

$$a_{v^0} = w(v^0) (4.4)$$

These two constraints ensure that the initial basic block is never included in the set of removed (i.e., instrumented) vertices because the monitor should sample the at the beginning of the program to extract the initial values of the variables in  $\mathcal{V}_{\Pi}$ .

#### 4.2.2.3 Constraints on Arc Weights and Internal Vertices

After performing the necessary instrumenting transformations (i.e., IT(CFG, v)) on  $CFG'_P$ , the effective longest sampling period should be equal or larger that the target sampling period that the user specifies. Let SP be the target longest sampling period. Then for every arc  $(u, v) \in A$ ,

$$a_u + SP \cdot x_v \ge SP \tag{4.5}$$

In other words, the solution should ensure that all arc weights become at least SP. If any instance of this constraint cannot be met, then no solution exists such that P can be sampled at SP while preserving correctness in program state reconstruction.

Whenever a vertex is removed by applying the transformation IT(CFG, v), the arc weights will change. The arc weight of vertex v,  $a_v$ , is subject to two different cases:

Case 1 If  $x_v = 0$  then  $a_v = w(v)$

Case 2 If  $x_v = 1$  then  $a_v = w(v) + w(u)$ , where  $(u, v) \in A$ . Even though vertex v is removed upon applying IT(CFG, v),  $a_v$  is used to retain the value of the newly created arc for simplicity. Also, outgoing arcs from u automatically satisfy Equation 4.5.

To enforce mutual exclusivity of these two cases in the model and correct arc weights, the set of choice variables,  $\mathbf{y}$ , are used. The choice variables in this model exhibit the following properties:

**Property 1:**  $y_v$  and  $y'_v$  are such that one of them is zero and the other is  $a_u$ . This property enforces mutual exclusivity.

**Property 2:** If

$$x_v = 1$$

, then  $y_v = a_u$  and  $y'_v = 0$ . If  $x_v = 0$ , then  $y_v = 0$  and  $y'_v = a_u$ .

A special data structure, called *Special Ordered Set Type 1*  $(sos_1(...))$  [47], is used to enforce the first property. This data structure ensures that at most one variable can take on a non-zero value. The constraints of the two properties may be expressed as:

$$y_v + y_v' = a_u \tag{4.6}$$

$$sos_1(y_v, y_v') \tag{4.7}$$

$$1 \le x_v + y_v' \le a_u \tag{4.8}$$

The following constraints implement Cases 1 and 2, respectively.

$$w(v) + a_u - y_v' = a_v (4.9)$$

$$y_v + w(v) = a_v \tag{4.10}$$

These five constraints are duplicated for each incoming arc to vertex v. Since the depth of nested conditional statements is not normally high, it is unlikely that models of programs would cause an explosion in the number of a-variables in the model.

## 4.2.2.4 Loop Constraint

To ensure that self-loops are not removed, one more constraint is added to the ILP model. For each cycle  $v_1 \to v_2 \to \cdots \to v_n \to v_1$ , at most n-1 vertices can be removed using IT(CFG, v):

$$\sum_{i=1}^{n} x_{v_i} \le n - 1 \tag{4.11}$$

During the construction of the (critical) control-flow graph, cycles are already detected, so there is no need to explore the graph again to identify them.

# 4.3 Heuristics

In order to tackle the intractability of the optimization problem for larger software systems, [18] proposed a mapping of the problem to an instance of ILP. The ILP model enabled the authors to utilize state-of-the-art ILP-solvers to solve the models for relatively small benchmark programs. Some additional experiments were conducted on programs from the same benchmark using this ILP mapping. The results are tabulated in Table 4.1. The ILP solver's performance quickly degrades as the size of the critical control-flow graph increases.

With the observation described in Section 4.1 that trading off small amounts of memory can significantly increase the effective longest sampling period, three heuristics were explored. Each heuristic is described in the remainder of this section. All three heuristics take a control-flow graph G and a desired sampling period SP as input and return a set

## Subroutine 4.1 PruneCFG(G,SP)

```

1: for v \in CFG.V do

2: if (w(u,v) > SP \ \forall (u,v) \in CFG.A) \land (w(v,u) > SP \ \forall (v,u) \in G.A) then

3: G = \text{CollapseNode}(G,v)

4: end if

5: end for

6: return G

```

U of vertices to be deleted as prescribed by the transformation IT(CFG, v) defined in Section 3.3.3. This set identifies the location where additional instructions should be interleaved in the program under examination to buffer critical events for the time-triggered monitor to process upon the next sample it takes.

In the remainder of this section, the control-flow graph shown in Figure 4.2(a) will be used to illustrate how the various heuristics work. In the greedy and minimum vertex covered based heuristics, both of the heuristics initially go through a procedure referred to as pruning the input control-flow graph. Pruning a control-flow graph involves removing all vertices whose weights of all its incoming and outgoing arcs are greater than or equal to SP by applying the transformation T(CFG, v) defined in Section 3.3.1. In the two heuristics that prune the input control-flow graph, such vertices may be safely ignored because the longest sampling period is unaffected by these vertices. The procedure to prune a control-flow graph is shown in Subroutine 4.1. Subroutine 4.1 calls Subroutine 4.2 to 'collapse' (or remove) the selected node from the current control-flow graph. Note that Subroutine 4.2 is equivalent to the function T(CFG, v). For the example shown in Figure 4.2(a), Figure 4.2(b) shows the resulting graph after pruning when SP = 3. Vertex h in this case is removed because both the incoming and outgoing arcs are greater than or equal to SP.

# Subroutine 4.2 CollapseNode(G, node)

```

1: Incoming = \{u : (u, node) \in G.A\}

2: Outgoing = \{v : (node, v) \in G.A\}

3: for u \in \text{Incoming do}

for v \in \text{Outgoing do}

4:

if (u, v) \in G.E then

5:

w(u, v) = \min\{w(u, v), w(u, \text{node}) + w(\text{node}, v)\}\

6:

else

7:

w(u, v) = w(u, \text{node}) + w(\text{node}, v)

8:

end if

9:

end for

10:

11: end for

12: Destroy all incoming and outgoing arcs to node

13: Remove node from G

14: return G

```

Figure 4.2: CFG used for illustrating heuristics.

# Heuristic 4.3 Greedy

**Input:** A critical control-flow graph  $G = \langle V, v^0, A, w \rangle$  and target sampling period SP. **Output:** A set U of vertices to be deleted from G.

```

1: U := \{\};

2: G := \operatorname{PruneCFG}(G, SP);

3: while (MW(G) < SP \land U \neq V) do

4: v := \operatorname{GreedySearch}(G);

5: G := \operatorname{CollapseVertex}(G, v);

6: U := U \cup \{v\};

7: end while

8: if (U = V) then declare failure;

9: return U;

```

# 4.3.1 Heuristic 1: Greedy Heuristic

The first heuristic presented is a simple greedy algorithm (see Heuristic 4.3). The explanation of the heuristic is illustrated by using the example control-flow graph shown in Figure 4.2(a) and SP = 3:

- First, it prunes the input control-flow graph G (Line 2). After pruning the graph in Figure 4.2(a), the graph shown in Figure 4.2(b) is obtained.

- Next, it explores G to find the vertex, v, incident to the maximum number of incoming and outgoing arcs whose weights are strictly less than SP (Line 4). The intuition behind the selection of this vertex to delete/collapse is that such a vertex results in removing a high number of arcs whose weights are less than SP; this should have a greater (if not the greatest) impact on increasing the longest sampling period of the graph. From the pruned graph shown in Figure 4.2(b), vertex c would be the first selected candidate to greedily collapse because it has a total of 3 incoming and outgoing arcs combined that are less than SP (see Figure 4.3(a)). The other

## Subroutine 4.4 GreedySearch(G,SP)

```

1: bestcount = 0

2: node = \emptyset

3: for v \in G.V do

4: if |\{a:(u,v) \in V.A, u \in G.V \land w(u,v) = SP\} \cup \{a:(v,u) \in V.A, u \in G.V \land w(v,u) = SP\}| > \text{bestcount then}

5: bestcount = |\{a:(u,v) \in V.A, u \in G.V \land w(u,v) = msp\} \cup \{a:(v,u) \in V.A, u \in G.V \land w(v,u) = msp\}|

6: node = v

7: end if

8: end for

9: return node

```

candidates for collapsing have fewer than 3 incoming and outgoing arcs whose weights are less than SP.

- Then, it collapses vertex v identified on Line 4. This operation (Line 5) results in merging incoming arcs to v with outgoing arcs from v in the fashion described in the transformation function T(CFG, v). Applying this transformation on vertex c in the example results in the graph shown in Figure 4.3(b).

- Obviously, the basic block corresponding to vertex v contains a critical instruction that requires buffering (i.e., added instrumentation to save the event into memory). Thus, v is added to U (Line 6). Note that Lines 5 to 6 is performs actions that are very similarly to the transformation IT(CFG, v).

- Lines 3-7 are repeated until the longest sampling period of G is greater than or equal to SP (i.e., the minimum arc weight currently in the graph after applying the transformation). The terminating condition is expressed within the while-loop condition on Line 3. In the running example, this heuristic terminates after the set of vertices  $\{b, c, d, e, i, j, k\}$  are removed from G. The effective control-flow graph is shown in Figure 4.3(c).

- If the graph cannot be further transformed, (i.e., only the source and sink vertices remain in the graph), then the graph's structure will not permit increasing the sampling

period to SP and the algorithm declares failure.

Figure 4.3: Illustrations of Heuristic 1.

# Subroutine 4.5 Approximate-Vertex-Cover(G)

#### 4.3.2 Heuristic 2: Minimum Vertex Cover Heuristic

The second heuristic that was explored is an algorithm based on a solution to the *minimum* vertex cover problem. The minimum vertex cover problem is defined as follows:

Given a (directed or undirected) graph  $G = \langle V, E \rangle$ , the goal is to find the minimum set  $U \subseteq V$ , such that each edge in E is incident to at least one vertex in U.

The minimum vertex cover problem is NP-complete, but there exists several approximation algorithms that find nearly optimal solutions. [48] describes a 2-approximation algorithm for the minimum vertex cover problem. This heuristic employs the 2-approximation algorithm in [48] to determine an approximate minimum vertex cover for the control-flow graph under examination. The pseudocode for this approximation algorithm is shown in Subroutine 4.5.

Heuristic 4.6 presents the minimum vertex cover based heuristic as pseudocode. This algorithm works as follows and is illustrated using the example control-flow graph shown in Figure 4.2(a).

- First, it prunes G (Line 2). Figure 4.2(b) shows the resulting graph after pruning the graph in Figure 4.2(a).

- Next, an approximate minimum vertex cover of graph G is computed (Line 4), denoted as vc. The graph that is used to determine the minimum vertex cover consists of arcs whose weights are strictly less than SP are considered. The subgraph that

## Heuristic 4.6 Vertex Cover Based

**Input:** A critical control-flow graph  $G = \langle V, v^0, A, w \rangle$  and desired sampling period SP. **Output:** A set U of vertices to be deleted from G.

```

1: U := \{\};

2: G := \mathsf{PruneCFG}(G, SP);

3: while (MW(G) < SP \land U \neq V) do

4: vc := \mathsf{Approximate-Vertex-Cover}(G);

5: for each vertex v \in vc do

6: G := \mathsf{CollapseNode}(G, v);

7: U := U \cup \{v\};

8: end for

9: end while

10: if (U = V) then declare failure;

11: return U;

```

is generated from the pruned graph in Figure 4.2(b) is shown in Figure 4.4(a). The intuition behind determining the minimum vertex cover is that collapsing all vertices in vc may result in removing all arcs whose weights are strictly less than SP because the graph is pruned and the vertex cover vc covers all arcs of the graph. The approximation minimum vertex cover algorithm adopted from [48] is a non-deterministic randomized algorithm and may produce different covers for the same input graph. To improve the solution, Line 4 is invoked multiple times (this parameter may be changed by the user) and of the generated approximate minimum vertex covers, the heuristic selects the smallest vertex cover. This is abstracted away from the pseudocode. Figure 4.4(b) shows an approximate minimum vertex cover from the subgraph in Figure 4.4(a).

• Then, similar to Heuristic 4.3, vertices  $v \in vc$  are collapsed (Lines 5-7). The graph transform operation (Lines 5-7) results in merging incoming arcs to v with outgoing arcs from v in the fashion described by transformation function T(CFG, v). The

basic block corresponding to vertex v contains a critical instruction that needs to be buffered in memory through additional instrumentation. Thus, v is added to U (Line 7). Figure 4.4(c) shows the graph that results upon collapsing all vertices in the vertex cover shown in Figure 4.4(b).

- Lines 3-8 are repeated until the minimum arc weight(s) of G are greater than or equal to SP. In other words, the heuristic will repeat until the effective graph's longest sampling period is at least SP. This termination condition is expressed in the while-loop condition on Line 3. One possible solution that this heuristic may return after processing the graph in Figure 4.2(a) is shown in Figure 4.4(d).

- If the graph cannot be collapsed further (i.e., all vertices are collapsed), then the graph's structure will not permit increasing the sampling period to SP and the algorithm declares failure.

- (a) Generate vertex cover subgraph.

- (b) Approximate minimum vertex cover.

Figure 4.4: Illustrations of Heuristic 2.

# 4.3.3 Heuristic 3: Genetic Algorithm

The final heuristic that was considered for approximating a (near-)optimal instrumentation scheme is a genetic algorithm (GA). Genetic algorithms are search heuristics that adopt a process that is evolutionary-like. In this context, the heuristic aims at collapsing the fewest number of vertices in a critical control-flow graph G such that the longest sampling period in the resulting graph G' (after collapsing the selected vertices) is equal to or greater than the target (i.e., desired) sampling period SP.

The optimization problem is mapped to the following necessary facets of a genetic algorithm; the subsequent subsections will describe these facets in greater detail:

**Chromosomes:** A chromosome represents the list of vertices in a critical control-flow graph, G. Each bit in a chromosome maps to a vertex in G. When a bit's value is set to true, it represents the condition where the corresponding vertex is selected to be collapsed in G.

**Fitness Function:** The fitness function of a chromosome is the number of collapsed vertices represented by the chromosome. The fittest chromosome is one that has the fewest number of bits set to *true* for all chromosomes in the population.

**Reproduction:** Both crossover and mutation are used to generate new generations of chromosomes.

**Termination:** The genetic algorithm terminates when the upper limit on the number of generations is reached.

#### 4.3.3.1 Chromosomes

Let  $G = \langle V, v^0, A, w \rangle$  be a critical control-flow graph. Each chromosome in the genetic model has |V| entries. Each entry is a tuple  $\langle \text{vertex id}, \text{SP}_{min}, \text{value} \rangle$  that represents a vertex in G. Vertex id is the vertex identifier, min-SP is the minimum weight of the incoming and outgoing arcs of the vertex and value is a boolean value that indicates if the vertex is collapsed in G. If value = true for a vertex v, then v is collapsed and auxiliary memory is used to temporarily store the event until the monitor flushes the history buffer.

The chromosome's longest sampling period is defined as the longest sampling period of the control-flow graph obtained by collapsing the vertices in the chromosome. In this genetic model, each chromosome's longest sampling period must be always at least SP.

## 4.3.3.2 Initialization (Seeding)

The number of chromosomes created in each generation is chosen by the user. Let  $|\mathcal{G}|$  denote the size of a generation. In the initialization step of this genetic algorithm,  $|\mathcal{G}|$  chromosomes are randomly created. To generate these random chromosomes, a set of vertices are arbitrarily collapsed in G so that the chromosomes' longest sampling period is at least SP. The generation of an arbitrary initial chromosome follows these three steps:

- 1. Find the set of vertices,  $U \subseteq V$  where  $u_{min-SP} < SP$ ,  $\forall u \in U$ .

- 2. Randomly choose a vertex  $u \in U$  to collapse in G to produce a new control-flow graph G' = T(G, v).

- 3. Calculate the longest sampling period of G',  $LSP_{G'}$ . If  $LSP_{G'} < SP$ , return to step one and operate on G'.

#### 4.3.3.3 Selection/Fitness Function

Since the goal of solving this optimization problem is to transform a graph such that  $LSP \ge SP$  with as few collapsed vertices as possible, the chromosome's fitness is characterized by the number of *value* in the chromosome's tuple are set to *true*. Hence, the fitness function of a chromosome chr is defined as:

$$\mathcal{F}_{chr} = \sum_{i=1}^{|V|} chr. \text{value} \tag{4.12}$$

$\mathcal{F}_{chr}$  represents the number of nodes collapsed in chr. Consequently, if  $\mathcal{F}_{chr}$  is smaller, then the chromosome is more fit.

#### 4.3.3.4 Reproduction

Both genetic operators, *crossover* and *mutation*, are used to evolve the current generation into the next generation. Reproduction/evolution in this genetic algorithm first modifies the chromosomes by crossover. The resulting chromosomes are then mutated to form the next generation of chromosomes as required.

**Crossover.** New chromosomes are formed by applying *one-point* crossover. Two parents are randomly chosen for crossover. In the crossover, the two parents are split into halves; the two children are produced by swapping one of the two halves between the parents. For each child, if the child chromosome's longest sampling period is at least SP, the child will be added to the set of chromosomes of the next generation; if this condition is not satisfied, the child will be mutated.

**Mutation.** The mutation process takes the children passed over by the crossover process and mainpulates each child by the following steps:

- 1. Find the set of vertices,  $U \subseteq V$  where  $u_{min-SP} < SP \ \forall u \in U$ .

- 2. Randomly select a vertex  $u \in U$  to collapse by T(G, u).

- 3. Find the set of collapsed vertices S in the chromosome for vertices where  $s_{min-SP} > SP$ ,  $S \subseteq U$ .

- 4. Randomly select a vertex  $s \in S$  to expand, meaning that s is restored (as a vertex) to the control-flow graph represented by the child chromosome.

- 5. Check if the chromosome's longest sampling period,  $LSP_{chr}$ , is at least SP. If  $LSP_{chr} < SP$ , return to step 1 and continue until the chromosome's longest sampling period is at least SP or when the maximum number of mutations allowable is reached.

- 6. If the resulting chromosome's longest sampling period is at least SP when it reaches step 5, it is added to the next generation.

Crossover and Mutation Limitations. Sometimes the crossover and mutation processes fails to create  $|\mathcal{G}|$  chromosomes to populate the next generation. When this occurs, it