# Bit Serial Systolic Architectures for Multiplicative Inversion and Division over $GF(2^m)$

by

Amir K. Daneshbeh

A thesis

presented to the University of Waterloo

in fulfillment of the

thesis requirement for the degree of

Master of Applied Science

in

Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2005

©Amir K. Daneshbeh, 2005

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by examiners.

I understand that my thesis may be made electronically available to the public.

Amir K. Daneshbeh

#### Abstract

Systolic architectures are capable of achieving high throughput by maximizing pipelining and by eliminating global data interconnects. Recursive algorithms with regular data flows are suitable for systolization. The computation of multiplicative inversion using algorithms based on EEA (Extended Euclidean Algorithm) are particularly suitable for systolization. Implementations based on EEA present a high degree of parallelism and pipelinability at bit level which can be easily optimized to achieve local data flow and to eliminate the global interconnects which represent most important bottleneck in todays sub-micron design process. The net result is to have high clock rate and performance based on efficient systolic architectures.

This thesis examines high performance but also scalable implementations of multiplicative inversion or field division over Galois fields  $GF(2^m)$  in the specific case of cryptographic applications where field dimension m may be very large (greater than 400) and either m or defining irreducible polynomial may vary. For this purpose, many inversion schemes with different basis representation are studied and most importantly variants of EEA and binary (Stein's) GCD computation implementations are reviewed. A set of common as well as contrasting characteristics of these variants are discussed. As a result a generalized and optimized variant of EEA is proposed which can compute division, and multiplicative inversion as its subset, with divisor in either polynomial or triangular basis representation. Further results regarding Hankel matrix formation for double-basis inversion is provided. The validity of using the same architecture to compute field division with polynomial or triangular basis representation is proved.

Next, a scalable unidirectional bit serial systolic array implementation of this proposed variant of EEA is implemented. Its complexity measures are defined and these are compared against the best known architectures. It is shown that assuming the requirements specified above, this proposed architecture may achieve a higher clock rate performance w.r.t. other designs while being more flexible, reliable and with minimum number of intercell interconnects.

The main contribution at system level architecture is the substitution of all counter or adder/subtractor elements with a simpler distributed and free of carry propagation delay structures. Further a novel restoring mechanism for result sequences of EEA is proposed

using a double delay element implementation.

Finally, using this systolic architecture a CMD (Combined Multiplier Divider) datapath is designed which is used as the core of a novel systolic elliptic curve processor. This EC processor uses affine coordinates to compute scalar point multiplication which results in having a very small control unit and negligible with respect to the datapath for all practical values of m. The throughput of this EC based on this bit serial systolic architecture is comparable with designs many times larger than itself reported previously.

## ${\bf Acknowledgments}$

Thanks to Professor Hasan for his guidance, support, patience and constant presence. I specially thank him for keeping me on track to complete this work.

# List of Important Acronyms

**CMD** Combined Multiplier Divider PE

**DPA** Differential Power Analysis

**DH** Diffie-Hellman

**DL** Discrete Logarithm

**DSA** Digital Signature Algorithm

**EC** Elliptic Curve

ECC Elliptic Curve CryptographyEEA Extended Euclidean Algorithm

**GF** Galois Field

GCD Greatest Common Divisor

$\mathbf{LFSR} \qquad \text{Linear Feedback Shift Register}$

PBIA Polynomial Basis Inversion Algorithm

**PE** Processing Element

**RSA** Rivest Shamir Adleman Public Key Cryptosystem

STBIA Shifted Triangular Basis Inversion Algorithm

**TBIA** Triangular Basis Inversion Algorithm

# Contents

| 1        | Intr | roduction                                             | 1  |

|----------|------|-------------------------------------------------------|----|

|          | 1.1  | Motivation                                            | 1  |

|          | 1.2  | Previous Work                                         | 3  |

|          | 1.3  | Objectives                                            | 5  |

|          | 1.4  | Thesis Outline                                        | 6  |

| <b>2</b> | Ma   | thematical Background                                 | 8  |

|          | 2.1  | Basis representation                                  | 8  |

|          |      | 2.1.1 Polynomial or Canonical Basis                   | 8  |

|          |      | 2.1.2 Dual Basis                                      | 9  |

|          |      | 2.1.3 Normal and Optimal Normal Bases                 | 10 |

|          |      | 2.1.4 Triangular Basis                                | 11 |

|          | 2.2  | Multiplicative Inversion                              | 13 |

|          |      | 2.2.1 Non-Algorithmic Look-Up Table Inversion         | 14 |

|          |      | 2.2.2 Fermat's Little Theorem Based Inversion         | 14 |

|          |      | 2.2.3 Extended Euclidean Algorithm Based Inversion    | 17 |

|          | 2.3  | Summary                                               | 19 |

| 3        | (Ex  | tended) Euclidean and Binary GCD Algorithm            | 20 |

|          | 3.1  | Greatest Common Divisor Computation                   | 20 |

|          |      | 3.1.1 Basic GCD and EEA                               | 20 |

|          | 3.2  | Right-Shift GCD Algorithm, Right-Shift EEA            | 22 |

|          |      | 3.2.1 Binary GCD Algorithm and its Plus-Minus Variant | 23 |

|   |     | 3.2.2   | Binary GCD Division Algorithm                                      | 26 |

|---|-----|---------|--------------------------------------------------------------------|----|

|   |     | 3.2.3   | Almost Inverse Algorithm                                           | 28 |

|   | 3.3 | Left-S  | hift GCD Algorithm, Left-Shift EEA                                 | 30 |

|   |     | 3.3.1   | Berlekamp's Inversion Algorithm with No Modulo Reduction           | 33 |

|   |     | 3.3.2   | Shifted Result Problem                                             | 36 |

|   |     | 3.3.3   | Inversion Algorithm without Conditional Branching                  | 36 |

|   |     | 3.3.4   | Inversion Algorithm with Right-Left-Shift of Result Sequence       | 37 |

|   |     | 3.3.5   | Division Algorithm with a Two-step Shifted Result Solution         | 39 |

|   |     | 3.3.6   | Division Algorithm with Auxiliary Polynomial for Partial Remainder | 40 |

|   | 3.4 | Summ    | ary                                                                | 42 |

| 4 | Inv | ersion  | using Double-Basis representation                                  | 43 |

|   | 4.1 | Single  | -Basis Inversion                                                   | 43 |

|   | 4.2 | Double  | e-Basis Inversion                                                  | 45 |

|   | 4.3 | Invers  | ion by applying EEA to a Hankel Matrix                             | 48 |

|   | 4.4 | Genera  | alized Polynomial Inversion and Division                           | 50 |

|   |     | 4.4.1   | Polynomial Basis Inversion using EEA                               | 50 |

|   |     | 4.4.2   | Triangular Basis Inversion Using EEA                               | 51 |

|   | 4.5 | Key R   | esults on Inversion and Division using Triangular Basis            | 51 |

|   |     | 4.5.1   | Inversion Algorithm Revisited                                      | 52 |

|   |     | 4.5.2   | Comments                                                           | 55 |

|   |     | 4.5.3   | Algorithms for Division                                            | 55 |

|   | 4.6 | Summ    | ary                                                                | 57 |

| 5 | Sys | tolic A | rchitectures                                                       | 58 |

|   | 5.1 | Comp    | lexity measures in VLSI Design                                     | 58 |

|   | 5.2 | Systol  | ization of Polynomial Updating Step                                | 59 |

|   |     | 5.2.1   | Task 1 and Shifted Remainder                                       | 60 |

|   |     | 5.2.2   | Task 2 and Swapped Shifted Long Division Algorithm                 | 62 |

|   |     | 5.2.3   | Tasks 3, 4 and Putting All Together                                | 63 |

|   |     | 5.2.4   | An Example of Stepwise Restoring Action of Algorithm 21            | 67 |

|   | 5.3 | Bit Se  | rial Unidirectional Systolic Architectures                         | 69 |

|   |                | 5.3.1   | Bit Serial Unidirectional Systolic Structure              | 69  |

|---|----------------|---------|-----------------------------------------------------------|-----|

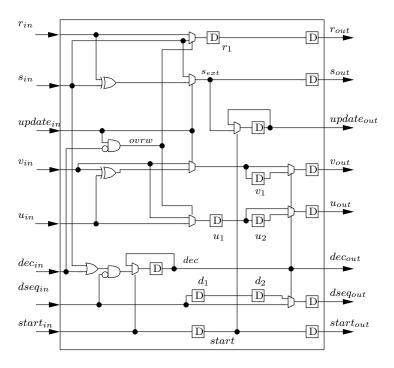

|   |                | 5.3.2   | Processing Element for Inversion                          | 70  |

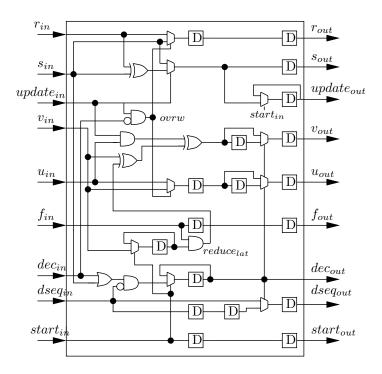

|   |                | 5.3.3   | Processing Element for Division                           | 72  |

|   |                | 5.3.4   | Bit Serial Inverter-Divider in Triangular Basis           | 73  |

|   | 5.4            | Gener   | alization and Optimization                                | 75  |

|   |                | 5.4.1   | Universal Bit Serial Systolic Inverter-Divider            | 75  |

|   |                | 5.4.2   | Trading off Throughput for Storage Area                   | 76  |

|   |                | 5.4.3   | Area and Latency Optimization without Throughput Loss     | 76  |

|   |                | 5.4.4   | Implementation Results                                    | 77  |

|   | 5.5            | Comp    | parison                                                   | 78  |

|   | 5.6            | Summ    | nary                                                      | 80  |

| 6 | $\mathbf{Sys}$ | tolic E | Elliptic Curve Processor                                  | 81  |

|   | 6.1            | Backg   | $\operatorname{round}$                                    | 81  |

|   | 6.2            | Relate  | ed Work                                                   | 83  |

|   | 6.3            | Ellipt  | ic Curve Cryptography and EC Arithmetic                   | 85  |

|   |                | 6.3.1   | EC Point Add and Point Double over $GF(2^m)$              | 85  |

|   |                | 6.3.2   | System Level Block Diagram of an EC Cryptoprocessor       | 88  |

|   | 6.4            | EC B    | it-Serial Systolic Accelerator over $\mathrm{GF}(2^m)$    | 89  |

|   |                | 6.4.1   | Bit Serial Systolic Architecture for Field Multiplication | 90  |

|   |                | 6.4.2   | Bit Serial Systolic Architecture for Field Division       | 92  |

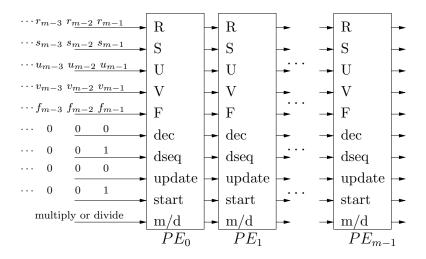

|   |                | 6.4.3   | Processing Element of a Combined Multiplier Divider       | 93  |

|   | 6.5            | Imple   | mentation Issues                                          | 94  |

|   |                | 6.5.1   | EC Full Point Add using the CMD Datapath                  | 95  |

|   |                | 6.5.2   | An FSM-type Control Unit                                  | 97  |

|   |                | 6.5.3   | Scalability and Dealing with Varying Dimension            | 97  |

|   |                | 6.5.4   | Implementation Results                                    | 98  |

|   |                | 6.5.5   | Comparison                                                | 100 |

|   | 6.6            | Summ    | nary                                                      | 101 |

| 7 | Cor            | nclusio | n and Future Work                                         | 102 |

|   | 7 1            | Summ    | pary and Conclusions                                      | 102 |

|  | 7.2 | Future Work. |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  | 1 | 0 | Z |

|--|-----|--------------|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|---|---|---|

|--|-----|--------------|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|---|---|---|

# List of Tables

| 1.1 | The security margin of cryptosystems as a function of their keying material | 3  |

|-----|-----------------------------------------------------------------------------|----|

| 5.1 | Example of inversion over $GF(2^3)$                                         | 68 |

| 5.2 | Comparison of bit serial systolic dividers and inverter                     | 79 |

| 6.1 | Comparison of Stepwise Computation Step of Algorithm 22                     | 87 |

# List of Figures

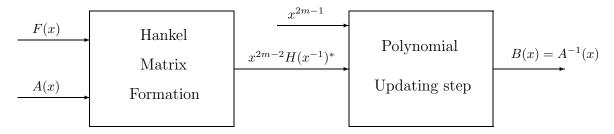

| 4.1 | Two step block diagram of Algorithm TBIA                                     | 55 |

|-----|------------------------------------------------------------------------------|----|

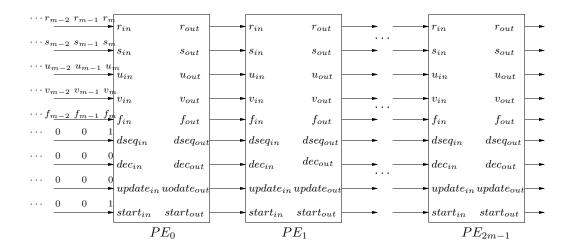

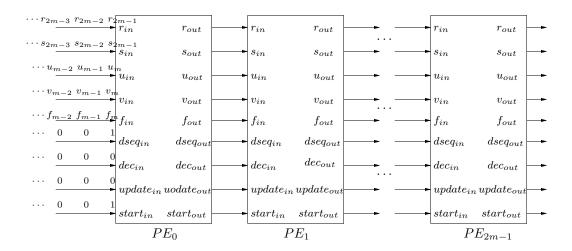

| 5.1 | Bit serial unidirectional systolic architecture for Inversion/Division       | 70 |

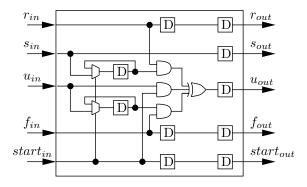

| 5.2 | Processing element for the inverter where D is a delay element               | 71 |

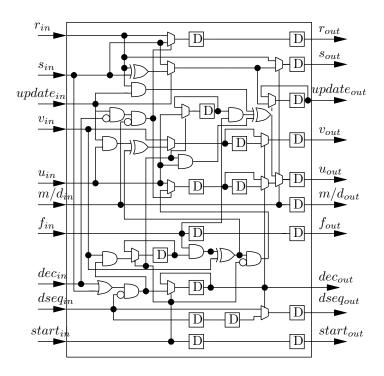

| 5.3 | Processing element for the divider                                           | 73 |

| 5.4 | Bit serial systolic architecture for Inversion/Division in Double-basis      | 74 |

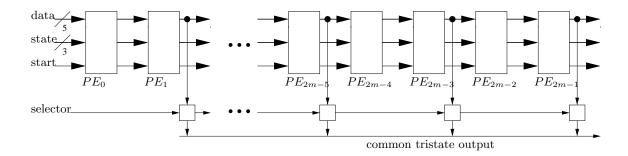

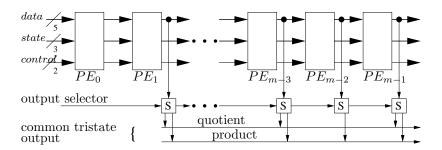

| 5.5 | Variable dimension divider using selectors over common tristate output       | 75 |

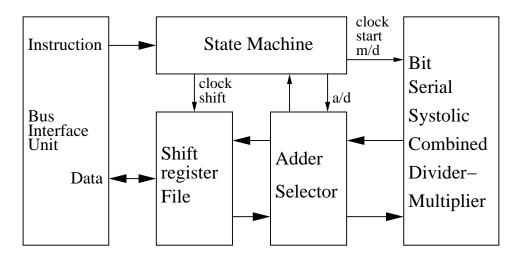

| 6.1 | System level integration                                                     | 88 |

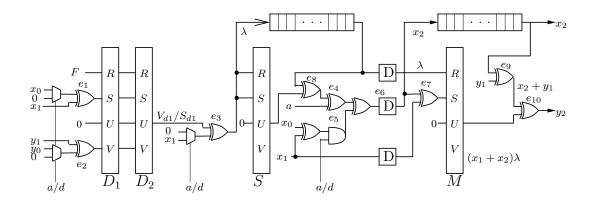

| 6.2 | Bit serial systolic architecture for a CMD                                   | 91 |

| 6.3 | Processing element for the multiplier                                        | 93 |

| 6.4 | Processing element of a CMD                                                  | 94 |

| 6.5 | Bit serial functional sequence of an EC full point add computation           | 95 |

| 6.6 | Inputs selection of a CMD for four operational cases                         | 96 |

| 6.7 | Variable dimension architecture using selectors over common tristate output. | 98 |

# Chapter 1

## Introduction

Continuous innovation in diverse domains from data processing to coding theory has created an exponential growth in new applications based on means of communication. Around the world, everything and everyone can be seen connected in real time. A well-known example of these applications is secure and fraud free e-commerce over the Internet [22]. As our dependence on these new applications grows, the challenge to achieve higher performance and always available "open" systems must meet the demand for security, privacy and integrity of information. Further, in an "open" environment where new players may enter at any time, the source of information requires authenticity and non-repudiation. Mathematical algorithms to perform finite field operations are a main tool to provide privacy, integrity, authenticity and non-repudiation of data communication.

In this work, hardware implementations of a specific class of operations, the multiplicative inversion and field division over Galois fields  $GF(2^m)$ , required in many fundamental protocols of data communication systems, e.g., public-key cryptography, is examined and some novel structures are proposed. In particular, the utilization and trade-offs of systolic implementations of inversion and division over Galois fields are investigated.

#### 1.1 Motivation

Any challenge in the design of new communication and data processing devices aims at a higher performance as well as feasibility, reliability and scalability. A practical utilization

of the Internet and data networking relies on privacy and authenticity of information. This is achievable with the implementation of cryptographic functions. The challenge to undertake is to design an efficient hardware implementation of these functions which achieves high performance but also is reliable and scalable. Basic security functions include secret-key, public-key cryptosystems and digital signature functions. These functions can efficiently be implemented in software or hardware. A software implementation which provides flexibility can never be as fast as a special purpose hardware accelerator. Specific algorithms are optimized in order to enhance target processors [1, 6, 44, 113]. However, to reach a higher throughput, the above functions are implemented directly in hardware. In this case, basic arithmetic operations required for these functions should be optimized under the constraint of area, time and energy [75, 91, 118].

Arithmetic operations in Galois field  $GF(2^m)$  where m represents the dimension of field have applications in coding theory [11,81], computer algebra, digital signal processing [77,94] and cryptography [74,82]. However, field dimension requirements are drastically different among these applications. The specific case of cryptography incurs a continuous demand for larger field dimensions as faster data processing devices (computers) crunch higher MIPS (millions of instructions per second). In particular, in public key cryptographic applications, the field dimension may exceed 4000 for discrete logarithm cryptosystems or 500 for elliptic curve cryptosystems [82]. Such trend reflected in using larger length of keying material is shown in Table 1.1 [112].

In this work, hardware implementations of inversion and division over Galois fields are investigated and novel architectures and some practical applications of these are proposed. Not only a higher performance in terms of throughput and clock rate, but also the feasibility and scalability of such implementations are examined.

In the next few chapters inversion and division algorithms over Galois fields will be described. The feasibility, constraints, and requirements of systolic implementations of these algorithms will be discussed. In this context, the following facts will be highlighted:

- Multiplicative inversion operation over Galois fields which is used in certain standard protocols of public-key cryptography requires to be optimized for large dimension fields.

- Most efficient algorithms to compute inversion are recursive algorithms based on vari-

| Asymmetric Crypt.  | Discrete Logarithm | Elliptic Curve DL  | Security Margin       |

|--------------------|--------------------|--------------------|-----------------------|

| key size (in bits) | key size (in bits) | key size (in bits) | (in MIPS years)       |

| RSA, DH            | DSA                | ECC                |                       |

| 622                | 112                | 117                | $3.51 \times 10^{7}$  |

| 777                | 118                | 124                | $5.00 \times 10^{8}$  |

| 952                | 125                | 132                | $7.13 \times 10^9$    |

| 1068               | 129                | 136                | $3.51 \times 10^{10}$ |

| 1191               | 133                | 141                | $1.73 \times 10^{11}$ |

| 1369               | 138                | 146                | $1.45 \times 10^{12}$ |

Table 1.1: The security margin of cryptosystems as a function of their keying material

ants of EEA (Extended Euclidean Algorithm) and binary (Stein's) GCD (Greatest Common Divisor) Algorithm.

- As the field dimension increases, a centralized, either register based or parallel, implementation of EEA type algorithms are not efficient, scalable or even feasible under given time-area constraints.

- Systolic architectures are more suitable for recursive algorithms [70] such as variants of EEA.

- Systolic architectures achieve the highest throughput by maximizing the parallelism inherent in algorithms with use of fine-grain (bit or digit level) pipelining, and they eliminate the interconnect bottlenecks of sub-micron designs.

## 1.2 Previous Work

The main advantages of VLSI technology, *i.e.*, large amount of logic available at a very low cost, reduced physical size and power consumption, and increased reliability, allow the implementation of computationally intensive and recursive algorithms as part of a SoC (System on a Chip). However, as the integration density increases, the interconnection

and wiring (the routing congestion issue in sub-micron designs) dominate the design complexity. Special architectures which can increase the logic utilization without an increase in interconnection are desirable. Luckily, such architectures, the array processors in general or systolic structures in particular, exist.

Systolic architectures are specifically proposed to achieve high throughput and clock rates by maximizing the pipelining and by eliminating the global data interconnects [69, 70, 93]. Recursive algorithms such as extended Euclidean algorithm with regular data flows are particularly suitable for systolization. These present a high degree of parallelism at a bit level which can easily be optimized with few local data flow and interconnect architectures. There are many systolic architectures proposed to compute multiplication [31, 38, 67, 80, 114, 117, 120], division [48, 68] and inversion [32, 40, 108, 110, 115] over Galois fields.

Among the arithmetic operations over Galois fields the multiplicative inversion and division are the most costly ones. This complexity is even more pronounced for larger field dimensions. In general, three major schemes to compute multiplicative inverses exist: Fermat's little theorem, variants of extended Euclidean algorithm (EEA) or a solution of a set of linear equations. First scheme is efficient if either a fast squaring or multiplication method is available [57]. The extended Euclidean algorithm (EEA) based schemes to compute inversion and division are the most efficient in time and area. The third method is generally inefficient for large values of field dimension. However, it is shown that a set of linear equations formed upon triangular basis representation can be solved by schemes similar to EEA [46].

However, a limitation of a direct repetitive application of the extended Euclidean algorithm to compute multiplicative inverses is a conditionally swap operation which cannot easily be serialized. This may require variable size counter-like structures with carry propagation chains to keep track of the difference of the degree of polynomials, e.g., [40,96,115], in which case they are not suitable for high-performance and scalable VLSI implementations (including systolic architectures). Many systolic array proposals for multiplicative inversion or division over  $GF(2^m)$  based on EEA or its dual (extended Stein's algorithm), i.e., [37,56,116,119], all require counter-like structures with carry propagation delays. Since the carry propagation chain depends on the field dimension m, in general, it dominates

the critical delay path. Only counter or comparator architectures with no carry propagation chain can be considered dimension independent. Moreover, a counter with no carry propagation chain can be easily transformed into a distributed structure.

The above discussion is valid for inversion algorithms in alternative Galois field basis representations, such as a novel multiplicative inversion algorithm, by solving a set of linear equations using double-basis representation over  $GF(2^m)$ , [46]. In that paper, a centralized control architecture to implement this algorithm is proposed. However, again, as the field dimension increases, a VLSI implementation of such centralized control design with long global control signals becomes inefficient or even impractical for certain clock rate and throughput requirements. In this case, the possibility to incorporate a pipelined change of basis structure and a systolic inverter/divider with a distributed ring counter structure may result in an optimal solution.

## 1.3 Objectives

This work aims to investigate and propose a class of optimized (free of carry propagation) systolic architectures for inversion and division over Galois fields. The driving force is to improve the throughput and clock rate as a measure of performance without increasing the circuit (area) and design complexity while providing the best solution for scalability (unidirectional single cell type structure) and reliability (ease of fault-tolerant circuit insertion). Particular attention is given to minimize the interconnect at the expense of extra logic. Specifically, the proposed systolic structure will be optimized as follows:

- maximizing the regularity of the array processor,

- minimizing number of cell types,

- reducing out of order signals by elimination of data dependencies with the goal to eliminate the retiming latches between cells.

As a consequence, a feasible architecture with an extremely regular structure is sought. This architecture should be easily scalable, should deliver very high throughput, ideally with a transparent in-line computation over incoming bit streams.

Moreover, from the cryptographic and field application point of view, the design aims to process a field of any dimension, and to be independent of the choice of the field defining irreducible polynomial.

Finally, a practical deployment of such systolic structure (with a unified multiplier divider cell) as the core of an elliptic curve crypto processor will be proposed. The relative cost of the data path versus a complete state machine based control unit for EC scalar point multiplication is investigated and other performance measures are discussed.

#### 1.4 Thesis Outline

The organization of this thesis is as follows:

In Chapter 2, three basis representations of field elements are defined and their relative importance for the implementation of particular operations over Galois fields are compared. Specifically, triangular basis is introduced which will be used for the inversion computation over double-basis. Next, a variety of inversion algorithms each best suitable in a different bases and using different number theory techniques are explained.

In Chapter 3, a detailed survey of many EEA type, binary (Stein's) GCD Algorithm and the best known application of these to perform inversion/division over Galois fields are reviewed. Common and contrasting characteristics of these are classified. Optimization techniques proposed in certain implementations and some important conclusions used in this thesis are highlighted.

In Chapter 4, inversion and division using double-basis representation by applying EEA to a Hankel matrix is reviewed. Some results regarding Hankel matrix entry formation are described. Further, a common set of algorithms to compute inversion and division based on EEA with both polynomial and triangular basis is discussed.

In Chapter 5, systolic architectures as a solution to overcome the ever increasing complexity of computational intensive algorithms are introduced. Next, an optimized (free of carry propagation) systolic array structure for EEA computation is examined which is used as a building block for Galois field inverter-divider. A unidirectional bit serial systolic architecture of inversion and division in both polynomial and triangular basis is introduced. A single type Processing Element (PE) of such architecture and its complexity measures

are investigated and evaluated against similar architectures.

In Chapter 6, a practical application of such an architecture is presented. First, optimizing Elliptic Curve Cryptographic operations in the presence of fast dividers (comparable to multipliers) is discussed. Next, a combined multiplier-divider cell structure is proposed and a unidirectional bit serial systolic architecture as the main data path unit is designed. By incorporating a state machine control unit and shift register files, an extremely high clock rate systolic processor is devised and its performance is evaluated against best known designs in the literature.

In Chapter 7, after summarizing what is accomplished, some remarks regarding future work conclude the thesis.

# Chapter 2

# Mathematical Background

Optimized algorithms to compute multiplicative inversion, as well as other operations over Galois fields, depend upon the choice of field element representation. In this chapter, some common basis representation of Galois field elements which are of practical use, namely *polynomial*, *dual*, *normal* and *triangular* basis will be reviewed. Next, different algorithms for inversion or division with some implementation examples suitable in each basis representation will be compared. Refer to [78] for a general background on finite prime fields, extension fields and the theory of polynomials over finite fields.

### 2.1 Basis representation

In the following main classes of basis representation and some variants of each are reviewed. Their relevance while optimizing certain field operations and some basis conversion techniques are discussed.

### 2.1.1 Polynomial or Canonical Basis

Given an irreducible polynomial F(x) of degree m over the finite field GF(2), considering one of the roots of F(x) such as  $\omega$ , i.e.,  $F(\omega) = 0$ , it is well known that the set of elements

$$\{1,\omega,\omega^2,\cdots,\omega^{m-1}\},$$

is linearly independent and forms a basis referred to as polynomial or canonical basis. Then, any element  $A \in GF(2^m)$  can be represented as

$$A = \sum_{i=0}^{m-1} a_{\Omega i} \omega^i,$$

where  $a_{\Omega i} \in \{0, 1\}$  is the *i*-th coordinate of A with respect to the polynomial basis  $\Omega$ , or in a column vector form  $\underline{a}_{\Omega} = [a_{\Omega 0}, a_{\Omega 1}, \cdots, a_{\Omega m-1}]^T$  over GF(2).

In this representation, the *addition* of two elements is simply a pairwise bit addition. This can be easily implemented using XOR gates and hence it has a linear complexity. On the other hand, the implementation of multiplication, if not optimized, can be very costly. That is because a modulo reduction step must follow or be incorporated into polynomial multiplication operation. There are more efficient proposals which have low complexity in this basis, [24,51,58,66,75,99,101,117,118,120,121]. In this basis, many proposals to compute multiplicative inversion and division exist as well which will be reviewed in detail later.

#### 2.1.2 Dual Basis

In order to have an efficient implementation of field multiplication, in some situations a specific basis, namely, dual basis relative to a primal basis can be used. In [10], Berlekamp proposed the use of combined polynomial and its *dual basis* for efficient implementation of multiplication.

Let us consider the polynomial basis  $\{1, \omega, \omega^2, \cdots, \omega^{m-1}\}$  of  $GF(2^m)$  where  $\omega$  is a root of the irreducible polynomial F(x) of degree m. Now, let

$$\{\gamma_0, \gamma_1, \cdots, \gamma_{m-1}\},\$$

be the dual basis so that

$$Tr(\omega^i \gamma_j) = \lambda_{ij}, \quad i, j = 0, 1, 2, \cdots, m-1,$$

where  $Tr(\cdot)$  is the trace function from  $GF(2^m)$  to GF(2) and  $\lambda_{ij}$  is the Kronecker delta function, equal to 1 if i = j and zero otherwise.

The two representations of any element, e.g., x, of the field are related as follows,

$$x = \sum_{i=0}^{m-1} x_i \omega^i = \sum_{i=0}^{m-1} x_i' \gamma_i,$$

where the coordinate  $x'_i$  of x with respect to the dual basis is given by  $x'_i = Tr(\omega^i x)$ .

There are well-known methods to find the dual basis of a polynomial basis, e.g., in [74]. Let us consider the polynomial basis  $\{1, \omega, \omega^2, \cdots, \omega^{m-1}\}$ , where the minimal polynomial of  $\omega \in GF(2^m)$  over GF(2) is F(x), (the minimal polynomial is the monic irreducible polynomial over GF(2) of least degree having  $\omega$  as a root). Then, the dual basis can be computed by

$$\left\{\frac{g_0}{F'(\omega)}, \frac{g_1}{F'(\omega)}, \cdots, \frac{g_{m-1}}{F'(\omega)}\right\} \tag{2.1}$$

where

$$F(x) = (x + \omega) \left( \sum_{i=0}^{m-1} g_i x^i \right), \quad g_i \in GF(2^m), \quad g_{m-1} = 1,$$

and F'(x) is the derivative of F(x) over GF(2) or alternatively  $F'(\omega) = \prod_{j=1}^{m-1} (\omega + \omega^{2^j})$  [109].

Among the pair of dual bases, there are those which are the dual of their own. Such basis is called a *self-dual basis* [84, 109]. It has the advantage that there is no need for a conversion from and to their respective duals. However, such self-duality does not exist for all bases.

### 2.1.3 Normal and Optimal Normal Bases

Considering the Galois field  $GF(2^m)$  as an m-dimensional vector space over GF(2), a basis for  $GF(2^m)$  of the form

$$\{\beta, \beta^2, \beta^4, \cdots, \beta^{2^{m-1}}\}$$

is called a *normal basis*. The element  $\beta \in GF(2^m)$  is the generator of the normal basis. It is well-known, [74], that  $GF(2^m)$  has a normal basis for every  $m \geq 1$ . Even though normal basis can be defined for a *suitable* element of the field, there are no straightforward methods to identify such an element.

Using normal basis, the operation of squaring a field element is extremely simple. Considering the normal basis  $\{\beta, \beta^2, \beta^4, \dots, \beta^{2^{m-1}}\}$ , any field element a can be represented as

$$a = \sum_{i=0}^{m-1} a_i \beta_i$$

where  $a_i \in \{0, 1\}$  and  $\beta_i = \beta^{2^i}$  for  $0 \le i \le m-1$ .

Then

$$a^2 = \sum_{i=0}^{m-1} a_{i-1}\beta_i$$

where subscripts are reduced modulo  $m$  (2.2a)

$$= \sum_{i=1}^{m-1} a_{i-1}\beta_i + a_{m-1}\beta_0 \tag{2.2b}$$

That is, the coordinate vector for  $a^2$  is computed by a cyclic shift of the coordinate vector for a.

In general, multiplication in normal basis is costly. However, Massy and Omura have devised an efficient algorithm [89] for multiplication using normal basis. Further, by applying this algorithm to a specific class of normal basis, *i.e.*, optimal normal basis, a very efficient hardware implementation for field multiplication is obtained [85]. As in the case of self-dual basis, the optimal normal basis does not exist for all values of m.

#### 2.1.4 Triangular Basis

The number of distinct bases of an extension field over its ground field is rather large. In practice all the bases can be transformed to each other by matrix multiplication as explained next. However, in general, such an operation has very costly implementation. Among different bases the *triangular* basis of a polynomial has the main advantage that the change of coordinates between the two bases can be easily and efficiently implemented by shift register techniques.

Let  $F(x) = \sum_{i=0}^{m} f_i x^i$  be the field defining irreducible polynomial of degree m of  $GF(2^m)$ . Then,  $GF(2^m)$  can be viewed as a vector space of dimension m over GF(2) and any ordered basis

$$\Theta = (\underline{\Theta}_0, \underline{\Theta}_1, \cdots, \underline{\Theta}_{m-1})$$

can be viewed as an  $m \times m$  matrix over GF(2). Note that  $\underline{\Theta}$ 's can be viewed as column vectors over GF(2). Similarly, a new basis  $\Lambda = (\underline{\Lambda}_0, \underline{\Lambda}_1, \dots, \underline{\Lambda}_{m-1})$  can be considered as another  $m \times m$  matrix which can be computed by post-multiplying the matrix  $\Theta$  with a transformation matrix, e.g., M. That is

$$\Lambda = \Theta M$$

Such a transformation can be done if and only if the basis transformation matrix M is an  $m \times m$  non singular matrix over GF(2) [50].

Let c be an element of the filed  $GF(2^m)$ , then c can be written in basis  $\Theta$  as  $c = \underline{c}_{\Theta}\underline{\Theta}^T$ , with  $\underline{c}_{\Theta} \in GF(2^m)$  being the vector of coordinates of c with respect to  $\Theta$ , and similarly,  $c = \underline{c}_{\Lambda}\underline{\Lambda}^T$ .

It is easy to show that  $\underline{c}_{\Theta} = \underline{c}_{\Lambda} M^T$  and vice versa,  $\underline{c}_{\Lambda} = \underline{c}_{\Theta} (M^T)^{-1}$ . A suitable choice of M can facilitate the transformation of coordinates from one basis system to the other.

Let  $M = [M_{ij}]$  with

$$M_{i,j} = \begin{cases} f_{i+j+1} & 0 \le i+j \le m-1, \\ 0 & m \le i+j \le 2m-2, \end{cases}$$

(2.3)

which is a Hankel matrix with constants on its back-diagonals. Then  $M^{-1}$  is a matrix with entries

$$(M^{-1})_{i,j} = \begin{cases} 0 & 0 \le i+j \le m-2, \\ h_{i+j+1-m} & m-1 \le i+j \le 2m-2, \end{cases}$$

(2.4)

with  $h_0 = 1$  and

$$h_k = \sum_{i=0}^{k-1} f_{m-k+i} h_i.$$

Given this particular choice of M,  $\Lambda$  is referred to as the *triangular basis* with respect to  $\Theta$ . With this particular choice of M, the change of coordinates of any element c between  $\Theta$  and  $\Lambda$  can be easily implemented by shift register techniques using:

$$(\underline{c}_{\Theta})_{j} = \sum_{i=0}^{m-j-1} f_{i+j+1}(\underline{c}_{\Lambda})_{i} \quad 0 \le j \le m-1$$

(2.5)

and

$$(\underline{c}_{\Lambda})_{k} = \begin{cases} (\underline{c}_{\Theta})_{m-1-k} & k = 0, \\ (\underline{c}_{\Theta})_{m-1-k} + \sum_{i=0}^{k-1} f_{m-k+i}(\underline{c}_{\Lambda})_{i} & 1 \leq k \leq m-1. \end{cases}$$

$$(2.6)$$

The implementation of Equation (2.5) is possible with an (m-1) stage linear feed-forward shift register while that of Equation (2.6) requires an (m-1) stage linear feed-back shift register.

Considering the specific case of  $\Theta = \Omega$ , as a polynomial basis, i.e.,

$$\Theta = \{1, \omega, \omega^2, \cdots, \omega^{m-1}\},\$$

where  $\omega$  satisfies an irreducible polynomial  $F(\omega) = 0$ , then, field element representation with respect to the corresponding triangular basis has the feature:

$$\underline{\omega}_{\Lambda}^{j} = (t_{j+1}, t_{j+2}, \cdots, t_{j+m})$$

with  $t_0 = 1$ ,  $t_1 = t_2 = \cdots = t_{m-1} = 0$ , and

$$t_k = \sum_{i=0}^{m-1} f_i t_{k-m-i}$$

for  $k \ge m$ ,

which can be implemented using a conventional m stage linear feedback shift register (LFSR) with F(x) as its feedback function [50].

## 2.2 Multiplicative Inversion

Multiplicative inverse of element A, denoted by  $A^{-1}$ , is defined as  $A \cdot A^{-1} = 1$ . When polynomial basis is used, we have

$$A(x) \cdot A^{-1}(x) \equiv 1 \mod F(x),$$

where F(x) is its defining irreducible polynomial. It is known that all nonzero elements of the field have distinct inverses. Commonly, multiplicative inversion is computed using one of the following techniques:

• Fermat's little theorem scheme [28, 30, 57, 106],

- extended Euclidean algorithm (EEA) [5,15,40,41], or extended binary (Stein's) GCD computation [54,103,110,116]

- the solution of a set of linear equations [21, 46, 108].

Before describing algorithmic techniques a possible non algorithmic method to compute inverses and its main drawback is mentioned.

#### 2.2.1 Non-Algorithmic Look-Up Table Inversion

The easiest and the fastest method to find the inverse of a field element would be a look-up table technique. Since the inverses of field elements are unique, a look-up table can be precomputed. In [68, 105], some variants of this method have been proposed and implemented. For example in [105], Vries et al. proposed a ROM look-up table scheme for a field dimension of (m=8) which had better performance in terms of area and time when compared to algorithmic schemes of the same dimension. However, such a non-algorithmic scheme is only suitable for "small" size fields, where "small" is understood by the amount of available memory. In addition, there are proposals in which in order to compute the inverses of specific large field elements, *i.e.*, Optimal Extended Fields, first the element is reduced to a subfield element where the inverses can be easily computed by other means such as binary extended Euclidean algorithm [6], direct parallel inversion [91] or a look-up table method.

#### 2.2.2 Fermat's Little Theorem Based Inversion

The easiest but not necessarily the most efficient method to compute the multiplicative inversion is using Fermat's little theorem which reduces inversion computation to a series of multiplication (and/or squaring). Fermat's little theorem [36] asserts,

**Theorem 2.1** If  $\beta$  is an element of  $GF(2^m)$ , then

$$\beta^{2^m - 1} = 1. (2.7)$$

Then, the inverse of  $\beta$  is given by

$$\beta^{-1}=\beta^{2^m-2}.$$

Thus the following efficient method to compute the inverse element  $\beta^{-1}$  using Fermat's theorem can be devised. It is known that

$$2^m - 2 = \sum_{i=1}^{m-1} 2^i,$$

the element  $\beta^{2^m-2}$  may be written as

$$\beta^{-1} = \beta^{2^m - 2} = \beta^{2^1} \times \beta^{2^2} \times \dots \times \beta^{2^{m-1}}.$$

(2.8)

If there is a basis where either squaring or multiplication is "cheap" and/or fast, the above scheme will be useful. In *normal basis* representation, it is said that the *squaring* can be computed by simple shift operation. Hence, efficient algorithms can be devised. For example Wang et al., in [106], proposed a simple but costly implementation of Equation (2.8). In such a scheme the number of iterations are equal to the dimension of the field minus one. That is a total of (m-1) squaring and (m-2) multiplications are needed.

In [111], Wei uses the following recursive expression

$$2^m - 2 = 2(1 + 2 + (1 + 2(1 + \cdots))),$$

where number of iterations is (m-1), to devise a polynomial basis inversion algorithm based on Fermat's theorem such that

$$\beta^{-1} = (\beta \cdots \beta (\beta (\beta (\beta^2)^2)^2)^2. \tag{2.9}$$

Also in this technique, a total of (m-1) squaring and (m-2) multiplications are needed. In order to speed up the algorithm different alternatives are possible. In [28], Feng and in [57], Itoh and Tsujii have proposed variants of Fermat's theorem scheme where the number of multiplications can be reduced. In general, for a normal basis where the squaring is almost free, the multiplication operation is a costly one and all the optimization of the design must be concentrated on it. Optimal normal basis provides an alternative solution for multiplication optimization. Reducing the number of multiplications by choosing certain basis to have a low Hamming weight binary representation is an approach. For example, Feng uses the binary expression of m-1

$$m-1 = m_q 2^q + m_{q-1} 2^{q-1} + \dots + m_1 q^1 + m_0 2^0, \qquad m_i \in \{0, 1\}, \ 0 \le i \le q$$

(2.10)

to devise an efficient inversion algorithm [28]. Hence, in order to compute  $\beta^{-1}$ , (q+p) multiplications and (m-1) squarings are required, where p is the number of one's in the binary expression of m-2. On average, the computational complexity can be reduced to  $O(m \times \log m)$ . According to algorithm in [28], both simple squaring and square-rooting are required which can efficiently be implemented by right and left shift operations respectively.

In [57], Itoh and Tsujii have proposed an alternative approach to reduce the number of multiplication using normal basis which requires only forward squaring and its implementation is easier. The Itoh and Tsujii's scheme uses the fact that since the inverse of an element  $\beta$  in a field according to Fermat's little theorem is:

$$\beta^{-1} = \beta^{2^m - 2} = \left(\beta^{2^{m-1} - 1}\right)^2,$$

then, if m is odd, i.e., (m-1) is even, knowing

$$2^{m-1} - 1 = \left(2^{(m-1)/2} - 1\right) \left(2^{(m-1)/2} + 1\right),$$

then

$$\beta^{2^{m-1}-1} = \left(\beta^{2^{(m-1)/2}-1}\right)^{2^{(m-1)/2}+1},$$

and this operation requires only one multiplication to compute  $\beta^{2^{m-1}-1}$  knowing  $\beta^{2^{(m-1)/2}-1}$ ; recall that squaring is free and it is not counted. Also, if m is even, then

$$\beta^{2^{m-1}-1} = \beta^{2(2^{(m-1)/2}-1)(2^{(m-1)/2}+1)+1},$$

and it requires two multiplications to evaluate  $\beta^{2^{m-1}-1}$ , once  $\beta^{2^{(m-1)/2}-1}$  has been computed.

Thus a recursive algorithm with minimum number of multiplications can be devised. In general, when m is the field dimension, exactly  $\lfloor \log{(m-1)} \rfloor + \omega{(m-1)} - 1$  field multiplications are required, where  $\omega{(m-1)}$  denotes the Hamming weight, the number of 1's in the binary representation of (m-1). To summarize, in general, efficient inversion algorithms in normal basis require:

- Number of Multiplications =  $\lfloor \log (m-1) \rfloor + \omega(m-1) \le 2 \lfloor \log (m-1) \rfloor$

- Number of Shifts = m-1

Both algorithms in [28] and [57] have similar computational complexities. Itoh's algorithm in [57], although simpler to implement, requires a stack structure to hold the intermediate temporary results. That is the algorithm is not completely serializable with use of a single temporary variable. In [3], Agnew et al. have discussed the hardware implementation of this scheme and its space requirements. They showed how to modify the scheme in order to trade-off an increase in number of multiplications for the space requirements. The following scheme is proposed. Suppose that m-1=gh. Then

$$2^{m-1} - 1 = 2^{gh} - 1 = (2^g - 1) \left( \sum_{i=0}^{h-1} 2^{gi} \right).$$

(2.11)

Now,

$$\beta^{-1} = \beta^{2^{m-1}-2} = \beta^{2(2^{m-1}-1)} = \gamma^{(2^g-1)(\sum_{i=0}^{h-1} 2^{gi})}, \tag{2.12}$$

where  $\gamma = \beta^2$ . Then  $\lambda = \gamma^{(2^g-1)}$  can be calculated in g-1 multiplications and  $\lambda^{\sum_{i=0}^{h-1} 2^{gi}}$  can be computed in h-1 multiplications. Hence,  $\beta^{-1}$  can be computed in (g+h-2) multiplications. It is said that the number of multiplications using this approach is minimized when g and h are about  $\sqrt{m-1}$ . In the case that such suitable values are not available, alternative factorizations methods can be used [3].

### 2.2.3 Extended Euclidean Algorithm Based Inversion

If a fast multiplier (squarer) does not exist, then the most efficient way to compute inverses is using schemes based on Extended Euclidean Algorithm (EEA) or binary (Stein's) GCD computation. The EEA is based on the classical Euclidean algorithm which computes the greatest common divisor of two integers greater than unity. The Euclidean algorithm in its polynomial form may be generalized to computes the greatest common divisor of two polynomials greater than zero polynomial. In this section a first description of EEA is provided. But in the next chapter, a detail comparison of implementations based on variants of EEA and binary GCD computation will be reviewed.

In an extended Euclidean algorithm (EEA) not only the GCD of two polynomials a and b but also two auxiliary polynomials a' and b' are computed such that

$$aa' + bb' = GCD(a, b).$$

The advantage is that the computation of three unknowns: GCD(a, b), a', b', can be done simultaneously by keeping track of only two vectors of three elements each. In the following, the application of EEA over polynomial to compute the inverse of an element is presented.

Let A(x) be a polynomial corresponding to element  $A \in GF(2^m)$ , where  $GF(2^m)$  is defined by the irreducible polynomial F(x). Since F(x) is an irreducible polynomial, GCD(F(x), A(x)) = 1. In order to compute the *inverse* of A(x), *i.e.*, A'(x), the following relationship can be used

$$A(x)A'(x) + F(x)U(x) = 1.$$

(2.13)

Constructing two initial equations

$$A(x)A'^{(-1)}(x) + F(x)U^{(-1)}(x) = R^{(-1)}(x), (2.14)$$

$$A(x)A'^{(0)}(x) + F(x)U^{(0)}(x) = R^{(0)}(x), (2.15)$$

where  $A'^{(-1)}(x) = 0$ ,  $A'^{(0)}(x) = 1$ ,  $U^{(-1)}(x) = 1$ ,  $U^{(0)}(x) = 0$ , and  $R^{(-1)}(x) = F(x)$ ,  $R^{(0)}(x) = A(x)$ . Now, applying a GCD computation sequence to pair  $[R^{(-1)}(x), R^{(0)}(x)]$ , at each iteration, a triple of auxiliary polynomials can be computed as

$$A'^{(i)}(x) = A'^{(i-2)}(x) + Q^{(i)}(x)A'^{(i-1)},$$

$$U^{(i)}(x) = U^{(i-2)}(x) + Q^{(i)}(x)U^{(i-1)},$$

$$R^{(i)}(x) = R^{(i-2)}(x) + R^{(i)}(x)U^{(i-1)},$$

where  $Q^{(i)}(x) = \lfloor R^{(i-2)}(x)/R^{(i-1)}(x) \rfloor$ . Note that addition and subtraction over GF(2) are the same. With these transformations at the *i*th step when  $Q^{(i)}(x) = GCD(A(x), F(x)) = 1$  is reached, then Equation (2.13) can be conceived as

$$A(x) \cdot A'^{(i)}(x) + F(x) \cdot U^{(i)}(x) \equiv 1 \pmod{F(x)}.$$

F(x) is an irreducible polynomial,  $F(x) \cdot U^{(i)}(x) \equiv 0 \pmod{F(x)}$  always, and  $A'^{(i)}(x)$  is the *inverse* of element A(x).

As far as numbers of iterations, in [87], two theorems by Norton show that for uniformly distributed normalized polynomials of degree m and n over GF(2), the average number of iterations of a binary left- or right-shift GCD algorithm is

$$\frac{1}{2}m + \frac{1}{3}n + O(1)$$

if  $m \ge n \ge 0$ ,

and the maximum number of iterations, the worst case, is

$$m + \left\lfloor \frac{n}{2} \right\rfloor + 1.$$

These results improve similar estimations by Knuth [63]. The average number of EEA iterations is less than Fermat's little theorem and also the operations needed in each iteration can be efficiently implemented, as it will be shown.

## 2.3 Summary

In this chapter, a brief review of basis representation of elements in extension fields has been presented. It has been mentioned that the choice of an efficient technique for inversion and other operations are intimately tied to the choice of basis representation of the field. Next, some methods for computing inverses, most importantly those based on Fermat's little theorem have been reviewed.

In the next chapter, methods to compute inverses based on variants of extended Euclidean algorithm or binary (Stein's) GCD algorithm will be compared and classified. Further, it will be shown that a method based on solving a set of linear equations using double-basis (polynomial and triangular) representation can make use of EEA type algorithms for efficient inversion and division computation.

## Chapter 3

# (Extended) Euclidean and Binary GCD Algorithm

## 3.1 Greatest Common Divisor Computation

The Greatest Common Divisor (GCD) computation is fundamental to algebraic and symbolic operations. Algorithms and implementations applied to integers can be easily modified for polynomials hence applied to Galois fields. In particular, the extended variants of the GCD computation has many applications in coding theory and cryptography. Because of inherent parallelism and iterative nature of many algorithms based on GCD, especially those applied to Galois fields, an iterative hardware mapping of these is common.

The greatest common divisor (GCD) can be defined as follows. If r and s are integers (or polynomials), not both zero, their greatest common divisor, gcd(r, s), is the larger integer (or polynomial) that evenly divides both r, s [64].

#### 3.1.1 Basic GCD and EEA

In [64], Knuth provides the classic GCD and EEA algorithms for integers, which can readily be extended for polynomials.

It can be noted that primarily the GCD computation is a repeated remainder calculation. However, the repetition itself makes a GCD computation more complex than its basic

#### Algorithm 1 Classic GCD computation Algorithm.

```

input: r and s integers or polynomials.

output: gcd(r, s).

while (s \neq 0) do

[r, s] \leftarrow [s, r \pmod{s}];

return r

```

remainder calculation. Algorithm 1 shows the classic GCD computation where the value of s decreases monotonically in all steps, and  $s \leq r$  always, except in the first iteration if s > r at input. This condition  $s \leq r$  ensures the termination of the algorithm. Let us assume that  $s \leq r$  at input, then the worst case number of iterations occurs when the integer inputs are consecutive Fibonacci numbers. In this case the binary representation of an integer s decreases at most one bit at each iteration. For an s = r and s = r are consecutive Fibonacci numbers. In this case the binary representation of an integer s = r and s = r and s = r are consecutive Fibonacci numbers. For an s = r and s = r are consecutive Fibonacci numbers are consecutive Fibonacci numbers. For an s = r and s = r are consecutive Fibonacci numbers are consecutive Fibonacci numbers. In this case the binary representation of an integer s = r and s = r are consecutive Fibonacci numbers. For an s = r and s = r are consecutive Fibonacci numbers are consecutive Fibonacci numbers. For an s = r are consecutive Fibonacci numbers are consecutive Fibonacci numbers. For an s = r are consecutive Fibonacci numbers are consecutive Fibonacci numbers. For an s = r are consecutive Fibonacci numbers are consecutive Fibonacci numbers. For an s = r are consecutive Fibonacci numbers are consecutive Fibonacci numbers. For an s = r are consecutive Fibonacci numbers are consecutive Fibonacci numbers. For an s = r are consecutive Fibonacci numbers are consecutive Fibonacci numbers. For an s = r are consecutive Fibonacci numbers are consecutive Fibonacci numbers. Fibonacci numbers are consecutive Fibonacci numbers are consecutive Fibonacci numbers. Fibonacci numbers are consecutive Fibonacci numbers are consecutive Fibonacci numbers. Fibonacci numbers are consecutive Fibonacci numbers are consecutive Fibonacci numbers are consecu

$$gcd(r,s) = gcd(s, r - qs), (3.1)$$

$$gcd(r,0) = |r|. (3.2)$$

Equation (3.1) represents a GCD-preserving transformation, also described by Brent et al. in [14]. Formally, in a GCD-preserving transformation, a pair of polynomials [r,s] are transformed into  $[\overline{r}, \overline{s}]$  such that  $gcd(\overline{r}, \overline{s}) = gcd(r, s)$ . Other such transformations will be mentioned in all GCD and EEA variants. The extended Euclidean Algorithm (EEA) based on Algorithm 1 is shown in Algorithm 2.

In Algorithm 2, the implementation of  $[w_3, u_3, t_3]$  are not required if  $[w_1, u_1, t_1]$  and  $[w_2, u_2, t_2]$  can be updated simultaneously, as is the case in hardware implementations. More importantly, if  $w_3$ ,  $u_3$ , and  $t_3$  can be updated simultaneously, *i.e.*,  $w_3$  and  $u_3$  can be transformed according to the  $t_3$  transformation, then these remainders can be computed with no need to compute q explicitly.

In EEA, the sequence of t's represents the gcd transformation sequence, and the sequence of u's, the result transformation sequence (for inversion and division). At each

#### Algorithm 2 Extended Euclidean Algorithm (EEA).

```

input: r and s integers or polynomials.

output: w, u, t such that w \ r + u \ s = t = gcd(r, s)

[w_1, u_1, t_1] \leftarrow [1, 0, r]; \quad [w_2, u_2, t_2] \leftarrow [0, 1, s];

while (t_2 \neq 0) do

q \leftarrow \lfloor t_1/t_2 \rfloor such that t_1 - qt_2 = t_3;

[w_3, u_3, t_3] \leftarrow [w_1, u_1, t_1] - [w_2, u_2, t_2]q;

[w_1, u_1, t_1] \leftarrow [w_2, u_2, t_2]; \quad [w_2, u_2, t_2] \leftarrow [w_3, u_3, t_3];

return w_1, u_1, t_1

```

iteration i, the invariant of Algorithm 2 is

$$w_i r + u_i s = t_i. (3.3)$$

The division step of Algorithm 2 required to compute a remainder, explicitly shown as modulo reduction in Algorithm 1, is computationally expensive and alternatives to it must be found. All efficient implementations, in particular for large size of operands in hardware designs, implement this remainder calculation in a *stepwise* fashion, *e.g.*, digit or bit serial. In general, this is achieved by a single step shift per iteration up to an *alignment* condition. This operation represents the first common task of all algorithms which will be reviewed in this thesis. We will refer to this as Task 1. There are two classes of architecture to perform such a stepwise shift and alignment operation. These are referred to as *left-shift* and *right-shift* algorithms. Let us start with right-shift class of algorithms.

## 3.2 Right-Shift GCD Algorithm, Right-Shift EEA

An alternative to the classic GCD computation without a division step is the binary GCD (or Stein's) algorithm, also called right-shift or low-order first, which uses only additions, shifts and comparisons. These are so called since they perform *GCD-preserving* transformations based on checking the value of the lowest order coefficients of polynomials or least significant bit (lsb) of integers. Polynomials (or integers) shrink from their higher order degrees (or most significant bits) but not necessarily monotonically, up to reaching

a zero remainder as expected by the classic GCD algorithm. In the following six variants of binary GCD algorithm or their extended versions are discussed.

#### 3.2.1 Binary GCD Algorithm and its Plus-Minus Variant

The basic variant of binary GCD (Stein's) algorithm is shown in Algorithm 3.

#### **Algorithm 3** Stein's Binary GCD Algorithm.

**input:** r and s non-negative integers or polynomials, where  $s_0 = 1$ , and  $s_0$  represents the lsb of binary representation of integer s, or the coefficient of degree zero of polynomial s.

```

output: gcd(r, s).

while (r \neq 0) do

while (r_0 = 0) do

r \leftarrow r/2;

if (r < s) then

[r, s] \leftarrow [s, r]; // swap //

r \leftarrow r - s;

return s

```

In Algorithm 3, no division step is required and this implies that a newly computed r may be less or greater than s, in contrast with Algorithm 1 where it is ensured that  $s \leq r$  always. Hence, the division step is eliminated at the expense of a comparison and a probable **swap** step. In Algorithm 3, the comparison step and a possible **swap** is required to ensure  $s \leq r$ , but the implementation complexity of such a task plus a stepwise shift and alignment operation to implement Task 1 is by far less than a division step. On the other hand, on average the number of iterations of Algorithm 3 are much greater than Algorithm 1 using a division step applied on the same set of input values, however in a hardware implementation, each iteration (cycle) time of Algorithm 3 is much shorter than Algorithm 1. In practice, all GCD and extended GCD computation algorithms, except one [56], which implement a variant of Task 1, have a **swap** condition checking mechanism as well. We will refer to this as Task 2.

A major difficulty in implementing Algorithm 3 is that the comparison (r < s) requires a knowledge of all digits of r and s which is not possible in certain (bit serial) implementations

and in any case it has  $O(\log r)$  computational complexity (Brent [14]). In [14], an efficient hardware alternative named plus-minus (PM) is proposed as shown in Algorithm 4.

```

Algorithm 4 Plus-Minus Variant of Binary GCD Algorithm for integers.

```

```

input: r, s, non-negative integers, where r is odd and s < r.

output: \gcd(r, s).

d \leftarrow 0; // This counter estimates the difference between \lceil \log |r| \rceil and \lceil \log |s| \rceil //

while (s \neq 0) do

while (s_0 = 0) do

s \leftarrow s/2; d \leftarrow d + 1;

if (d \geq 0) then

[r, s] \leftarrow [s, r] \quad d \leftarrow -d; // swap //

if ((r + s) \mod 4 = 0) then

s \leftarrow (r + s)/2;

else

s \leftarrow (r - s)/2;

return |r|

```

Algorithm 4 neither has a division step nor a comparison between two integers. A hardware implementation of Algorithm 4 may run faster than Algorithm 1 even though the  $s \leftarrow (r+s)/2$  operation may not allow an optimal decrease of integers at each iteration (as occurs in the classic GCD). Also, the hardware implementation of Algorithm 4 is more efficient than Algorithms 3. This is mainly due to possibility of using a counter to keep track of the number of shifts of integers. The counter value represents an estimate (an upper-bound) on the difference of the size of integers (or degree of polynomials). The computational complexity of the incrementer-decrementer of this counter is only  $O(\log \log r)$  as compared to  $O(\log r)$  required for the comparison step of Algorithm 3.

Algorithm 4 can be modified to compute polynomial GCD as well. In the specific case of binary polynomials, in fact, it can be simplified with no need to distinguish between plus or minus operation. Hence, a simplified variant as in Algorithm 5 may be considered.

In [87], Norton proves that in the worst case, the number of iterations of polynomial right-shift GCD algorithm over extended binary fields with polynomials of degree  $m \geq n \geq n$

**Algorithm 5** Plus-Minus Variant of Binary GCD Algorithm for binary polynomials.

```

input: r, s, binary polynomials, where r_0 = 1 and s < r.

output: \gcd(r, s).

d \leftarrow 0; // This counter estimates the difference between \deg(r) and \deg(s) //

while (s \neq 0) do

while (s_0 = 0) do

s \leftarrow s/x; d \leftarrow d + 1;

if (d \geq 0) then

\operatorname{swap}(r, s); d \leftarrow -d;

s \leftarrow (r - s)/x;

```

0 is  $m + \lfloor n/2 \rfloor + 1$ . It can be noted that this is less than what was said in Section 3.1.1. Achieving such a lower bound depends on the implementation feasibility and in the case of prime fields or polynomials over non-binary fields the previously stated lower bound, *i.e.*, m + n + 1, prevails.

The implementation of Algorithms 4 and 5 can be further optimized in hardware designs, specifically advantageous in bit serial architectures, where d can be represented by a "sign and magnitude unary" scheme. In this scheme the sign of d and the absolute value |d| are kept separate and a new variable  $\delta = 2^{|d|}$  represents the magnitude [17, 116]. Not only this scheme is suitable for bit-level pipelining but even in a centralized control scheme it eliminates the delay of incrementer-decrementer of a counter by using right or left shift operation. The representation of  $\delta$  requires a maximum of m+1 storage spaces, i.e., registers, which is available and convenient to have in a bit serial implementation. In other cases, this may not be a desirable feature. This representation of d which may represent the difference of degree of polynomials as well, can be used not only in the right-shift but also in the left-shift GCD algorithms as it will be discussed later.

Based on Algorithm 4, different schemes to compute multiplicative inverses are proposed. In [103], Takagi proposed a direct extension of Algorithm 4, similar to the EEA, to compute multiplicative inverses over integer prime fields. Next, Takagi et al. in [110], and Wu et al. in [115,116] proposed specific extended binary GCD algorithms to compute multiplicative inversion and division over binary finite fields  $GF(2^m)$ .

#### 3.2.2 Binary GCD Division Algorithm

An implementation of division over finite fields, using a direct application of Stein's algorithm is presented in [115] which is shown in Algorithm 6.

Algorithm 6 Modular Division over Prime Fields using Extended Binary GCD Algorithm. input: p prime field modulus, b integer dividend, a > 0 integer divisor.

```

output: b/a \mod p.

[r,s] \leftarrow [p,a] \quad [u,v] \leftarrow [0,b]

while (s>0) do

if (s=1) then

if (s<r) then

[r,s] \leftarrow [s,r-s]

[u,v] \leftarrow [v,(u-v) \mod p]

else

[r,s] \leftarrow [r,s-r]

[u,v] \leftarrow [u,(v-u) \mod p]

[r,s] \leftarrow [r,s/2]

[u,v] \leftarrow [u,(v/2) \mod p]

return v

```

In Algorithm 6 the pair [r, s] represents the gcd sequence and the [u, v] represents the result sequence. The gcd sequence follows the GCD-preserving transformation of Stein's algorithm, e.g.,  $[r, s] \leftarrow [r, s/2]$ . In Algorithm 6, also the result sequence follows the same GCD-preserving transformation, and a division  $b/a \mod p$  can be computed since each (u-v) or (v/2) operation is followed by a modulo reduction if necessary. Note that the modulo reduction step of this algorithm is required either a division or solely inversion is performed.

An important distinction between the modulo reduction required in the result transformation sequence and the one mentioned in the gcd transformation sequence is in order. The modulo reduction mentioned in the gcd transformation sequence represents an integer (or a polynomial) division to compute a remainder, corresponding to a shrinking divisor at each iteration. Hence, efficient solutions to implement it with right-shift or left-shift variants are proposed. However, a probable modulo reduction in the result transformation

sequence is an effective modulo reduction by an irreducible polynomial (or a modulus) of the underlying field. This modulo reduction, when required, cannot be transformed similar to the gcd transformation sequence case; even though, a stepwise implementation of the gcd transformation sequence may facilitate the implementation of this modulo reduction.

Another variant of Algorithm 6 proposed by Takagi et al. in [110], which will not be repeated, follows the Brent's idea and compares the degree of polynomials instead of polynomial themselves. Always in [110], a divider implementation is proposed which requires two counters, first to keep track of the *exit* condition of the **while** loop of Algorithm 6, and second to hold the difference of the degree of polynomials.

In [115], a hardware optimization of Algorithm 6 to implement a systolic divider over  $GF(2^m)$  with fixed number of iterations is proposed which is shown in Algorithm 7. Clearly, this implementation does not require the first counter described in [110]. In a systolic architecture the cost of a stepwise modulo reduction is contained. In Algorithm 7, the swap condition based on the degree tracking by a counter as described by Brent et al. and Takagi et al. is used as well.

**Algorithm 7** Polynomial Division over Binary Fields by Extended Binary GCD Algorithm.

```

input: f(x) irreducible polynomial of a field of dimension m, dividend b(x) and divisor a(x).

output: b(x)/a(x) \mod f(x).

d \leftarrow -1; \quad [r,s] \leftarrow [f(x),a(x)]; \quad [u,v] \leftarrow [0,b(x)];

for (k=1 \text{ to } 2m-1) do

if (s_0=1) then

if (d<0) then

[r,s] \leftarrow [s,r+s];

[u,v] \leftarrow [v,u+v]; \quad d \leftarrow -d

else

[r,s] \leftarrow [r,r+s];

[u,v] \leftarrow [u,u+v];

[r,s] \leftarrow [r,s/x];

[u,v] \leftarrow [u,(v/x) \mod f(x)]; \quad d \leftarrow d-1;

return v

```

In Algorithm 7, the overwriting of r and u occurs only when d < 0, which means the number of shifts of s is greater than r. In other words, it corresponds to the case s < r of Algorithm 6. Also, in a binary field case, all subtractions are substituted with XOR operations, hence no ordering of polynomials where d < 0 or otherwise is shown.

Algorithm 7 is the first algorithm in which a new formulation of the exit condition is provided. We will refer to this exit condition checking as Task 3. All algorithms presented here have a variant of this. In Algorithm 7, the **while** loop with exit condition checking s > 0 is changed into a **for** loop of 2m - 1 since the maximum number of iterations require for polynomial s to reach zero is 2m. This is a typical case for hardware implementations where irregular behavior and hence condition checking such as variable number of iterations are not desirable. For example, systolic architectures where an exact number of iterations can be mapped into an exact number of processing elements.

#### 3.2.3 Almost Inverse Algorithm

In [96], another variant of the extended Binary GCD algorithm for computing multiplicative inverses over finite fields named *Almost Inverse Algorithm* is proposed which is shown as Algorithm 8.

Algorithm 8 combines ideas from Stein's binary GCD algorithm for the gcd sequence transformation and Berlekamp's result sequence transformation [12] described later. Also in this algorithm, the pair [r, s] represents the gcd transformation sequence and the [u, v] represents the result transformation sequence. The gcd transformation sequence follows the GCD-preserving transformation of Stein's algorithm. This algorithm avoids a possible costly modulo reduction of the result sequence. However, it cannot compute division since no modulo reduction is used. When Algorithm 8 ends, It returns an output  $ux^k$  such that  $u \equiv a^{-1}(x) \mod f(x)$ , where f(x) can be either the binary representation of prime field modulus or the irreducible polynomial or a binary field, and x is the indeterminant of polynomial representation of field elements. When it terminates the inputs and the outputs are related by

$$wx^k f(x) + ux^k a(x) = x^k.$$

Hence, in order to get the correct result, it is necessary to divide  $ux^k$  by  $x^k$ , or multiply by  $x^{-k}$ .

#### Algorithm 8 Almost Inverse Algorithm.

```

input: f(x) prime field modulus or irreducible polynomial, a(x) a field element.

output: ux^k, k where u \equiv a^{-1}(x) \mod f(x).

k \leftarrow 0; [r, s] \leftarrow [f(x), a(x)]; [u, v] \leftarrow [1, 0];

while (\deg(s) > 0) do

if (s_0 \neq 0) then

if (\deg(s) < \deg(r)) then

[r,s] \leftarrow [s,(r-s)];

// swap //

[u,v] \leftarrow [(u-v),u];

else

[r,s] \leftarrow [r,(s-r)];

[u,v] \leftarrow [(v-u),v];

while (s_0 = 0) do

[r,s] \leftarrow [r,(s/x)];

[u,v] \leftarrow [u,(vx)]; \quad k \leftarrow k+1;

return ux^k, k

```

Algorithm 8 as shown requires three counters (more efficient hardware implementations are possible). First, two independent counters are needed to keep track of  $\deg(s)$  and  $\deg(r)$ . Note that these counters are not simple incrementer-decrementers since at each **swap** a new value of s with a possible new degree value is computed. The difference of these two counters is used for the **swap** condition checking. Next, a third counter is required to keep track of total number of shifts of s. This third counter is represented by k in Algorithm 8. A relationship between k and the degree of r and s at each iteration can be found but its implementation may not be more efficient hence it is not explicitly shown or used here.

In Algorithm 8 the result sequence follows a transformation due to Berlekamp [12] which is identified by an reverse shifting of result sequence with respect to the gcd sequence. This is particularly useful since no modulo reductions applied to partial results are required. Only a final modulo reduction after multiplication by  $x^{-k}$  is needed. Hence, this algorithm may have efficient implementation where intermediate modulo reductions are expensive, e.g., software implementations, and on the other hand, for certain classes of irreducible

polynomials the final multiplication by  $x^{-k}$  and modulo reduction can be implemented efficiently [96]. However, in [113], it is shown that Algorithm 8 is not suitable for other software implementations.

In [33], a comparison between Algorithm 8 and 7 in computing both inversion and division has shown that only under certain choices of *suitable* irreducible polynomials, Almost inverse algorithm has a better performance as reported in other papers. Let  $F(x) = \sum_{i=0}^{m} f_i$  be irreducible polynomial and  $l = \min\{i \geq 1 \mid f_i = 1\}$ . Now, "the irreducible polynomial is said to be *suitable* if l is above some threshold which may depend on the implementation, e.g.,  $l \geq 32$  ... since, then, less effort is required in the reduction step." [33].

### 3.3 Left-Shift GCD Algorithm, Left-Shift EEA

In the previous six algorithms, the right-shift (or low-end or binary or Stein's) GCD Algorithm and its extended alternatives have been reviewed. A set of algorithms, dual to above, based on a direct modification of Euclidean GCD computation exists which is called left-shift or high-end GCD class of algorithms. These algorithms perform GCD-preserving transformations based on checking the value of the higher order coefficients of polynomials or most significant bit (msb) of integers. This class of algorithms is advantageous where polynomial or integers must be processed from the highest degree (or msb) first. Moreover, this class of algorithms can keep track of the exact difference of degree of polynomials (or size of integers), and where a least or optimal number of iterations per GCD computation may be achieved. Also, a specific variant of EEA of this class can compute multiplicative inverses with no modular reduction step at all.

All three tasks mentioned in the right-shift class are required in left-shift algorithms as well. The main difference regards the implementation of Task 1, which is discussed next.

In left-shift class of algorithms, in order to compute the quotient q or mainly the remainder of a division step of Algorithm 2, a series of stepwise transformations is used which mimics a "long division". The "long division" algorithm described by many authors [15, 17, 40, 119] is shown in Algorithm 9. (The application of Algorithm 9 to implement a systolic structure for inversion and division over extension binary fields is described in [17].

#### Algorithm 9 Polynomial Long Division Algorithm.

```

input: r and s polynomials.

output: r \pmod{s}.

\delta \leftarrow \deg(r) - \deg(s)

while (\delta \ge 0) do

[r,s] \leftarrow [(r-x^{\delta}s),s];

\delta \leftarrow \deg(r) - \deg(s);

return r

```

In Algorithm 9 consecutive values of  $\delta$ , if exist, represent the coefficients of quotient polynomial q of Algorithm 2, and the corresponding partial remainders of these "long division" steps are computed using simple subtractions accordingly. Algorithm 9 ensures to end with  $(\deg(r) < \deg(s))$ . In fact, at **input** no pre-condition on the degrees of r and s is imposed. It can be noted that Algorithm 9 is a GCD-preserving transformation. Algorithm 9 can be used for integers without any modification as well.

Next, a single division step of a GCD computation or EEA, as in Algorithms 1 and 2 can be substituted by a "long division", and a complete GCD computation or EEA can be implemented by as a series of "long-division" algorithm, plus a polynomial (or integer) **swap** mechanism between each two consecutive "long divisions". Hence, only simple operations: shift, subtraction and a mechanism to keep track of difference of the degree of polynomials are sufficient to complete GCD computation or EEA which are exactly the same operations seen in right-shift binary GCD schemes.

Left-shift class of GCD computation algorithms must ensure that the *exit* condition of Algorithm 1 seen in Section 3.1.1 holds at all iterations. This is said to be  $(s \le r)$ . At each iteration of Algorithm 9, if an implementation ensures that the left-shifted value  $x^{\delta}s$  is computed on-the-fly or it is not written over s, the *exit* condition holds. In other implementations where the shifted value of s are saved, either an auxiliary polynomial (storage) must be used or, more interestingly, a mechanism to keep track of the number of shifts of s must be in place. The former may be called a *restoring* and the latter a *non-restoring* gcd transformation sequence. While the former can be used for both polynomial or integer GCD computation, the latter is applicable only to polynomial GCD computation.

In a non-restoring case, a refinement of Algorithm 9 into an exact single step shifting

with re-ordered outputs can be devised as shown in Algorithm 10.

#### **Algorithm 10** Swapped Shifted Polynomial Long Division Algorithm.

```

input: r and s polynomials with \deg(r) > \deg(s).

output: x^{\delta}(r \pmod{s}), \ x^{\delta}s.

\delta \leftarrow 0

while (\deg(r) > \deg(s)) do

\delta \leftarrow \delta + 1

s \leftarrow xs;

[r, s] \leftarrow [s, (r - s)]; // first alignment, and overwriting of r //

while (\delta > 0) do

s \leftarrow xs;

if (\deg(r) = \deg(s)) then

s \leftarrow (r - s);

return r, s

```

Algorithm 10 is a modified version of Algorithm 9 where each polynomial is shifted one step at a time and the degree of shifted polynomials are not restored afterward. Here, a pre-condition is defined as the degree of its dividend to be greater than the degree of its divisor. And as a post-condition, it ensures that the degree of its shifted remainder is less than the degree of its shifted divisor at its termination.

In Algorithm 10, a  $\delta$  times shifted version of final remainder and the divisor are returned. Initially, the degree of dividend is greater than the degree of divisor by  $\delta$  units. For  $\delta$  iterations a divisor polynomial is left shifted. At a first alignment iteration where the degree of shifted divisor is reached the degree of dividend, a remainder polynomial is computed which may have a degree greater, equal or less than the pre-shifted divisor, but always its degree is less than the degree of the shifted divisor. Next, a "virtual" restoring of divisor starts. That is the degree of the shifted divisor is not decreased, but rather in the next  $\delta$  iterations, the remainder or partial remainders are left shifted where none, one or more other alignments may occur and new partial remainders may be computed. After exactly  $\delta$  iterations, the pre-shifted divisor is "virtually" restored, and in all these  $\delta$  iterations the remainder polynomial is continuously updated to a degree less than the shifted divisor. Thus, at the termination of each "long division" operation, its post-condition is ensured.