# Low Power Register Exchange Viterbi Decoder for Wireless Applications

by

Dalia Abdel-Wahed Fouad El-Dib

A thesis

presented to the University of Waterloo

in fulfilment of the

thesis requirement for the degree of

Doctor of Philosophy

in

Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2004 © Dalia Abdel-Wahed Fouad El-Dib 2004 I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### Abstract

Since the invention of wireless telegraphy by Marconi in 1897, wireless technology has not only been enhanced, but also has become an integral part of our everyday lives. The first wireless mobile phone appeared around 1980. It was based on first generation analog technology that involved the use of Frequency Division Multiple Access (FDMA) techniques. Ten years later, second generation (2G) mobiles were dependent on Time Division Multiple Access (TDMA) techniques and Code Division Multiple Access (CDMA) techniques. Nowadays, third generation (3G) mobile systems depend on CDMA techniques to satisfy the need for faster, and more capacious data transmission in mobile wireless networks. Wideband CDMA (WCDMA) has become the major 3G air interface in the world. WCDMA employs convolutional encoding to encode voice and MPEG4 applications in the baseband transmitter at a maximum frequency of 2Mbps. To decode convolutional codes, Andrew Viterbi invented the Viterbi Decoder (VD) in 1967. In 2G mobile terminals, the VD consumes approximately one third of the power consumption of a baseband mobile transceiver. Thus, in 3G mobile systems, it is essential to reduce the power consumption of the VD.

Conceptually, the Register Exchange (RE) method is simpler and faster than the Trace Back (TB) method for implementing the VD. However, in the RE method, each bit in the memory must be read and rewritten for each bit of information that is decoded. Therefore, the RE method is not appropriate for decoders with long constraint lengths. Although researchers have focused on implementing and optimizing the TB method, the RE method is focused on and modified in this thesis to reduce the RE method's power consumption.

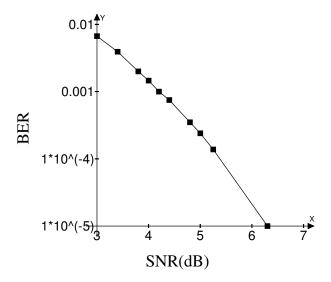

This thesis proposes a novel modified RE method by adopting a pointer concept for implementing the survivor memory unit (SMU) of the VD. A pointer is assigned to each register or memory location. The contents of the pointer which points to one register is altered to point to a second register, instead of copying the contents of the first register to the second. When the pointer concept is applied to the RE's SMU implementation (modified RE), there is no need to copy the contents of the SMU and rewrite them, but one row of memory is still needed for each state of the VD. Thus, the VDs in CDMA systems require 256 rows of memory. Applying the pointer concept reduces the VD's power consumption by 20 percent as estimated by the VHDL synthesis tool and by the new power reduction estimation that is introduced in this work. The coding gain for the modified RE method is 2.6dB at an SNR of approximately  $10^{-3}$ .

Furthermore, a novel zero-memory implementation for the modified RE method is proposed. If the initial state of the convolutional encoder is known, the entire

SMU of the modified RE VD is reduced to only one row. Because the decoded data is generated in the required order, even this row of memory is dispensable. The zero-memory architecture is called the MemoryLess Viterbi Decoder (MLVD), and reduces the power consumption by approximately 50 percent. A prototype of the MLVD with a one third convolutional code rate and a constraint length of nine is mapped into a Xilinx 2V6000 chip, operating at 25~MHz with a decoding throughput of more than 3Mbps and a latency of two data bits.

The other problem of the VD which is addressed in this thesis is the Add Compare Select Unit (ACSU) which is composed of 128 butterfly ACS modules. The ACSU's high parallelism has been previously solved by using a bit serial implementation. The 8-bit First Input First Output (FIFO) register, needed for the storage of each path metric (PM), is at the heart of the single bit serial ACS butterfly module. A new, simply controlled shift register is designed at the circuit level and integrated into the ACS module. A chip for the new module is also fabricated.

#### Acknowledgments

Foremost, all thanks are due to Almighty, the most merciful God. God blessed me and gave me the strength to finish this study while taking care of my family.

Prof. M.I. Elmasry, my thesis supervisor, has guided my work insightfully and enriched my research with his fruitful experience. Special thanks for trusting me and providing such a flexible working environment.

My parents, though not with me in Canada, have supported me with their love, care and prayers. Owing them my success, I will never be able to thank them enough. To them, I would like to express my sincere thanks.

My husband, Sherif Sadek, deserves a special acknowledgement. He has always encouraged me and stood by my side taking care of our little children (Hassan and Hussein). I would never have completed this work without his support. Also my dear and only brother, Mohamed El-Dib, has supported me unconditionally. Thanks to him and all my family members and friends.

Our VLSI system administrator, Phil Regier, has provided all of us with a very organized lab, and is always willing to help out with any technical problem. I really appreciate his dedication and experience, which helped me a lot throughout this research work.

CMC has provided me with a fabrication grant to fabricate my chip and provided technical support during the design, fabrication and test of the chip. Special thanks to Mariusz Jarosz and Hui Xu from CMC. Finally, I would like to acknowledge the financial support provided by the Egyptian government. OGSST and Professor Elmasry's NSERC Research Grants have supported my work for the last year.

### Contents

| 1 | Intr | oducti | ion                                    | 1  |

|---|------|--------|----------------------------------------|----|

|   | 1.1  | Motiva | ation for Low Power                    | 1  |

|   | 1.2  | Third  | Generation (3G) Mobile Systems         | 2  |

|   | 1.3  | Thesis | S Overview                             | 2  |

| 2 | Low  | Powe   | er Digital VLSI Design                 | 4  |

|   | 2.1  | Energ  | y Consumption versus Power Consumption | 4  |

|   | 2.2  | Source | es of Power Dissipation                | 4  |

|   |      | 2.2.1  | Switching Power                        | 5  |

|   |      | 2.2.2  | Short Circuit Power                    | 6  |

|   |      | 2.2.3  | Leakage Power                          | 7  |

|   |      | 2.2.4  | Static Power                           | 7  |

|   | 2.3  | Low P  | Power Design Techniques                | 7  |

|   |      | 2.3.1  | System Level Optimization              | 7  |

|   |      | 2.3.2  | Algorithm Level Optimization           | 8  |

|   |      | 2.3.3  | Architecture Level Optimization        | 9  |

|   |      | 2.3.4  | Logic Level Optimization               | 11 |

|   |      | 2.3.5  | Circuit Level Optimization             | 12 |

|   |      | 2.3.6  | Physical Level Optimization            | 13 |

| 3 | CD             | MA W     | Fireless Systems and Viterbi Decoders (VDs)            | 17 |

|---|----------------|----------|--------------------------------------------------------|----|

|   | 3.1            | Multip   | ole Access Comparison                                  | 17 |

|   |                | 3.1.1    | Frequency Division Multiple Access (FDMA)              | 18 |

|   |                | 3.1.2    | Time Division Multiple Access (TDMA) $\ldots \ldots$ . | 18 |

|   |                | 3.1.3    | Code Division Multiple Access (CDMA)                   | 19 |

|   | 3.2            | Brief 1  | History                                                | 20 |

|   | 3.3            | WCD      | MA Transceiver                                         | 23 |

|   |                | 3.3.1    | WCDMA Transmitter                                      | 23 |

|   |                | 3.3.2    | WCDMA Receiver                                         | 24 |

|   | 3.4            | Convo    | olutional Codes                                        | 25 |

|   | 3.5            | Viterb   | oi Algorithm (VA)                                      | 26 |

|   |                | 3.5.1    | Trace Back (TB) Method                                 | 28 |

|   |                | 3.5.2    | Register Exchange (RE) Method                          | 28 |

|   | 3.6            | Viterb   | pi Decoder (VD)                                        | 29 |

| 4 | Mo             | dified [ | Register Exchange (RE) Viterbi Decoder (VD)            | 31 |

|   | 4.1            | Survey   | ying the State of the Art Developments                 | 31 |

|   | 4.2            | Modif    | ied RE Method                                          | 34 |

|   |                | 4.2.1    | Performance Simulation Results                         | 37 |

|   |                | 4.2.2    | Other Suboptimal Decoders                              | 37 |

|   | 4.3            | VHDI     | Models for Comparison                                  | 39 |

|   |                | 4.3.1    | TB Survivor Memory Unit (SMU) VHDL Model               | 39 |

|   |                | 4.3.2    | Modified RE VHDL Model                                 | 40 |

|   |                | 4.3.3    | SMU Comparison                                         | 41 |

| 5 | $\mathbf{Adc}$ | d Com    | pare Select Unit (ACSU) Chip                           | 45 |

|   | 5.1            | Previo   | ous Designs for the ACSU                               | 45 |

|   | 5.2            | Bit Se   | erial ACS Architecture                                 | 47 |

|   | 5.3            | Simple   | e Shift Register                                       | 48 |

|          | 5.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Carry Propagation                                                                                  |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

|          | 5.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Low Power Adder                                                                                    |

|          | 5.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Chip Specifications                                                                                |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5.6.1 Chip Testing                                                                                 |

| 6        | Mei                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | moryless Viterbi Decoder (MLVD)                                                                    |

|          | 6.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Architecture of the MLVD                                                                           |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6.1.1 Convolutional Encoder                                                                        |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6.1.2 Branch Metric Unit (BMU)                                                                     |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6.1.3 Add Compare Select $Unit(ACSU)$                                                              |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6.1.4 Add Compare Select TO Survivor Memory (ACSTOSM) $$                                           |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6.1.5 Pointer                                                                                      |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6.1.6 Most Significant Bit (MSB)                                                                   |

|          | 6.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Power Consumption of the MLVD                                                                      |

|          | ٠                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | •                                                                                                  |

|          | 6.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Xilinx Implementation and Test Results                                                             |

| 7        | 6.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Xilinx Implementation and Test Results                                                             |

|          | 6.3<br>Con                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                    |

| Pι       | 6.3<br>Cor<br>ablic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | aclusions and Recommendations                                                                      |

| Pı<br>Bi | 6.3<br>Con<br>ablica                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | aclusions and Recommendations ations graphy                                                        |

| Pı<br>Bi | 6.3<br>Con<br>ablica<br>bliog                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | aclusions and Recommendations ations graphy DL code for the Memoryless Viterbi Decoder             |

| Pı<br>Bi | 6.3  Corublication of the coruble of | aclusions and Recommendations ations graphy  DL code for the Memoryless Viterbi Decoder  Lfsr.vhd  |

| Pı<br>Bi | 6.3  Corublication of the coruble of | aclusions and Recommendations ations graphy  DL code for the Memoryless Viterbi Decoder  Lfsr.vhd  |

| Pı<br>Bi | 6.3  Corublication of the coruble of | aclusions and Recommendations ations graphy  DL code for the Memoryless Viterbi Decoder  Lfsr.vhd  |

| Pı<br>Bi | 6.3  Corublication of the coruble of | aclusions and Recommendations ations  graphy  DL code for the Memoryless Viterbi Decoder  Lfsr.vhd |

| В | Inputs of the ACSUs | 109 |

|---|---------------------|-----|

|   | A.11 Viterbi.vhd    | 105 |

|   | A.10 Ledcounter.vhd | 104 |

|   | A.9 Comparator.vhd  | 103 |

|   | A.8 Pointer.vhd     | 102 |

|   | A.7 Bmu.vhd         | 101 |

### List of Figures

| 2.1  | Energy consumption versus power consumption                              |    |

|------|--------------------------------------------------------------------------|----|

| 2.2  | Glitching in static CMOS gates                                           | 6  |

| 2.3  | DC current in a Pseudo-NMOS inverter                                     | 8  |

| 2.4  | Simple and parallel architectures of an 8 x 8 multiplier $\dots \dots$   | 14 |

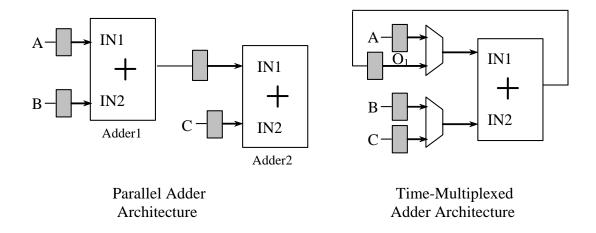

| 2.5  | Parallel and time-multiplexed architectures for a simple adder           | 15 |

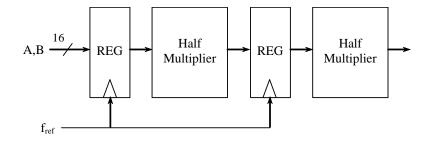

| 2.6  | Pipelined architecture for the multiplier                                | 15 |

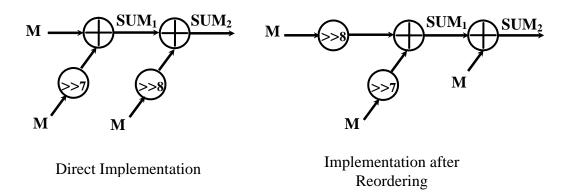

| 2.7  | Reducing activity by reordering inputs                                   | 16 |

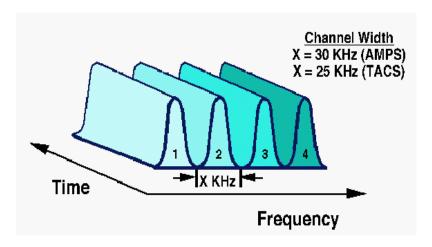

| 3.1  | FDMA waveform                                                            | 18 |

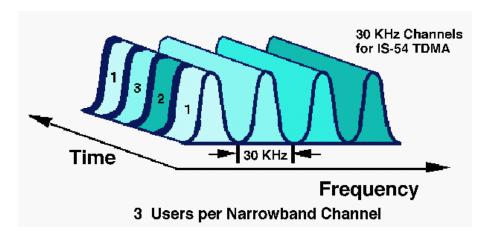

| 3.2  | TDMA waveform                                                            | 19 |

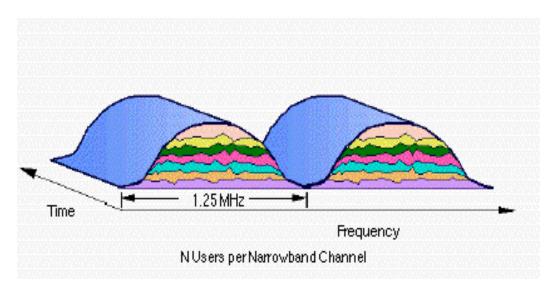

| 3.3  | CDMA waveform                                                            | 20 |

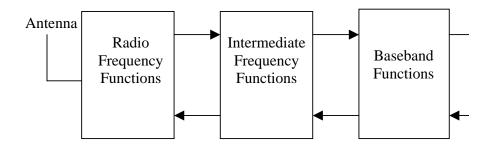

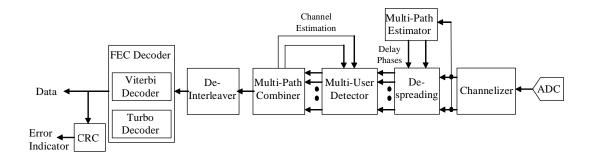

| 3.4  | Block diagram of a wideband CDMA transceiver                             | 23 |

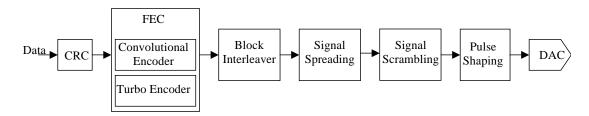

| 3.5  | Block diagram of a WCDMA digital transmitter                             | 23 |

| 3.6  | Block diagram of a digital WCDMA receiver                                | 24 |

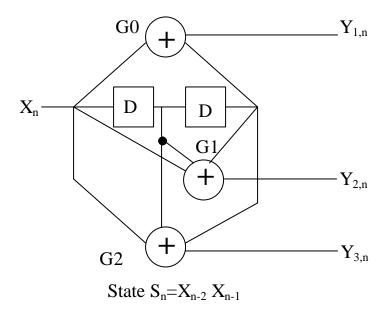

| 3.7  | 4 state rate $1/3$ convolutional encoder                                 | 25 |

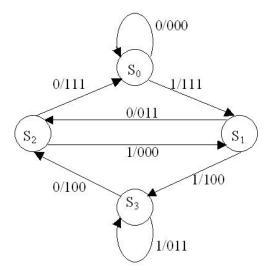

| 3.8  | State diagram for the encoder shown in Figure 3.7                        | 26 |

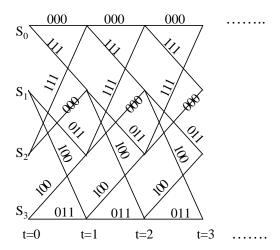

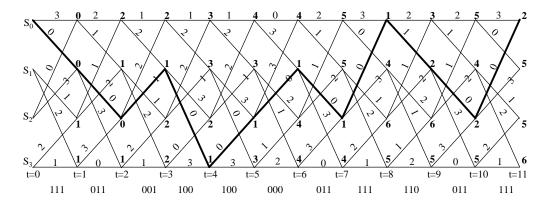

| 3.9  | Trellis diagram for the encoder shown in Figure 3.7                      | 27 |

| 3.10 | Trace Back (TB) Viterbi Decoding                                         | 28 |

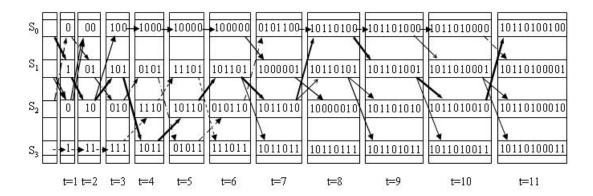

| 3.11 | Register Exchange (RE) Method                                            | 29 |

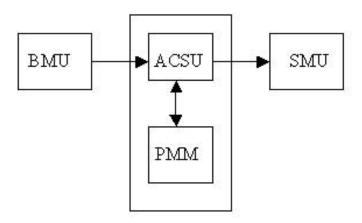

| 3.12 | Simplified block diagram of the VD $\ \ldots \ \ldots \ \ldots \ \ldots$ | 30 |

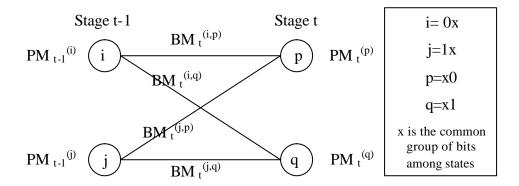

| 4.1  | Butterfly structure of the ACS                                           | 35 |

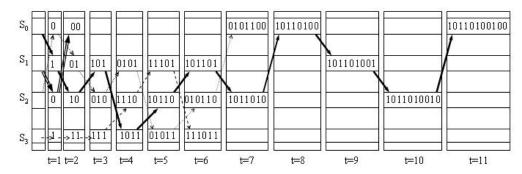

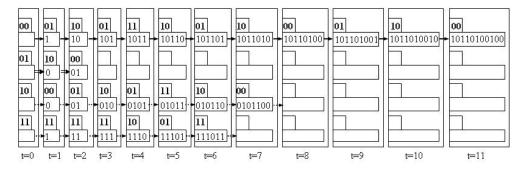

| 4.2 | Register contents for the modified RE method                                                                                           | 36 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------|----|

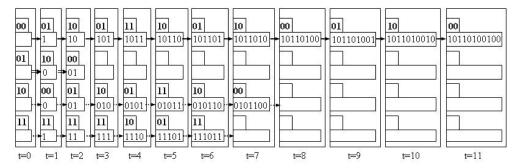

| 4.3 | New RE approach with pointer implementation (the upper register carries the pointer and the lower register carries the decoded bits) . | 37 |

| 4.4 | BER vs. SNR for the proposed modified RE method                                                                                        | 38 |

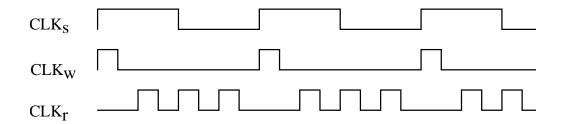

| 4.5 | Timing chart of the main clocks for the TB VD                                                                                          | 40 |

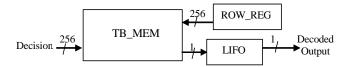

| 4.6 | VHDL block diagram of the TB SMU architecture                                                                                          | 40 |

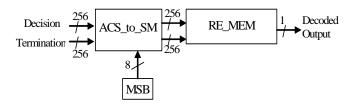

| 4.7 | VHDL block diagram for the new RE SMU architecture                                                                                     | 41 |

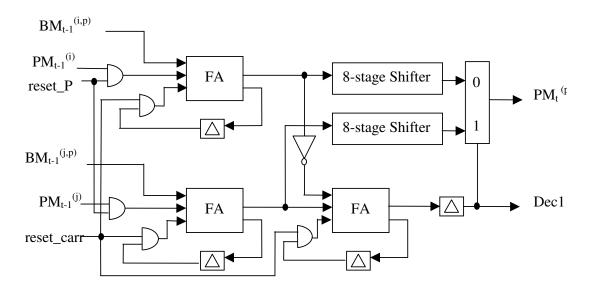

| 5.1 | Bit serial ACS architecture                                                                                                            | 47 |

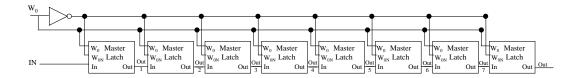

| 5.2 | 8-bit shifter                                                                                                                          | 48 |

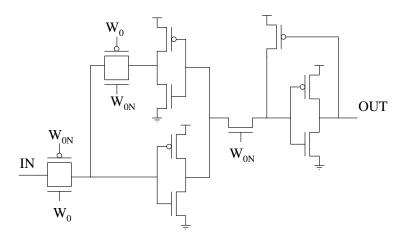

| 5.3 | New master latch                                                                                                                       | 48 |

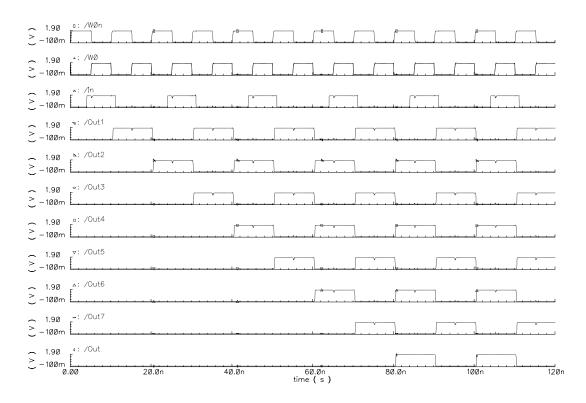

| 5.4 | Timing simulations for the 8-bit shifter                                                                                               | 49 |

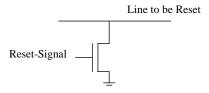

| 5.5 | Simple resetter                                                                                                                        | 50 |

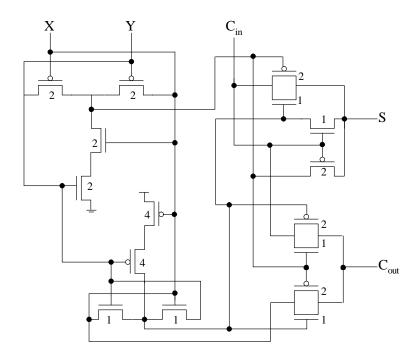

| 5.6 | 16-transistor low power FA                                                                                                             | 51 |

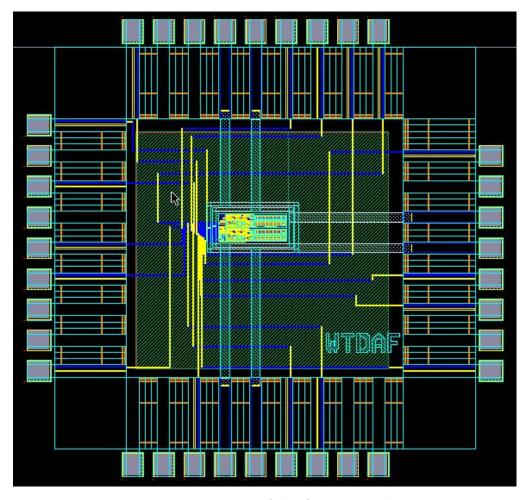

| 5.7 | Layout of the fabricated chip                                                                                                          | 52 |

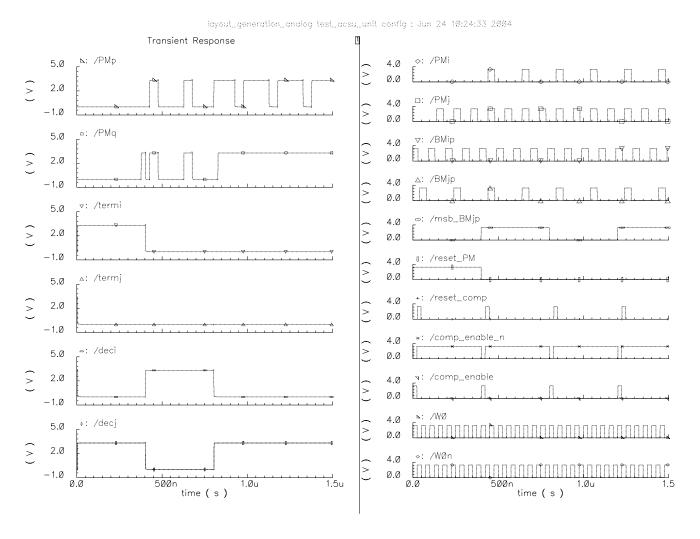

| 5.8 | Timing simulation of the layout                                                                                                        | 53 |

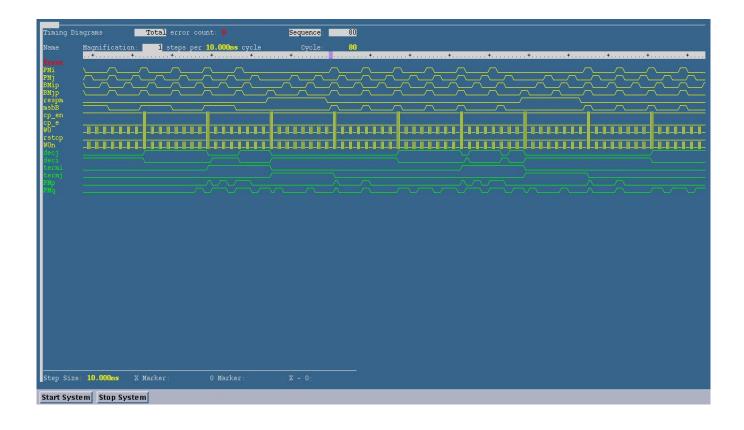

| 5.9 | Testing simulations of the chip on the IMS shifter                                                                                     | 55 |

| 6.1 | New RE approach with pointer implementation (the upper register carries the pointer and the lower register carries the decoded bits) . | 58 |

| 6.2 | MLVD approach with pointer implementation (the upper box carries the pointer and the lower box carries the decoded bits)               | 58 |

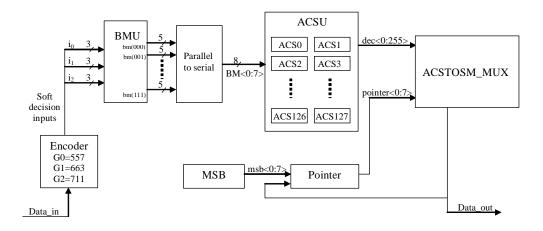

| 6.3 | MLVD block diagram                                                                                                                     | 59 |

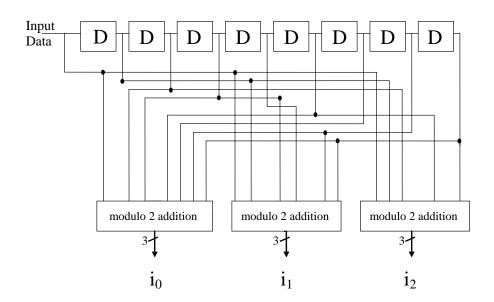

| 6.4 | Convolutional encoder: $G0=557$ , $G1=663$ , and $G2=711$                                                                              | 60 |

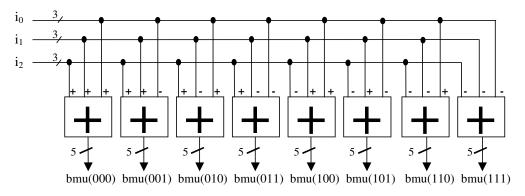

| 6.5 | Branch Metric Unit (BMU) operations                                                                                                    | 61 |

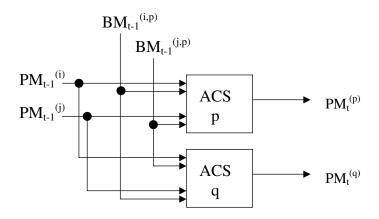

| 6.6 | One ACS butterfly module                                                                                                               | 62 |

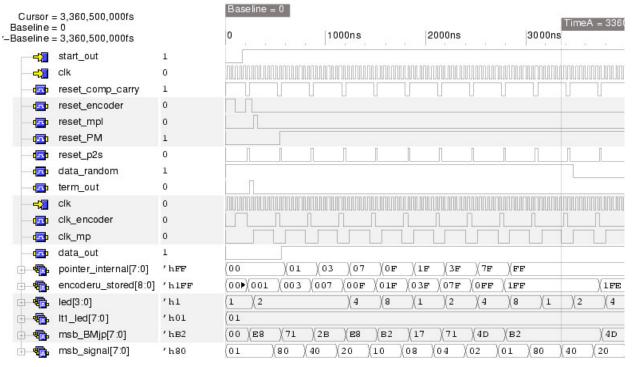

| 6.7 | Snapshot of the timing simulation for the routed MLVD                                                                                  | 66 |

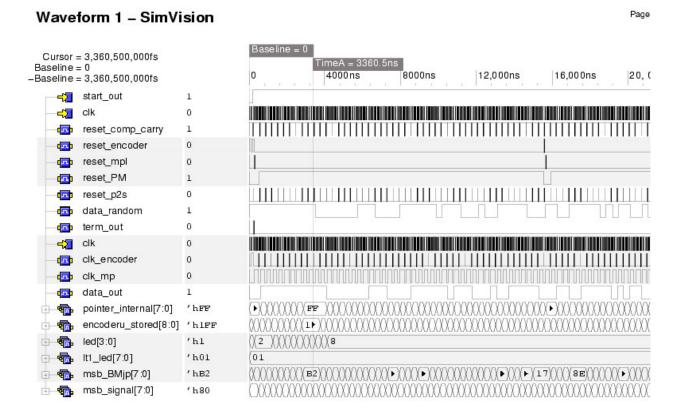

| 6.8 | Snapshot of the timing simulation for the routed MLVD (zoom out)                                                                       | 67 |

| 6.9 | Rapid prototyping system                                                                                                               | 68 |

### List of Tables

| 2.1 | Binary and gray code representations                                              | 10  |

|-----|-----------------------------------------------------------------------------------|-----|

| 3.1 | Evolutionary path of mobile generations                                           | 22  |

| 4.1 | Surveying the state of the art developments                                       | 33  |

| 4.2 | Comparison of the memory/register operations to decode $48$ codewords             | 43  |

| 4.3 | Estimated cost function for the memory/register operations to decode 48 codewords | 44  |

| 5.1 | Function of the control signals                                                   | 54  |

| 6.1 | VD specifications                                                                 | 59  |

| 6.2 | Estimated cost function to decode 48 codewords                                    | 64  |

| 6.3 | Specifications comparison                                                         | 65  |

| B.1 | ACSU modules connections                                                          | 109 |

### List of Abbreviations

| Abbreviation | Details                                          |  |  |

|--------------|--------------------------------------------------|--|--|

| 1G           | First Generation                                 |  |  |

| 2G           | Second Generation                                |  |  |

| 3G           | Third Generation                                 |  |  |

| ACS          | Add Compare Select                               |  |  |

| ACSTOSM      | Add Compare Select TO Survivor Memory            |  |  |

| ACSU         | Add Compare Select Unit                          |  |  |

| ADC          | Analog to Digital Converter                      |  |  |

| AMPS         | Advanced Mobile Phone Service                    |  |  |

| ASIC         | Application Specific Integrated Circuits         |  |  |

| AWGN         | Additive White Gaussian Noise                    |  |  |

| BER          | Bit Error Rate                                   |  |  |

| BM           | Branch Metric                                    |  |  |

| BMU          | Branch Metric Unit                               |  |  |

| CDMA         | Code Division Multiple Access                    |  |  |

| CMC          | Canadian Microelectronics Corporation            |  |  |

| CPL          | Complementary Pass Gate Logic                    |  |  |

| CRC          | Cyclic Redundancy Code                           |  |  |

| CS           | Carry Save                                       |  |  |

| CTIA         | Cellular Telecommunications Industry Association |  |  |

| DSP          | Digital Signal Processor                         |  |  |

| FDMA         | Frequency Division Mutliple Access               |  |  |

| GSM          | Global System for Mobile Communications          |  |  |

| IF           | Intermediate Frequency                           |  |  |

| IPR          | Intellectual Property Rights                     |  |  |

| ITU          | International Telecommunication Union            |  |  |

| LFSR         | Linear Feedback Shift Register                   |  |  |

| LSB          | Least Significant Bit                            |  |  |

| Abbreviation | Details                                  |  |  |

|--------------|------------------------------------------|--|--|

| MLVD         | MemoryLess Viterbi Decoder               |  |  |

| MSB          | Most Significant Bit                     |  |  |

| OVSF         | Orthogonal Variable Spreading Factor     |  |  |

| PCCC         | Parallel Concatenated Convolutional Code |  |  |

| PDC          | Personal Digital Cellular                |  |  |

| PM           | Path Metric                              |  |  |

| PMM          | Path Metric Memory                       |  |  |

| PSK          | Phase Shift Keying                       |  |  |

| QAM          | Quadrature Amplitude Modulation          |  |  |

| QPSK         | Quadrature Phase Shift Keying            |  |  |

| RE           | Register Exchange                        |  |  |

| RF           | Radio Frequency                          |  |  |

| RTL          | Register-Transfer-Level                  |  |  |

| SMU          | Survivor Memory Unit                     |  |  |

| TACS         | Total Access Communication System        |  |  |

| TB           | Trace Back                               |  |  |

| TDMA         | Time Division Multiple Access            |  |  |

| TTA          | Telecommunication Technology Association |  |  |

| UPR          | Users' Performance Requirements          |  |  |

| VA           | Viterbi Algorithm                        |  |  |

| VD           | Viterbi Decoder                          |  |  |

| VLSI         | Very Large Scale Integrated              |  |  |

| WCDMA        | Wideband Code Division Multiple Access   |  |  |

#### Chapter 1

### Introduction

From the advent of integrated circuits, circuit designers have been concerned with increasing circuit performance and minimizing the design area. Although low power microelectronics can be traced back to the invention of the transistor in 1947, it was an afterthought, not a design criterion. Today, a major creative challenge facing VLSI designers is to design products which consume minimal power on both the circuit level and the system level. This will significantly increase the battery life of portable devices, a necessity for the consumer who is on the go and requires a reliable and efficient wireless environment. Therefore, reducing the power consumption of 3G mobile terminals is the main objective of this thesis. The motivations for low power design are detailed in the next section.

#### 1.1 Motivation for Low Power

The motivation for low power electronics has been derived from the following needs:

- 1. To extend the battery lifetime for portable devices such as laptops, cellular phones, electronic organizers, pacemakers, and hearing aids. This is the earliest and the most demanding motivation for low power design.

- 2. To increase the packing density which imposes severe restrictions on the power dissipation density in order to further enhance the speed of high performance systems. Low power reduces the costs that are associated with packaging, cooling, and fans, in addition to keeping a certain level of system reliability, which is threatened by excessive power dissipation. This is the most recent motivation for low power design.

3. To curb the increasing power consumption of desktop and deskside systems, where a competitive cost to performance ratio demands low power operations to reduce the power supply and cooling costs. In addition, the fact that 50 percent of office power is used by PCs suggests that low power design is essential for reducing the overall power budget. This is the broadest need for low power design.

A brief introduction to 3G mobile terminals is given in the next section.

#### 1.2 Third Generation (3G) Mobile Systems

Since the introduction of cellular networks in the early 1980s, mobile technology has evolved very rapidly. In the 1990s 1G analog wireless systems were replaced by 2G digital technologies that delivered significant improvements in capacity, voice quality, and spectral efficiency. Most importantly, 2G digital technologies laid the foundation for the value added services, including data, which will continue to be enhanced into the future. Now, the 3G era that promises further improved network capacity provides high speed packet data, simultaneous data, and voice and realtime multimedia services.

The benefits of 3G to end users translate to the availability of a full suite of innovative services such as mobile access to intranets or the Internet, videoconferencing, and sending and receiving high quality images. 3G terminals and devices can provide the user interface for experiencing these enhanced services. CDMA2000 and WCDMA are two technologies that have been approved for 3G. Since the world's first commercial 3G network was based on WCDMA, the VD, which is part of the WCDMA mobile terminal, is investigated in this thesis to reduce the VD's power consumption.

#### 1.3 Thesis Overview

Chapter 2 deals with the sources of power dissipation and the various low power design techniques. In Chapter 3, an overview of CDMA mobile systems and the application of the Viterbi Algorithm (VA) to decode the convolutional codes in such systems is presented. Chapter 4 introduces the pointer concept and its novel application to the RE implementation of a VD. Chapter 5 describes the fabricated chip which implements an ACS module, and Chapter 6 presents the ultra low

power VD architecture, the MLVD. Finally, the conclusions and recommendations for future work are outlined in Chapter 7.

#### Chapter 2

### Low Power Digital VLSI Design

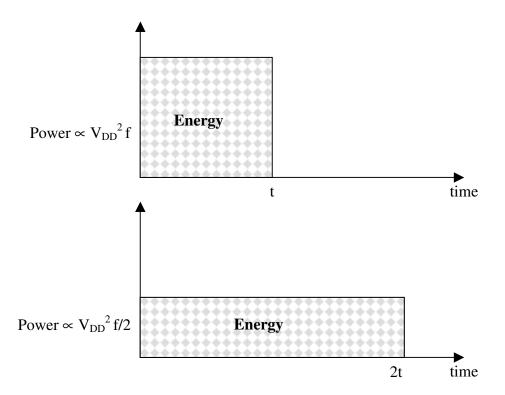

### 2.1 Energy Consumption versus Power Consumption

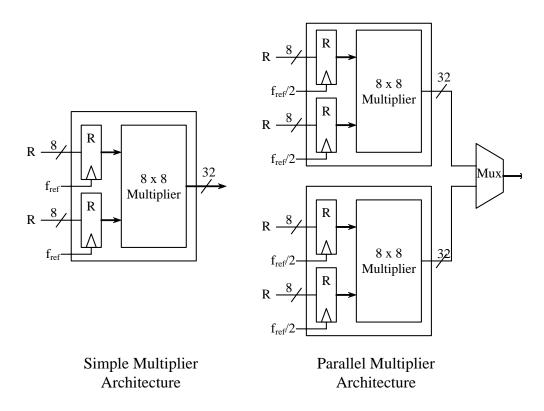

Energy consumption is different from power consumption. If for example, for a CMOS gate we reduce its clock rate f, its power consumption will be reduced by the same proportion. However, its energy consumption will still be the same as shown in Figure 2.1 [1]. Only, the time required to complete the computation with low clock rate, will be increased. Therefore, after the computation is completed the battery will be just as dead as if the computation had been performed at high clock rate. Thus, for battery-operated devices low energy design is more important than low power design. However, the conventional term low power is used throughout the thesis to mean that low energy is the target [2].

#### 2.2 Sources of Power Dissipation

In the 1980s, an increase in the power dissipation of Application Specific Integrated Circuits (ASICs) caused a worldwide shift from NPN bipolar and NMOS technologies to CMOS technology. CMOS significantly reduces the average power dissipation, but it is the demand for higher packing densities and higher operating frequencies in microelectronics that keeps low power design as the primary requirement. In order to minimize the power dissipation of a CMOS circuit, the main sources for the power dissipation of CMOS devices must be identified. There are three major power dissipation components within the CMOS inverter switching power, leakage power, and short circuit power [3].

Figure 2.1: Energy consumption versus power consumption

#### 2.2.1 Switching Power

The most dominant source of power dissipation in digital circuits is dynamic power dissipation. It describes the power required to charge and discharge the load capacitance,  $C_L$ , at the switching activity  $\alpha$ , and is expressed as.

$$P_{dync} = \alpha C_L V_{DD} V_{swing} f. \tag{2.1}$$

Equation (2.1) shows that the dynamic power is decreased, by reducing the supply voltage, but this also reduces the speed.  $P_{dyn}$  is reduced also, by reducing  $C_L$ , but it is noted that scaling down the circuit does not necessarily reduce the capacitance by the same ratio. This occurs because the wiring capacitance does not scale well with submicron technologies. Thus, this source of power dissipation is usually reduced at the algorithmic, architectural, and Register-Transfer-Level (RTL) levels. A very important part of dynamic power is the glitching power, which is discussed as follows.

#### Glitching Power

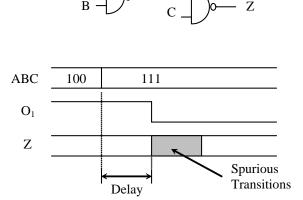

In a static logic gate, the output or internal nodes can switch before the correct logical value is reached. Figure 2.2 depicts the logic transitions for a cascaded configuration. When the input is switched from 100 to 111, the output should remain high, but due to the delay associated with each gate, a glitch is added to the total switching of the circuit. The glitch is sometimes called a spurious transition.

Figure 2.2: Glitching in static CMOS gates

If the power dissipation that is due to spurious transitions is important, then the logic of the circuit should be redesigned to avoid the cascaded implementation and to balance the delay paths, particularly on highly loaded nodes.

#### 2.2.2 Short Circuit Power

Short circuit power is due to finite rise and fall times of the input signal. For a short period of time, there will be a conducive path open between  $V_{DD}$  and GND, because both NMOS and PMOS devices are ON. Such a path never exists in dynamic circuits, as precharge and evaluate transistors should never be ON simultaneously as this would lead to incorrect evaluation [4]. Short circuit power can be expressed as:

$$P_{sc} = I_{sc}V_{DD}, (2.2)$$

where  $I_{sc}$  is the short circuit current. This power is limited by giving the output signal and the input signal equal rise and fall times. As a result, the  $P_{sc}$  is less than

20 percent of the total power. For submicron devices, where the  $V_{DD}$  approaches  $(V_{Tn} + V_{Tp})$  or is less, the  $P_{sc}$  can be eliminated, because both devices cannot conduct simultaneously [2].

#### 2.2.3 Leakage Power

The leakage power can be expressed as:

$$P_{leakage} = I_{leakage} V_{DD}, (2.3)$$

where  $I_{leakage}$  is the total leakage current in a CMOS circuit [3].  $I_{leakage}$  is caused by six short channel leakage mechanisms [5] the reverse bias pn junction leakage, subthreshold leakage, oxide tunneling current, gate current due to hot carrier injection, gate induced drain leakage, and the channel punchthrough current. For deep submicron devices with low supply voltages and low threshold voltages, the subthreshold leakage is the dominant leakage mechanism. As CMOS process advances to the sub-100nm regime, the gate oxide thickness of sub-20 $\mathring{A}$  prevails in CMOS processes [3]. Gate leakage may become the dominant factor for sub-100nm generations unless new solutions emerge [6].

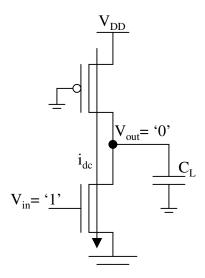

#### 2.2.4 Static Power

Some CMOS circuit families such as the pseudo NMOS dissipate static power when the output is at logic 0 as illustrated in Figure 2.3 for a pseudo-NMOS inverter.

#### 2.3 Low Power Design Techniques

Power dissipation is minimized at all design levels. At the circuit level, for example, the power is minimized by aggressively scaling down the supply voltage. It is also essential to minimize the switching activity. This can be accomplished at the logic, RTL, architectural, or algorithmic levels. The following is a brief discussion of some low power methodologies that are applied at various levels, including the system, algorithm, architecture, logic, circuit, and physical levels [2] [4].

#### 2.3.1 System Level Optimization

Usually, low power design at the system level is realized by utilizing lower system clocks, in addition to using a high level integration. The high level integration

Figure 2.3: DC current in a Pseudo-NMOS inverter

includes the integration of off-chip memories and digital and analog peripherals. Other ways to reduce power at system level include using dynamic  $V_{DD}$  control according to system workload [3].

#### 2.3.2 Algorithm Level Optimization

Secondly, at the algorithm level, the main concern is to minimize the number of operations, and thus, the number of hardware resources, or to minimize the switching activity by data coding.

#### Minimizing the Number of Operations

Minimizing the number of operations is crucial in minimizing power dissipation. However, different types of operations do not consume the same amount of power. The number of operations at the algorithm level can be decreased by data coding. The use of an appropriate coding technique for the signals, rather than a direct binary code, can reduce power by reducing the temporal bit transition activity. The following sections provide some examples of different data representations which are used to reduce power dissipation [4].

One Hot Coding: In regards to an inter-chip communication problem, where n-bit data words will be transmitted, a connection of  $m = 2^n$  wires can be used. The n-bit data word is encoded for transmission by placing a 1 on the ith wire and 0 on the remaining m-1 wires. One hot encoding requires an exponentially increasing number of wires  $(2^n)$ , but the coding does guarantee that precisely one  $0 \rightarrow 1$  and one  $1 \rightarrow 0$  bit transition occur when a different data word is sent.