# Energy-Efficient Turbo Decoder for 3G Wireless Terminals

by

Ibrahim A. Al-Mohandes

A thesis

presented to the University of Waterloo

in fulfillment of the

thesis requirement for the degree of

Doctor of Philosophy

in

Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2005

© Ibrahim A. Al-Mohandes 2005

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### Abstract

Since its introduction in 1993, the turbo coding error-correction technique has generated a tremendous interest due to its near Shannon-limit performance. Two key innovations of turbo codes are parallel concatenated encoding and iterative decoding. In its IMT-2000 initiative, the International Telecommunication Union (ITU) adopted turbo coding as a channel coding standard for Third-Generation (3G) wireless high-speed (up to 2 Mbps) data services (cdma2000 in North America and W-CDMA in Japan and Europe).

For battery-powered hand-held wireless terminals, energy consumption is a major concern. In this thesis, a new design for an energy-efficient turbo decoder that is suitable for 3G wireless high-speed data terminals is proposed. The Log-MAP decoding algorithm is selected for implementation of the constituent Soft-Input/Soft-Output (SISO) decoder; the algorithm is approximated by a fixed-point representation that achieves the best performance/complexity tradeoff. To attain energy reduction, a two-stage design approach is adopted.

First, a novel dynamic-iterative technique that is appropriate for both good and poor channel conditions is proposed, and then applied to reduce energy consumption of the turbo decoder. Second, a combination of architectural-level techniques is applied to obtain further energy reduction; these techniques also enhance throughput of the turbo decoder and are area-efficient. The turbo decoder design is coded in the VHDL hardware description language, and then synthesized and mapped to a  $0.18\mu m$  CMOS technology using the standard-cell approach. The designed turbo decoder has a maximum data rate of 5 Mb/s (at an upper limit of five iterations) and is 3G-compatible. Results show that the adopted two-stage design approach reduces energy consumption of the turbo decoder by about 65%.

A prototype for the new turbo codec (encoder/decoder) system is implemented on a Xilinx XC2V6000 FPGA chip; then the FPGA is tested using the CMC Rapid Prototyping Platform (RPP). The test proves correct functionality of the turbo codec implementation, and hence feasibility of the proposed turbo decoder design.

#### Acknowledgements

I would like to first thank my thesis supervisor, Prof. Mohamed Elmasry. It was through his patience and invaluable guidance that this work was accomplished. I would also like to express my appreciation for Prof. Amir Khandani, Prof. Catherine Gebotys, Prof. Manoj Sachdev, and Prof. Mohamed Sawan for serving as my committee members and commenting on this work.

I would like to acknowledge the support of our VLSI lab system administrator, Phil Regier, especially his fast response to technical problems. I would also like to thank my colleagues in the VLSI lab for their help and advise. Special thanks go to Jonathan Lutz, now with Motorola Co.

Finally, I send my sincere thanks and great appreciation to my parents and my wife for their love and support during this work.

# Contents

| 1 | $\mathbf{Intr}$ | roducti | ion                                                      | 1  |

|---|-----------------|---------|----------------------------------------------------------|----|

|   | 1.1             | Thesis  | Contributions                                            | 2  |

|   | 1.2             | Organ   | ization                                                  | 3  |

| 2 | Tur             | bo Co   | des                                                      | 4  |

|   | 2.1             | Digita  | l Communication Systems                                  | 4  |

|   |                 | 2.1.1   | Channel Fundamental Limits                               | 7  |

|   | 2.2             | Chann   | nel Coding Techniques                                    | 8  |

|   |                 | 2.2.1   | Linear Block Codes                                       | 8  |

|   |                 | 2.2.2   | Convolutional Codes                                      | Ć  |

|   | 2.3             | Turbo   | Codes                                                    | 10 |

|   |                 | 2.3.1   | Turbo Encoder                                            | 11 |

|   |                 | 2.3.2   | Interleaver                                              | 12 |

|   |                 | 2.3.3   | Iterative Decoding of Turbo Codes                        | 13 |

|   | 2.4             | Standa  | ardized Turbo Codes for 3G Wireless Systems              | 15 |

| 3 | VLS             | SI Desi | ign of Turbo Decoders                                    | 19 |

|   | 3.1             | Algori  | thmic-Level Design                                       | 19 |

|   |                 | 3.1.1   | MAP Decoding Algorithm                                   | 19 |

|   |                 | 3.1.2   | Max-Log-MAP Decoding Algorithm                           | 21 |

|   |                 | 3.1.3   | Log-MAP Decoding Algorithm                               | 23 |

|   |                 | 3.1.4   | SOVA Decoding Algorithm                                  |    |

|   |                 | 3.1.5   | Comparison of MAP and SOVA Iterative Decoding Algorithms | 26 |

|   | 3.2 | Explor | ration of System Design Space for Turbo Codecs             | 31 |

|---|-----|--------|------------------------------------------------------------|----|

|   |     | 3.2.1  | Turbo Decoder Optimization                                 | 32 |

|   | 3.3 | Archit | ectures and Design Techniques for Turbo Decoders           | 37 |

|   | 3.4 | Dynan  | nic-Iterative Techniques for Turbo Decoders                | 40 |

|   | 3.5 | Source | es of Power and Energy Consumption                         | 43 |

| 4 | AN  | lew Dy | ynamic-Iterative Technique for Turbo Decoders              | 45 |

|   | 4.1 | Quant  | ization of the Log-MAP Turbo Decoder                       | 45 |

|   |     | 4.1.1  | Decoding Performance of the Fixed-Point Approximation      | 46 |

|   | 4.2 | Energy | y Reduction with Dynamic-Iterative Techniques              | 46 |

|   |     | 4.2.1  | CRC Stopping Method                                        | 50 |

|   |     | 4.2.2  | HDA Stopping Method                                        | 51 |

|   | 4.3 | A New  | Dynamic-Iterative Technique: CRC-HDD                       | 51 |

|   |     | 4.3.1  | Iteration Stopping Using the CRC Method                    | 52 |

|   |     | 4.3.2  | Introducing a Novel Cancellation Method: HDD               | 52 |

|   |     | 4.3.3  | The New CRC-HDD Dynamic-Iterative Algorithm                | 55 |

|   |     | 4.3.4  | Comparing Decoding Performance for CRC, HDA, and CRC-HDD . | 57 |

|   |     | 4.3.5  | Comparing Iteration Reduction for CRC, HDA, and CRC-HDD $$ | 57 |

|   | 4.4 | Hardw  | vare Complexity of the CRC-HDD Logic                       | 60 |

|   |     | 4.4.1  | Complexity Reduction of the HDD Section                    | 61 |

| 5 | An  | Energy | y-Efficient Design of Turbo Decoder                        | 63 |

|   | 5.1 | Archit | ectural-Level Techniques Applied to the Turbo Decoder      | 63 |

|   |     | 5.1.1  | Algorithm Selection and Quantization                       | 63 |

|   |     | 5.1.2  | Parallelism                                                | 64 |

|   |     | 5.1.3  | A New Operator Reduction Method for the max* Logic         | 64 |

|   |     | 5.1.4  | Normalization of State Metrics                             | 66 |

|   |     | 5.1.5  | Resource Sharing                                           | 69 |

|   |     | 5.1.6  | Interleaver Design                                         | 70 |

|   |     | 5.1.7  | Double Buffering                                           | 70 |

|   | 5.2 | Turbo  | Decoder Design Hierarchy                                   | 71 |

| 6 | Synthesis Results                                  |                                                                               |    |

|---|----------------------------------------------------|-------------------------------------------------------------------------------|----|

|   | 6.1                                                | 1 Synthesis Results for a 0.18 $\mu m$ CMOS Standard-Cell Based Turbo Decoder |    |

|   |                                                    | 6.1.1 Applying the Architectural-Level Techniques to the Turbo Decoder        | 82 |

|   |                                                    | 6.1.2 Energy Reduction with the CRC-HDD Dynamic-Iterative Technique           | 84 |

|   |                                                    | 6.1.3 Effect of Memory Integration on the Turbo Decoder                       | 86 |

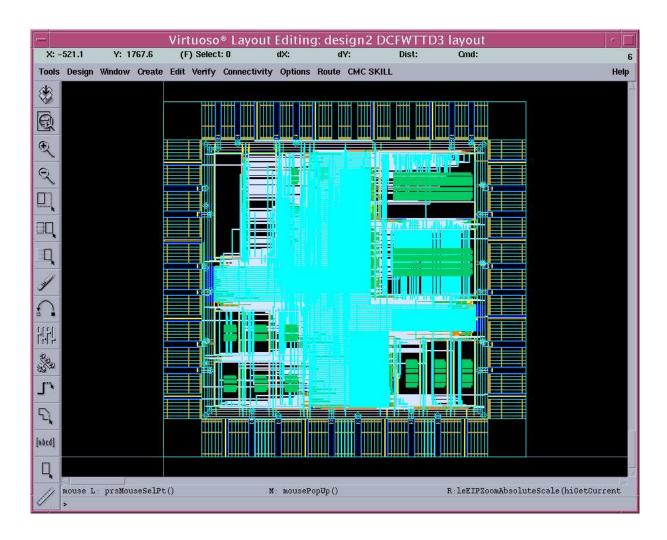

|   | 6.2                                                | CMOS Layout of the Turbo Decoder Including Memory Blocks                      | 88 |

|   | 6.3                                                | Comparison with State-of-the-Art Turbo Decoders                               | 89 |

| 7 | FPGA Design and Testing of a Turbo Codec Prototype |                                                                               |    |

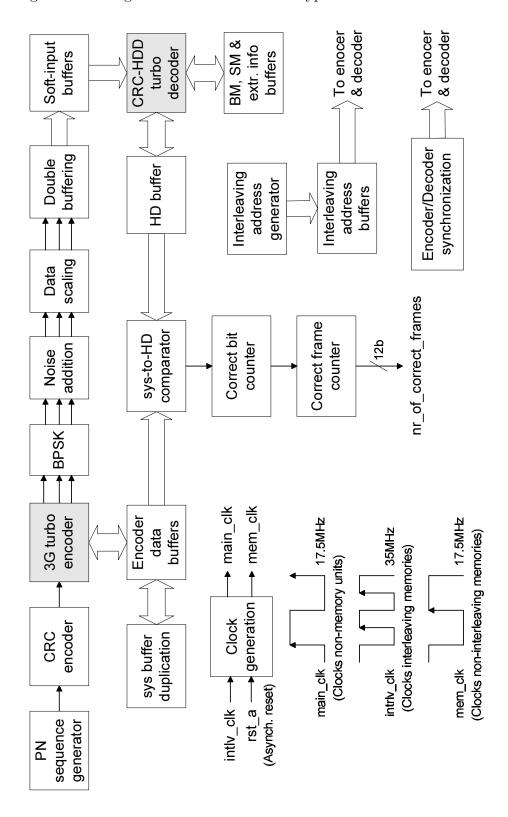

|   | 7.1                                                | The Turbo Codec Design                                                        | 93 |

|   | 7.2                                                | FPGA Testing with the CMC RPP Environment                                     | 94 |

| 8 | Cor                                                | nclusion                                                                      | 98 |

# List of Tables

| 2.1                             | Puncturing patterns for the turbo code of Figure 2.6                                                                                                                                                   | 17                         |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 4.1<br>4.2                      | Reduction in iteration number by CRC, HDA, and CRC-HDD techniques . Typical vs. low-complexity HDD circuit implementations                                                                             | 60<br>62                   |

| 5.1<br>5.2                      | Results for classical and new implementations of the max* logic Implementation results for the two SM normalization methods                                                                            | 67<br>69                   |

| 6.1<br>6.2<br>6.3<br>6.4<br>6.5 | Turbo decoder characteristics at different stages of the design process  Turbo decoder characteristics before and after applying CRC-HDD technique Memory characteristics for the turbo decoder design | 84<br>85<br>86<br>87<br>91 |

| 7.1                             | Key characteristics of the turbo codec FPGA                                                                                                                                                            | 97                         |

# List of Figures

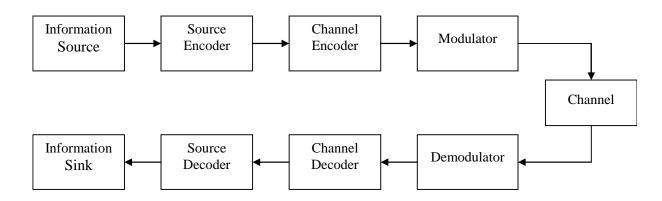

| 2.1 | The general model of a digital communication system                         | 5  |

|-----|-----------------------------------------------------------------------------|----|

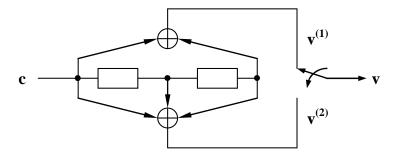

| 2.2 | A rate 1/2 convolutional encoder                                            | 9  |

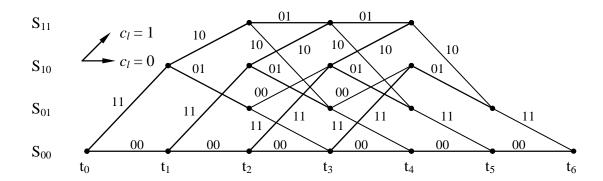

| 2.3 | Trellis diagram for the $1/2$ non-systematic encoder in Figure 2.2          | 11 |

| 2.4 | General diagram of a rate 1/3 turbo encoder                                 | 12 |

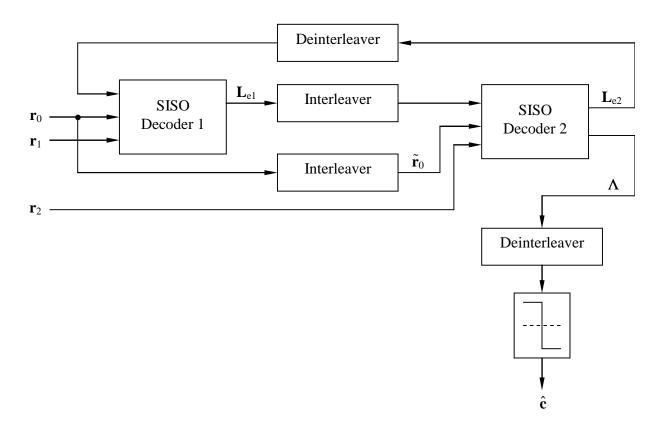

| 2.5 | General diagram of an iterative turbo decoder                               | 14 |

| 2.6 | Standardized turbo code for 3G wireless systems                             | 16 |

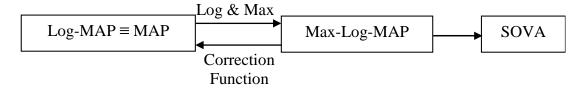

| 3.1 | Relationship between MAP, Log-MAP, Max-Log-MAP, and SOVA                    | 26 |

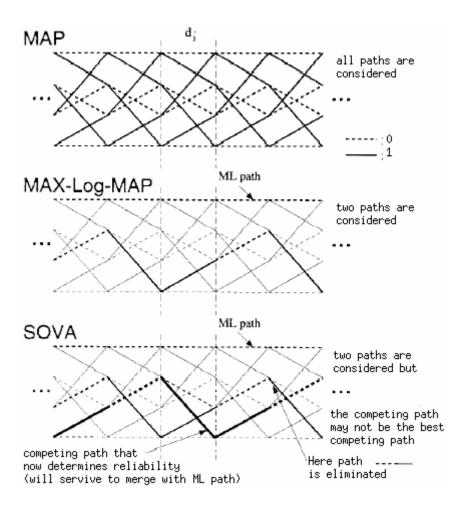

| 3.2 | Comparing (Log-)MAP, Max-Log-MAP, and SOVA                                  | 28 |

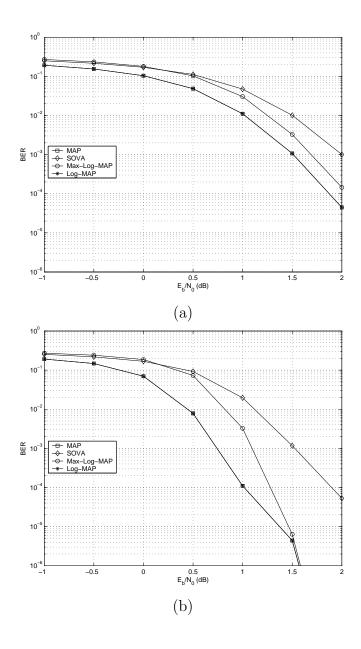

| 3.3 | BER vs. $E_b/N_0$ for MAP, SOVA, Max-Log-MAP, and Log-MAP decoders .        | 29 |

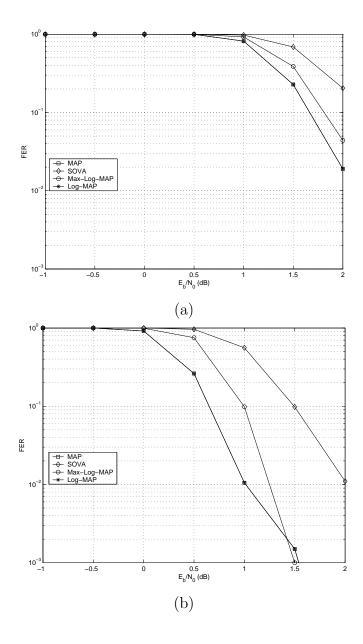

| 3.4 | FER vs. $E_b/N_0$ for MAP, SOVA, Max-Log-MAP, and Log-MAP decoders .        | 30 |

| 3.5 | System design space for turbo codecs                                        | 32 |

| 4.1 | BER vs. $E_b/N_0$ for floating-point and fixed-point Log-MAP turbo decoders | 47 |

| 4.2 | FER vs. $E_b/N_0$ for floating-point and fixed-point Log-MAP turbo decoders | 48 |

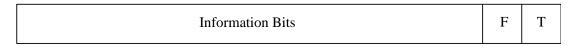

| 4.3 | Frame structure used in 3G wireless CDMA standards                          | 50 |

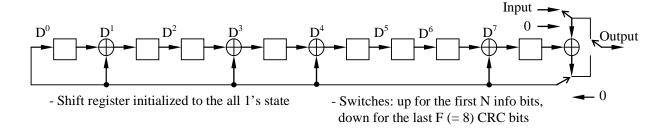

| 4.4 | The 8-bit CRC-encoder for cdma2000 and W-CDMA standards $\ \ldots \ \ldots$ | 51 |

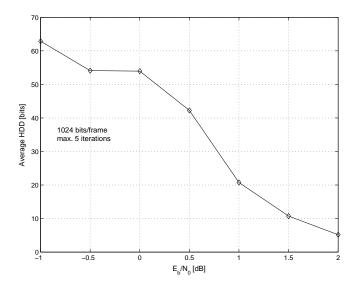

| 4.5 | Average HDD vs. $E_b/N_0$ (1024 bits/frame, max. 5 iterations)              | 54 |

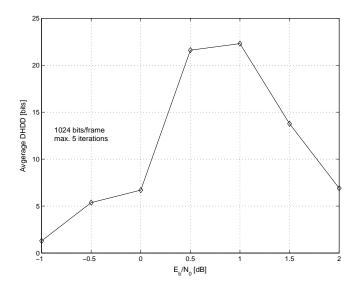

| 4.6 | Average DHDD vs. $E_b/N_0$ (1024 bits/frame, max. 5 iterations)             | 54 |

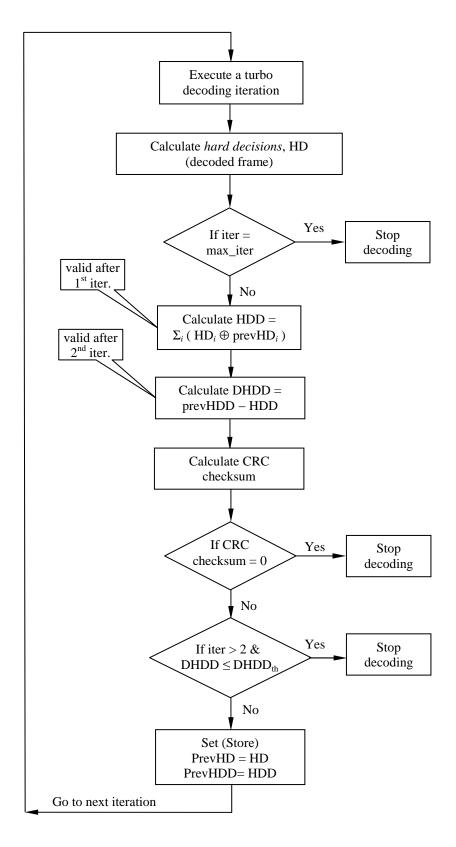

| 4.7 | The CRC-HDD algorithm                                                       | 56 |

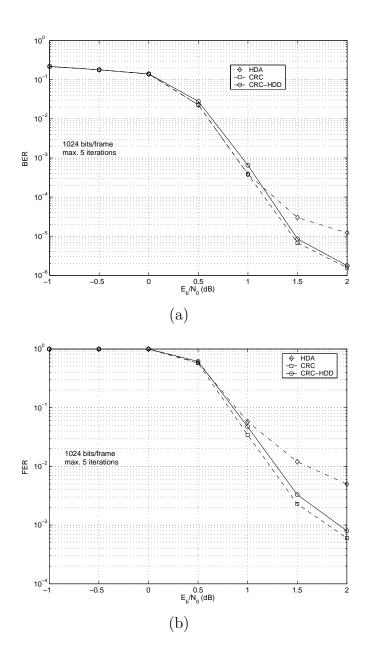

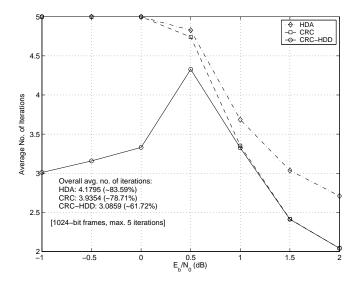

| 4.8 | BER and FER vs. $E_b/N_0$ for CRC, HDA, and CRC-HDD decoders                | 58 |

| 4.9 | Average iteration no. vs. $E_b/N_0$ for CRC, HDA, and CRC-HDD decoders .    | 59 |

| 5 1 | Parallel processing of two half-frames                                      | 65 |

| 5.2  | The max* operation                                                                | 66 |

|------|-----------------------------------------------------------------------------------|----|

| 5.3  | The parallel max state-metric normalization logic                                 | 68 |

| 5.4  | The subtraction-based state-metric normalization algorithm                        | 68 |

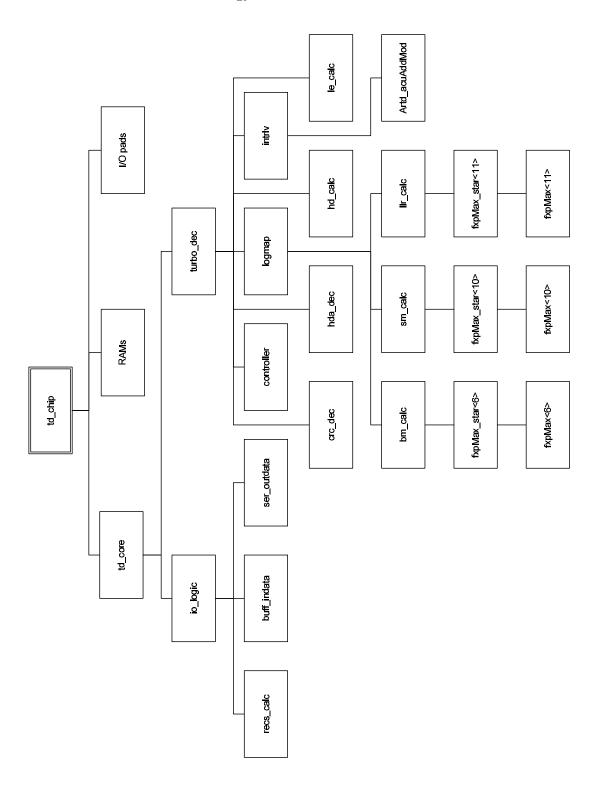

| 5.5  | Design hierarchy of the VHDL-based turbo decoder                                  | 72 |

| 5.6  | Block diagram of the new turbo decoder $(td\_chip)$                               | 73 |

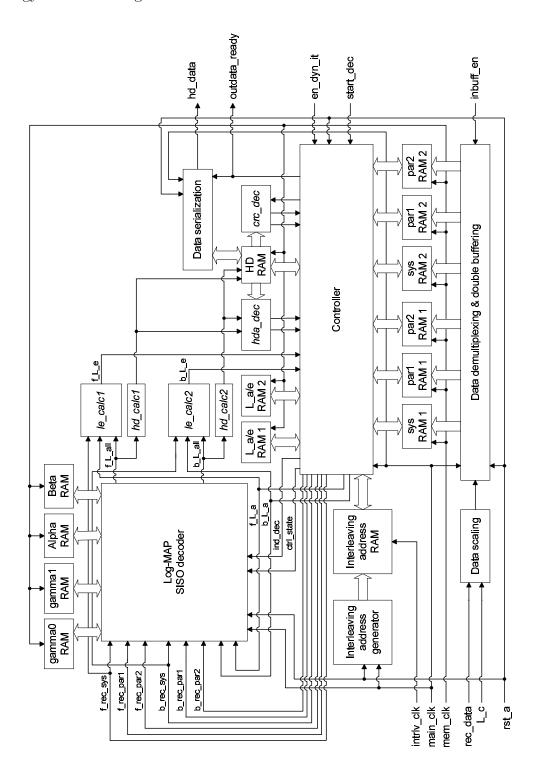

| 5.7  | Block diagram of the Log-MAP SISO decoder $(logmap)$                              | 75 |

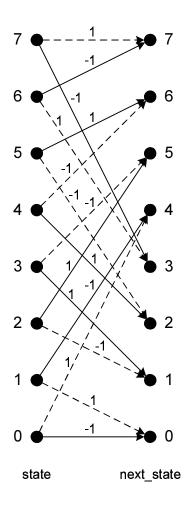

| 5.8  | RSC encoder state transitions and corresponding parity symbols                    | 76 |

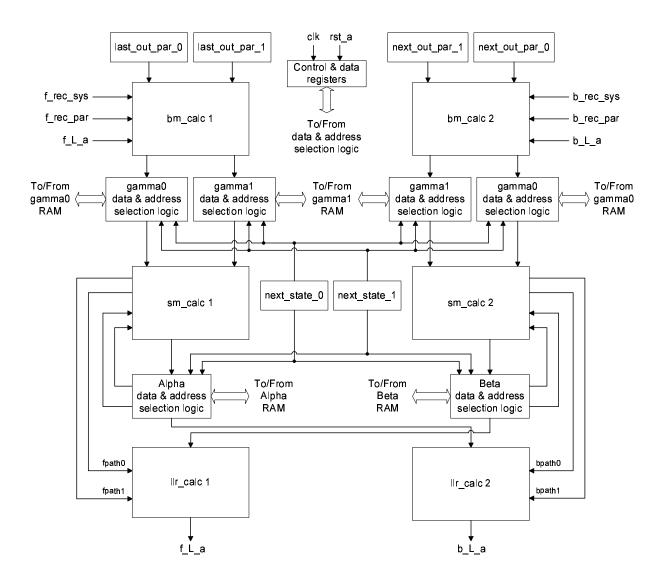

| 5.9  | Block diagram of the branch metrics calculation $(bm\_calc)$ unit                 | 77 |

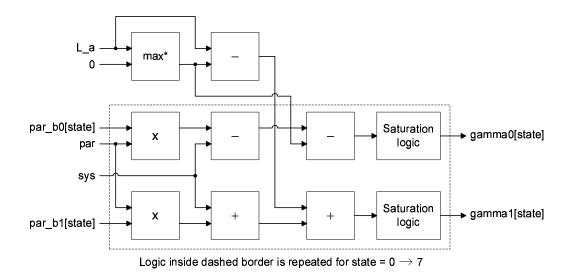

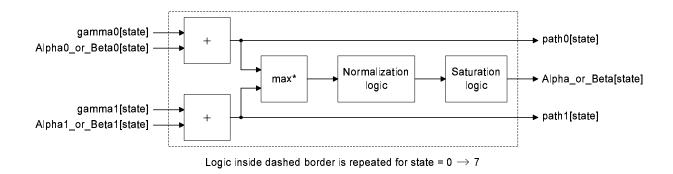

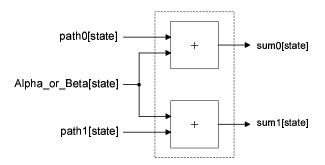

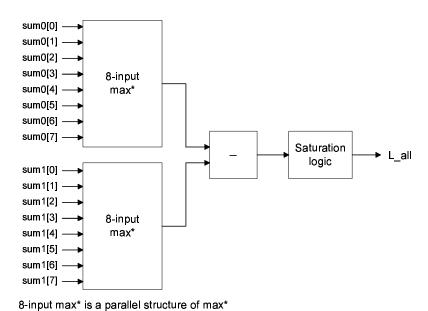

| 5.10 | Block diagram of the state metrics calculation $(sm\_calc)$ unit                  | 77 |

| 5.11 | Block diagram of the LLR calculation $(llr_{-}calc)$ unit                         | 78 |

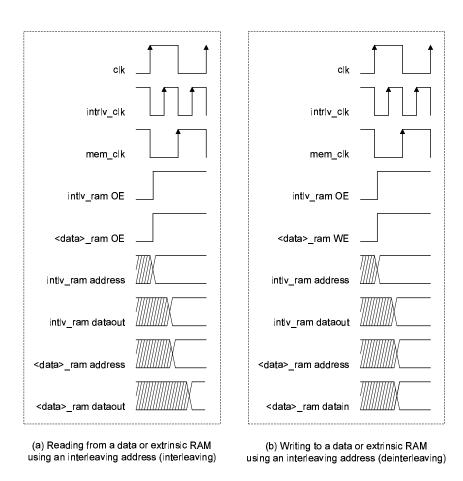

| 5.12 | Timing diagram for data interleaving/deinterleaving by the <i>controller</i> unit | 81 |

| 6.1  | Floorplan report for the turbo decoder chip                                       | 89 |

| 6.2  | CMOS layout of the 128-bit turbo decoder                                          | 90 |

| 7.1  | Block diagram of the turbo codec system                                           | 95 |

| 7.2  | CMC Rapid Prototyping Platform                                                    | 96 |

# List of Acronyms

3G Third-Generation

ACS Add-Compare-Select

APP A Posteriori Probability

ARQ Automatic Repeat Request

AWGN Additive White Gaussian Noise

BER Bit Error Rate

BM Branch Metric

BPSK Binary Phase Shift Keying BSC Binary Symmetric Channel

CDMA Code Division Multiple Access

cdma2000 3G CDMA standard (for year 2000) in North America

CRC Cyclic Redundancy Check

DHDD Decrease in Hard Decision bit-wise Difference

FEC Forward Error Correction

FER Frame Error Rate

HD Hard Decision

HDA Hard Decision Aided

HDD Hard Decision bit-wise DifferenceHSDPA High Speed Downlink Packet Access

IMT-2000 International Mobile Telecommunications for year 2000

ITU International Telecommunication Union

LLR Log-Likelihood Ratio

MAP Maximum A Posteriori

ML Maximum Likelihood

RPP Rapid Prototyping Platform

RSC Recursive Systematic Convolutional

RTL Register-Transfer-Level SCR Sign-Change Ratio

SISO Soft-Input/Soft-Output

SM State Metric

SNR Signal-to-Noise Ratio

SOVA Soft-Output Viterbi Algorithm

W-CDMA 3G (Wideband) CDMA standard in Europe and Japan

# List of Symbols

- L A priori, or extrinsic, information

- $L_a$  A priori information

- $\beta$  Backward state metric

- $E_b$  Bit energy

- $\gamma_i$  Branch metric for bit  $i \in \{0, 1\}$

- B Channel bandwidth

- C Channel capacity

- $L_c$  Channel reliability factor

- $\eta$  Channel spectral efficiency

- R Code rate

- $f_c$  Correction function for Jacobian logarithm

- $L_e$  Extrinsic information

- $\alpha$  Forward state metric

- N Frame (or block) length

- ${f g}$  Generator polynomial for convolutional code

- $\hat{\mathbf{x}}$  Hard decision for original  $\mathbf{x}$

- $\tilde{\mathbf{x}}$  **x** interleaved

- $\Lambda$  Log-likelihood ratio (or probability)

- $N_0$  One-sided noise power spectral density

- $E_s$  Symbol energy

# Chapter 1

### Introduction

For many digital communication services, bandwidth and transmission power are limited resources, and it is well known that the use of Forward Error-Correction (FEC) codes plays a fundamental role in increasing power and spectrum efficiency. However, Shannon demonstrated in [1] that the development of error-correction techniques with increasing coding gain has a limit arising from the channel capacity.

Since then, FEC code designers have been looking for new codes that approach as close as possible the Shannon limit. However, each increased coding gain comes at the expense of decoder complexity, and its practical feasibility must be evaluated for the available technologies [2].

A new class of binary parallel concatenated Recursive Systematic Convolutional (RSC) codes, called *turbo codes* [3], are capable of achieving power efficiency close to the Shannon limit. Turbo codes have been adopted by the International Telecommunication Union (ITU) to effectively improve system capacity for Third-Generation (3G) wireless high-speed data services (cdma2000 and W-CDMA).

The goal of the ITU is to achieve a harmonized 3G wireless standard that would allow users to roam anywhere in the world without resorting to multimedia terminals. Despite being a small part of the overall system, turbo code specifications in the cdma2000 and W-CDMA systems are designed to have as much commonality as possible toward achieving this goal [4].

Now, communication system designers have a large spectrum of turbo-code decoders

at their disposal. However, performance and power are usually contradicting metrics; the decoder with an excellent decoding performance also has a very complex hardware architecture that results in a large amount of power consumption [5].

By applying high-performance power-reduction techniques in the design of the turbo decoder, energy consumption of the mobile terminal can be reduced in two ways. The first one is directly achieved by reducing energy consumption of the turbo decoder, thereby reducing energy consumption of the entire mobile terminal. The second way is indirectly derived from the fact that a high performance decoder can decode codes transmitted with low signal-to-noise ratios (SNR); this allows for the reduction of power emitted by the transceiver which results in a further energy reduction of the entire mobile terminal. Moreover, the reduction in energy consumption permits the reduction in mobile terminal size due to three factors. The first one is the use of small-size batteries, which is now possible because of the reduction in energy consumption. The other two factors include the reduction in both of the turbo decoder silicon area (due to lower complexity) and the antenna size (due to lower transmission power). In addition to decoding performance, energy, and area/size factors, throughput and latency are also considered when applying power-reduction techniques. When the optimizations of these factors are contradictory, the best possible tradeoff has to be chosen.

#### 1.1 Thesis Contributions

In this thesis, a new energy-efficient design of a 3G-compliant turbo decoder is proposed. A two-stage design approach is adopted:

- 1. A novel low-complexity dynamic-iterative technique that reduces energy of the turbo decoder at both good and poor channel conditions is proposed.

- 2. A combination of architectural-level techniques is applied for further energy reduction; the techniques also enhance throughput of the turbo decoder and are areaefficient. One of the applied techniques is a novel operator reduction method that reduces power, area, and critical-path delay of the turbo decoder.

Introduction 3

The new energy-efficient turbo decoder is coded in VHDL, and then synthesized into  $0.18\mu m$  CMOS, achieving a maximum data rate of 5 Mb/s (with an upper limit of 5 iterations). Results show an energy consumption reduction of about 65% (compared to a basic implementation), with an energy efficiency of about 4.5 nJ/b/iteration.

To prove feasibility of the proposed turbo decoder design, a prototype is implemented for the turbo codec (encoder/decoder) on a Xilinx XC2V6000 FPGA. The Xilinx FPGA is tested using the CMC Rapid Prototyping Platform (RPP) and found to be functionally correct.

#### 1.2 Organization

The thesis is organized into eight chapters. Chapter 2 provides an introduction to turbo codes as an efficient error-control coding for transmission over noisy channels. The role of turbo codes in 3G wireless systems is also presented. In Chapter 3, turbo decoder algorithms and design techniques are discussed, with an emphasis on iteration reduction and energy consumption. In Chapter 4, a novel dynamic-iterative technique (CRC-HDD) is introduced. A fixed-point approximation of the Log-MAP algorithm is also presented. Chapter 5 discusses architectural-level techniques suggested for improving area, throughput, and energy efficiency of the turbo decoder. In Chapter 6, key results from a  $0.18\mu m$  CMOS implementation of the turbo decoder are detailed. In Chapter 7, the design and testing of an FPGA prototype for the new turbo codec are presented. Chapter 8 summarizes the results and concludes the thesis, along with suggestions for future work.

# Chapter 2

### Turbo Codes

Turbo coding is used as a FEC technique for transmission over noisy channels. Turbo codes have been used over the last decade in different wireless communication systems such as Code Division Multiple Access (CDMA), deep space, and satellite communication systems. In the IMT-2000 standard, turbo coding has been chosen by the ITU as a channel coding technique for 3G wireless high-speed (up to 2 Mbps) data services.

This chapter serves as a background for turbo coding as a channel coding technique. Also, the standardized turbo codes for 3G wireless communication systems are described.

#### 2.1 Digital Communication Systems

To understand the role of turbo coding as an error-control technique, the general model of a digital communication system is shown in Figure 2.1. This system consists of three major parts: *transmitter*, *channel*, and *receiver*. Each of the transmitter and the receiver has its own components.

The task of the transmitter is to transform the information generated by a source into a form that can withstand the effects of noise over the communication channel. An information source generates message-bearing information (such as words and code symbols) to be transmitted. The source encoder converts the information source output to a sequence of binary digits with minimum redundancy. If the source encoder generates  $r_b$  bits per second (bps),  $r_b$  is called the data rate.

Figure 2.1: The general model of a digital communication system

Since channel impairments cause errors in the received signal, the *channel encoder* is incorporated to add redundancy to the information sequence. This redundancy is used to minimize transmission errors. The channel encoder assigns to each message of k bits a longer message of n bits called a *codeword*. A good error-control code generates codewords which are as different as possible from each other. This makes the communication system less vulnerable to channel errors. Each code word is characterized by a ratio R = k/n < 1, called the *code rate*. The data rate at the output of the channel encoder is  $r_c = r_b/R$  bps. The primary goal of error-control coding is to maximize the reliability of transmission within the constraints of signal power, system bandwidth, and circuit complexity. It is achieved by introducing structured redundancy into transmitted signals. This usually results in a lowered data transmission rate, or an increased channel bandwidth, relative to an uncoded system [6].

The channel encoder output is not normally suitable for transmission. Therefore, the modulator is incorporated to match the signal to the channel, to enable simultaneous transmission of a number of signals over the same physical channel, and to increase the speed of information transmission. The modulator maps the encoded digital sequences into a train of short analog waveforms that are appropriate for propagation. An M-ary modulator maps a block of l binary digits from the channel encoder into one of M possible waveforms, where  $M=2^l$ . The duration of the modulator output waveform is T sec and is referred to as the signaling interval, whereas  $r_s=1/T$  is called the symbol rate.

The minimum signal bandwidth is equal to  $r_s$  Hz, where  $r_s = r_b/Rl$ . Modulation can be performed by varying amplitude, phase, and/or frequency of a sinusoidal waveform called the *carrier*.

Channels are transmission media used to carry or store information. Channel examples include wire lines, microwave radio links over free space, satellite links, fibre optic channels, and magnetic recording media. Very often the term channel is used to refer to the frequency range allocated to a particular service such as television or phone channels. Two major limitations of real channels are thermal noise and finite bandwidth. In addition, mobile radio channels suffer from multipath propagation, fibre optic cables suffer from signal dispersion, and magnetic media are exposed to duct and physical damage.

In the receiver, the demodulator typically generates a binary or analog sequence at its output as the best estimates of the transmitted codeword or the modulated sequence respectively. The channel decoder makes estimates of the actually transmitted message. The decoding process is based on the encoding rule and the characteristic of the channel. The goal of the decoder is to minimize the effects of channel noise. The source decoder transforms the bit sequence generated by the decoder into an estimate of the source output sequence and delivers it to the user (information sink).

If the demodulator generates a binary sequence, subsequent channel decoding is called hard decision decoding. In this case, the three blocks of modulator, channel, and demodulator can be simplified by a discrete channel. The input and output of the discrete channel are binary sequences at  $r_c$  bits per sec. If the demodulator output in a given symbol interval depends on the current transmitted signal and not any previous transmission, the channel is said to be memoryless. If this memoryless channel has equal error probabilities for the binary symbols 0 and 1, it is called a Binary Symmetric Channel (BSC).

If the demodulator output is quantized into more than two discrete levels or samples are taken from the analog received baseband signal, the subsequent decoding process is called *soft decision decoding*. Hard decisions result in a more irreversible information loss than soft decisions.

If bandwidth efficiency is essential, combining coding and modulation into a single entity obtains a more effective signal design. This results in increased noise immunity of the signal without increasing the channel bandwidth. The combined coding and modulation is called

trellis coded modulation [6].

#### 2.1.1 Channel Fundamental Limits

For a given channel there is an upper limit on the data rate related to the Signal-to-Noise Ratio (SNR) and the system bandwidth. Shannon has introduced the concept of *channel capacity*, C, as the maximum rate at which information can be transmitted over a noisy channel [1]. For an Additive White Gaussian Noise (AWGN) channel, channel capacity is given by the following formula:

$$C = B \log_2(1 + \frac{S}{N})$$

bits/sec (2.1)

where B is the channel bandwidth in Hz, and S/N is the average SNR, defined as

$$\frac{S}{N} = \eta \frac{E_b}{N_0} \tag{2.2}$$

where  $E_b/N_0$  is the bit energy to one sided noise power spectral density, and  $\eta$  is the spectral efficiency, defined as

$$\eta = \frac{r_b}{B} \quad \text{bits/sec/Hz}$$

(2.3)

Another important parameter is the power efficiency defined as the required  $E_b/N_0$  to achieve a specified bit error probability.

Shannon's channel coding theorem guarantees the existence of codes that can achieve an arbitrary small probability of error if the data transmission rate  $r_b$  is smaller than the channel capacity. Conversely, for a data rate  $r_b > C$ , it is not possible to design a code that can achieve an arbitrary small error probability.

This fundamental result shows that noise sets a limit on the data rate but not on the error probability, as widely believed before. Although the theorem does not indicate how to design specific codes that achieve maximum possible data rate at an arbitrary small error probability, it has motivated the development of a number of error-control techniques [6].

By substituting S/N from (2.2) into (2.1) and observing that  $\eta_{\text{max}} = C/B$ , the minimum required  $E_b/N_0$  for an error-free transmission is given by

$$\frac{E_b}{N_0} \ge \frac{2^{\eta} - 1}{\eta} \tag{2.4}$$

If the bandwidth is not limited (i.e.,  $B \to \infty$  or  $\eta_{\text{max}} \to 0$ ), then

$$\lim_{\eta_{\text{max}} \to 0} \frac{E_b}{N_0} = \ln 2 = -1.59 \quad dB \tag{2.5}$$

Hence, theoretically, the minimum required  $E_b/N_0$  for error-free transmission is -1.59 dB [6, 7, 8].

#### 2.2 Channel Coding Techniques

Various error-control codes have been used in the channel coding and decoding stages of wireless communication applications (e.g., deep space, CDMA, and satellite communications). Two main categories are linear block codes and convolutional codes. Other codes are derived from these two categories, and include serial concatenated codes and turbo codes (also called parallel concatenated convolutional codes).

The strength of an error-control code is measured by its *coding gain*. For a coded system, coding gain is defined as the reduction in SNR over an uncoded system to achieve the same Bit Error Rate (BER).

#### 2.2.1 Linear Block Codes

An (n,k) block encoder transforms a message of k bits into a message of n bits. The important feature of a block code is that a codeword depends only on the current input message and not on any previous message; i.e., the encoder is a memoryless device. In an (n,k) block code, there are  $2^k$  distinct messages. Since there is a one-to-one correspondence between a message and a codeword, there are also  $2^k$  distinct codewords. The code rate R = k/n determines the amount of redundancy.

An (n, k) block code is *linear* if

- the component-wise modulo-2 sum of two codewords is another codeword, and

- the code contains the all-zero codeword.

A linear *systematic* block code has the additional feature that the message itself is part of the codeword. In addition to the k-digit message sequence the codeword contains an

(n-k)-digit parity check sequence. This format allows the direct extraction of the message from the codeword.

The hamming distance between two codewords is defined as the number of places in which these codewords differ. The minimum hamming distance or minimum distance of a code is defined as the smallest hamming distance between any two different codewords in the code. This implies that for a linear block code, the minimum distance is the smallest weight (number of ones in a codeword) of the nonzero codewords in the code. The minimum distance parameter determines the error correction and detection capability of a code.

#### 2.2.2 Convolutional Codes

An (n, k, m) convolutional encoder has k input bits, n output bits, and m memory elements (m-bit shift register). Each output bit is the modulo-2 sum (XOR operation) of the current input bit and some or all of the previous m input bits. Then, the n output bits are multiplexed to produce the codeword. A systematic convolutional encoder has the additional feature of producing the input message as part of the output codeword. The structure of a rate 1/2 non-systematic non-recursive convolutional encoder is illustrated in Figure 2.2.

Figure 2.2: A rate 1/2 convolutional encoder

At time l, the input to the encoder is  $c_l$  and the output is a code block,

$$\mathbf{v}_l = (v_l^{(1)} v_l^{(2)})$$

The connections between the shift register elements and the modulo-2 adders can be described by generator sequences or generator polynomials

$$\mathbf{g}^{(1)} = (g_0^{(1)} g_1^{(1)} g_2^{(1)}) = (101)_2 = (5)_8 \text{ or } \mathbf{g}_1(D) = 1 + D^2$$

$\mathbf{g}^{(2)} = (g_0^{(2)} g_1^{(2)} g_2^{(2)}) = (111)_2 = (7)_8 \text{ or } \mathbf{g}_2(D) = 1 + D + D^2$

In other words,

$$\mathbf{g} = (\mathbf{g}^{(1)}, \, \mathbf{g}^{(2)}) = (5, 7)_8 \quad \text{or} \quad \mathbf{g}(D) = [\mathbf{g}_1(D) \, \mathbf{g}_2(D)] = [1 + D^2 \, 1 + D + D^2]$$

The term *convolutional code* comes from the observation that the  $i^{\text{th}}$  output sequence, where i = 1, 2, represents the convolution of the input sequence and the  $i^{\text{th}}$  generator sequence

$$\mathbf{v}^{(i)} = \mathbf{c} * \mathbf{g}^{(i)}, \qquad i = 1, 2$$

where \* denotes the convolution operator.

The encoder state transitions can be represented graphically by a trellis diagram. A trellis diagram is derived from the encoder state diagram by tracing all possible input/output sequences and state transitions. The encoder is trellis terminated if the final state is the same as the initial state for a specific frame length N. Figure 2.3 shows the trellis diagram of the convolutional encoder described in Figure 2.2, assuming trellis termination with N=6.

#### 2.3 Turbo Codes

Turbo codes, also known as Parallel Concatenated Convolutional Codes (PCCC) [9], and serial concatenated codes [10] concatenate two codes to achieve a good tradeoff between coding gain and decoding complexity.

Serial Concatenated Convolutional Codes (SCCC) use two codes in series separated by an *interleaver*. This approach has been adopted in space communications, with convolutional code as the inner code and low redundancy Reed-Solomon block code as the outer code. The primary reason for using a concatenated code is to achieve a low error rate with an overall decoding complexity that is lower than the one required for a single code with

Figure 2.3: Trellis diagram for the 1/2 non-systematic encoder of Figure 2.2 (trellis terminated, frame length N=6)

the same decoding performance. An interleaver is incorporated between the two codes to decorrelate the received symbols that are affected by burst errors generated by the inner decoder.

Turbo codes exploit a similar idea of connecting two codes and separating them by an interleaver [3]. The difference between turbo codes and serial concatenated codes is that, in turbo codes, two identical RSC codes are connected in parallel in the turbo encoder. Also, a long interleaver is used in turbo encoders to generate a concatenated code with a long block length, leading to a large coding gain. The turbo decoder consists of two RSC component decoders separated by interleavers and deinterleavers. The component decoders are based on a Soft-Input/Soft-Output (SISO) decoding algorithm, such as the Soft-Output Viterbi Algorithm (SOVA) or the Maximum A Posteriori (MAP) probability algorithm. A number of iterations are required by the turbo decoder to produce a BER as low as  $10^{-5}-10^{-7}$  at an SNR close to the Shannon capacity limit [6].

#### 2.3.1 Turbo Encoder

A turbo encoder is formed by parallel concatenation of two RSC encoders separated by a random interleaver [3]. The encoder structure is called parallel concatenation because the two encoders operate on the same set of input bits, rather than one encoder encoding the output of the other. A block diagram of a rate 1/3 turbo encoder is shown in Figure 2.4.

Figure 2.4: General diagram of a rate 1/3 turbo encoder

The generator matrix of a rate 1/2 constituent RSC code can be represented as

$$\mathbf{g}(D) = \begin{bmatrix} 1 & \frac{\mathbf{g}_1(D)}{\mathbf{g}_0(D)} \end{bmatrix}$$

where  $\mathbf{g}_0(D)$  and  $\mathbf{g}_1(D)$  are respectively feedback and feedforward polynomials with degree m. In the encoder, the same information sequence is encoded twice but in a different order. The first RSC component encoder operates directly on the input sequence  $\mathbf{c}$ , of length N, and has two outputs. The first output  $\mathbf{v}_0$  is equal to the input sequence  $\mathbf{c}$  since the encoder is systematic. The other output is the first parity check sequence  $\mathbf{v}_1$ . The second RSC encoder accepts the interleaved information sequence  $\tilde{\mathbf{c}}$  as input. Only the parity check sequence  $\mathbf{v}_2$  of the second encoder is transmitted. The information sequence and the parity check sequences of the two RSC component encoders are multiplexed to generate the turbo code sequence. Outputs from both RSC constituent encoders can be punctured and/or repeated to produce different code rates other than the direct 1/3 code rate.

For turbo encoders, either or both of the constituent RSC encoders is trellis terminated. Trellis termination means driving the encoder to the all-zero state. This is required at the end of each block to ensure that the initial state for the next block is the all-zero state.

#### 2.3.2 Interleaver

The interleaver in turbo coding is a pseudo-random block scrambler defined by a permutation of N elements with no repetitions.

The first role of the interleaver is to generate a long block code from small memory convolutional codes. Secondly, the interleaver decorrelates the inputs to the two SISO component decoders so that an iterative suboptimum decoding algorithm based on information exchange between the two component decoders can be applied. If the input sequences to the two component decoders are decorrelated, there is a high probability that after correction of some of the errors by one decoder, some of the remaining errors become correctable by the other decoder.

In a pseudo-random interleaver, a block of N input bits is read into the interleaver and read out pseudo-randomly. The pseudo-random interleaving pattern must be available at the decoder as well [6].

#### 2.3.3 Iterative Decoding of Turbo Codes

Turbo and serial concatenated codes can be decoded by either an A Posteriori Probability (APP) method or a Maximum Likelihood (ML) method. The practical importance of turbo and serial concatenated codes lies in the availability of a simple suboptimal decoding algorithm [3].

The iterative turbo decoder consists of two constituent SISO decoders serially connected via an interleaver, identical to the one in the encoder, and a corresponding deinterleaver, as shown in Figure 2.5.

The first SISO decoder takes as input the received information sequence  $\mathbf{r}_0$  and the received parity sequence  $\mathbf{r}_1$ , both generated by the first RSC encoder. Then, the decoder generates a soft-output (extrinsic information) which is interleaved and used to produce an improved estimate of the intrinsic information sequence at the input of the second SISO decoder.

The other two inputs to the second SISO decoder are the interleaved received information sequence  $\tilde{\mathbf{r}}_0$  and the received parity sequence produced by the second RSC encoder  $\mathbf{r}_2$ . The second decoder also produces a *soft output* (extrinsic information) which, after deinterleaving, is used to improve the estimate of the intrinsic information sequence at the input of the first SISO decoder. The decoder performance can be improved by this iterative operation, relative to a single operation of a serial concatenated decoder. The feedback loop is a distinct feature of this decoder and the term *turbo code* is derived from

Figure 2.5: General diagram of an iterative turbo decoder

the principle of the turbo engine.

After a certain number of iterations, the soft outputs of both decoders stop making further performance improvements. Then, the second SISO decoder creates *hard decisions*,  $\hat{\mathbf{c}}$ , that are deinterleaved. The hard decision detector and deinterleaver can be swapped to reduce memory usage.

The two identical component decoders can be based on either the MAP, an APP decoding algorithm, or the SOVA, an ML decoding algorithm. Therefore, there are two general categories of turbo decoders in relation to component decoder type: MAP and SOVA iterative turbo decoders.

The SOVA decoder has a lower complexity than that of the optimum MAP decoder, but the MAP decoder has a better decoding performance. Modified versions of the MAP

algorithm have been developed to achieve a near-optimum performance with a much lower complexity than the original MAP algorithm.

The Max-Log-MAP replaces multiplications and exponentiations in the original MAP by additions, and comparisons by logarithmic approximations; however, this comes at the expense of degrading decoding performance. The Log-MAP algorithm employs a more accurate logarithmic approximation by using lookup tables; it gives a decoding performance better than that of the SOVA, with a small additional complexity compared to that of the Max-Log-MAP. The performance is not far from that of the original MAP [6].

Consequently, most VLSI implementations are based on the Log-MAP algorithm which achieves an excellent tradeoff between complexity (hence area and power consumption) and decoding performance.

# 2.4 Standardized Turbo Codes for 3G Wireless Systems

Figure 2.6 illustrates the structure of standardized turbo-codes for 3G wireless systems [4]. For both RSC encoders,

$$\mathbf{g} = (\mathbf{g}_0, \, \mathbf{g}_1, \, \mathbf{g}_2) = (1011, 1101, 1111)_2 = (13, 15, 17)_8$$

where  $\mathbf{g}_0$  is the feedback polynomial, and  $\mathbf{g}_1$  and  $\mathbf{g}_2$  are the feedforward polynomials. The turbo code shown in Figure 2.6 is used in the cdma2000 standard [11], proposed by the TIA in USA, for high-speed (above 14.4 kbps) data services. Rate 1/2, 1/3, and 1/4 turbo codes are realized with appropriate puncturing patterns from Table 2.1.

For the UTRA/W-CDMA, proposed by ETSI in Europe and ARIB in Japan, the same constituent code is used for the rate 1/3 turbo code. Other code rates are obtained by a "rate matching" process, where coded bits are punctured or repeated accordingly [12]. The turbo code in Figure 2.6 is the result of an extensive simulation study [4].

For both of the 3G wireless systems, cdma2000 and UTRA/W-CDMA, turbo codes are terminated in a similar way. To enforce the trellis back to the all zero state, tail bits come from the contents of the shift registers, as shown by the dotted lines in Figure 2.6.

Figure 2.6: Standardized turbo code for 3G wireless systems (dotted lines effective for trellis termination only)

Moreover, because of the turbo interleaver, the contents of the shift register at the beginning of trellis termination are different for both constituent encoders. Therefore, for the standardized turbo code with eight state constituent codes, a total of  $3 \times 2 = 6$  tail bits are required to terminate both encoders.

For the sake of description, it is assumed that the first three tail bits are used to terminate the upper constituent encoder, whereas the last three tail bits are used to terminate the lower constituent encoder [4].

The standardized turbo interleavers for the two systems belong to the same general class of interleavers in that they share the following properties:

1. A small number of "mother interleavers" are specified, from which interleavers of

| Rate                    | 1/2 | 1/3 | 1/4 |

|-------------------------|-----|-----|-----|

| $\mathbf{x}(t)$         | 11  | 11  | 11  |

| $\mathbf{y}_0(t)$       | 10  | 11  | 11  |

| $\mathbf{y}_1(t)$       | 00  | 00  | 10  |

| $\mathbf{x}\prime(t)$   | 00  | 00  | 00  |

| $\mathbf{y}_0\prime(t)$ | 01  | 11  | 01  |

| $\mathbf{y}_1\prime(t)$ | 00  | 00  | 11  |

Table 2.1: Puncturing patterns for the turbo code of Figure 2.6

medium size are derived by *pruning* [13] unnecessary indexes. Pruning means ignoring an index that results in an invalid address because it exceeds the range of interest.

- 2. The mother interleavers can be viewed as two-dimensional matrices, where the entries are written into the matrix row by row and read out column by column.

- 3. Before reading out the entries, intra- and inter-row permutations are performed.

cdma2000 and UTRA/W-CDMA turbo interleavers differ from each other in the exact specifications of intra- and inter-row permutations and in the matrix dimensions of the mother interleavers [4].

There are several reasons why turbo codes are particularly suited for high-speed data services of 3G wireless systems:

- 1. At high speeds, sufficiently long blocks of data can be accumulated (e.g., within a frame of 10 or 20 ms) without causing substantial delay in the system. Turbo codes become more and more effective as block (or interleaver) size increases because of spectral thinning (i.e., the multiplicity of "neighbour" codewords becomes smaller as the interleaver size gets larger) [9].

- 2. For 3G high-speed data services, error-free data transmission is accomplished by Automatic Repeat Request (ARQ) protocol implemented in higher layers. As a

result, the more appropriate figure of merit is Frame Error Rate (FER), rather than BER. The performance difference between turbo and convolutional codes becomes even larger when the codes are compared in terms of FER as opposed to BER [14]. For turbo codes, however, the power of the code increases significantly as the frame size increases due to spectral thinning.

3. With fast power control, turbo codes are more effective as an FEC technique for 3G wireless systems. Indeed, without any power control, the performance advantage of turbo codes over convolutional codes decreases considerably. Power control is an important feature for the success of CDMA systems, which have been selected for 3G wireless technology.

# Chapter 3

# VLSI Design of Turbo Decoders

As stated in Chapter 2, turbo codes have been selected as a channel coding standard for 3G wireless high-speed data services. However, turbo decoding is a relatively complex task, hence consuming a considerable amount of area and energy of the entire mobile terminal. To obtain an efficient decoder implementation without degrading the required decoding performance, the system design space needs to be explored on multiple levels (e.g., algorithmic, architectural, gate, and circuit).

#### 3.1 Algorithmic-Level Design

As discussed in Chapter 2, there are two main algorithms that can be used in the component SISO decoders of the turbo decoder. These are the MAP decoding algorithm, based on APP probabilities, and the SOVA decoding algorithm, based on ML probabilities. Both algorithms use the iterative technique to enhance decoding performance. In addition, there are lower-complexity variations of the original MAP decoding algorithm such as Max-Log-MAP and Log-MAP.

#### 3.1.1 MAP Decoding Algorithm

The Bahl-Cocke-Jelinek-Raviv (BCJR) algorithm, also known as symbol-by-symbol MAP algorithm (MAP algorithm for short), is optimal for estimating the states or outputs of

a Markov process observed in white noise [15]. In the following, a brief overview of the algorithm is given [16].

Let the state of the encoder at time k be  $S_k$ , taking the values from 0 to  $2^{M-1}$ , where M is the encoder memory order. The bit  $d_k$  is associated with the transition from step k-1 to step k. It is assumed that the data frame length is N, and that the encoder is trellis terminated. The goal of the MAP algorithm is to provide us with the ratio of the APP of each information bit  $d_k$  being 1 to the APP of it being 0. The following is obtained

$$\Lambda(d_k) = \ln \frac{\Pr\{d_k = 1 | y_k\}}{\Pr\{d_k = 0 | y_k\}} = \ln \frac{\sum_{S_k} \sum_{S_{k-1}} \gamma_1(y_k, S_{k-1}, S_k) \cdot \alpha_{k-1}(S_{k-1}) \cdot \beta_k(S_k)}{\sum_{S_k} \sum_{S_{k-1}} \gamma_0(y_k, S_{k-1}, S_k) \cdot \alpha_{k-1}(S_{k-1}) \cdot \beta_k(S_k)}$$

(3.1)

where the forward recursion of the MAP can be expressed as

$$\alpha_k(S_k) = \frac{\sum_{S_{k-1}} \sum_{i \in \{0,1\}} \gamma_i(y_k, S_{k-1}, S_k) \cdot \alpha_{k-1}(S_{k-1})}{\sum_{S_k} \sum_{S_{k-1}} \sum_{i \in \{0,1\}} \gamma_i(y_k, S_{k-1}, S_k) \cdot \alpha_{k-1}(S_{k-1})}$$

$$\alpha_0(S_0) = \begin{cases} 1 & \text{for } S_0 = 0\\ 0 & \text{otherwise} \end{cases}$$

(3.2)

and the backward recursion as

$$\beta_k(S_k) = \frac{\sum_{S_{k+1}} \sum_{i \in \{0,1\}} \gamma_i(y_{k+1}, S_k, S_{k+1}) \cdot \beta_{k+1}(S_{k+1})}{\sum_{S_k} \sum_{S_{k+1}} \sum_{i \in \{0,1\}} \gamma_i(y_{k+1}, S_k, S_{k+1}) \cdot \alpha_k(S_k)}$$

$$\beta_N(S_N) = \begin{cases} 1 & \text{for } S_N = 0\\ 0 & \text{otherwise} \end{cases}$$

(3.3)

The branch transition probabilities are given by

$$\gamma_{i}[(y_{k}^{s}, y_{k}^{p}), S_{k-1}, S_{k}] = p(y_{k}^{s}|d_{k} = i) \cdot p(y_{k}^{p}|d_{k} = i, S_{k}, S_{k-1}) \cdot q(d_{k} = i|S_{k}, S_{k-1}) \cdot \Pr\{S_{k}|S_{k-1}\}; \quad i \in \{0, 1\}$$

(3.4)

The value of  $q(d_k = i|S_k, S_{k-1})$  is 1 if bit i is associated with the transition from state  $S_{k-1}$  to state  $S_k$ , and 0 otherwise.  $\Pr\{S_k|S_{k-1}\}$  represents the a priori information of bit  $d_k$ : In case of no parallel transitions,  $\Pr\{S_k|S_{k-1}\} = \Pr\{d_k = 1\}$  if  $q(d_k = 1|S_k, S_{k-1}) = 1$ , and  $\Pr\{S_k|S_{k-1}\} = \Pr\{d_k = 0\}$  if  $q(d_k = 0|S_k, S_{k-1}) = 1$ .

#### 3.1.2 Max-Log-MAP Decoding Algorithm

The MAP algorithm, in its original form, is difficult to implement because of numerical representation of probabilities and non-linear operations such as exponentiations and multiplications [16]. To avoid these problems, the logarithms of  $\gamma_i[(y_k^s, y_k^p), S_{k-1}, S_k], \alpha_k(S_k)$ , and  $\beta_k(S_k)$  are taken instead.

By taking the logarithm of  $\gamma_i[(y_k^s, y_k^p), S_{k-1}, S_k]$  derived in (3.4) and inserting

$$p(y_k^s|d_k = i) = \frac{1}{\sqrt{\pi N_0}} \cdot e^{-\frac{1}{N_0} [y_k^s - x_k^s(i)]^2}$$

$$p(y_k^p|d_k = i, S_k, S_{k-1}) = \frac{1}{\sqrt{\pi N_0}} \cdot e^{-\frac{1}{N_0} [y_k^p - x_k^p(i, S_k, S_{k-1})]^2}$$

(3.5)

we obtain the following expression for  $q(\cdot) = 1$

$$\ln \gamma_i[(y_k^s, y_k^p), S_{k-1}, S_k] = \frac{2y_k^s x_k^s(i)}{N_0} + \frac{2y_k^p x_k^p(i, S_k, S_{k-1})}{N_0} + \ln \Pr\{S_k | S_{k-1}\} + K$$

(3.6)

Since the constant K cancels out in the calculation of  $\ln \alpha_k(S_k)$  and  $\ln \beta_k(S_k)$ , it can be ignored. Notice that  $N_0$  must be estimated to correctly weigh the channel information with the a priori probability  $\Pr\{S_k|S_{k-1}\}$ .

For  $\ln \alpha_k(S_k)$ , we get

$$\ln \alpha_k(S_k) = \ln \left( \sum_{S_{k-1}} \sum_{i \in \{0,1\}} e^{\ln \gamma_i [(y_k^s, y_k^p), S_{k-1}, S_k] + \ln \alpha_{k-1}(S_{k-1})} \right) -$$

$$\ln \left( \sum_{S_k} \sum_{S_{k-1}} \sum_{i \in \{0,1\}} e^{\ln \gamma_i [(y_k^s, y_k^p), S_{k-1}, S_k] + \ln \alpha_{k-1}(S_{k-1})} \right)$$

$$(3.7)$$

To simplify the solution, the following approximation is used:

$$\ln(e^{\delta_1} + \ldots + e^{\delta_n}) \approx \max_{i \in \{1...n\}} \delta_i$$

(3.8)

$\max_{i \in \{1...n\}} \delta_i$  can be calculated by successively using n-1 maximum functions over only two values. From now on, we will use the notation:  $\bar{\gamma}(\cdot) = \ln \gamma(\cdot)$ ,  $\bar{\alpha}(\cdot) = \ln \alpha(\cdot)$ , and  $\bar{\beta}(\cdot) = \ln \beta(\cdot)$ . Eventually, we obtain

$$\bar{\alpha}_{k}(S_{k}) = \max_{(S_{k-1},i)} \{ \bar{\gamma}_{i}[(y_{k}^{s}, y_{k}^{p}), S_{k-1}, S_{k}] + \bar{\alpha}_{k-1}(S_{k-1}) \} - \max_{(S_{k}, S_{k-1}, i)} \{ \bar{\gamma}_{i}[(y_{k}^{s}, y_{k}^{p}), S_{k-1}, S_{k}] + \bar{\alpha}_{k-1}(S_{k-1}) \}$$

$$(3.9)$$

and similarly,

$$\bar{\beta}_k(S_k) = \max_{(S_{k+1},i)} \{ \bar{\gamma}_i [(y_{k+1}^s, y_{k+1}^p), S_k, S_{k+1}] + \bar{\beta}_{k+1}(S_{k+1}) \} - \max_{(S_k, S_{k+1}, i)} \{ \bar{\gamma}_i [(y_{k+1}^s, y_{k+1}^p), S_k, S_{k+1}] + \bar{\alpha}_k(S_k) \}$$

(3.10)

The second terms are a consequence of the derivation from (3.2) and (3.3); omitting them has no effect on the value of the output of the Max-Log-MAP algorithm since these normalization terms will cancel out in (3.11). Similarly, an approximation of the log-likelihood reliability of each bit  $d_k$  can be given as follows

$$\Lambda(d_k) \approx \max_{(S_k, S_{k-1})} \{ \bar{\gamma}_1[(y_k^s, y_k^p), S_{k-1}, S_k] + \bar{\alpha}_{k-1}(S_{k-1}) + \bar{\beta}_k(S_k) \} - \max_{(S_k, S_{k-1})} \{ \bar{\gamma}_0[(y_k^s, y_k^p), S_{k-1}, S_k] + \bar{\alpha}_{k-1}(S_{k-1}) + \bar{\beta}_k(S_k) \}$$

(3.11)

To be used in a turbo decoder, the output of the Max-Log-MAP algorithm,  $\Lambda(d_k)$ , is split into three terms (extrinsic, a priori, and systematic components). We begin with defining

$$\bar{\gamma}_i \prime (y_k^p, S_{k-1}, S_k) = \ln p(y_k^p | d_k = i, S_k, S_{k-1}) + \ln q(d_k = i | S_k, S_{k-1})$$

(3.12)

By inserting this into (3.11), we obtain

$$\Lambda(d_k) \approx \left[ \max_{(S_k, S_{k-1})} \{ \bar{\gamma}_1 \prime (y_k^p, S_{k-1}, S_k) + \bar{\alpha}_{k-1} (S_{k-1}) + \bar{\beta}_k (S_k) \} + \ln p(y_k^s | d_k = 1) + \ln \Pr\{d_k = 1\} \right] - \left[ \max_{(S_k, S_{k-1})} \{ \bar{\gamma}_0 \prime [y_k^p, S_{k-1}, S_k] + \bar{\alpha}_{k-1} (S_{k-1}) + \bar{\beta}_k (S_k) \} + \ln p(y_k^s | d_k = 0) + \ln \Pr\{d_k = 0\} \right]$$

(3.13)

which can be written as

$$\Lambda(d_k) \approx \max_{(S_k, S_{k-1})} \{ \bar{\gamma}_1 \prime (y_k^p, S_{k-1}, S_k) + \bar{\alpha}_{k-1} (S_{k-1}) + \bar{\beta}_k (S_k) \} - \\

\max_{(S_k, S_{k-1})} \{ \bar{\gamma}_0 \prime [y_k^p, S_{k-1}, S_k] + \bar{\alpha}_{k-1} (S_{k-1}) + \bar{\beta}_k (S_k) \} + \\

\frac{4y_k^s}{N_0} + L(d_k) \tag{3.14}$$

The first two terms comprise the so-called extrinsic information, the third term is the systematic component, and the last term is the a priori component. The extrinsic information is easily obtained by subtracting the systematic and the a priori components from the output Log-Likelihood Ratio (LLR),  $\Lambda(d_k)$ . The extrinsic information of the current decoding stage will be used as the a priori information,  $L(d_k)$ , in the next decoding stage.

We need to determine the a priori information,  $\ln \Pr\{S_k|S_{k-1}\}$ , in (3.6). If  $q(d_k = 1|S_k, S_{k-1}) = 1$ , then

$$L(d_k) = \ln \frac{Pr\{d_k = 1\}}{Pr\{d_k = 0\}} = \ln \frac{Pr\{S_k | S_{k-1}\}}{1 - Pr\{S_k | S_{k-1}\}}$$

(3.15)

hence,  $\ln \Pr\{S_k|S_{k-1}\} = L(d_k) - \ln(1 + e^{L(d_k)})$ . Using (3.8), this can be approximated to

$$\ln \Pr\{S_k | S_{k-1}\} \approx L(d_k) - \max[0, L(d_k)]$$

(3.16)

If  $q(d_k = 0|S_k, S_{k-1}) = 1$ , then

$$L(d_k) = \ln \frac{Pr\{d_k = 1\}}{Pr\{d_k = 0\}} = \ln \frac{1 - Pr\{S_k | S_{k-1}\}}{Pr\{S_k | S_{k-1}\}}$$

(3.17)

hence,  $\ln \Pr\{S_k|S_{k-1}\} = -\ln(1+e^{L(d_k)})$ . Similarly, it can be approximated to

$$\ln \Pr\{S_k | S_{k-1}\} \approx -\max[0, L(d_k)]$$

(3.18)

#### 3.1.3 Log-MAP Decoding Algorithm

Because of the approximation in (3.8), the Max-Log-MAP algorithm is sub-optimal and yields an inferior soft-output than that of the MAP algorithm. The problem is to exactly

calculate  $\ln(e^{\delta_1} + \ldots + e^{\delta_n})$ . This problem can be solved by using the Jacobian logarithm [16]

$$\ln(e^{\delta_1} + e^{\delta_2}) = \max(\delta_1, \delta_2) + \ln(1 + e^{-|\delta_2 - \delta_1|}) = \max(\delta_1, \delta_2) + f_c(|\delta_2 - \delta_1|)$$

(3.19)

where  $f_c(\cdot)$  is a correction function. By using recursion, it can be proven that

$$\ln(e^{\delta_1} + \dots + e^{\delta_n}) = \ln(e^{\delta} + e^{\delta_n}) = \max(\delta, \delta_n) + f_c(|\delta_n - \delta|),$$

where  $\delta = \ln(e^{\delta_1} + \dots + e^{\delta_{n-1}})$  (3.20)

When deriving the Log-MAP algorithm, all maximizations over two values are augmented with the correction function. As a consequence, by correcting, at each step, the approximation made by the Max-Log-MAP, we have preserved the original MAP algorithm.

By calculating  $f_c(\cdot)$ , we lose some of the low complexity of the Max-Log-MAP algorithm. The correction function in (3.19) can be implemented using a lockup table. It is found in [16] that excellent results can be obtained with eight stored values and  $|\delta_2 - \delta_1|$  ranging between 0 and 5.

## 3.1.4 SOVA Decoding Algorithm

The Viterbi algorithm (VA), in its MAP form, is described in [17]. It searches for the  $i^{\text{th}}$ -state sequence  $\mathbf{S}^{(i)}$ , and thus the desired information sequence  $\mathbf{d}^{(i)}$ , by maximizing over i the APP

$$P(\mathbf{S}^{(i)}|\mathbf{y}) = p(\mathbf{y}|\mathbf{S}^{(i)}) \cdot \frac{P(\mathbf{S}^{(i)})}{p(\mathbf{y})}$$

(3.21)

Since y is fixed, the following is equivalently maximized:

$$P(\mathbf{y}|\mathbf{S}^{(i)}) \cdot P(\mathbf{S}^{(i)}) \tag{3.22}$$

The maximization is realized in the code trellis, when for each state s and each time k, the path with the largest probability, *i.e.*, ML,  $p(\mathbf{S}_{j\leq k}^{(i)}, \mathbf{y}_{j\leq k}^{(i)})$  is selected. This probability can be obtained by multiplying the branch transition probabilities associated to path i. They are  $\gamma_j(st^{(i)}, s^{(i)})$  for  $1 \leq j \leq k$  and are similar to those defined by (3.4). Since

the maximum is not changed if the logarithm is taken, the same metric computation can be performed as described for the forward recursion of the Log-MAP algorithm. For the metric of the  $i^{th}$  path at time k,

$$M_k(s^{(i)}) = M_{k-1}(st^{(i)}) + \frac{1}{2}L_c(y_k^s x_k^{s^{(i)}} + y_k^p x_k^{p^{(i)}}) + \frac{1}{2}L(d_k)x_k^{s^{(i)}}$$

where  $L_c = 4\frac{E_s}{N_0}$  for AWGN channel (3.23)

This slight modification of the metric of the VA in (3.23) incorporates the a priori information about the probability of the information bits. The SOVA can be implemented in the register exchange mode or in the trace-back mode. It will be described now for the latter mode using the log-likelihood algebra [18].

It is desirable to obtain the soft output for bit  $\hat{d}_k$ , which the VA decides after a delay  $\delta$ . The VA proceeds in the usual way by calculating the metrics for the  $i^{\text{th}}$  path using (3.23). For each state, the VA selects the path with the larger metric  $M_k(s^{(i)})$ . At each time  $k + \delta$ , the VA has selected the ML path with index  $i_{\delta}$  and has discarded the other path with index  $i_{\delta}'$  ending at this state. Along the ML path  $i_{\delta}$ , which decides the bit  $\hat{d}_k$ ,  $\delta + 1$  non-surviving paths  $i_l'$  with indices  $l = 0, \ldots, \delta$  have been discarded. The metric difference is defined as

$$\Delta_k^l = M_{k+l}(S^{(i_l)}) - M_{k+l}(S^{(i_l)}) \ge 0 \tag{3.24}$$

It is shown in [19] that the L-value of the hard decision  $\hat{d}_k$  is approximated by

$$L(\hat{d}_k) \approx \hat{d}_k \cdot \min_{l=0,\dots,\delta} \Delta_k^l \tag{3.25}$$

Thus, we have the same hard decisions as the classical VA, and the reliability of the decisions is obtained by taking the minimum of the relevant metric differences along the ML path.

From (3.23) and (3.24), we find

$$\Delta_k^l = (M_{j < k}^{(1)} - M_{j < k}^{(2)}) + (M_{k < j < k+l}^{(1)} - M_{k < j < k+l}^{(2)}) + \frac{1}{2} L_c y_k^p (x_k^{p^{(1)}} - x_k^{p^{(2)}}) + \frac{1}{2} L_c y_k^s [\hat{d}_k - (-\hat{d}_k)] + \frac{1}{2} L(d_k) [\hat{d}_k - (-\hat{d}_k)]$$

(3.26)

Therefore, the minimum value in (3.25) has the same structure. Thus, the SOVA output in its approximate version in (3.25) has the format

$$L_{\text{SOVA}}(\hat{d}_k) = L_c y_k^s + L(d_k) + \underbrace{\hat{d}_k \cdot \{\text{first 3 items in } (3.26)\}}_{L_e(\hat{d}_k)}$$

(3.27)

Similar to the Log-MAP algorithm, the output LLR consists of three components: systematic (first term), a priori (second term), and extrinsic information (last term). Also, extrinsic information of the current decoding stage, which is produced by subtracting the first two terms from the output LLR, is used as a priori information in the next decoding stage.

# 3.1.5 Comparison of MAP and SOVA Iterative Decoding Algorithms

The relationship between MAP, Log-MAP, Max-Log-MAP, and SOVA turbo decoding algorithms is illustrated in Figure 3.1 [16].

Figure 3.1: Relationship between MAP, Log-MAP, Max-Log-MAP, and SOVA

From the previous discussion, it can be seen that the Max-Log-MAP algorithm and the SOVA work with the same metric. If only the hard decisions are considered, the algorithms are identical; however, they behave in different ways in computing the information returned about the reliability of decoded bit  $d_k$ . The SOVA considers only one competing path per decoding step; *i.e.*, for each bit  $d_j$ , it does not consider all the competing paths but only the survivors of the Viterbi algorithm. To be taken into account in the reliability estimation, a competing path must join the path chosen by the Viterbi algorithm without being eliminated.

A comparison of (Log-)MAP, Max-Log-MAP, and SOVA is illustrated in Figure 3.2 [16]. The MAP includes all paths in its calculation but splits them into two sets: those that have an information bit one, at step j, and those that have an information bit zero; it returns the LLR of these two sets. The only thing that changes from step to step is the classification of the paths into the respective sets. Due to the Markov properties of the trellis, the computation can be done recursively. In contrast, the Max-Log-MAP looks at only two paths per step: the best with bit zero and the best with bit one at transition j; it then outputs the difference of the log-likelihoods. However, from step to step, one of these paths can change, but one will always be the ML path. The SOVA will always correctly find one of these two paths (the ML path), but not necessarily the other, since it may be eliminated before merging with the ML path. There is no bias on the SOVA output when compared to that of the Max-Log-MAP algorithm; only the former will be noisy.

Comparing decoding performance for the previously discussed decoding algorithms, it is found that [16]:

- The (Log-)MAP decoder is the best, followed by the Max-Log-MAP and SOVA.

- For a few iterations or for a small SNR, Max-Log-MAP and SOVA significantly degrade with respect to the (Log-)MAP.

- With an increasing number of iterations or with increasing SNR, the Max-Log-MAP approaches the (Log-)MAP.

Furthermore, for small memories the SOVA is roughly half as complex as the Log-MAP algorithm [16, 18].

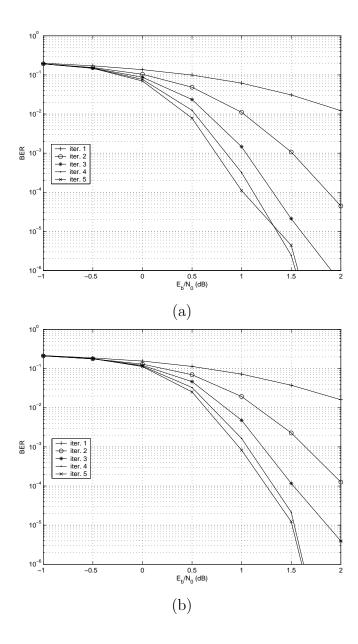

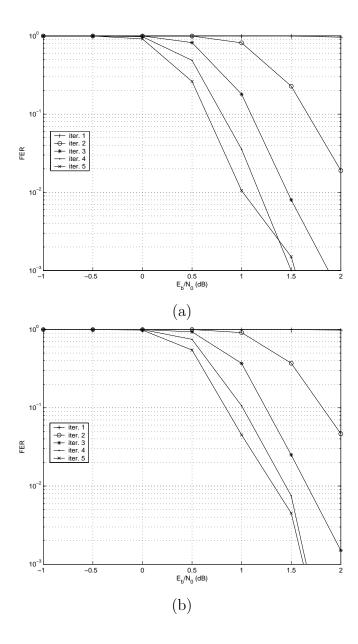

Figures 3.3 and 3.4 compare the decoding performance of the four algorithmic implementations of the turbo decoder for both low and high number of iterations. Figure 3.3 shows BER vs.  $E_b/N_0$  for the four algorithmic choices with both two and five iterations. Similarly, Figure 3.4 shows FER vs.  $E_b/N_0$  for the four algorithmic choices of the turbo decoder with both two and five iterations. These simulations are based on a rate 1/3 turbo code with generator polynomial  $\mathbf{g} = (13, 15)_8$ , which is suitable for 3G wireless systems.

From the performance graphs, it is evident that the MAP and Log-MAP have better performance than the SOVA and Max-Log-MAP. The results are in agreement with the conclusions found in [16, 18], as previously discussed.

Figure 3.2: Comparing (Log-)MAP, Max-Log-MAP, and SOVA [16]

From the previous discussion, the Log-MAP algorithm is selected for implementation since it has the best tradeoff between decoding performance and decoder complexity. It has the same high decoding performance as the highly-complex original MAP; however, this comes at some additional complexity, compared to that of the low decoding performance Max-Log-MAP and SOVA.

Figure 3.3: BER vs.  $E_b/N_0$  for the MAP, SOVA, Max-Log-MAP, and Log-MAP turbo decoders with: (a) 2 iterations, (b) 5 iterations (rate 1/3,  $\mathbf{g} = (13, 15)_8$ , 1024 bits/frame, 2000 frames)

Figure 3.4: FER vs.  $E_b/N_0$  for the MAP, SOVA, Max-Log-MAP, and Log-MAP turbo decoders with: (a) 2 iterations, (b) 5 iterations (rate 1/3,  $\mathbf{g} = (13, 15)_8$ , 1024 bits/frame, 2000 frames)

# 3.2 Exploration of System Design Space for Turbo Codecs

Although turbo codes have been employed in wide-band (3G) mobile radio systems, turbo decoders are relatively complex for implementation. To obtain efficient decoder implementations, the system design space needs to be explored on multiple levels. In this section, the system design space is explored with focus on the implementation-dependent part. The design decisions are rated regarding complexity, throughput, and power consumption.

Although iterative decoding is significantly less complex than optimal decoding, it remains a computationally complex task due to the iterative use of costly component decoders. Even the use of the sub-optimal Max-Log-MAP algorithm [16] for component code decoding results in considerably high computing performance needs. First order complexity estimations reveal approximately 1500 MOPS for a user data rate of 2 Mbps, assuming constraint length K=3 codes and five iterations [20].

In order to achieve complexity reduction, simplifications can be attempted at different abstraction levels (e.g., system, architecture, register-transfer, gate, and transistor levels). However, the optimization potential is, in general, closely related to the abstraction level. Application knowledge can be exploited to significantly simplify high-level specifications towards lower implementation complexity, where low-level design representations, in most cases, lack this opportunity. Thus, cost efficient turbo-decoder implementations require system design space exploration before mapping the algorithmic-level specification onto hardware or DSP.

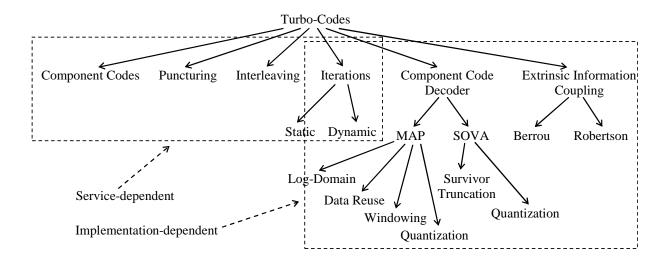

Figure 3.5 depicts the system design space for turbo codecs. It is comprised of a service-dependent part and an implementation-dependent part. The components of the turbo-code encoder directly define the service dependent part of the system design space: component codes, puncturer, and interleaver. This is underlined by only the encoder being defined by standardization bodies. Although the required number of iterations is implementation-dependent, this number may also depend on the service to realize different qualities of service. The number of iterations is either static or dynamically determined during decoding after evaluation of some criteria [21].

Component RSC codes are decoded with the MAP algorithm or with the SOVA. When

Figure 3.5: System design space for turbo codecs [20]

implementing MAP or SOVA, the designer has to choose among several implementation options which reduce computational complexity, increase throughput, and/or reduce power consumption. Extrinsic information coupling (for the feedback) is performed according to Berrou's original method [3] or rather directly as proposed by Robertson [21].

The FEC control has to sustain certain BERs for given SNRs: BER = f(SNR). However, implementation options influence this function. Due to the lack of a comprehensive turbo-code theory, the degradation has to be validated by simulation and traded off against implementation complexity [20]. Results of the influence of service-related parameters, such as component codes, puncturing, and interleaving, on the BER are beyond the scope of this discussion, and the focus is on implementation-dependent parameters.

## 3.2.1 Turbo Decoder Optimization

The complexity of the turbo decoder (TD) is a function of the component code decoder (CD) and the number of iterations (IT):

$$O_{\rm TD} = f({\rm CD, IT}) \tag{3.28}$$

where the complexity of the component code decoder (CD) depends on operator strength (OS), amount of data reuse (DR), parallelism (P), and quantization (Q):

$$O_{\rm CD} = f(\rm OS, \rm DR, \rm P, \rm Q) \tag{3.29}$$

In this subsection, design tradeoffs with respect to these parameters are discussed. Also, extrinsic information coupling and intricacies of software implementations are briefly addressed [20]:

### 1. Component decoder (CD) optimization:

### (a) Operator strength (OS):

Mainly two alternatives have been proposed for formulating the SOVA: trace-back and register exchange structures [18, 22]. These induce different implementation architectures. The superior performance of turbo-decoding with the MAP algorithm is clearly demonstrated in [23, 16]; hence, the SOVA is excluded from the following discussion.

In addition, implementation complexities of the MAP and SOVA do not differ significantly. As per the discussion in Section 3.1 about the iterative decoding algorithms, it is found that the Log-MAP is equivalent in decoding performance to the original MAP, avoids its numerical problems, and is easier to implement due to operator strength reduction [20, 24]. Thus, from an implementation point of view, the MAP should always be implemented in the logarithmic domain. Further simplification yields the Max-Log-MAP by omitting the correction term of the Jacobian algorithm; however, this degrades the performance.

As for the Max-Log-MAP, the inner loops of the forward and backward recursions of the Log-MAP comprise an add-compare-select (ACS) operation, but the add operation hereby additionally involves the evaluation of the correction term of the Jacobian algorithm. This correction term is best computed by using a lookup table, but this requires additional memory access and an extra logic for each ACS. The memory accesses can be traded for area (assuming a hardware implementation) if the lookup table is implemented as a combinational logic block. Either way, decoding speed decreases and power consumption increases for most target architectures.

### (b) Data reuse (DR):

Calculations independent of the decoding iteration can be performed only once, and the intermediate results can be used in each MAP iteration: In case of a trellis transition, the corresponding branch metric of the (Max-)Log-MAP calculates as a sum of terms depending on the received symbols and the a priori (hence previous stage extrinsic) information [16]. Equation (3.6) is rewritten to clarify this point:

$$\bar{\gamma}_i[(y_k^s, y_k^p), S_{k-1}, S_k] = \frac{2y_k^s x_k^s(i)}{N_0} + \frac{2y_k^p x_k^p(i, S_k, S_{k-1})}{N_0} + \ln \Pr\{S_k | S_{k-1}\} \quad (3.30)$$

The a priori information  $\ln \Pr\{S_k|S_{k-1}\}$  changes after each MAP iteration, whereas the terms stemming from the received symbols  $y_k^s$  and  $y_k^p$  remain constant during the entire decoding process of one data block. Therefore, precalculation of constant terms and performing, e.g., five decoding iterations (with two SISO decoders each) saves approximately 20% of the computational complexity. The total memory size does not increase, as the pre-calculated intermediate terms replace the received symbols [20].

### (c) Parallelism (P) and pipelining:

The inherent parallelism of turbo-decoders can be exploited to nearly arbitrarily tradeoff area for speed and power consumption.

On the top-most level, the component decoders can be arbitrarily pipelined (i.e., functionally parallelized). The amount of additional buffer memory hereby depends on the pipeline depth.

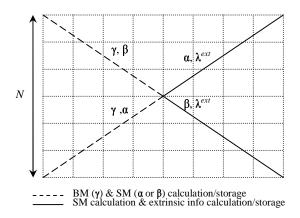

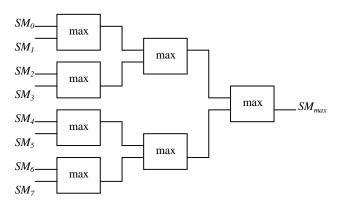

On the component (SISO) decoder level, the functional units can be parallelized to some extent. For example, the functional units of the SISO decoder include the branch metric, forward and backward state metric, and soft-output (LLR) calculation. An obvious solution is to parallelize the branch metric with the forward state metric calculation, and the backward state metric with the soft-output calculation. Compared to a serialized solution, this approximately doubles the throughput. Adding a second branch metric calculation unit and a second soft-output calculation unit again doubles the throughput; this is described as follows. For the first half of the data block, each of the forward

and backward state metric calculation units is parallelized with a branch metric calculation unit. For the second half, each state metric calculation unit is parallelized with a soft-output calculation unit [20, 25].

Parallelism, on an additional level, is introduced by observing that the decoding of a data block in a component decoder can be divided into the decoding of a set of overlapping sub-blocks. This is called the "sliding window technique" or "windowing" [20, 25]. Windowing permits to further increase the throughput or to minimize the required memory size. For the window overlap being small compared to the window size, serial window processing reduces the required memory size by the ratio of block size to window size, while retaining throughput. In contrast, parallel window processing increases throughput by the same factor, while memory size remains constant.

On a lower level, the trellis butterflies (ACS sections) can obviously be processed in parallel during forward and backward recursion. It is quite evident that throughput, area, and power consumption increase according to the degree of parallelism.

When the parallelism of turbo-decoding is exploited, many tradeoffs are possible to obtain an optimal architecture. However, the impact of parallelism, at different levels, on memory size and structure is complex and should be carefully watched.

### (d) Quantization (Q) and normalization

Quantization and normalization are ways to decrease the bit-width of a fixed-point approximation of a turbo-decoder. Each saved bit has a significant impact on area and power consumption of the decoder implementation. Memory can also be saved since the bit-width of the values is reduced. A good tradeoff between decoding performance and decoder complexity (hence area and power consumption) is desired.

### 2. Effect of the number of iterations (IT):

Depending on the quality of the channel and the demanded quality of service, the number of decoding iterations can be varied dynamically in order to save power.

However, the decoder has to be designed to handle the worst case. Many power saving techniques have been suggested in recent research: Some of these techniques are based on power-down mode [26] and some use voltage scaling [26] to save power consumption. Alongside one of these two techniques, there has to be a stopping criterion for further decoding iterations. Some of the stopping criteria compare soft-outputs and/or extrinsic information to some predefined thresholds, some compare hard decisions (decoded bits) of the current and previous iterations, and some use Cyclic-Redundancy-Check (CRC) checksums.

- 3. Regarding extrinsic information coupling, the Robertson's method is recommended over the original Berrou's method. Robertson's method is computationally less complex, performs as well, and does not require knowledge of the extrinsic information distribution parameters. For example, this saves up to 30% logic area for the FPGA implementation in [20].

- 4. For a software implementation of a turbo-decoder, it is essential to find a formulation of the algorithm that fits best to the given core and memory architecture, which are highly depending on the target device. This can be achieved by application of common data and control flow transformations. Since turbo-decoding is a data-flow dominated application, memory mapping and register assignment are important issues for the resulting performance. For multiple memory banks and multiport memory, parallel transfers highly increase the bandwidth. A skillful arrangement of the data within the memory simplifies the memory access order and allows easier addressing modes, leading to incremental addressing for example.

The performance of pure software implementations is below the requirements for high data rate applications. Hardware implementations outperform software implementations, but they lack flexibility. Therefore, to achieve the high performance of hardware implementations and flexibility of software solutions, a hardware/software co-design can be used. In this mixed hardware/software implementation, performance-critical parts are implemented in hardware and flexibility-critical parts are implemented in software [20].

# 3.3 Architectures and Design Techniques for Turbo Decoders