## Silicon Nanowire Based Photodetectors: Modeling and Fabrication

by

Anita Fadavi Roudsari

A thesis presented to the University of Waterloo in fulfillment of the thesis requirement for the degree of Doctor of Philosophy in Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2014

© Anita Fadavi Roudsari 2014

# Author's Declaration

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

## Abstract

This research is focused on investigating the role of silicon nanowires in designing high gain, high sensitivity photodetectors, and is based on both device modeling and fabrication. We demonstrate that the superior electrostatic control within the nanowires enables us to effectively engineer the energy band and design novel photodetector architectures. This is due to the high surface to volume ratio in nanowires which allows for the ability to change the electrical properties of a nanowire device in response to a voltage applied to the gate contact.

In the first part of the thesis, two photodetector geometries are proposed and theoretically studied. The first geometry is a Metal Oxide Semiconductor (MOS) device with nanowires incorporated in its channel. The next geometry is a junction-less phototransistor, e.g. a photoconductor with a third terminal as the gate. Both geometries are important due to their ability to generate optical gain. For both cases, first the role of nanowire parameters and their pros and cons on the device photo-response is investigated. Afterwards, we propose modifications to the device geometry in order to improve the performance of the device in terms of optical gain and sensitivity.

The first modification is allocating a wide region for light absorption in the channel, since single nanowire based photodetectors suffer from lack of efficient absorption, due to their small cross sectional area. Use of phototransistors also helps the photocurrent increase, due to the device's internal gain. The second modification incorporates two nanowire/ gate geometries to improve the device photo-response, in terms of both dark- and photo-current. The charge flow in each nanowire is controlled by a gate, which changes the energy band within the nanowire. This band engineering allows for both increasing the optical gain of the phototransistor, and keeping the dark current low. We report nanowire based phototransistors that are potentially able to detect low levels of light intensity (photon rate of less than  $50s^{-1}$ ).

The second part of the thesis is devoted to the fabrication of the nanowire based structures. Top-down approach is used, mainly due to the better control on the nanowire size and position, and repeatability of the processes involved. Fabrication process includes several steps of electron beam lithography, dry and wet etching, metal and dielectric deposition and annealing. Predeveloped recipes are used when available. New recipes are also developed to better suit the specific needs of the devices. The measurement results of the fabricated structures verify most of the concepts proposed in the modeling phase.

In the third part of this thesis, we characterize MOS capacitors with and without illumination, based on Silicon on Insulator (SOI) structures used in the previous chapters. Here, we report the first observation of photon induced negative capacitance in a conventional Metal Oxide Semiconductor (MOS) capacitor without the use of ferroelectric materials. Design and implementation of this phenomenon is presented in a capacitor where an aluminum oxide layer serves as the gate dielectric, and the capacitor is in depletion mode. Through extensive modeling, we establish that trap states at the semiconductor-oxide interface, coupled with the injection of photo-generated electrons are responsible for the negative capacitance. We find that varying the trap density and/or light intensity can tune the value of the negative capacitance. We show that in the presence of photons, the experimentally measured quasi-static capacitance in depletion is almost twice the value without photons. Further, the measured capacitance is larger than the values in accumulation and inversion.

## Acknowledgments

First and foremost I would like to express my deepest appreciation to my supervisors, professor M. P. (Anant) Anantram, and professor Simarjeet Saini. Even though I was from a completely different background, professor Anantram believed in my passion and my ability to work in this field. Thanks to professor Saini for his interest in this project, and his generous help and support. I am thankful to both of them for guiding me through this work, and for their instructive advice that helped me observe problems from different angles.

I would like to offer my thanks to the members of my dissertation committee, professor Shirley Tang, professor Karim S. Karim, professor Bo Cui, and professor Siva Sivoththaman for their constructive questions and suggestions that all helped elevate the quality of this work. I sincerely appreciate professor David Janes who accepted to be in my examination committee.

This PhD work was supported through WIN nanofellowship, and Teledyne DALSA Inc. I would like to thank Dr. Nixon O for his interest in this project, and his help and support during completion of this work. I am also thankful to Dr. Kevin Davis who helped me with device characterization and measurements.

I had a great opportunity to work at the Quantum Nano Centre (QNC) facility for fabricating the photodetector devices. By that time, due to space limitations of the temporary location of the facility (at the Institute for Quantum Computing, IQC), it was not possible to have all the necessary equipments at one place. However, the available equipments were very well thought and the facility was extremely well maintained; and this made it possible for me to complete the majority steps of device fabrication at QNC. My special thanks goes to Brian Goddard, Rodello Salandanan, Nathan Nelson-Fitzpatrick and Vito Logiudice.

I would like to specially appreciate professor Bo Cui, professor Selva Selvakumar, and professor Andrei Sazonov for guiding me through the fabrication challenges I encountered. I am also thankful to Joe Street, Zhen Gao, and Roohollah Samadzadeh Tarighat at the Centre for Advanced Photovoltaic Devices and Systems (CAPDS) for annealing the samples, and also Richard Barber (Giga-to-Nanoelectronics (G2N) Centre), Rasoul Keshavarzi and Paul Hayes for providing the opportunity to use their probe station systems.

I am indebted to my friends at QNC, G2N, and IQC for generously sharing their fabrication experience and resources with me. I would like to thank Jean-Luc Orgiazzi, Alireza Zandieh, Mustafa Muhammad, Mohsen Keshavarz Akhlaghi, Aidin Taeb, Jian Zhang, Yipu Song, Mustafa Bal, Shiva Abbaszadeh, Ehsan Fathi, Navid Jahed, Florian Ong, Reza Khorasaninejad, Bahareh Sadeghimakki, Michael Adachi, and professor Guoxing Miao. Special thanks to my colleague Jeyran Amirloo for helping me with deposition of silicon nitride on some samples, and to my colleagues Jenny Wan, Golam Rabbani, Navneet Dhindsa, and especially Iman Khodadad for their help with device characterization and measurements. I also would like to thank Guanting Li for his help during high temperature simulations.

My colleagues at the University of Waterloo, Nazy Ranjkesh, Behrooz Semnani, Naimeh Ghafarian, Sareh Taebi, and my friends Shiva Zaboli, Sahar Molla Aghajanzadeh, Fatemeh Dorri, Jennifer Doyle, Fatemeh Charkhab, Roshanak Houmanfar, Arash Tabibiazar, Mohsen Baratvand, Mehdi Torbatian, Leila Shayanpour, Reza Sherafat and Leila Yousefi made my stay in Canada pleasant and memorable. I am so proud and grateful for having such friends.

I would like to sincerely appreciate my parents, Aghdas Ghotbzadeh Asrar and Bahram Fadavi Roudsari, for their never-ending love and unconditional support. My parents taught me to think big and work hard. They taught me that nothing can prevent a person's will to reach his dreams, except himself. I am also thankful to my dear sisters, Ida and Atessa, my brother Alireza, and my niece Rose for their support and all of our unforgettable and wonderful memories.

Last but not the least, I am deeply grateful to my dearest friend and extraordinary colleague, my true love Daryoush. His passion for learning and hard-work for discovering the unknowns always inspires me. Taking this journey without his endless love and support was indeed impossible. To Daryoush

and to my parents:

Aghdas Asrar and Bahram Fadavi

# **Table of Contents**

| Li       | List of Tables xi          |                                                                                                                                                                          |    |  |  |

|----------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|

| Li       | List of Figures xxi        |                                                                                                                                                                          |    |  |  |

| Li       | List of Abbreviations xxii |                                                                                                                                                                          |    |  |  |

| 1        | $\mathbf{Intr}$            | oduction                                                                                                                                                                 | 1  |  |  |

|          | 1.1                        | Absorption of Light                                                                                                                                                      | 2  |  |  |

|          | 1.2                        | Noise in Photodetectors                                                                                                                                                  | 3  |  |  |

|          | 1.3                        | Figures of Merit in Photodetectors                                                                                                                                       | 5  |  |  |

|          | 1.4                        | Imagers: CCD versus CMOS                                                                                                                                                 | 6  |  |  |

|          | 1.5                        | Photoconductors                                                                                                                                                          | 9  |  |  |

|          | 1.6                        | Photodiodes                                                                                                                                                              | 11 |  |  |

|          |                            | 1.6.1 $pn$ Junction Photodiodes $\ldots \ldots \ldots$   | 11 |  |  |

|          |                            | 1.6.2 <i>pin</i> Junction Photodiodes                                                                                                                                    | 12 |  |  |

|          |                            | 1.6.3 Avalanche Photodiodes (APD) $\ldots \ldots \ldots$ | 14 |  |  |

|          | 1.7                        | Phototransistors                                                                                                                                                         | 16 |  |  |

|          | 1.8                        | Nanowire based Photodetectors                                                                                                                                            | 19 |  |  |

|          | 1.9                        | Research Objectives                                                                                                                                                      | 20 |  |  |

|          | 1.10                       | Organization of the Thesis                                                                                                                                               | 21 |  |  |

| <b>2</b> | Nan                        | owire based Junction Phototransistors                                                                                                                                    | 23 |  |  |

|          | 2.1                        | Photodetector Structure and Modeling                                                                                                                                     | 23 |  |  |

|          | 2.2                        | Role of Channel Width and Doping                                                                                                                                         | 28 |  |  |

|   |     | 2.2.1 Devices with Nanowire Arrays                                                                        | 34 |

|---|-----|-----------------------------------------------------------------------------------------------------------|----|

|   | 2.3 | Role of Channel Thickness                                                                                 | 35 |

|   | 2.4 | Ideas to Increase the Photocurrent                                                                        | 38 |

|   |     | 2.4.1 Role of Nanowire Width and Length                                                                   | 43 |

|   | 2.5 | Discussion                                                                                                | 46 |

|   | 2.6 | Chapter Summary                                                                                           | 48 |

| 3 | Nar | nowire based Junction-less Phototransistors                                                               | 50 |

|   | 3.1 | Junction-less Phototransistors: Principle of Operation                                                    | 51 |

|   |     | 3.1.1 Role of Channel Width and Doping                                                                    | 53 |

|   |     | 3.1.2 Role of Gate Length                                                                                 | 57 |

|   | 3.2 | Ideas to Increase the Optical Gain: Use of Multiple Gates                                                 | 58 |

|   |     | 3.2.1 Role of Bias and Nanowire Geometry                                                                  | 61 |

|   |     | 3.2.2 Linearity $\ldots$ | 67 |

|   |     | 3.2.3 Phototransistor Speed                                                                               | 68 |

|   | 3.3 | Chapter Summary                                                                                           | 69 |

| 4 | Dev | vice Fabrication                                                                                          | 70 |

|   | 4.1 | Junctions                                                                                                 | 71 |

|   | 4.2 | Active Region                                                                                             | 76 |

|   | 4.3 | Fabrication of the Gate Dielectric                                                                        | 82 |

|   | 4.4 | Source, Drain and Gate Contacts                                                                           | 84 |

|   | 4.5 | Chapter Summary                                                                                           | 87 |

| 5 | Neg | gative Capacitance; Experiment and Theory                                                                 | 89 |

|   | 5.1 | Ideal MOS Capacitor                                                                                       | 89 |

|   | 5.2 | Negative MOS Capacitor                                                                                    | 93 |

|   |     | 5.2.1 Device Fabrication and Measurements                                                                 | 95 |

|   |     | 5.2.2 Device Modeling                                                                                     | 97 |

|   |     | 5.2.3 Design Considerations: Role of Thickness and Width                                                  | 02 |

|   | 5.3 | Chapter Summary                                                                                           | 04 |

| 6            | Measurement Results 105 |                                                                 |       |

|--------------|-------------------------|-----------------------------------------------------------------|-------|

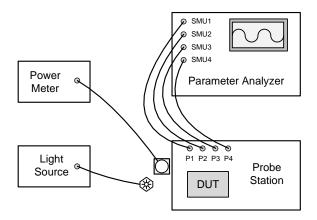

|              | 6.1                     | Measurement Setup                                               | . 105 |

|              | 6.2                     | Decision about Device Thickness                                 | . 105 |

|              | 6.3                     | Multiple Gate Structures                                        | . 110 |

|              |                         | 6.3.1 Normal and Mirrored Measurements                          | . 113 |

|              | 6.4                     | Chapter Summary                                                 | . 120 |

| 7            | Con                     | clusion and Future Work                                         | 121   |

|              | 7.1                     | Ideas for Future Work                                           | . 123 |

| A            | PPE                     | NDICES                                                          | 126   |

| $\mathbf{A}$ | Ana                     | lytical Approach for Lateral Bipolar Action in Phototransistors | 127   |

| в            | Noi                     | se Calculation                                                  | 132   |

| Bi           | bliog                   | graphy                                                          | 153   |

# List of Tables

| 2.1 | Parameters for the constant low-field mobility model                                           | 26  |

|-----|------------------------------------------------------------------------------------------------|-----|

| 2.2 | Comparison of junction phototransistors                                                        | 48  |

| 3.1 | Comparison of multiple gate junction-less phototransistors                                     | 66  |

| 3.2 | Rise time and fall time of multiple gate junction-less phototransistors $\ldots \ldots \ldots$ | 69  |

| 4.1 | Properties of the phosphorous ions that result the profile of figure 4.2 $\ldots$ .            | 72  |

| 4.2 | Summary of the $n^+pn^+$ junction fabrication                                                  | 75  |

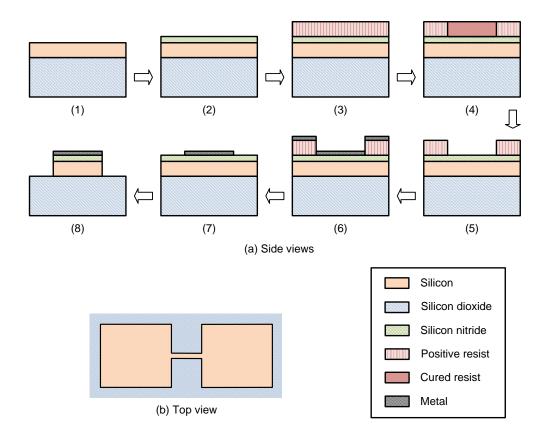

| 4.3 | Fabrication of the active region, using a hard metallic mask $\ldots \ldots \ldots \ldots$     | 78  |

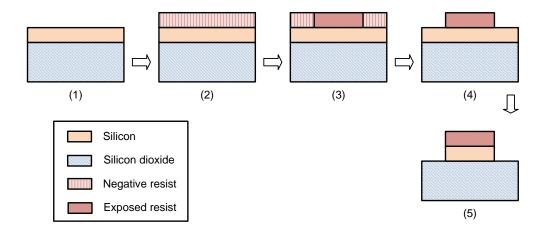

| 4.4 | Fabrication of the active region, using a negative resist for patterning and etching .         | 82  |

| 4.5 | Fabrication of the Gate Dielectric                                                             | 83  |

| 4.6 | Fabrication of the Contacts                                                                    | 86  |

| 5.1 | Parameters of the bandgap interface defect model                                               | 98  |

| 6.1 | Maximum possible depletion width $(t_s)$ , as a function of $C_{tot}/C_{ox}$                   | 109 |

| 6.2 | Effect of surface recombination on phototransistors                                            | 119 |

# List of Figures

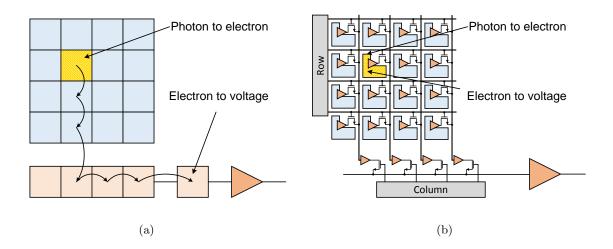

| 1.1 | Block diagram of (a) a CCD imager; and (b) a CMOS imager [14].                                                                                                                                                                                                                    | 7  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

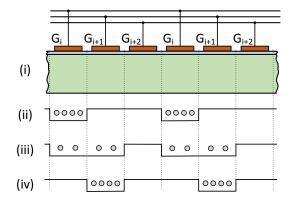

| 1.2 | Read out process in a CCD imager. (i) Line of detectors; $VG_i$ is positive; gates $G_{i+1}$ and $G_{i+2}$ are zero biased and screened from the light. (ii) Charge is trapped under $G_i$ . (iii) $VG_{i+1}$ is positive and charge is shared between $G_i$ and $G_{i+1}$ . (iv) | 0  |

| 1.3 | $VG_i$ is zero and charge is moved under $G_{i+1}$ now [16], page 297                                                                                                                                                                                                             | 8  |

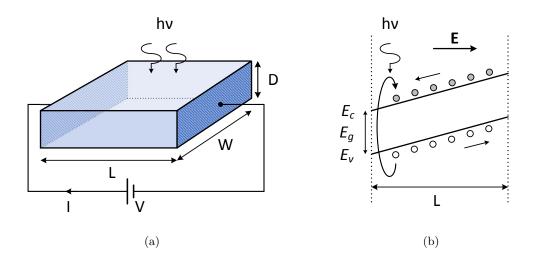

|     | generated electron-hole pairs drift towards the contacts in response to the electric                                                                                                                                                                                              |    |

|     | field                                                                                                                                                                                                                                                                             | 10 |

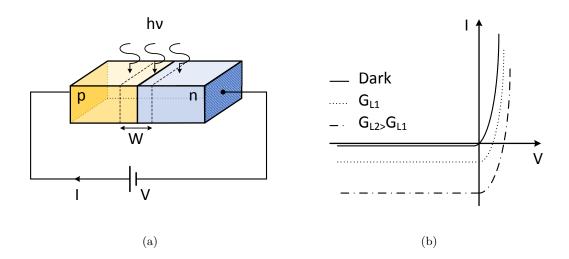

| 1.4 | (a) A $pn$ junction photodiode biased at a DC voltage $V$ . (b) Device current versus applied voltage under different light intensities                                                                                                                                           | 12 |

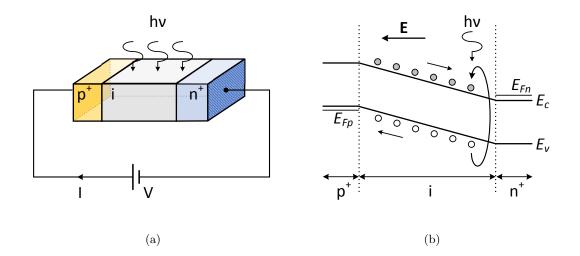

|     |                                                                                                                                                                                                                                                                                   | 14 |

| 1.5 | (a) A <i>pin</i> Photodiode. (b) Energy band diagram of the photodiode; most of the                                                                                                                                                                                               |    |

|     | photons are absorbed in the intrinsic region                                                                                                                                                                                                                                      | 13 |

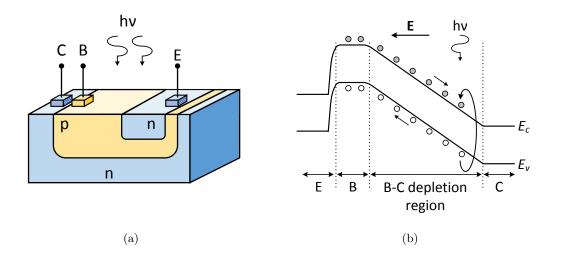

| 1.6 | (a) A bipolar phototransistor. (b) Energy band diagram of the structure; photo-                                                                                                                                                                                                   |    |

|     | generated holes are accumulated in the base region and act as the base signal                                                                                                                                                                                                     | 17 |

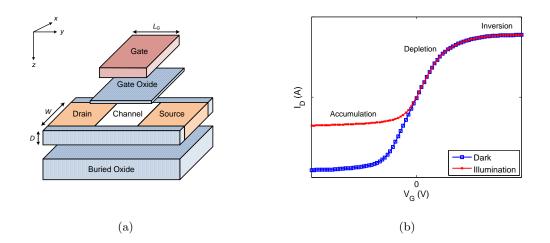

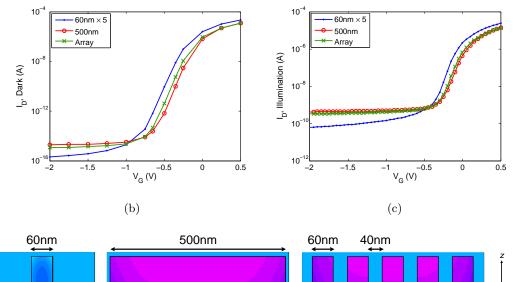

| 2.1 | (a) Block diagram of a SOI MOS phototransistor. The device is $200nm$ thick, and                                                                                                                                                                                                  |    |

|     | source, channel and drain regions are $1\mu m$ long. Source and drain are <i>n</i> -type, with                                                                                                                                                                                    |    |

|     | doping level of $10^{20} cm^{-3}$ . The channel is <i>p</i> -type. (b) An example of drain current                                                                                                                                                                                |    |

|     | as a function of gate voltage, under dark and illumination conditions. $\ldots$                                                                                                                                                                                                   | 24 |

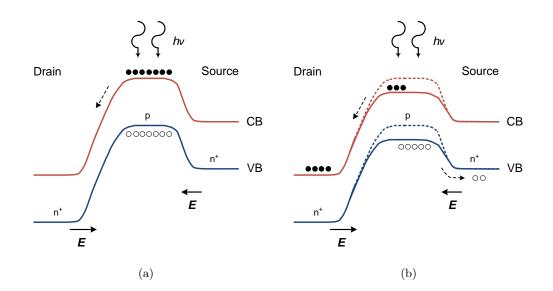

| 2.2 | Lateral bipolar action in SOI MOS phototransistors. Energy band diagram of the                                                                                                                                                                                                    |    |

|     | phototransistor in figure 2.1(a), at a cutline along $y$ direction. (a) Electron-hole                                                                                                                                                                                             |    |

|     | generation after illumination. (b) Barrier lowering due to accumulation of holes in                                                                                                                                                                                               |    |

|     | the channel. $V_G < 0$ and $V_D > 0$                                                                                                                                                                                                                                              | 25 |

|     |                                                                                                                                                                                                                                                                                   |    |

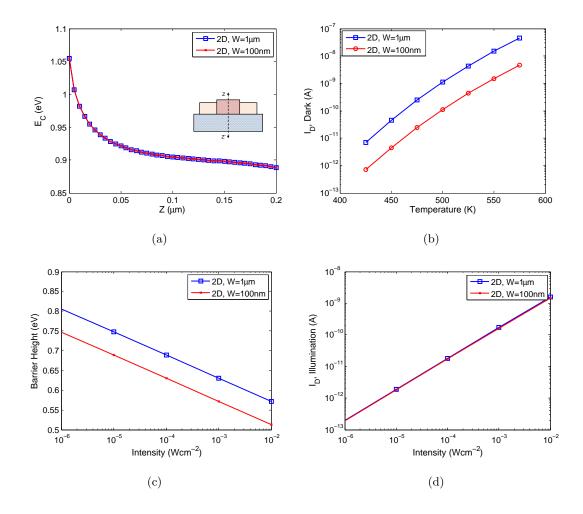

| 2.3 | Two dimensional structures with channel widths of $1\mu m$ and $100nm$ are compared<br>in terms of (a) Conduction band at dark (along cutline ZZ') (b) dark current versus<br>temperature, (c) barrier height and (d) photocurrent as a function of intensity.<br>Device thickness: $200nm$ . Channel doping: $10^{16}cm^{-3}$ , $V_G = -2V$ , $V_D = 0.5V$                                                                                                                                                                                                                                                                                 | 29 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

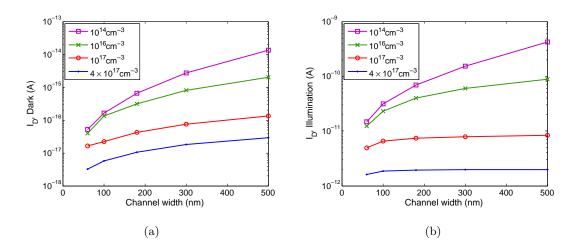

| 2.4 | Room temperature drain current of the phototransistor in figure 2.1(a), as a func-<br>tion of channel width and doping, under (a) Dark, and (b) illumination conditions.<br>$V_G = -2V, V_S = 0V, V_D = 0.5V$ . Light intensity and photon rate are $10^{-4}W/cm^2$<br>and $1.9 \times 10^5 s^{-1}$ , respectively                                                                                                                                                                                                                                                                                                                          | 30 |

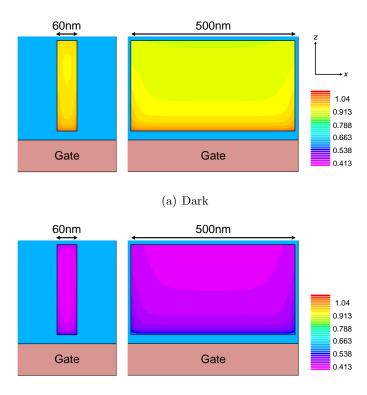

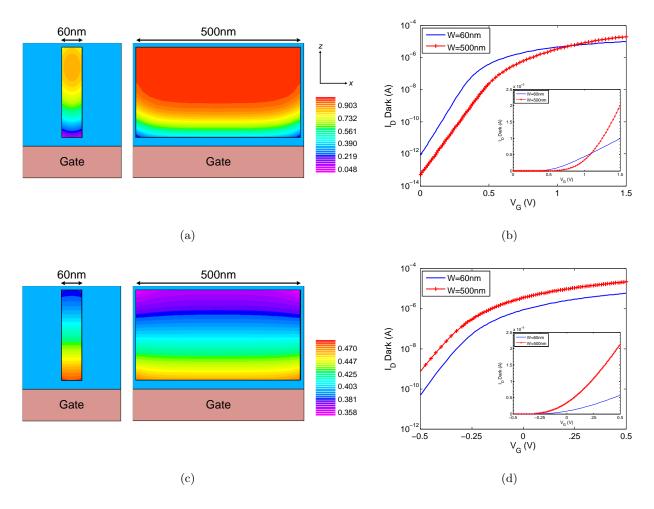

| 2.5 | Conduction band energy contours of two 3D SOI MOS structures (figure 2.1(a)) at (a) dark, and (b) illumination conditions. The channel width is $60nm$ for the structure on the left, and $500nm$ for the structure on the right. The contours are obtained across the channel, $xz$ plane. The channel doping is $10^{16}cm^{-3}$ ; $V_G = -2V$ , $V_S = 0V$ , $V_D = 0.5V$                                                                                                                                                                                                                                                                | 31 |

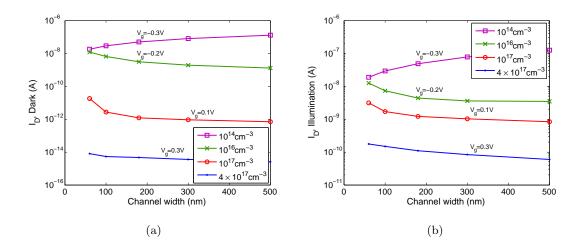

| 2.6 | Room temperature drain current of the phototransistor in figure 2.1(a), as a func-<br>tion of channel width and doping in depletion mode. (a) Dark, and (b) illumination<br>conditions. $V_S = 0V$ , $V_D = 0.5V$ . Light intensity and photon rate are $10^{-4}W/cm^2$<br>and $1.9 \times 10^5 s^{-1}$ , respectively                                                                                                                                                                                                                                                                                                                      | 32 |

| 2.7 | (a) Conduction band energy contours of two SOI MOS structures (figure 2.1(a)), with channel doping of $10^{17}cm^{-3}$ . The gate is biased in depletion mode, at 0.4V. (b) Drain current of the structures in (a) as a function of the gate voltage. Inset shows the current in linear scale. (c) Conduction band energy contours of two SOI MOS structures, with channel doping of $10^{14}cm^{-3}$ . The gate is biased in depletion mode, at $-0.5V$ . (d) Drain current of the structures in (c) as a function of the gate voltage. Inset shows the current in linear scale. The contours are obtained across the channel, $xz$ plane. | 33 |

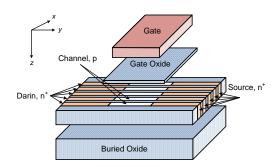

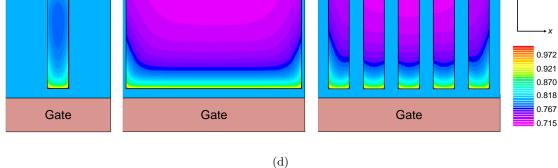

| 2.8 | (a) Photodetector with array of nanowires. The nanowires are $60nm$ wide. The channel is <i>p</i> -type, with doping level of $10^{16}cm^{-3}$ . Other specifications of the device are similar to figure 2.1. Drain current versus the gate voltage of the nanowire array device, under dark (b) and illumination (c). The results are compared with those of a single channel device with channel width of $60nm$ , whose current is multiplied by 5, and also a single channel device whose channel is $500nm$ wide. $V_S = 0V$ , $V_D = 0.5V$ ; the striking photon rate= $9.6 \times 10^5 sec^{-1}$ .(d) Conduction band energy        | 00 |

|     | contours of the structures at dark. $V_G = -2.0V, T = 475K$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 36 |

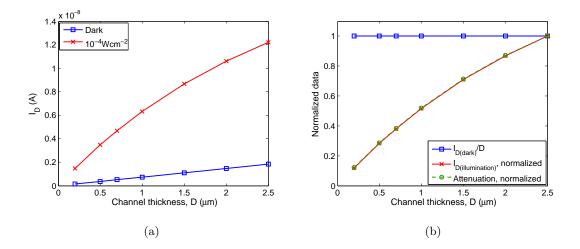

- 2.9 Dependence of the drain current on the semiconductor thickness in a two dimensional lateral bipolar transistor (n<sup>+</sup>pn<sup>+</sup>), with channel width, length and doping of 1µm, 1µm, and 10<sup>16</sup>cm<sup>-3</sup>, respectively. (a) Drain current versus thickness under dark (T = 475K) and illumination. (b) Blue: I<sub>Drain</sub>(D)/D, (D: semiconductor thickness) under dark. Red: the drain current under illumination, normalized to its maximum value at D = 2.5µm. Green: attenuation curve, normalized to its value at D = 2.5µm. V<sub>S</sub> = 0V and V<sub>D</sub> = 0.5V.

37

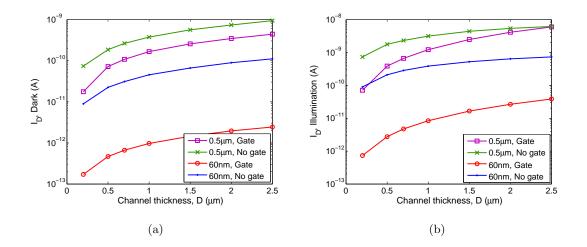

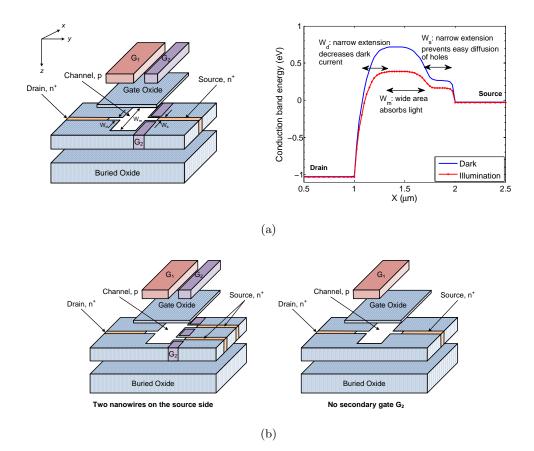

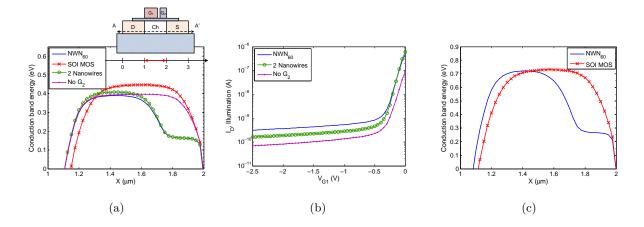

- 2.11 (a) Multiple gate NWN phototransistor, along with its energy band diagram. The widths of the nanowires on the source and drain sides,  $W_s$  and  $W_d$ , are both 60nm.  $W_m = 500nm$ , and the total channel length is  $1\mu m$ . Active region thickness: 200nm. Channel doping:  $10^{16}cm^{-3}$ . (b) Left: NWN photodetector with two nanowires on the source side. Right: NWN photodetector without the secondary gate  $G_2$ . Light is shined through a  $0.5 \times 0.5\mu m^2$  window over the channel. . . . . 41

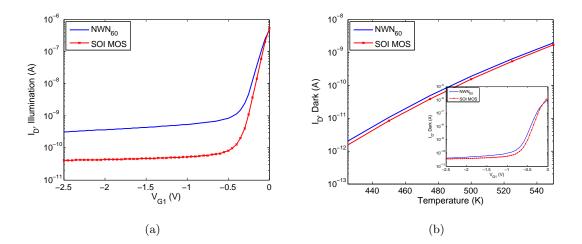

- 2.12 (a) Drain current versus gate voltage of NWN<sub>60</sub> (figure 2.11(a)) and SOI MOS (figure 2.1(a)), under illumination. Light intensity is  $0.01 mW/cm^{-2}$  and light is illuminated through a  $0.25 \mu m^2$  window. (b) Dark current versus temperature for NWN<sub>60</sub> and SOI MOS; inset: Drain current versus  $V_{G1}$  at T = 475K. Channel doping:  $10^{16}cm^{-3}$ .  $V_S = 0V$ ,  $V_D = 1V$ , and  $V_{G2} = 0V$  (where applicable). . . . . . 42

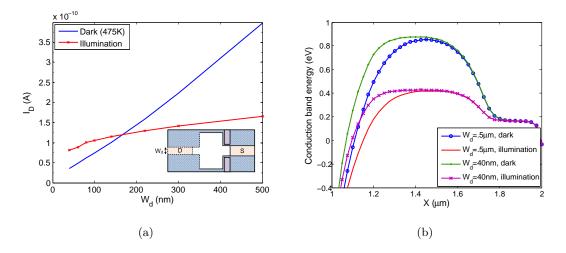

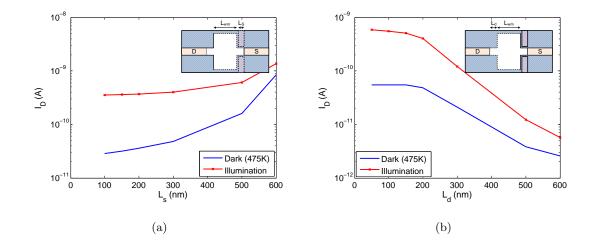

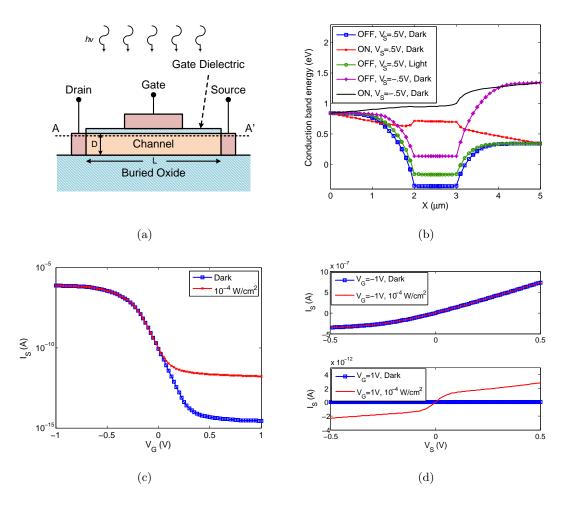

2.14 (a) Drain current versus nanowire width on the source side  $(W_s)$ , while the nanowire width on the drain side is 60nm (NWN structure in figure 2.11(a)). (b) Conduction band energy of two structures with  $W_s$  of 40nm and  $0.5\mu m$ , under dark and illumination. The energy bands are obtained along the channel, at 5nm above the bottom oxide-semiconductor interface. Light intensity= $2.4\mu W/cm^2$  and the number of photons striking the channel per second is kept the same. T = 475K442.15 (a) Drain current versus nanowire width on the drain side  $(W_d)$ , while the nanowire width on the source side is 60nm (NWN structure in figure 2.11(a)). (b) Conduction band energy of two structures with  $W_d$  of 40nm and  $0.5\mu m$ , under dark and illumination. The energy bands are obtained along the channel, at 5nm above the bottom oxide-semiconductor interface. Light intensity= $2.4\mu W/cm^2$  and the number of photons striking the channel per second is kept the same. T = 475K452.16 (a) Drain current versus nanowire length on the source side  $(L_s)$ . The nanowire length on the drain side is 200nm (NWN structure in figure 2.11(a)). (b) Drain current versus nanowire length on the drain side  $(L_d)$ . The nanowire on the source side is 300nm long. The total channel length is  $1\mu m$ , and hence  $L_{wm}$  is varied in each experiment. T = 475K for dark. 473.1(a) Single gate junction-less phototransistor. The semiconductor is p-type silicon with doping level of  $10^{15} cm^{-3}$  and thickness (D) of 350 nm. The width (W) and the length (L) of the channel are  $2\mu m$  and  $5\mu m$ , respectively. The gate covers the central  $1\mu m$  of the channel length, and is located over 20nm silicon dioxide. Light is shined through a window with the area of  $3.6\mu m^2$ . (b) Energy band diagram of the phototransistor, along the channel (cutline AA'). The blue and green curves represent the energy band under positive gate bias and the red curve shows the energy band under negative gate bias  $(V_S = +0.5V)$ . The purple and the black curves show the energy band when  $V_S = -0.5V$ . (c) Source current versus gate voltage, under dark and illumination conditions. (d) Source current versus source 52

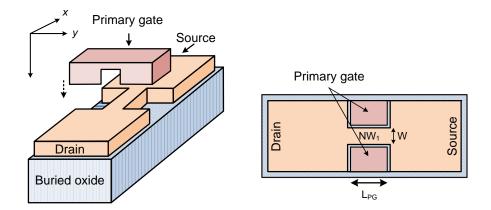

| 3.2 | Single gate, junction-less phototransistor with nanowire channel. The semicon-<br>ductor is <i>p</i> -type silicon with doping level of $10^{15} cm^{-3}$ and thickness of $0.85 \mu m$ .                                                                                                                                                                                                                                                                                                                                     |    |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | The length of the channel is $5\mu m$ . The channel is $2\mu m$ wide everywhere except                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

|     | the $NW_1$ region. The gate covers the central $1\mu m$ of the channel length, and is                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

|     | located over $20nm$ silicon dioxide                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 54 |

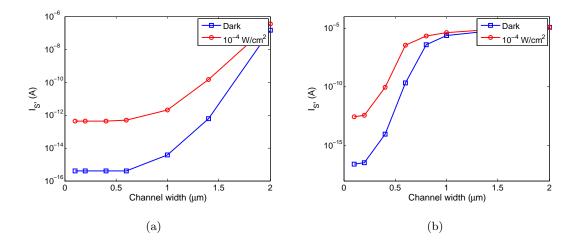

| 3.3 | Source current versus channel width in a single gate, junction-less phototransistor with nanowire channel (figure 3.2) when the semiconductor doping is (a) $10^{15} cm^{-3}$ ,                                                                                                                                                                                                                                                                                                                                               |    |

|     | and (b) $10^{16} cm^{-3}$ . $V_G = 1.0V$ , $V_S = 0.5V$ , $V_D = 0V$                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 55 |

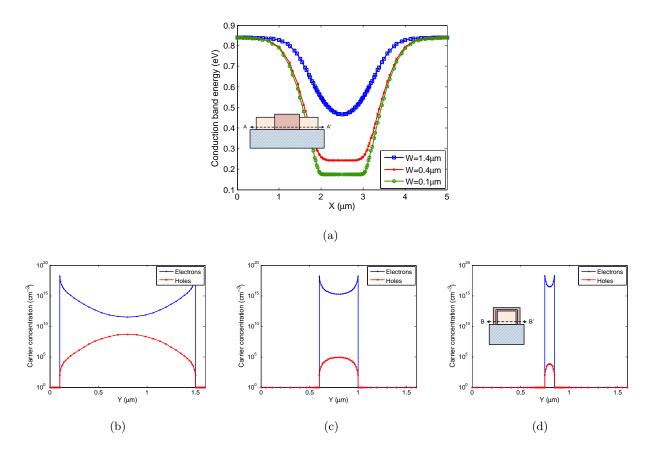

| 3.4 | (a) Energy band diagram of three single gate nanowire phototransistors (figure 3.2) with widths of $600nm$ , $400nm$ and $100nm$ , along the channel (cutline AA').<br>$V_G = 1.0V$ , $V_S = 0V$ , $V_D = 0V$ . (b)-(d) Electron and hole concentration of the                                                                                                                                                                                                                                                                |    |

|     | aforementioned structures at cutline BB' across the channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 56 |

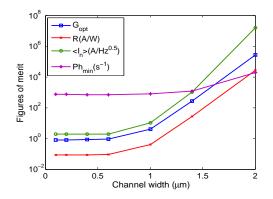

| 3.5 | Figures of merit versus channel width. Similar to figure 3.3(a), the channel thickness is $0.85\mu m$ , and $V_G = 1.0V$ , $V_S = 0.5V$ , $V_D = 0V$ .                                                                                                                                                                                                                                                                                                                                                                        | 57 |

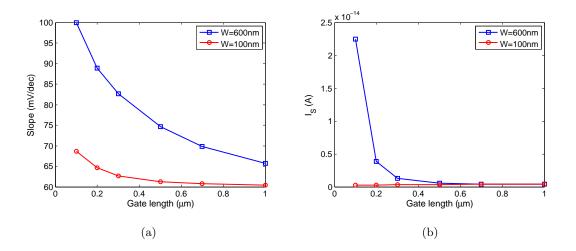

| 3.6 | Single gate phototransistors with nanowire widths of $100nm$ and $600nm$ , role of gate length $L_{PG}$ (figure 3.2). (a) Sub-threshold slope versus gate length. (b) Dark current as a function of gate length. Data is obtained for semiconductor doping of $10^{15}cm^{-3}$ . Dark current data for $100nm$ wide channel is obtained by simulating the device at high temperatures and estimating the room temperature current                                                                                             | 58 |

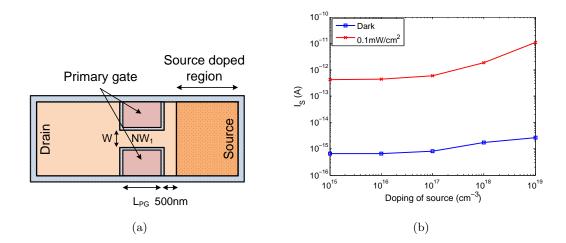

| 3.7 | (a) Top view of the nanowire phototransistor with a higher doping concentration<br>on the source side. (b) Source current versus doping level on the source side. The<br>semiconductor doping is $10^{15} cm^{-3}$ elsewhere ( <i>p</i> -type). Semiconductor thickness is<br>$0.85\mu m$ . $NW_1$ is $200nm$ wide. $L_{PG} = 1\mu m$ , $V_G = 1.0V$ , $V_S = 0.5V$ , $V_D = 0V$                                                                                                                                              | 59 |

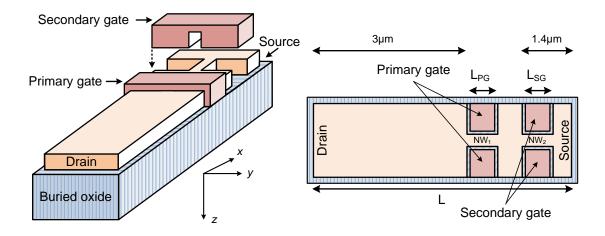

| 3.8 | Junction-less phototransistor with multiple gates. Semiconductor is entirely $p$ -type (doping: $10^{15}cm^{-3}$ ), with the thickness of $0.85\mu m$ . The total channel length is $5\mu m$ . The channel is $2\mu m$ wide everywhere except the narrow regions. The gate oxide is $20nm$ (not shown in figure). The secondary gate is lifted up to show the narrow region $NW_2$ . A similar geometry is present underneath the primary gate that is shown in the top view, where the gates' top layer is removed. Light is |    |

|     | shined through a window with the area of $5.6\mu m^2$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 61 |

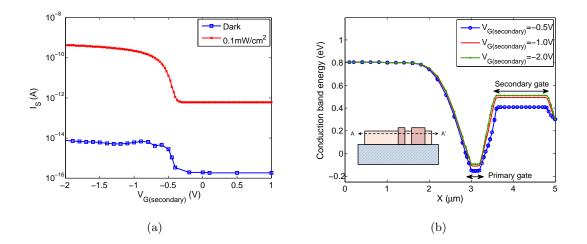

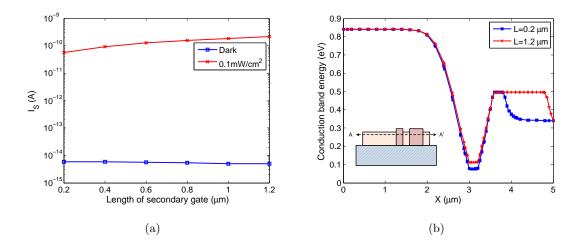

| 3.9  | (a) Source current versus the secondary gate bias in the multiple gate, junction-                      |          |

|------|--------------------------------------------------------------------------------------------------------|----------|

|      | less phototransistor (figure 3.8). The primary gate is $200nm$ long and covers a                       |          |

|      | $200nm$ wide channel $(NW_1)$ . The secondary gate is $1.2\mu m$ long, and covers a                    |          |

|      | $20nm$ wide region $(NW_2)$ . (b) Impact of the secondary gate bias on conduction                      |          |

|      | band energy of the structure along the channel (cutline AA'). Device thickness is                      |          |

|      | $0.85\mu m, V_{G(primary)} = 1.0V, V_S = 0.5V, V_D = 0V.$                                              | 62       |

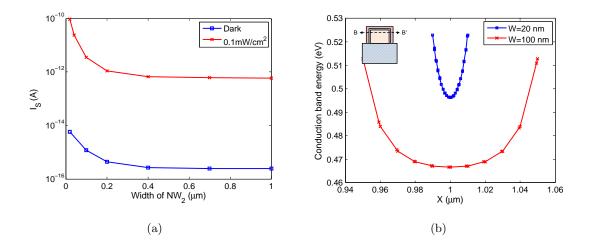

| 3.10 | (a) Source current versus width of $NW_2$ , in the multiple gate junction-less pho-                    |          |

|      | to<br>transistor of figure 3.8. The primary gate is $200nm$ long and covers a<br>200nm                 |          |

|      | wide nanowire $(NW_1)$ . The secondary gate is 400nm long. $V_{G(primary)} = 1.0V$ ,                   |          |

|      | $V_S = 0.5V, V_D = 0V, V_{G(secondary)} = -1.0V.$ (b) Conduction band energy, across                   |          |

|      | the source area (cutline BB')                                                                          | 63       |

| 3.11 | (a) Source current versus nanowire length underneath the secondary gate (figure                        |          |

|      | 3.8). (b) Conduction band energy, along the channel for different lengths of the                       |          |

|      | secondary gate and $NW_2$ . For both cases the primary gate is $200nm$ long and                        |          |

|      | covers a $200nm$ wide nanowire $(NW_1)$ , and the secondary gate covers a $20nm$ wide                  |          |

|      | channel (NW <sub>2</sub> ). $V_{G(primary)} = 1.0V, V_{G(secondary)} = -1V, V_S = 0.5V, V_D = 0V.$ .   | 64       |

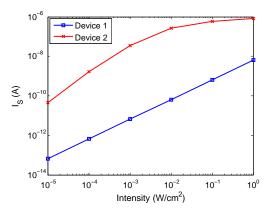

| 3.12 | Source current versus light intensity in two multiple gate structures (rows 1 and 5                    |          |

|      | of table 3.1). In both structures, $NW_1$ is $200nm$ wide and is covered by a 200nm                    |          |

|      | long primary gate. In Device 1, the secondary gate is biased at $-1V$ ; the secondary                  |          |

|      | gate is $400nm$ long and covers a $400nm$ wide $NW_2$ . In Device 2, the secondary gate                |          |

|      | is $1.2\mu m$ long and is biased at $-2V$ . The width and thickness of $NW_2$ are $20nm$               |          |

|      | and 50nm, respectively. Semiconductor thickness is $0.85\mu m$ , except for $NW_2$ in                  |          |

|      | Device 2                                                                                               | 67       |

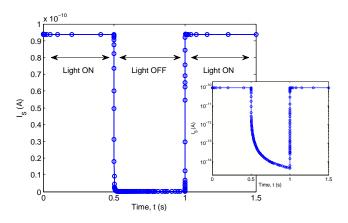

| 3.13 | Transient response of a junction-less, multiple gate phototransistor, that corre-                      |          |

|      | sponds to the second row of table 3.2. The width of $NW_1$ and $NW_2$ is $200nm$                       |          |

|      | and $20nm$ , respectively. The inset shows the same data in logarithmic scale.                         |          |

|      | $V_{G(primary)} = 1.0V, V_{G(secondary)} = -1.0V, V_S = 0.5V, V_D = 0V$ , Intensity= $10^{-4}W/c^{-1}$ | $cm^2$ . |

|      |                                                                                                        |          |

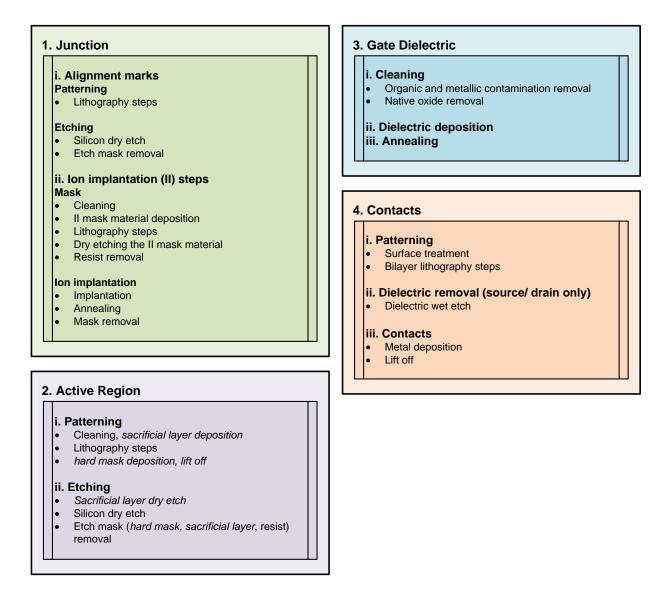

| 4.1  | Four major steps of device fabrication. In the second block (Active Region), two                       |          |

|      | fabrication approaches are followed; and that is why some of the steps are written                     |          |

|      | in <i>italic</i>                                                                                       | 71       |

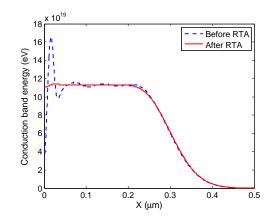

| 4.2  | Modeling results of the ion implantation profile. The target material is $p$ -type                     |          |

|      | silicon, with background doping level of $10^{15} cm^{-3}$ . The implants are phosphorous              |          |

|      | ions, whose dose and energy are listed in table 4.1                                                    | 73       |

|      |                                                                                                        |          |

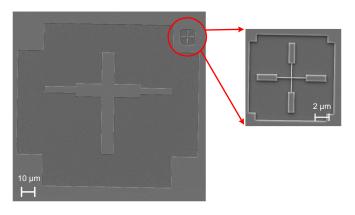

| 4.3  | Alignment marks, in the form of ridges fabricated on the wafer by electron beam<br>lithography and dry etching the silicon. The large alignment marks are used for                                                                                                                                                                                                                                                                                                            |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | optical lithography, while the small ones (magnified in the inset) are used for                                                                                                                                                                                                                                                                                                                                                                                               |    |

|      | electron beam lithography                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 74 |

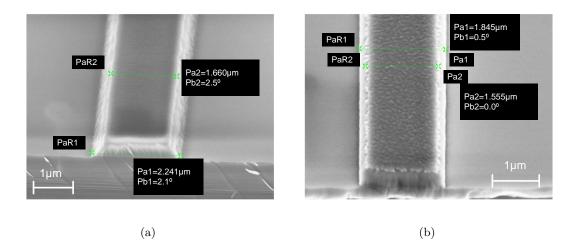

| 4.4  | Profile of the $SiO_2$ layer after dry etching, (a) when the etch mask is photoresist,<br>and (b) when the etch mask is aluminum                                                                                                                                                                                                                                                                                                                                              | 76 |

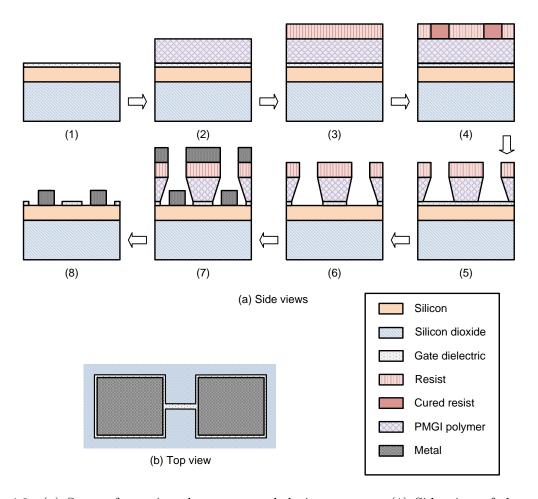

| 4.5  | <ul> <li>(a) Fabrication of the active region. (1) Side view of the sample (the top silicon and the buried oxide layers are shown). (2) Silicon nitride is deposited. (3) Resist is spun. (4) Resist is exposed to the electron beam. (5) Side view after development.</li> <li>(6) Metal is deposited. (7) Side view after lift-off. (8) Side view after etching. (b) Top view of the active region after the metal mask and the silicon nitride layer are removed</li></ul> | 77 |

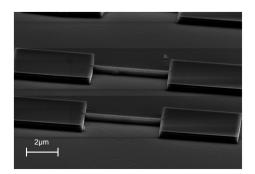

| 4.6  | Etch profile of a sample, after the $SiN_x$ and $Si$ layers are etched. The Al mask is                                                                                                                                                                                                                                                                                                                                                                                        | •• |

| 1.0  | still on top of the $SiN_x$ layer. The thickness of silicon layer is $350nm$                                                                                                                                                                                                                                                                                                                                                                                                  | 80 |

| 4.7  | Top view of (parts of) the active region, (a) before, and (b) after Al mask and                                                                                                                                                                                                                                                                                                                                                                                               |    |

|      | $SiN_x$ removal                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 80 |

| 4.8  | <ul><li>Fabrication of the active region, when the electron beam resist is used as a mask for dry etching. (1) Side view of the sample (the top silicon and the buried oxide layers are shown). (2) Resist is spun. (3) Resist is exposed to the electron beam.</li><li>(4) Side view after development. (5) Side view after etching</li></ul>                                                                                                                                | 81 |

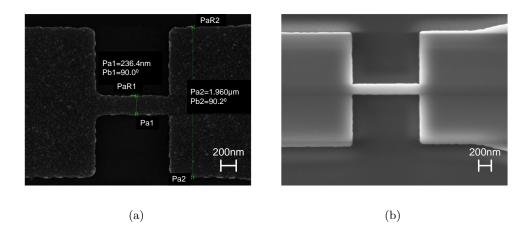

| 4.9  | <ul> <li>(a) Steps of creating the source and drain contacts. (1) Side view of the sample. (2)</li> <li>PMGI polymer is spun. (3) PMMA resist is spun. (4) PMMA is cured by electron</li> <li>beam lithography. (5) Side view after development. (6) Dielectric is etched. (7)</li> <li>Metal is deposited. (8) Side view after lift-off. (b) Top view after lift-off. Creating</li> <li>the gate involves similar steps, except step 6 which is skipped</li></ul>            | 84 |

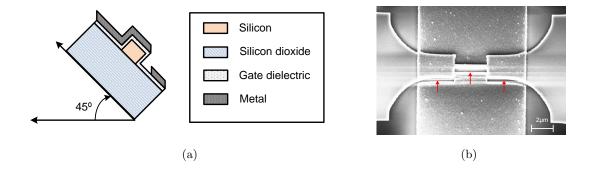

| 4.10 | (a) Mounting the sample on a $45^{\circ}$ angle during metal deposition for gate. The bilayer resist is not shown. (b) SEM image of a gate contact that is deposited                                                                                                                                                                                                                                                                                                          |    |

|      | using the $45^{\circ}$ mount. The arrows show the areas that are not covered with metal                                                                                                                                                                                                                                                                                                                                                                                       | 85 |

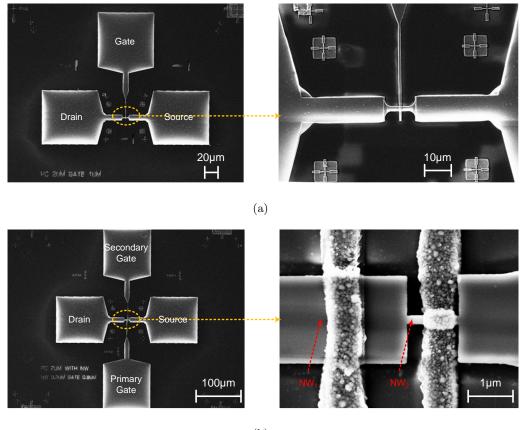

| 4.11 | SEM graph of a fabricated (a) single gate and (b) multiple gate device (correspond-<br>ing to figure 3.8)                                                                                                                                                                                                                                                                                                                                                                     | 87 |

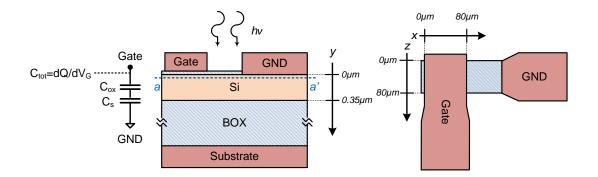

| 5.1  | Side and top views of the MOS capacitor. The silicon layer is <i>p</i> -type, with doping concentration of $10^{15} cm^{-3}$ .                                                                                                                                                                                                                                                                                                                                                | 90 |

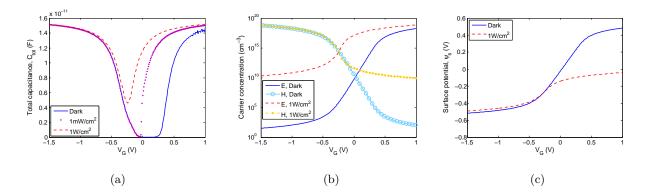

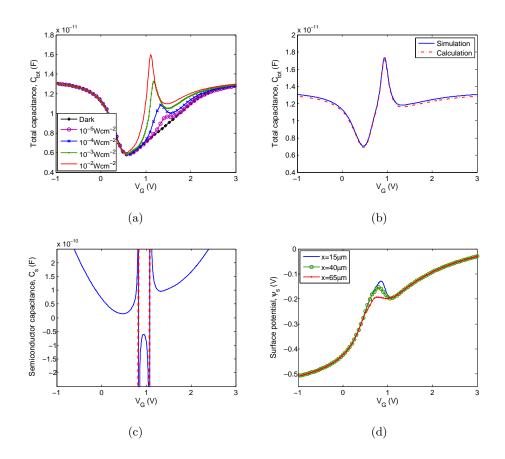

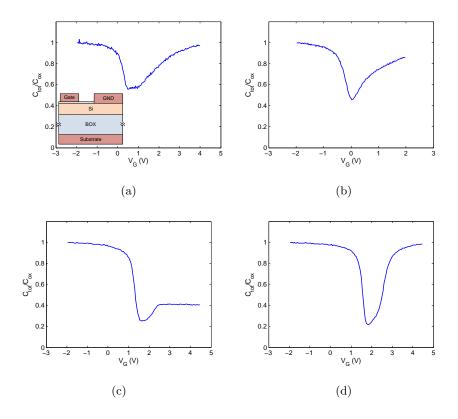

| 5.2        | (a) Quasi-static capacitance-voltage (QSCV) curves of the MOS capacitor in fig-<br>ure 5.1, under dark and illumination conditions. (b) Electron (E) and hole (H)<br>concentration versus gate voltage at $(x, y) = (40 \mu m, 1 \text{\AA})$ . (c) Surface potential as                                                                                                                                                                                                                   |     |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|            | a function of gate bias, at $(x, y) = (40 \mu m, 0)$ .                                                                                                                                                                                                                                                                                                                                                                                                                                     | 91  |

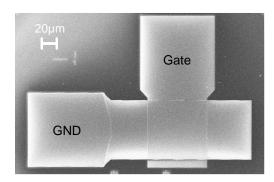

| 5.3<br>5.4 | SEM image of the fabricated MOS capacitor                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 95  |

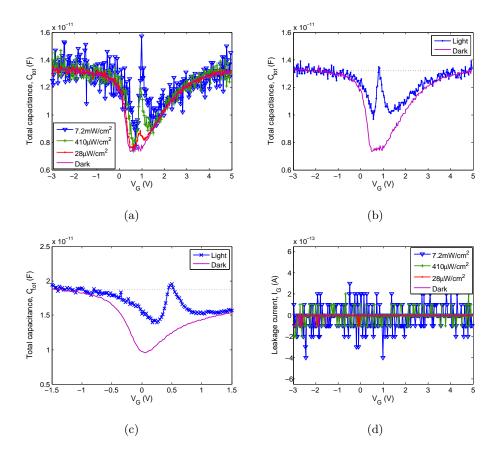

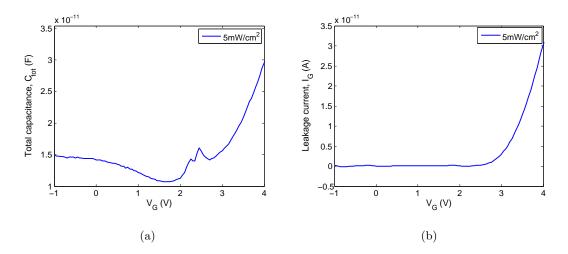

| 5.5        | gate voltage for the device in (a)                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 96  |

|            | current versus gate voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 97  |

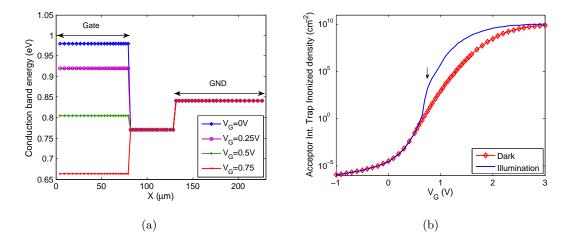

| 5.6        | Results from modeling and calculations (capacitor dimensions are presented in figure 5.1). (a) The capacitance versus voltage for different light intensities calculated using the drift-diffusion framework. (b) The solid line is the capacitance corresponding to the intensity of $1Wcm^{-2}$ ; the dashed line is obtained from the surface potential data using equation 5.13. (c) Semiconductor capacitance, $C_s$ . (d) Surface potential at different points underneath the gate. | 100 |

| 5.7        | (a) Conduction band energy, along the channel below the gate dielectric. (b) Density of the occupied trap states. Capacitor dimensions are presented in figure 5.1. The plots are obtained at $(x, y) = (30 \mu m, 0.1 \text{\AA})$ .                                                                                                                                                                                                                                                      | 101 |

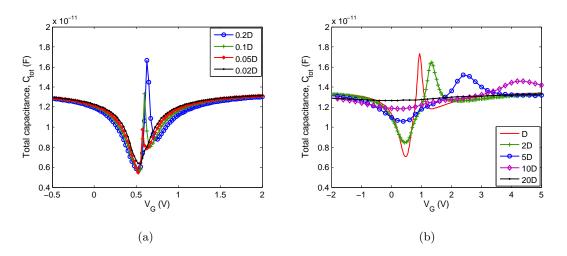

| 5.8        | Impact of interface trap density on the photon induced capacitance peak. CV curve versus gate bias, when the trap densities are (a) smaller and (b) larger than the original trap density shown in table 5.1. Capacitor dimensions are presented in figure 5.1.                                                                                                                                                                                                                            |     |

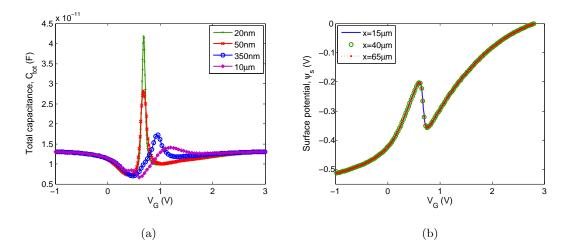

| 5.9        | (a) Impact of the thickness of the silicon layer on the capacitance peak. (b) Surface potential at different points underneath the gate, for a MOS capacitor with silicon thickness of 20nm.                                                                                                                                                                                                                                                                                               |     |

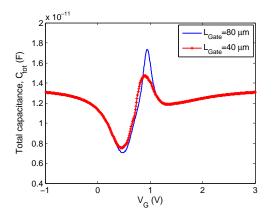

| 5.10       | Impact of the gate length on the capacitance peak. In both capacitors the area is $6.4 \times 10^3 \mu m^2$ . Silicon thickness is $350nm$ .                                                                                                                                                                                                                                                                                                                                               | 104 |

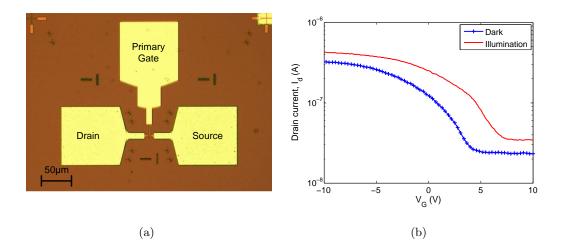

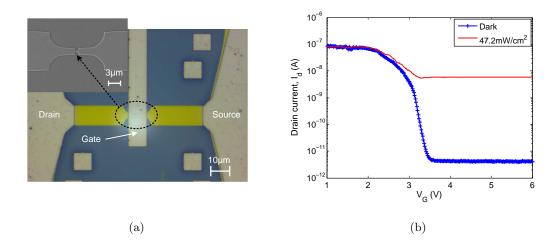

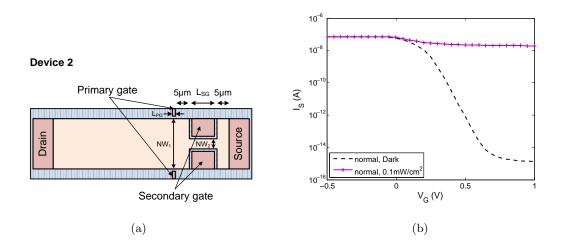

- 6.2 A fabricated single gate, junction-less photodetector with a nanowire channel. (b) Drain current as a function of gate bias, under dark and illumination. Channel width: 200nm. Total channel length:  $17\mu m$ . Nanowire length:  $1.2\mu m$ . Semiconductor thickness: 350nm.  $V_S = 0V$ ,  $V_D = 1V$ . Light intensity is not recorded. . . . 107

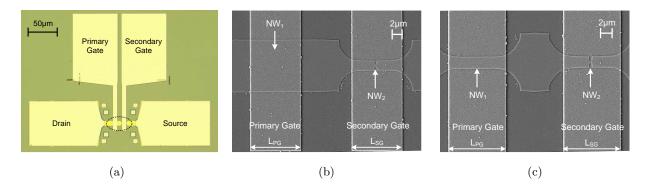

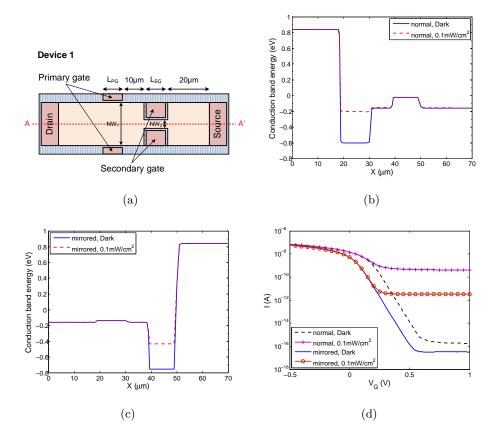

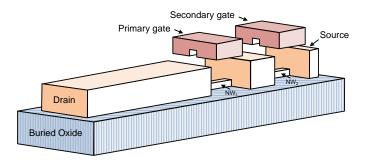

- 6.5 (a) Junction-less phototransistor with multiple gates. (b) SEM image of the device channel (inside the black oval in (a)), showing NW<sub>1</sub> (10μm wide) and NW<sub>2</sub> (200nm wide). (c) SEM image of the channel, showing NW<sub>1</sub> (2μm wide) and NW<sub>2</sub> (200nm wide). Device thickness is 35nm. The gate lengths L<sub>PG</sub> and L<sub>SG</sub> are both 10μm. 111

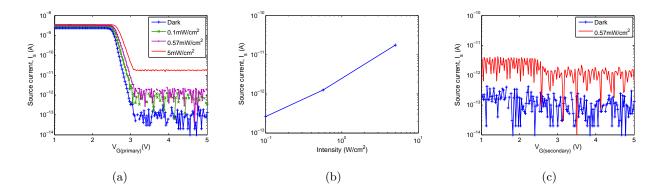

- 6.7 Current versus the primary gate bias for devices with (a)  $NW_1$ :  $10\mu m$  wide and  $NW_2$ :  $2\mu m$  wide, and (b)  $NW_1$ :  $10\mu m$  wide and  $NW_2$ : 200nm wide. Other dimensions are similar to figure 6.5.  $V_D = 0V$ ,  $V_S = 1V$ ,  $V_{G(secondary)} = -3V$ , and  $\lambda = 405nm$ .

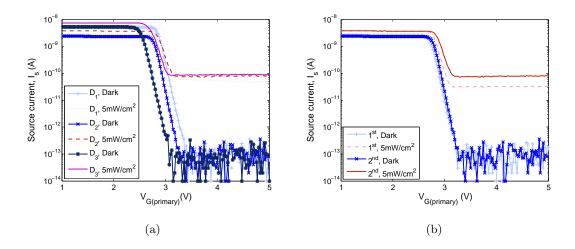

- 6.8 (a) Current versus the primary gate bias for three devices (labeled  $D_1$ ,  $D_2$  and  $D_3$ ) with similar size and geometry. (b) Two measurements of a single device  $(D_2)$ . The width of  $NW_1$  and  $NW_2$  is  $10\mu m$  and 200nm, respectively. Other dimensions are similar to figure 6.5.  $V_D = 0V$ ,  $V_S = 1V$ , and  $V_{G(secondary)} = -3V$ .  $\lambda = 405nm$ . 114

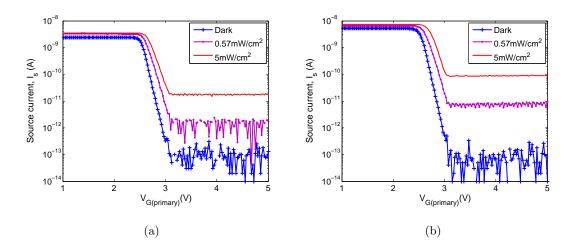

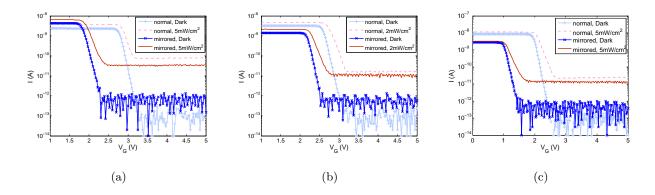

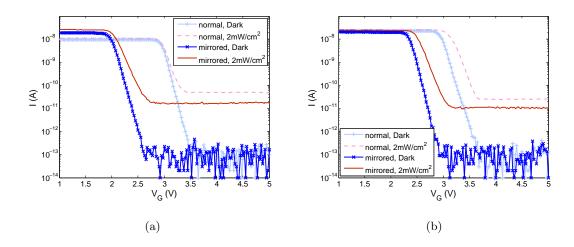

- 6.9 Normal measurement: change of the current (at source contact) as a function of primary gate bias, under dark and illumination. V<sub>D</sub> = 0V, V<sub>S</sub> = 1V, and V<sub>G(secondary)</sub> = -3V. Mirrored measurement: change of the current (at drain contact) as a function of secondary gate bias (acting as primary gate), under dark and illumination. V<sub>D</sub> = 1V, V<sub>S</sub> = 0V, and V<sub>G(primary)</sub> = -3V. (a) NW<sub>1</sub> width=10µm, NW<sub>2</sub> width=200nm. (b) NW<sub>1</sub> width=10µm, NW<sub>2</sub> width=2µm. (c) NW<sub>1</sub> width=2µm, NW<sub>2</sub> width=200nm. Other dimensions are similar to figure 6.5. λ = 405nm.

- 7.1 Junction-less phototransistor with multiple gates, and nanowires that bridge the thick sections of active region. The gates are lifted up to show  $NW_1$  and  $NW_2$ . . . 125

# List of Abbreviations

| ALD                 | Atomic Layer Deposition                      |

|---------------------|----------------------------------------------|

| APD                 | Avalanche Photodiode                         |

| APS                 | Active Pixel Sensor                          |

| BOX                 | Buried Oxide                                 |

| BHF                 | Buffered Hydrofluoric acid                   |

| CCD                 | Charge Coupled Device                        |

| CMOS                | Complementary Metal Oxide Semiconductor      |

| CNT                 | Carbon Nanotube                              |

| CT                  | Computerized Tomography                      |

| DUT                 | Device Under Test                            |

| $\mathbf{FF}$       | Fill Factor                                  |

| FPN                 | Fixed Pattern Noise                          |

| GND                 | Ground                                       |

| HBT                 | Heterojunction Bipolar Transistor            |

| $\operatorname{HF}$ | Hydrofluoric acid                            |

| HMDS                | hexamethyldisilazane                         |

| $I^2E$              | Impact Ionization Engineering                |

| ICPRIE              | Inductively Coupled Plasma Reactive Ion Etch |

| IPA                 | IsoPropyl Alcohol                            |

| MIBK                | Methyl IsoButyl Ketone                       |

| MIS                 | Metal Insulator Semiconductor                |

| MOS                 | Metal Oxide Semiconductor                    |

| MRI                 | Magnetic Resonance Imaging                   |

| NEP                 | Noise Equivalent Power                       |

| PMGI                | Polymethylglutarimide                        |

| PMMA                | Poly(methyl methacrylate)                    |

| PMT                 | Photomultiplier                              |

|                     |                                              |

| PECVD | Plasma Enhanced Chemical Vapor Deposition |

|-------|-------------------------------------------|

| PPS   | Passive Pixel Sensor                      |

| QSCV  | Quasi-Static Capacitance-Voltage          |

| RF    | Radio Frequency                           |

| RTA   | Rapid Thermal Annealing                   |

| SC-1  | Standard Clean 1                          |

| SC-2  | Standard Clean 2                          |

| SEM   | Scanning Electron Microscope              |

| SMU   | Source Monitor Unit                       |

| SOI   | Silicon on Insulator                      |

| SOS   | Silicon on Sapphire                       |

| SRH   | Shockley Read Hall                        |

## Chapter 1

# Introduction

Photodetectors are abundantly found in scientific and industrial instrumentations, consumer products, and even household appliances. Different members of this family detect a wide frequency range from Terahertz and far infrared up to gamma rays, and operate at different speeds [1]. Automatic door openers and household remote controls for example, are rather slow and less sensitive detectors that normally work in the infrared and microwave range [2–4]. Optical communication sensors on the other hand, require extremely fast and highly sensitive detectors to receive a large capacity of information in infrared spectrum (wavelength:  $1.3\mu$ m and  $1.55\mu$ m) [5–8]. In the field of astronomy the wavelength range is quite vast, from sub-millimetre far infrared up to very high energy X- and gamma rays; and also in some cases, the device must be capable of detecting a single photon. This wide frequency range requires different types of detectors [9–12]. Process controls in factories need detectors in the range of either infrared or UV, based on the type of application. They might be used in a simple position sensor or an intensity meter, or a more complicated imaging system. Photodetectors are also being widely used in television and cable broadcasting systems and digital cameras, as well as in biomedicine and military applications [1,13–15].

Photoelectric emission and photon absorption in semiconductors are both quantum events. Both require a minimum level of photon energy which depends on the band-structure of the material, as well as the type of absorption (inter- or intra- band) [16]. During photoelectric emission, that takes place in vacuum photodiodes and photomultipliers (PMT), the absorbed light in a metal excites the electrons and gives them enough energy to overcome the surface barrier potential and escape from the metal surface. The emitted electrons in photomultipliers are then accelerated by a series of electrodes to create secondary electrons [16]. This gives PMTs the ability of detecting very weak signals. In fact, some PMTs are able to detect a single photon. They are however expensive and usually bulky devices that require very high voltages (in the range of kV) [17]. Even the most recent fingertip size device, known as  $\mu$ PMT, operates at 900V [18].

In semiconductors, on the other hand, the absorbed photon can give enough energy to an electron to jump from the valance band into the conduction band. The photo-generated electronhole pairs would in turn change other properties of the semiconductor, such as its conductivity, which can be observed in the device output terminals by measuring the output current or voltage [1, 16].

Research on enhancing the performance of photodetectors is still in progress. Designing photodetectors that consume less power, or operate faster, or improving photodetector designs to detect lower light intensities are examples of the research areas. Exploring the use of nano-structures such as carbon nanotubes (CNT), silicon and germanium nanowires is also actively pursued by different groups around the world [19–21]

This chapter is devoted to the introductory review of semiconductor based photon detectors and details about their operation. First we explain the concept of inter-band photon absorption in semiconductors and then briefly introduce the important sources of noise and figures of merit in such devices to facilitate comparing different structures together. Next, the two mainstream technologies of imaging industry, Charge Coupled Devices (CCD) and Complementary Metal Oxide Semiconductor (CMOS) devices, are introduced and their advantages and disadvantages are discussed. Finally, a selected family of photodetectors, specifically those with nanowires within their geometry, are explained and different aspects of their performance are discussed and compared together.

### 1.1 Absorption of Light

Part of the light that strikes a semiconductor is reflected due to the difference in the refractive indices of the air and the semiconductor material. The penetrating part excites the atoms and creates electron-hole pairs inside the semiconductor, provided that the light wavelength is larger than the semiconductor bandgap. It is possible to obtain the optical power of the incident light at a depth x inside the semiconductor, by solving the decaying equation described by Beer-Lambert Law  $\frac{d}{dx}P_{opt}(x) = \alpha P_{opt}(x)$ , where  $P_{opt}(x)$  is the optical power at position x, and  $\alpha$  is the material absorption coefficient [1]. The solution is exponential, as shown below. The surface reflection R is also included, and  $P_{in}$  denotes the optical power at the interface x=0.

$$P_{opt}(x) = (1-R)P_{in}e^{(-\alpha x)} \qquad (unit:W)$$

$$(1.1)$$

The photo-generation rate  $G_L(x)$  (unit:  $(cm^3s)^{-1}$ ) is then obtained by derivation of the optical power.

$$G_L(x) = \frac{-1}{Ah\nu} \frac{d}{dx} P_{opt}(x) = (1 - R) \frac{P_{in}}{A} \frac{1}{h\nu} \alpha e^{(-\alpha x)}$$

(1.2)

In equation 1.2, A is the total area that light is shining through; and h and  $\nu$  are the Planck constant and the frequency of the light, respectively [1]. Please note that  $P_{opt}(x)$  is substituted from equation 1.1. Assuming the semiconductor thickness is D, one can calculate the average of the photo-generation rate,  $\bar{G}_L$ .

$$\bar{G}_L = (1 - R)(1 - e^{-\alpha D})\frac{P_{in}}{AD}\frac{1}{h\nu}$$

(1.3)

Equations 1.2 and 1.3 both put a limit on the semiconductor thickness. The exponential term suggests that in order to convert most of the photons into carriers, the thickness of the absorbing layer must be at least greater than  $\alpha^{-1}$ . The absorption coefficient  $\alpha$  strongly depends on semiconductor bandgap energy, bandgap type (direct or indirect), wavelength of the incident light, and also the symmetry of the electronic states at conduction and valance bands.

### **1.2** Noise in Photodetectors

Noise is a randomly varying signal observed at the output of all electrical circuits, regardless of the existence of any signal at the input. In a photodetector, it affects the device performance by limiting the weakest source of radiation that can be detected. This detection limit is specified by a figure of merit called detectivity (defined later in this chapter). Noise originates from the optical source, the photodetector itself, or even the circuit which later amplifies the electric signal [1]. Assuming that  $I_n(t)$  is the random process representing the noise current as a function of time t, the noise power can be defined as [22].

$$\langle I_n^2 \rangle = \lim_{T \to \infty} \int_{-T}^{T} I_n^2(t) dt \qquad (unit: A^2)$$

$$(1.4)$$

#### Shot Noise

This type of noise originates from the discrete nature of photons and carriers that generate the current in a device. As the time passes, photons impinge the detector in a random manner rather than at uniformly spaced time intervals. Similarly, the number of carriers passing through the device electrodes fluctuates over the time, and as a result of this randomness, the device current shows some fluctuations. The shot noise can be calculated as [1]

$$\langle I_{sh}^2 \rangle = 2qIB \tag{1.5}$$

where q is the electron charge and I is the average current passing through the device; and B represents the frequency bandwidth of operation, which is normally determined by the receiver bandwidth.

#### Generation-Recombination Noise

The rate of carrier generation, either thermal or optical, and also the rate of carrier recombination are both random processes, resulting in fluctuations in carrier concentration. The noise that originates from thermal generation depends on the material bandgap; for bandgaps close to  $k_BT$ ( $k_B$ : Boltzmann constant, T: temperature) the generation-recombination noise can be quite large, unless the device is used at low temperatures [16]. Generation-Recombination noise is the main noise source in photoconductors. The noise power within the frequency range f to  $f + \Delta f$  can be calculated as [16]

$$\langle I_{GR}^2 \rangle = \frac{4qIG}{1 + (2\pi f\tau_c)^2} \Delta f \tag{1.6}$$

In equation 1.6, I denotes the total current; and  $\tau_c$  and G are the minority carrier lifetime and the photoconductor gain, respectively. The expression shows that noise is almost frequency independent at low frequencies when  $f \ll (2\pi\tau_c)^{-1}$ ; otherwise it decreases with frequency.

#### Thermal (Johnson) Noise

This type of noise originates from the random velocity of electrons in a resistor. The random motion of electrons creates small fluctuations in the potential (and therefore the current) of the resistor, that is present even when no external voltage is applied. At the frequency bandwidth B smaller than  $\frac{k_BT}{h}$  (h is the Planck constant), thermal noise can be written as [16]

$$\langle I_T^2 \rangle = \frac{4k_B T B}{R} \tag{1.7}$$

where R is the resistance. As revealed from its name, thermal noise increases at higher temperatures due to the increased random motion of electrons.

#### Flicker (1/f) Noise

Flicker noise is not very well understood. It is believed that this noise is due to the random distributions of the traps in semiconductors. The power spectrum of flicker noise shows an inverse dependency on frequency [16]. At higher frequencies this noise is much lower than thermal noise and can be ignored. The flicker noise power is [23]:

$$\langle I_{(1/f)}^2 \rangle = \frac{K I_B^{\alpha} B}{f^{\beta}} \tag{1.8}$$

In equation 1.8, K is a constant; and  $I_B$  and f are the bias current and the operating frequency, respectively. The two other parameters,  $\alpha$  and  $\beta$  depend on device characteristics [23].

The overall noise in a linear system is the sum of the noise sources. Assuming the noise sources are uncorrelated, then the overall noise power, or  $\langle I_n^2 \rangle$ , is simply a summation over the noise powers [22].

$$< I_n^2 > = < I_{sh}^2 > + < I_{GR}^2 > + < I_T^2 > + < I_{(1/f)}^2 >$$

(1.9)

### **1.3** Figures of Merit in Photodetectors

Figures of merit, the quantities that help to characterize the performance of a device, allow us to compare different photodetectors together. Some of the most important figures of merit of photodetectors are introduced in this section.

#### Responsivity (R)

The responsivity of a photodetector is defined as the ratio of the photocurrent  $I_{ph}$ , to the optical power.

$$R = \frac{I_{ph}}{AP} \qquad (unit:AW^{-1}) \tag{1.10}$$

The photocurrent  $I_{ph}$  is generated by a light source with intensity of  $P(Wcm^{-2})$  that is shined through a window with area A (The optical power  $P_{opt} = PA$ ) [1].

#### External Quantum Efficiency $(\eta_e)$

This parameter determines the number of collected carriers per each incident photon. Quantum efficiency,  $\eta_e$ , is defined

$$\eta_e = \frac{\frac{I_{ph}}{q}}{\frac{P_{opt}}{h\nu}} = R \frac{h\nu}{q} \qquad (unit:1)$$

(1.11)

In equation 1.11, q is the electron charge, R is the responsivity, and  $h\nu$  denotes the photon energy [1].

#### Noise Equivalent Power (NEP) and Detectivity

NEP determines the minimum incident power that the device is able to detect. It is defined as the power of the optical signal that creates a signal to noise ratio of 1 at the detector output [23]. The signal power  $P_{opt}$  can be described as the photocurrent divided by responsivity (equation 1.10). Substituting the photocurrent with the root mean square (r.m.s) of the noise or  $\langle I_n^2 \rangle^{0.5}$ , based on definition of NEP, one finds [1,23]

$$NEP = \frac{\langle I_n^2 \rangle^{0.5}}{R} \qquad (unit:W) \tag{1.12}$$

The inverse of NEP is called detectivity (unit:  $W^{-1}$ ) which in fact shows the device ability in detecting small optical signals [1].

### 1.4 Imagers: CCD versus CMOS

Photodetectors are widely used in digital imaging devices. Imagers are found in a variety of applications including wireless handheld devices, scanners and fax machines, biometrics and medical devices as well as industrial, security and household cameras. There are two leading technologies in manufacturing image sensors: Charge Coupled Device (CCD) and Complementary Metal Oxide Semiconductor (CMOS) technologies; and although both of them were introduced almost at the same time in the late 60s and early 70s, CCDs won the competition for years, mostly due to the limitations of lithographic techniques required for fabricating CMOS based sensors [14, 24].

In a typical CCD or CMOS imager, photons are first collected by a lens and then passed through filters for wavelength discrimination. Next, a detector converts the absorbed photons to

Figure 1.1: Block diagram of (a) a CCD imager; and (b) a CMOS imager [14].

electrons; the electrons are later read, amplified and converted to a digital signal. Other circuit blocks are used for timing, signal processing and controlling the system [25].