# Cell Placement Using Constructive and Iterative Improvement Methods

by

Andrew Kennings

A thesis

presented to the University of Waterloo in fulfilment of the thesis requirement for the degree of Doctor of Philosophy

in

**Electrical Engineering**

Waterloo, Ontario, Canada, 1997

©Andrew Kennings 1997

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre rélérence

Our file Notre rélérence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced with the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette thèse à la disposition des personnes intéressées.

L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-21359-5

# Canadä

The University of Waterloo requires the signatures of all persons using or photocopying this thesis. Please sign below, and give address and date.

.

## Abstract

Modern integrated circuits contain thousands of switching cells making their design an overwhelming task. The design procedure is therefore divided into sequence of design steps. Circuit layout is the design step in which a physical realization of a circuit is obtained from its functional description. Placement is one subproblem of circuit layout which involves positioning cells within a target placement geometry while minimizing the placement area and the total interconnecting wire length. Placement heuristics capable of producing high quality (near optimal) placements with little computational effort are required as integrated circuits increase in size.

In this thesis, we propose and investigate a placement heuristic that combines constructive and iterative improvement methods. The heuristic is both flexible and extensible. A good initial placement is constructed through a combination of relative placements and circuit partitioning. Computational efficiency is achieved by using an interior point method for finding relative placements and cell interchange heuristics for finding circuit partitions. Two formulations for the relative placement problem are proposed and investigated. Iterative rather than direct methods are shown to reduce the computational time required by the interior point method. A clustering heuristic is also proposed for improving the efficiency of the placement heuristic. Subsequently, iterative improvement is applied to further improve the placement. We describe a simple and greedy iterative improvement method which is capable of producing high quality final placements when provided with a good initial placement. Placements generated by our heuristic are shown to compare favourably in terms of quality and computational efficiency to other established placement heuristics on a set of test circuits.

### Acknowledgements

Many people have made significant contributions during the completion of this work. It is not possible to sufficiently thank everyone, but special thanks must be extended to several individuals.

I would like to thank my supervisor, Dr. Anthony Vannelli. Without his time, financial support and patience during times of tantrums, this work would have never been completed. Thanks to the Natural Sciences and Engineering Research Council of Canada for making financial support available through a number of scholarships. I would like to thank my examining committee, Dr. George Kesidis, Dr. Henry Wolkowitz and Dr. Stefan Leue. Special thanks to my external examiner, Dr. Tamás Terlaky.

I would like to thank Dr. Victor Quintana, without whom I might never have pursued graduate studies, at least during this lifetime. Thanks to Dr. Shawki Areibi for valuable work related discussions and for making a short sabbatical abroad possible. I would like to thank Phil Regier, our system administator, for keeping my computer healthy. I would also like to thank my fellow graduate students, in particular Hussein Etwail, Tony Savor and William Bishop.

Last, but certainly not least, I would like to thank my family. Thanks to my sister Nancy and her husband Steve. Thanks to my youngest niece, Megen, for reminding me of how happy I must have been when I was two years old. Thanks to my older niece, Stephenie, for teaching me how to count to ten without a calculator. Finally, I would like to thank my parents, Reginald and Marlene Kennings, for their continual support.

To be means to be in competition.

C. S. Lewis

# Contents

| 1 | Intr        | oduction                            | 1 |

|---|-------------|-------------------------------------|---|

|   | 1.1         | Circuit Layout                      | 3 |

|   | 1. <b>2</b> | Research Motivations and Objectives | 5 |

|   |             | 1.2.1 Motivations                   | 5 |

|   |             | 1.2.2 Objectives                    | 6 |

|   | 1.3         | Thesis Outline                      | 7 |

| 2 | Cell        | Placement 10                        | D |

|   | 2.1         | Previous Approaches                 | 2 |

|   |             | 2.1.1 Constructive Methods          | 3 |

|   |             | 2.1.2 Iterative Improvement Methods | 3 |

|   | 2.2         | A Combination of Methods 1          | 4 |

|   | 2.3         | Test Circuits                       | 8 |

|   | 2.4         | Summary 19                          | 9 |

| 3 | Rela        | tive Placement 2                    | L |

|   | 3.1         | A Quadratic Programming Formulation | 3 |

|   |             | 3.1.1 The Objective Function        | 3 |

|   |             | 3.1.2 The Problem Constraints       | 4 |

|   | 3.2  | A Linear Programming Formulation                              | 26 |

|---|------|---------------------------------------------------------------|----|

|   |      | 3.2.1 The Objective Function                                  | 26 |

|   |      | 3.2.2 The Problem Constraints                                 | 27 |

|   | 3.3  | Analysis of the Formulations                                  | 29 |

|   | 3.4  | Summary                                                       | 32 |

| 4 | An   | Interior Point Method for Relative Placement                  | 33 |

|   | 4.1  | A Primal-Dual Interior Point Method                           | 35 |

|   | 4.2  | Solving the Augmented Equations                               | 38 |

|   |      | 4.2.1 Direct Methods                                          | 39 |

|   |      | 4.2.2 Iterative Methods                                       | 40 |

|   | 4.3  | Drop Tolerance Preconditioning                                | 41 |

|   |      | 4.3.1 The Augmented Equations and Zero Pivots                 | 42 |

|   | 4.4  | Numerical Results                                             | 45 |

|   | 4.5  | Summary                                                       | 48 |

| 5 | Par  | titioning the Placement Area                                  | 50 |

|   | 5.1  | Circuit Partitioning                                          | 53 |

|   |      | 5.1.1 General Description                                     | 53 |

|   |      | 5.1.2 Partitioning and Placement                              | 55 |

|   | 5.2  | A Proposed Strategy                                           | 58 |

|   |      | 5.2.1 Incorporating Circuit Partitioning                      | 58 |

|   |      | 5.2.2 Relative Placement and Circuit Partitioning Interaction | 61 |

|   | 5.3  | Summary                                                       | 63 |

| 6 | Init | ial Placement Construction                                    | 64 |

|   | 6.1  | Legalization Using Relative Cell Positions                    | 65 |

|   | <b>6.2</b> | Nume         | rical Results                                                 | 65        |

|---|------------|--------------|---------------------------------------------------------------|-----------|

|   |            | <b>6.2.1</b> | Computational Effort                                          | 66        |

|   |            | 6.2.2        | Total Computational Effort and Quality of the Placements      | 67        |

|   |            | 6.2.3        | Justification for Relative Placement and Circuit Partitioning | 69        |

|   | 6.3        | Summ         | ary                                                           | 70        |

| 7 | A S        | imple        | Iterative Improvement Method                                  | 73        |

|   | 7.1        | The G        | eneral Strategy                                               | 75        |

|   |            | 7.1.1        | Localizing the Improvement                                    | 75        |

|   |            | 7.1.2        | Cell Rearrangement Within a Tile                              | 76        |

|   | 7.2        | Nume         | rical Results                                                 | 81        |

|   |            | 7.2.1        | Computational Aspects                                         | 81        |

|   |            | 7.2.2        | Total Computational Effort and Quality of the Placements      | 83        |

|   | 7.3        | Summ         | ary                                                           | 85        |

| 8 | Circ       | cuit Cl      | lustering                                                     | 88        |

|   | 8.1        | Previo       | ous Approaches                                                | 89        |

|   | 8.2        | Propo        | sed Clustering Strategy                                       | 91        |

|   |            | 8.2.1        | Description                                                   | 91        |

|   |            | 8.2.2        | Incorporating Clustering into the Constructive Method         | 97        |

|   | 8.3        | Nume         | rical Results                                                 | 99        |

|   |            | 8.3.1        | Computational Effort and Impact on Netlist Sizes              | <b>99</b> |

|   |            | 8.3.2        | Computational Effort and Quality of Initial Placements        | 100       |

|   |            | 8.3.3        | Computational Effort and Quality of Final Placements          | 102       |

|   | 8.4        | Summ         | ary                                                           | 105       |

| 9 | Cor    | iclusio  | ns and Future Directions     | 107         |

|---|--------|----------|------------------------------|-------------|

|   | 9.1    | Sumn     | nary and Contributions       | . 108       |

|   |        | 9.1.1    | Constructive Placement       | . 108       |

|   |        | 9.1.2    | Improved Placement           | . 111       |

|   |        | 9.1.3    | Placement Enhancements       | . 112       |

|   | 9.2    | Futur    | e Directions                 | . 113       |

|   |        | 9.2.1    | Improved Cell Distribution   | . 113       |

|   |        | 9.2.2    | Interior Point Methods       | . 114       |

|   |        | 9.2.3    | Iterative Improvement        | . 115       |

|   |        | 9.2.4    | Performance Driven Placement | . 116       |

|   | 9.3    | Epilo    | gue                          | . 116       |

| A | Der    | ivatio   | n of the Augmented Equations | 11 <b>8</b> |

| в | Puł    | olicatio | <b>DB</b> S                  | 122         |

| B | ibliog | graphy   | ,                            | 123         |

# List of Tables

ļ

| 2.1        | Test circuit sizes and placement geometries                                 | 18  |

|------------|-----------------------------------------------------------------------------|-----|

| 2.2        | Additional test circuit statistics.                                         | 19  |

| 4.1        | Problem sizes and storage requirements for relative placement formulations. | 46  |

| 4.2        | Relative placement results for the QP formulation                           | 47  |

| 4.3        | Relative placement results for the LP formulation                           | 48  |

| 6.1        | Computational effort with the QP relative placement formulation             | 66  |

| <b>6.2</b> | Computational effort with the LP relative placement formulation             | 66  |

| 6.3        | Total computational effort for initial placements                           | 67  |

| 6.4        | Maximum row lengths for initial placements.                                 | 68  |

| 6.5        | Wire length estimates for initial placements                                | 68  |

| 6.6        | Single versus Several Relative Placements                                   | 69  |

| 7.1        | Constructive and iterative improvement times                                | 81  |

| 7.2        | Final solution times                                                        | 83  |

| 7.3        | Final placement areas                                                       | 84  |

| 7.4        | Final estimates of wire length                                              | 84  |

| 8.1        | Effects of clustering on netlist sizes.                                     | 100 |

| 8.2        | Computational effort with and without clustering.                           | 101 |

| 8.3 | Row lengths with and without circuit clustering               | 101 |

|-----|---------------------------------------------------------------|-----|

| 8.4 | Estimates of wire lengths with and without circuit clustering | 102 |

| 8.5 | Constructive and iterative improvement times                  | 103 |

| 8.6 | Final solution times                                          | 103 |

| 8.7 | Final placement areas.                                        | 104 |

| 8.8 | Final estimates of wire length                                | 105 |

# List of Figures

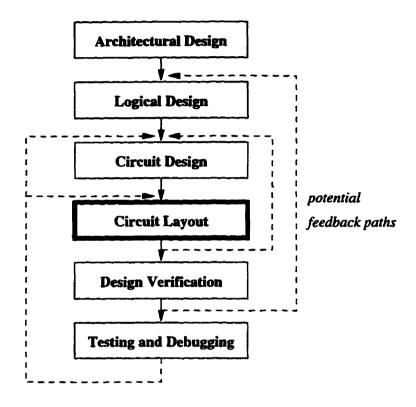

| 1.1         | Integrated circuit design procedure                               | 2 |

|-------------|-------------------------------------------------------------------|---|

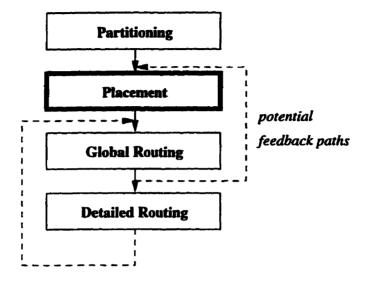

| 1. <b>2</b> | Circuit layout subproblems                                        | 4 |

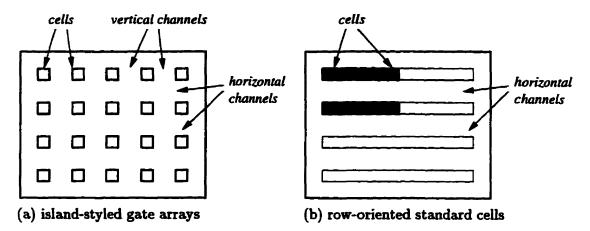

| 2.1         | Semi-custom design topologies                                     | 1 |

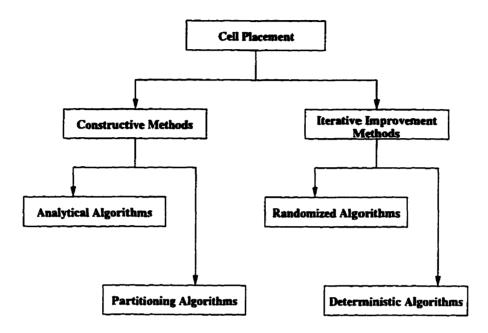

| 2.2         | Taxonomy of placement heuristics                                  | 2 |

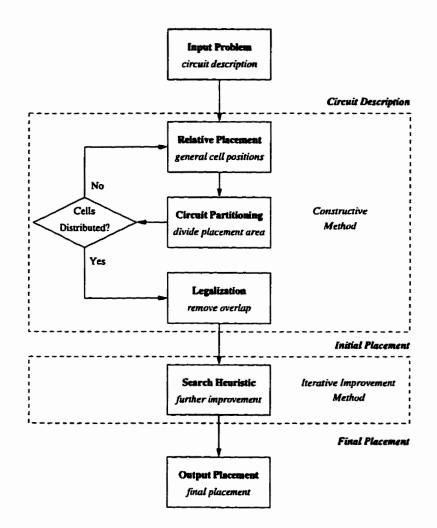

| 2.3         | A combination of constructive and iterative improvement methods 1 | 6 |

| 3.1         | Quadratic estimate of wire length                                 | 3 |

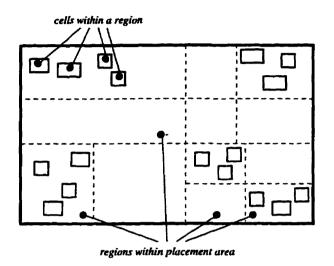

| 3.2         | Restriction of cells to regions                                   | 5 |

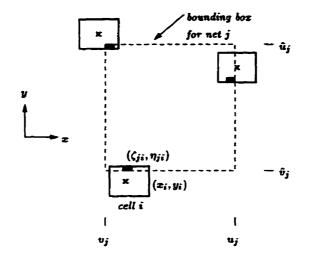

| 3.3         | Linear estimate of wire length                                    | 6 |

| 5.1         | Examples of relative placements                                   | 1 |

| 5.2         | Illustration of circuit partitioning                              | 4 |

| 5.3         | Methods for partitioning the placement area                       | 6 |

| 5.4         | Accounting for different measures of connectivity                 | 7 |

| 5.5         | Incorporating circuit partitioning into the placement heuristic   | 9 |

| 5.6         | Relative placement and circuit partitioning interaction           | 2 |

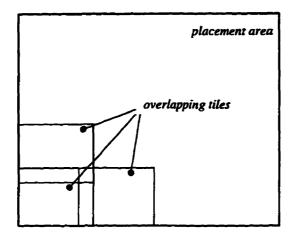

| 7.1         | Tiles overlapping the placement area                              | 5 |

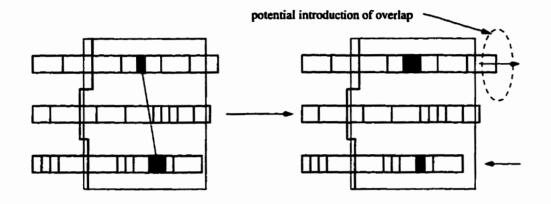

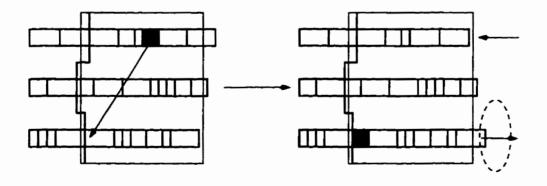

| 7.2         | Example of cell moves and swaps                                   | 9 |

| 7.3         | Algorithm for tile rearrangement.                                 | 0 |

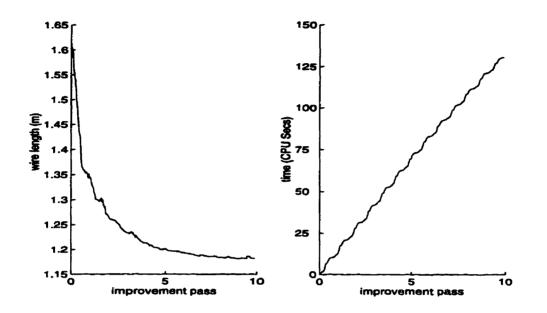

| 7.4 | Progression of the iterative improvement method            | 83 |

|-----|------------------------------------------------------------|----|

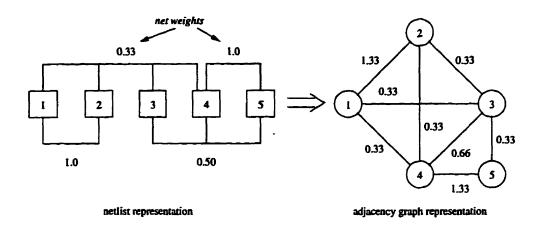

| 8.1 | Conversion from circuit netlist to adjacency graph         | 92 |

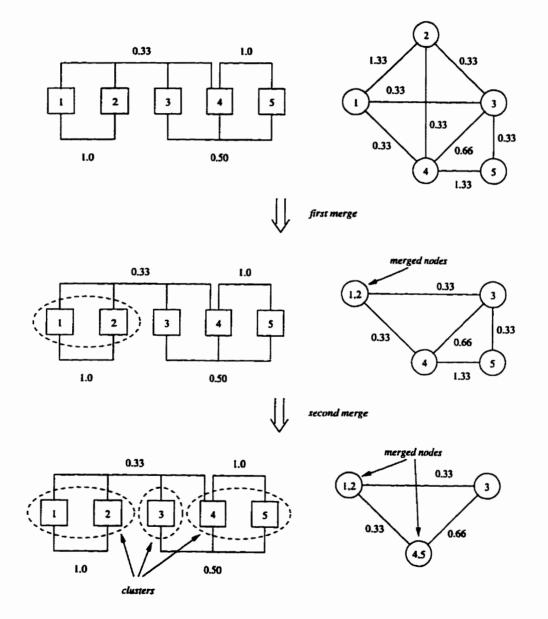

| 8.2 | Progression of the clustering heuristic                    | 94 |

| 8.3 | Pseudo-code for the clustering heuristic.                  | 95 |

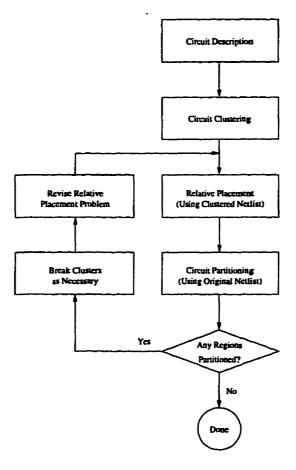

| 8.4 | Incorporating circuit clustering into the placement method | 98 |

# Chapter 1

# Introduction

Modern integrated circuits typically contain many thousands of switching cells. The large number of switching cells makes the design of an integrated circuit an overwhelming task. The design procedure is therefore divided into a sequence of design steps [22], namely architectural design, logical design, circuit design, circuit layout, design verification, testing, and debugging. These design steps are illustrated in Figure 1.1, and we briefly describe each of these steps.

Architectural design involves defining the goals and constraints of the system. This includes what the system will do, how the system will be divided into components and how the components will interact. Criteria for the system are also specified during the architectural design and may include specifications such as power requirements, area requirements, speed requirements and so forth.

Logic design involves deciding how each component of the system will be expressed logically. Various components may be implemented as RAM (random access memory), ROM (read only memory) or as PLAs (programmable logic arrays), for example.

Circuit design involves converting the logic design into electronic circuits that implement the desired functions. The result of the circuit design step is a set of functional blocks (cells) which are generally rectangular in shape and connected together via a set of signal paths (nets).

Figure 1.1: Integrated circuit design procedure.

Circuit layout involves converting the functional description of the circuit into a set of *physical masks* which can be used to physically realize the circuit. Since circuit layout is the topic of this thesis, a more detailed description of circuit layout is provided in a subsequent section.

Finally, design verification, testing and debugging involve checking the circuit to ensure all design criteria are satisfied, and that the circuit correctly performs its intend function.

Although the design procedure has been described as a sequence of steps, the individ-

ual design steps are not mutually exclusive operations. Each step influences subsequent steps, and the results of any step may be used as feedback information to revise an earlier step. Several iterations of the design procedure may be required to obtain a satisfactory design for any given integrated circuit.

### 1.1 Circuit Layout

As input to the circuit layout design step, we are given a description of a circuit in the form of a *netlist* which is a description of switching elements, or *cells*, and their interconnecting wires, or *nets*. Nets connect to cells via *pins* which represent electrical connection points to the cells and are located within the boundaries of the cells. Circuit layout involves determining the geometrical coordinates for cells within a two dimensional plane, or in one of a few planar layers, and connecting the cells according to the netlist. In performing this task, several objectives and requirements are satisfied. Typical objectives include (i) area minimization, (ii) wire length minimization, and (iii) minimization of performance driven criteria such as path delays, power consumption and so forth. Requirements represent constraints imposed by the design technology or fabrication technology being used, such as sufficient spacing between cells and wires, and so forth. Circuit layout is therefore an example of a constrained optimization problem.

The circuit layout problem itself is NP-hard [29] and is therefore divided into a sequence of subproblems which are solved one after another. These subproblems are also intractable, but are amendable to *heuristic solution methodologies* which are best described as approximate schemes capable of yielding near optimal solutions to the required problem with reasonable computational effort. The most common division of the circuit layout problem into subproblems is illustrated in Figure 1.2. First, a *partitioning* subproblem may be solved. This subproblem involves dividing a circuit into a small set

Figure 1.2: Circuit layout subproblems.

of relatively independent subcircuits which can be designed and implemented as separate circuits, and subsequently interconnected. The cell *placement* subproblem is solved (for each partitioned subcircuit) to determine the positions of the cells. Subsequently, the *global routing* and the *detailed routing* subproblems are solved to connect the cells according to the netlist. As illustrated for the circuit design procedure, the circuit layout subproblems are not mutually exclusive. The solution of each subproblem influences subsequent subproblems, and the results of any subproblem may be used as feedback information to revise and influence the solution of a previous subproblem.

As previously mentioned, circuit layout involves the minimization of several different objectives subject to constraints or restrictions imposed on the problem. However, due to the division of circuit layout into amendable subproblems, these objectives can often only be *estimated* during the solution of each subproblem. For instance, until the circuit routing is actually performed, quantities such as wire lengths and path delays are unknown. It is therefore necessary to have accurate estimates of these quantities during the

placement subproblem. The quality of the circuit layout highly depends on the design of the heuristic methods used to solve the placement and routing subproblems.

### **1.2 Research Motivations and Objectives**

In this thesis, we are concerned with the cell placement subproblem. Heuristics for cell placement may be classified as either iterative improvement [41] or as constructive methods [25]. We defer to Chapter 2 for a more detailed description of these heuristics and presently provide only enough description to illustrate the motivation and objectives for additional investigations into the cell placement subproblem.

#### 1.2.1 Motivations

Previously proposed placement heuristics all exhibit certain advantages and disadvantages. Interestingly, the advantages of certain heuristics tend to be the disadvantages of other heuristics. For instance, certain iterative improvement methods produce very high quality placements, but require excessively large computational effort to do so. Conversely, certain constructive methods require little computational effort, and although good, the placements produced by these methods are generally of lesser quality than their iterative improvement counterparts. In designing a placement heuristic, both quality and computational efficiency are issues that must be addressed. The quality of the placement is essential for the performance of the final circuit whereas computational efficiency is essential for shortening the design procedure (this is especially true for large circuits where a "short" design procedure may correspond to weeks, months or years). Finally, the flexibility and robustness of a placement heuristic are also issues which must be addressed as layout styles change and different design objectives are proposed. Ongoing research is therefore necessary to develop newer and better placement heuristics

which are: (i) effective, (ii) efficient, and (iii) flexible and robust.

#### 1.2.2 Objectives

In this thesis, our main objective is to investigate and develop a placement methodology which exhibits the aforementioned characteristics through enhancements, alterations and combinations of previously proposed constructive and iterative improvement methods. Essentially, we propose to combine constructive and iterative improvement methods where the constructive method is used to create a good initial placement which is subsequently improved using an iterative improvement method.

Our proposed constructive method requires a combination of mathematical programming and circuit partitioning. When used in combination with circuit partitioning, the solution of the mathematical program (which is known as the relative placement problem) provides relative cell positions (that is, cell adjacencies and proximities to desired positions) throughout the placement area. These cell positions represent useful information for determining cell positions in a good initial placement. We present two formulations of the relative placement problem which facilitate an investigation of the tradeoff in quality of the initial placements created by the constructive method versus the computational effort required to do so. Unlike previous heuristics, we propose an interior point method for solving the relative placement problems which arise during the constructive method. We introduce the interior point method as an enhancement to previously proposed solution methodologies since the interior point method allows a wide variety of constraints to be included into the formulation of the relative placement problem without requiring any changes in the solution methodology. We illustrate that the computational "bottleneck" of the interior point method is the solution of a sequence of systems of linear equations. Therefore, as an additional enhancement, we investigate the application of iterative methods as a means of solving these systems of equations. We illustrate that iterative methods

are useful for reducing the computational effort required to solve very large and sparse optimization problems when the degree of accuracy required in the solution (such as that required by the relative placement problem) is low. We also investigate circuit clustering as a means of reducing the computational effort required by the constructive method while improving the quality of the initial placements. Additionally, we illustrate that circuit clustering is applicable to other problems, such as circuit partitioning, which arise during the integrated circuit design procedure.

Our proposed iterative improvement method improves the placements created by the constructive method using a search heuristic to locally rearrange cells. We illustrate that, by taking into account the quality of the initial placement, the iterative improvement method requires little computational effort to create high quality placements. Finally, the objective function used to determine the improvement in any local rearrangement can be arbitrarily flexible when using a search heuristic, provided evaluation of the objective function is not prohibitive.

## **1.3 Thesis Outline**

This thesis is organized as follows. In Chapter 2, we describe cell placement in greater detail. We describe different types of placement topologies encountered in practice. Previous placement heuristics are also described. Finally, our proposed placement heuristic is described as a combination of constructive and iterative improvement methods. The purposes and interactions of the various components of the heuristics are described.

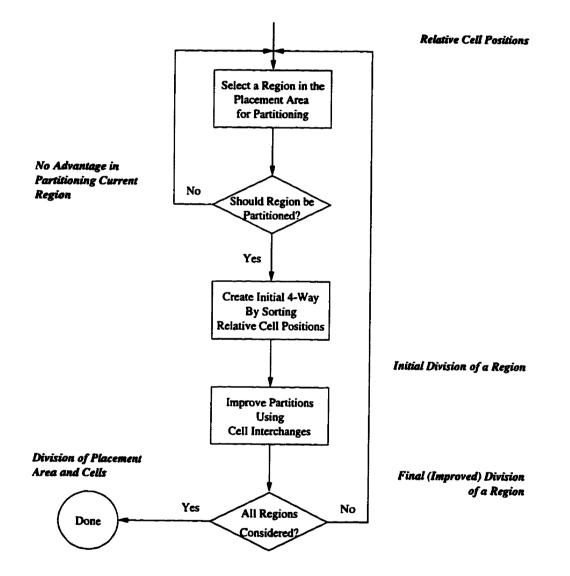

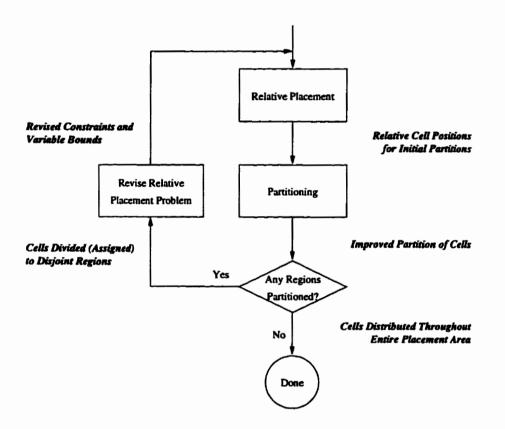

In Chapters 3 through 6, our constructive method for generating initial placements is described. In Chapter 3, the relative placement problem is described as a method for determining relative cell positions throughout the placement area. Two different formulations of the problem are presented to illustrate potential tradeoffs in quality versus speed during the relative placement. An interior point method which is suitable for solving both formulations of the relative placement problem is described in Chapter 4. In Chapter 5, the circuit partitioning problem is presented and its application to cell placement is described. We illustrate that several iterations of relative placement and circuit partitioning results in a procedure for determining a good distribution of cells throughout the placement area. This distribution of cells is shown to be useful in determining good cell positions in an initial legal placement. The creation of an initial legal placement from the cell positions provided by the relative placement and circuit partitioning iterations is described in Chapter 6. Additionally, numerical results are presented in Chapter 6 to illustrate the effectiveness and efficiency of our constructive method using both relative placement formulations.

In Chapter 7, an iterative improvement method is presented for further improving the initial placement provided by the constructive method. Numerical results are presented to demonstrate that final placements generated after the completion of the constructive and iterative improvement methods are comparable or better than existing placement heuristics on a set of test circuits. We consider iterative improvement as a necessary step in the overall placement heuristic.

Circuit clustering is described in Chapter 8. A clustering heuristic for condensing a circuit netlist is proposed. Circuit clustering is proposed in order to reduce the dimensionality of the relative placement problems thereby improving the computational efficiency of the constructive method. Numerical results are presented to demonstrate the effective-ness of circuit clustering when incorporated into the placement heuristic. Clustering is demonstrated to provide comparable placements (to those obtained without clustering) while substantially reducing the computational effort.

Finally, a summary of this thesis is presented in Chapter 9. The intention is to highlight the contributions of this thesis and to provide a description of future research

possibilities for additional enhancements to this work.

# Chapter 2

# **Cell Placement**

As previously mentioned, cell placement is a subproblem of the circuit layout design step which involves positioning cells (although a small number of cells, known as I/O*pads* are fixed at positions around the periphery of the placement area) within a specified placement geometry. In performing the placement, several objectives are minimized while satisfying several restrictions or constraints imposed on the positions of the cells. Primarily, the objectives in cell placement are minimization of (i) the placement area, (ii) the wire length, and/or (iii) performance criteria such as path delays and so forth. Restrictions on cell positions are generally due to the type of placement required, which is a function of the technology and layout style begin used in the design. For instance, the technology determines the size of the cells and may influence the required spacing between neigbouring cells. The layout style may require the cells to be positioned within rows or at points arranged in a grid [29].

The type of cell placement we consider is *semi-custom* design [29] which is applicable to the design of Application Specific Integrate Circuits (ASICs) and Field Programmable Gate Arrays (FPGAs). In semi-custom design, typical circuits may contain thousands of cells. Restrictions are imposed on the positions of cells and locations for routing con-

Figure 2.1: Semi-custom design topologies.

nections between cells. In other words, the physical topology of the circuit is essentially known a priori. Cells implementing different functions can be placed at any of the restricted positions and subsequently implemented by modifying a standard set of physical masks prior to the fabrication of the circuit.

Figure 2.1 illustrates common semi-custom design topologies, namely island-styled gate arrays and row-oriented standard cells/gate arrays. In island-styled gate arrays, cells are typically equal in width and height, and must be positioned at specified grid points within the placement area. Subsequent routing is performed in vertical and horizontal channels. In row-oriented placement, cells are equal in height, but are different in width. Cells must be placed into a prescribed number of rows located within the placement area. Once placed, routing is performed in the horizontal channels in between adjacent rows. Connections between cells in non-adjacent rows may be routed around the end of the rows, or through the insertion of additional cells, known as *feedthroughs*, into the rows. Since identical placement heuristics are typically used for each topology, we consider only row-oriented placement.

In performing cell placement, hand designs are impractical due to the large circuit sizes. Furthermore, the design objectives can only be approached at the expense of ex-

Figure 2.2: Taxonomy of placement heuristics.

cessive computational efforts. Therefore, high quality placements are obtained only by accepting excessive computational effort, or by sacrificing placement qualities. Automated placement heuristics are required to facilitate semi-custom design, and to reach a reasonable tradeoff in quality versus computational effort.

## 2.1 Previous Approaches

Many different heuristics have been proposed for cell placement. The taxonomy of these placement heuristics is illustrated in Figure 2.2. Placement heuristics may be broadly classified as either constructive or iterative improvement methods [29].

#### 2.1.1 Constructive Methods

Constructive methods produce placements directly from the circuit description (that is, the cell-net interconnections provided by the netlist). These methods may be subdivided into two major categories, namely partitioning algorithms [8, 40] and analytical algorithms [32]. Constructive methods are considered global approaches, since placements are obtained by considering all circuit connections simultaneously. Typically, the combination of partitioning and analytical algorithms has resulted in the most successful constructive methods [25, 49].

Constructive methods have the advantage that they are generally fast and produce reasonably good placements for large circuits due to the globality (that is, the simultaneous consideration of all cell interconnections) of the approach. However, these methods are typically restrictive in the design objectives which can be incorporated into the cost functions and therefore cannot produce the highest quality placements.

#### 2.1.2 Iterative Improvement Methods

Iterative improvement methods do not produce placements directly from the circuit description, but rather begin with an initial placement and search for an improved placement by making local changes to the existing placement. These perturbations are continued until a near optimal placement is obtained. Therefore, these methods are essentially local *search algorithms* which begin at an existing solution and move to neighbouring solutions via small and local perturbations. Iterative improvement methods may be subdivided into two major subclasses, namely randomized or deterministic algorithms. This division depends on whether or not a given perturbation is used to alter an existing placement.

Iterative improvement methods are highly flexibility in the design objectives which can be incorporated into the cost functions. Since the cost of a given placement is a function of the design objectives, it is only necessary to re-evaluate the cost function to determine if one placement is better than another placement.

Randomized algorithms always accept changes which lead to an improved solution, and may also accept changes leading to poorer solutions with a low probability. It is this acceptance of changes leading to poorer solutions which gives these algorithms the ability to escape from local minima, and to approach a global optimum. Randomized iterative improvement methods are traditionally based on Simulated Annealing [41] or on evolution-based algorithms [26, 27]. Randomized algorithms produce very high quality placements (often the best of the heuristic methods), which is a direct consequence of the ability of such approaches to escape from local minima. However, excessive amounts of computational effort are required by randomized algorithms to produce these results.

Unlike randomized algorithms, deterministic algorithms only accept changes which lead to improved solutions. These algorithms require less computational effort than their randomized counterparts, but are generally unable to produce placements of comparable quality due to their inability to escape from local minima. Deterministic algorithms that have the ability to escape local optima have been proposed [37]. Even so, these algorithms are not comparable to randomized algorithms in there ability to escape from local minima.

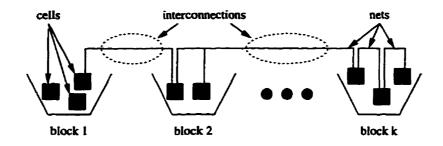

### 2.2 A Combination of Methods

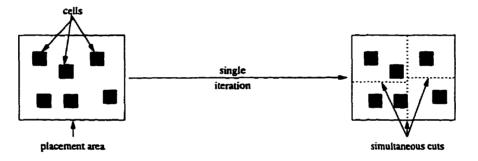

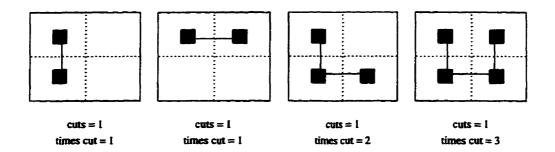

Since constructive and iterative improvement methods both exhibit advantages and disadvantages, further progress in developing placement heuristics requires combining and/or enhancing the different methods. Constructive methods, although not as flexible as iterative improvement methods, are capable of producing good placements with low computational effort. Flexibility for the constructive method may be achieved by enhancing existing constructive methods by using different modelling of the problem or by using more flexible solution algorithms. Conversely, iterative improvement methods are very flexible and are capable of producing high quality placements, but at the expense of excessive computational effort. By combining the methods, excessive computational efforts may be avoided. An iterative improvement method can take advantage of a good initial placement generated by a constructive method and less computational effort will be required to reach a near optimal placement. In other words, a deterministic improvement algorithm may be sufficient. Similarily, the quality of the final placement is not restricted by the flexibility of the constructive method since subsequent iterative improvement is performed. The combination of a constructive and an iterative improvement method results in an overall placement heuristic illustrated in Figure 2.3. As illustrated, the placement heuristic requires a combination of relative placements, circuit partitioning and search heuristics.

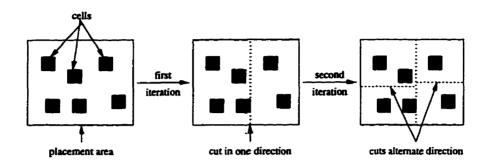

An initial placement is generated using a constructive method as follows. The circuit description and desired placement geometry is read, and an iterative procedure involving a combination of mathematical programming and circuit partitioning begins. The circuit description and placement geometry is first used to create an initial overlapping cell placement which is described by a mathematical program known as the *relative placement problem*. By allowing several placement violations (cells are allowed to overlap and are not restricted to positions within the rows), the solution of the relative placement problem provides the general positions of cells throughout the placement area while minimizing an estimate of the total wire length. The intention is to determine general cell proximities and adjacencies in the final placement while providing a global view of the circuit interconnections. Ideally, the placement restrictions should be included in the formulation of the relative placement problem. However, these simplifications are required in order to obtain a practical solution methodology for solving the relative placement formulations.

Figure 2.3: A combination of constructive and iterative improvement methods.

#### CHAPTER 2. CELL PLACEMENT

The simplifications made when determining relative cell positions may result in significant cell overlap. Furthermore, cells tend to cluster towards the center of the placement area. Circuit partitioning is applied to divide the cells into disjoint groups and the placement area into regions. By assigning the partitioned groups of cells to disjoint regions within the placement area cell overlap may be reduced (since cells in one regions are prevented from overlapping with cells in other regions) and area utilization is improved (by forcing cells into unoccupied portions of the placement area). By resolving the relative placement problem with additional information (constraints) appended from the circuit partitioning problem, a good (global) distribution of cells throughout the placement area may be obtained. This information aids in determining cell proximities in the final placement.

Therefore, there is an interaction between the relative placement and the circuit partitioning problems. The relative cell positions are used to generate initial partitions of the cells. These initial partitions are subsequently improved using circuit partitioning. Once the partitioning is completed, the division of the cells into disjoint regions throughout the placement area is taken into account during subsequent relative placements by including additional constraints into the relative placement formulations. This alternation between mathematical programming and circuit partitioning is repeated until cells are distributed evenly throughout the entire placement area. The interaction between the relative placement and circuit partitioning problems is described in more detail in Chapter 5. Subsequently, a *legalization* heuristic based on the cell positions can be applied to remove any residual cell overlap and to satisfy any placement restrictions imposed on the cell positions.

Once the initial cell placement is obtained, an iterative improvement method is applied to further improve the placement. Given the effort expended to produce an initial placement, we assume that the initial placement is good (cells are in the vicinity of their final

#### **CHAPTER 2. CELL PLACEMENT**

| Circuit   | Cells | Nets  | Pads | Rows |

|-----------|-------|-------|------|------|

| circuit1  | 833   | 983   | 81   | 21   |

| circuit2  | 3014  | 3136  | 107  | 21   |

| biomed    | 6417  | 5742  | 97   | 27   |

| industry1 | 2271  | 2478  | 580  | 15   |

| industry2 | 12142 | 13419 | 495  | 70   |

| industry3 | 15059 | 21938 | 375  | 50   |

Table 2.1: Test circuit sizes and placement geometries.

positions in a near optimal placement). A greedy and highly localized search heuristic based on cell moves and swaps is applied to rearrange cells. Localizing the rearrangement of the cells (which is possible as a consequence of the effort spent to produce the initial placement), implies our iterative improvement method requires less computational effort. That is, since the cells are highly restricted in their possible positions, the search for improved cell positions is accomplished in a more timely manner.

### 2.3 Test Circuits

Throughout this work, numerical results are presented on a set of test circuits to illustrate various aspects of the placement heuristic. All the numerical results presented were produced on a Sun SPARC station 5/85 with 64 Mbytes of memory.

The test circuits we consider are illustrated in Table 2.1. In Table 2.1, the identifier and the number of cells, nets and I/O pads for each circuit are presented. The first two test circuits are of our own creation and the remaining four circuits are taken from the MCNC benchmark test suite [28]. The number of rows required in the final placement of each circuit are also indicated in Table 2.1. The number of rows determines the desired placement geometry in the following sense. The height of the cells determines the height of the rows and the spacing between the rows. This in turn determines the height of the placement area. The width of the placement area is determined by the length of

| Circuit   | Cell | Deg. |      | Ne    | et Size |        |

|-----------|------|------|------|-------|---------|--------|

|           | Avg. | Std. | Avg. | Std.  | % ≤ 3   | % > 10 |

| circuit1  | 3.36 | 1.34 | 3.12 | 2.50  | 82.50   | 3.46   |

| circuit2  | 3.66 | 1.57 | 3.65 | 3.77  | 73.57   | 4.82   |

| biomed    | 3.23 | 1.06 | 3.66 | 20.89 | 84.78   | 3.48   |

| industry1 | 3.02 | 1.38 | 3.47 | 8.56  | 80.79   | 3.71   |

| industry2 | 3.81 | 1.81 | 3.59 | 10.97 | 85.22   | 4.48   |

| industry3 | 4.27 | 1.54 | 3.00 | 3.23  | 79.36   | 0.77   |

Table 2.2: Additional test circuit statistics.

the longest row once the cells are placed into the rows. By keeping the rows equal in length (which is generally not possible since the cells differ in widths), the width of the placement area is minimized.

Additional statistics for each circuit are presented in Table 2.2. For each circuit, the average and standard deviation for the number of nets incident on each cell are presented. These statistics indicate that very few nets are incident to each cell and that the variation in the number of incident nets is low. The average and standard deviation for the number of cells connected to each net are also presented in Table 2.2. Finally, the number of nets (expressed as a percentage of the total number of nets) connecting less than or equal to 3 cells and more than 10 cells are presented. These statistics indicate that a very large percentage of the nets are short (connected to only a few cells) and very few nets are long (connected to many cells). Therefore, the circuits are typically sparse. For several circuits, namely *biomed*, *industry1* and *industry2*, the standard deviations for the number of cells connected to each net are quite large. This indicates that for these test circuits, the variation in net connectivity is large and that some of the long nets are very long.

### 2.4 Summary

In this chapter, semi-custom design has been described. Semi-custom design is especially relevant to ASIC and FPGA design, where the circuits may contain many thousands of cells. Because of the large number of cells, hand design is not possible and optimal cell placements may only be obtained by accepting excessively large computational efforts. Several automated placement heuristics have been proposed and may broadly be classified as either constructive or iterative improvement methods. The classification depends on the approach for finding placements. Primarily, constructive methods are less flexible, but are capable of producing good placements with little computational effort. Conversely, iterative improvement methods are highly flexible, and are capable of producing high quality placements. Unfortunately, those iterative improvement methods capable of producing high quality placements require large computational time and effort.

To improve cell placement, a combination of methods is useful in order to exploit the advantages of the different methods. A constructive method is useful for generating a good initial placement which is subsequently improved using an iterative improvement method. Given that the initial placement is good, the computational effort of the iterative improvement method may be reduced by taking into account the quality of the initial placement. Similarily, the quality of the final placement is not restricted by the constructive method due to the subsequent iterative improvement. The combination of methods results in an overall placement heuristic requiring a combination of mathematical programming and circuit partitioning to construct an initial placement. This is followed by the application of a search heuristic to perform the iterative improvement.

In the next chapter, we begin the description of our proposed constructive method by introducing the relative placement problem.

# Chapter 3

# **Relative Placement**

In this chapter, we consider the relative placement problem. Relative placement involves determining the relative positions of cells throughout the placement area while minimizing an estimate to the total interconnecting wire length. In determining the relative cell positions, the relative placement problem takes a *global view* of the cell positions by considering all cell interconnections simultaneously. This global view aids in determining cell proximities and adjacencies in an initial legal (non-overlapping) placement. Several simplifications are made when formulating the relative placement problem in order to make the resulting problem solvable using an efficient algorithm. For instance, cells are permitted to overlap and are not restricted in their positioning provided they fall within the placement area. Due to these simplifications, the solution of the relative placement problem does not produce a legal placement by itself. Relative placement is a heuristic method intended to provide a good "idea" of the general cell positions. These cell positions can be provided to (or used in combination with) other heuristics to remove cell overlap and to satisfy placement restrictions.

The relative placement problem has been formulated as a mathematical program, typically with either linear or quadratic objective functions [3, 5, 20, 21, 23, 25, 37, 39, 38, 42,

#### **CHAPTER 3. RELATIVE PLACEMENT**

49]. The solution methodologies proposed have varied according to the objective function used and the constraints included in the formulation. Example solution methodologies have included linear programming methods [5, 23, 49], eigenvector methods [3, 20], linear systems methods [25, 37] and various lagrangian multiplier methods [21, 39, 38, 42].

In this chapter, we present two relative placement formulations. The first formulation uses a quadratic objective function whereas the second formulation uses a linear objective function. Both formulations are subject to a set of linear constraints and variable bounds. Therefore, one formulation may be solved as a Quadratic Program (QP) and the other as a Linear Program (LP). We consider two formulations since the different objective functions imply a different estimate of wire length and therefore different relative cell placements. Furthermore, the different formulations result in optimization problems which differ in the number of unknowns and the number of constraints. Therefore, the potential for tradeoffs in quality of solution versus computational effort may be investigated. Finally, we consider both formulations since both may be solved using an interior point method [45] (which is the topic of the next chapter).

This chapter is organized as follows. The formulations of the relative placement problem as a QP and a LP are presented in Sections 3.1 and 3.2, respectively. In Section 3.3, we present an analysis of the two formulations. We demonstrate the differences in the size and storage requirements for the two formulations. The potential benefits in quality versus computational effort for each of the formulations is also described to illustrate why both formulations should be considered. Finally, a summary of this chapter is provided in Section 3.4.

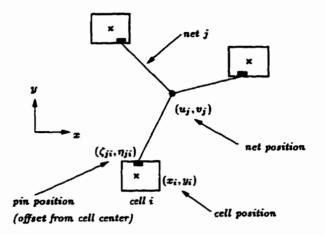

Figure 3.1: Quadratic estimate of wire length.

# 3.1 A Quadratic Programming Formulation

#### 3.1.1 The Objective Function

Quadratic program formulations are a result of the estimate used for wire length and the constraints included in the problem formulation [25]. As an estimate of wire length for net j, we use the sum of the squared distance from all pins to the net position, which is taken as the mean value of the coordinates of the connected pins. This estimate of wire length is illustrated in Figure 3.1. The resulting estimate of wire length for net j, denoted by  $l_j$ , is given by

$$l_{j} = \sum_{i \in C_{j}} \left[ (x_{i} + \zeta_{ji} - u_{j})^{2} + (y_{i} + \eta_{ji} - v_{j})^{2} \right], \qquad (3.1)$$

where  $C_j$  denotes the set of cells connected to net j,  $(x_i, y_i)$  denotes the position of cell i,  $(u_j, v_j)$  represents the location of net j, and  $(\zeta_{ji}, \eta_{ji})$  denotes the offset for the pin connecting cell i to net j. This estimate of wire length is separable in the x and y directions, and minimization can be performed independently in both directions. The

following description involves only the x direction, but extends to the y direction without any loss of generality.

The total estimate of the wire length is given by summing the estimates of wire length for all the nets. Performing this summation and substituting the coordinates for each net and the coordinates of all fixed I/O pads results in a total estimate of wire length (ignoring constant terms) that can be written in matrix form as

$$L_{QP} = \frac{1}{2} \mathbf{x}^T \mathbf{Q} \mathbf{x} + \mathbf{c}^T \mathbf{x}$$

(3.2)

where  $\mathbf{Q}$  is a symmetric positive definite matrix ( $\mathbf{Q} > 0$ ), c is a cost vector, and x is the vector of unknown cell positions. This estimate of wire length results in a symmetric positive definite quadratic objective function.

#### 3.1.2 The Problem Constraints

We now consider constraints imposed on the cell positions. Although we allow cells to overlap, we still include constraints in the formulation which tend to reduce the amount of cell overlap and provide an even distribution of cells throughout the placement area. We assume that the placement area has been partitioned into disjoint regions, and that each free cell has been assigned to one region (the method for obtaining a partitioning of the cells is the subject of a subsequent chapter). The partitioning of the placement area and the restriction of cells to regions is illustrated in Figure 3.2.

For each region j, let  $R_j$  denote the cells assigned to this region. Additionally, let  $L_j$ and  $U_j$  denote the lower and upper boundaries for region j, respectively. Cells assigned to region j are restricted to positions within the region by including the variable bounds given by

$$L_j \leq \boldsymbol{x}_i \leq U_j, \quad \forall i \in R_j. \tag{3.3}$$

Figure 3.2: Restriction of cells to regions.

The consequence of the variable bounds is a reduction in the total amount of cell overlap since cells in different regions are prevented from overlapping with each other.

To improve the distribution of cells throughout each region, we include first moment constraints. Let  $X_j$  denote the centre of region j. For each region j, we include the inequality constraints

$$(1-\alpha)X_j \leq \frac{1}{F_i}\sum_{i\in R_i}A_ix_i \leq (1+\alpha)X_j, \qquad (3.4)$$

where  $F_j$  denote the total area of the cells assigned to region j and  $\alpha \in (0, 1)$  is a parameter included to permit some (small) amount of flexibility on the value of the first moment for the cells in region j. The first moment constraints improve the distribution of cells within each region by requiring a balancing of cell area throughout the region. That is, if a cell tends to the left of a region due to the minimization of wire length, then other cells within the region will be forced to the right of the region in order to satisfy the first moment constraints. The result is a better usage of the area within each region.

Figure 3.3: Linear estimate of wire length.

The constraints and variable bounds can be expressed in matrix form as

$$\mathbf{A}\mathbf{x} \leq \mathbf{b}, \quad \mathbf{l} \leq \mathbf{x} \leq \mathbf{u}. \tag{3.5}$$

Equations (3.2) and (3.5) result in a QP formulation for the relative placement problem.

# 3.2 A Linear Programming Formulation

#### 3.2.1 The Objective Function

Like quadratic program formulations, linear program formulations are a result of the wire length estimate and the constraints included during the problem formulation [49]. As an estimate of wire length for each net, we use the half perimeter wire length (HPWL) as shown in Figure 3.3. For each net j, we enclose all cells connected to net j by a *bounding box*, and introduce the variables pairs  $(u_j, v_j)$  and  $(\hat{u}_j, \hat{v}_j)$  to denote the upper and lower limits on the bounding box in the x and y directions, respectively. The resulting estimate

#### **CHAPTER 3. RELATIVE PLACEMENT**

of wire length for net j is given by

$$l_{j} = (u_{j} - v_{j}) + (\hat{u}_{j} - \hat{v}_{j}).$$

(3.6)

This estimate of wire length is separable in the x and y directions and minimization can be performed independently in both directions. The rest of the discussion involves only the x direction, but extends to the y direction without any loss of generality.

The total estimate of the wire length is given by summing the estimates of wire length for all the nets. Performing this summation results in a total estimate of wire length that can be written in matrix form as

$$L_{LP} = \mathbf{c}^T (\mathbf{u} - \mathbf{v}) + \mathbf{0}^T \mathbf{x}, \qquad (3.7)$$

where u and v are vectors representing the net variables (that is, the vectors representing the upper and lower limits on the bounding boxes for all nets, respectively), x represents the unknown cell positions, 0 is the zero vector, and c is a cost vector (equal to e, where e denotes a vector of ones). This estimate of the total wire length is a linear objective function.

#### 3.2.2 The Problem Constraints

As for the QP formulation, variable bounds and first moment constraints are included in the LP formulation to eliminate overlap between cells in different regions and to improve cell distribution within each region, respectively.

For the QP formulation, nets are considered as points that can be expressed directly in terms of the cell positions (that is, by equality relationships) and therefore eliminated from the problem. Since the net variables represent only bounds on the surrounding bounding boxes, they cannot be expressed directly in terms of the cell positions and cannot be eliminated from the LP formulation. The LP formulation requires additional constraints to relate the net and cell positions. The net variables u and v must remain above and below all pin positions on the cells in the respective nets. This restriction can be accomplished using inequality constraints and variable bounds. Consider net j and its connected cells  $C_j$ . For each net j,  $u_j$  is restricted above all pins on the cells in net jusing the inequalities

$$u_j \geq x_i + \zeta_{ji}, \quad \forall i \in C_j. \tag{3.8}$$

(Recall that nets connect to pins. For instance, for a net j which connects to a pin of cell i, the pin position is  $x_i + \zeta_{ji}$ , where  $\zeta_{ji}$  is a *constant* expressed in the circuit description indicating the offset of the pin from the center of the cell). For free cells, these inequalities represent constraints since the cell positions are unknown. For fixed I/O pads, these inequalities represent variable bounds on the net variables u since the fixed I/O pad positions are known. By replacing  $u_j$  with  $v_j$  and changing the direction of the inequality, similar constraints can be included to restrict  $v_j$  below all cells in net j.

The problem constraints and variable bounds can be written in matrix form as

$$\mathbf{A}\begin{bmatrix}\mathbf{u}\\\mathbf{v}\\\mathbf{x}\end{bmatrix}\leq\mathbf{b}, \ \mathbf{l}\leq\begin{bmatrix}\mathbf{u}\\\mathbf{v}\\\mathbf{x}\end{bmatrix}\leq\mathbf{u}.$$

(3.9)

Equations (3.7) and (3.9) result in a LP formulation for the relative placement problem.

### **3.3** Analysis of the Formulations

Both the QP and LP formulations can be expressed as optimization problems in the form given by

minimize

$$\mathbf{c}^T \mathbf{z} + \frac{1}{2} \mathbf{z}^T \mathbf{Q} \mathbf{z}$$

subject to  $\mathbf{A} \mathbf{z} \leq \mathbf{b}$ , (3.10)

$\mathbf{0} \leq \mathbf{z} \leq \mathbf{u}$

where z represents the vector of unknowns. When  $\mathbf{Q} \neq \mathbf{0}$  the QP formulation is implied whereas when  $\mathbf{Q} = \mathbf{0}$  the LP formulation is implied. This optimization problem can be solved in polynomial-time using the same primal-dual interior point method [45]. It is important to emphasize that the LP formulation is *not* solved using a quadratic program solver simply by setting  $\mathbf{Q} = \mathbf{0}$ . The structure (that is, the sequence of steps and computational requirements at each step) of the interior point method is essentially the *same* regardless of whether or not the optimization problem is a QP or a LP. This represents one benefit of using the interior point method for solving the relative placement formulations in that both formulations are essentially solved using the same algorithm, with only minor changes required to implement the algorithm.

The question arises as to the advantages and disadvantages of both formulations. The complexity of the relative placement problem is a function of the solution method used (in our case the interior point method). In turn, the computational efficiency of the method is a function of the number of mathematical operations required during the solution method. It is therefore useful to consider the optimization problem sizes and storage requirements for both formulations.

Let p represent the number of pins in the circuit, n the number of nets, c the number of cells, and r the number of regions into which the placment area has been partitioned. When considering the optimization problem sizes and storage requirements, the quantities

#### CHAPTER 3. RELATIVE PLACEMENT

of interest are the number of variables and constraints, and the number of nonzeros in any matrices required in the formulation.

For the QP formulation the number of variables equals c and the number of constraints equals 2r. The number of nonzeros in the constraint matrix **A** (due to the first moment constraints) is 2c since each cell is involved in only 2 constraints. Consider next the matrix **Q**. If we consider one net connecting q cells, then we find that the quadratic estimate of wire length causes a  $q \times q$  dense block of nonzero entries (a clique) to appear in **Q**. Therefore, in the worst-case, where we find a net connecting every cell, the matrix **Q** will be totally dense and require storage for  $c^2$  nonzero entries. Considering both matrices **Q** and **A**, the storage requirements for the QP formulation are  $c^2 + 2c$ . We note, however, that for typical circuits the nonzero entries in **Q** is much lower than  $c^2$  due to the sparsity of the circuit (the circuit statistics presented in Chapter 2 support this observation).

For the LP formulation the resulting number of variables is equal to c + 2n due to the inclusion of the net variables within the formulation. For each pin, two constraints are required to represent the bounding box relationships. Therefore, the total number of bounding box constraints in 2p. Including the first moment constraints, the total number of constraints for the LP formulation is 2p + 2r. Since the matrix Q does not appear in the LP formulation, it is necessary to consider only the constraint matrix A. For each bounding box constraint, two nonzeros are introduced, resulting in a total of 4p nonzero entries. Considering the first moment constraints, this implies a total of 4p+2c nonzeros in A.

The QP formulation results in optimization problems which have substantially fewer variables and constraints than the LP formulation. Comparision of the storage requirements is slightly more difficult since the storage requirements for the QP formulation can only be bounded and not calculated explicitly. Although it appears that the QP formulation requires more storage (due to the quadratic term  $c^2$ ), in practical situations the storage requirements for the QP formulation are less than the LP formulation. This observation is highlighted in the next chapter, when we introduce the interior point method and solve several relative placement problems using both formulations. We briefly note that the optimization problem sizes and storage requirements for the LP formulation may be reduced somewhat by applying standard LP preprocessing techniques [16] whereas the QP formulation does not benefit from preprocessing due to the nature of the first moment constraints.

The analysis just presented, along with the empircal results presented in the next chapter for storage requirements, indicate that QP formulation is preferable to the LP formulation: It results in smaller optimization problems requiring less storage which implies lower computational efforts. However, the LP formulation cannot be ignored. Empirical investigations have shown that linear objective functions may produce better placements in terms of wire length than quadratic objective functions [37]. Quadratic objective functions over emphasize the minimization of long nets (nets connecting many cells) at the expense of short nets (nets connecting few cells), whereas linear objective functions consider all nets equally during the minimization of the wire length. Furthermore, linear objective functions better approximate the actual wiring strategies used to connect cells during the actual routing of the circuit. Therefore, the LP formulation offers the possibility of better final placements at the expense of increased computational effort. We consider the LP formulation for this reason and to faciliate an investigation of the tradeoff in computational effort versus quality of solution for different relative placement formulations.

## 3.4 Summary

In this chapter, the relative placement problem has been formulated as both a quadratic program and as a linear program. The formulation was shown to depend on the estimate of wire length. In terms of the resulting optimization problem sizes and storage requirements, the QP formulation is preferable to the LP formulation. Less variables and constraints are required for the QP formulation. Additionally, for practical circuits the storage requirements are lower for the QP formulation. The smaller problem sizes for the QP formulation were shown to be a consequence of representing the nets as points. When represented as points, the net variables can be expressed in terms of the cell positions and eliminated from the formulation. The elimination of the net variables was not possible for the LP formulation.

The optimization problem sizes and storage requirements do not necessarily make the LP formulation unattractive. Empirical results by other researchers have indicate that the LP formulation may result in better final placements [37]. This improvement in quality stems from the observation that the LP formulation considers all nets equally during the minimization of wire length and better represents the wiring strategies actually used when routing a circuit. The result is two different relative placement formulations, each with advantages and disadvantages. By considering both formulations, the tradeoff in quality versus computational effort may be investigated.

In the next chapter, we consider an interior point method as an efficient solution methodology for both the QP and LP formulations presented in this chapter.

# Chapter 4

# An Interior Point Method for Relative Placement

In this chapter, we consider a primal-dual interior point method [31, 45, 46] suitable for solving both the QP and LP relative placement formulations. We consider an interior point method for several reasons: (i) it has a worst-case polynomial-time complexity, (ii) it is simple to implement, and (iii) it exhibits effective solution times on large and sparse optimization problems. These characteristics make an interior point method attractive since the relative placement formulations result in large and sparse optimization problems.

As previously illustrated in Chapter 3, the QP and LP formulations presented are similar to those used by other researchers. However, the interior point method represents a different solution methodology than those previously proposed. For instance, previous LP formulations [23, 49] used simplex-based approaches [30] to obtain a solution (Although, more recently, a primal-dual interior point method specifically for solving an LP formulation has been proposed [5]). Computationally, the interior point method was demonstrated to be superior to the simplex-based approaches. For the QP formulation,

various solution methodologies have been proposed and rely on the constraints imposed on the problem. For wire length minimization, linear systems approaches have been used [25, 37]. However, these approaches are highly dependent on the structure of the constraints included in the problem formulation. Similarly, other QP approaches, such as eigenvector approaches [3, 20], also rely heavily on the formulation. When these approaches are used, careful consideration must be given when adding constraints into the formulation. Therefore, an interior point method suitable for the QP formulation offers more flexibility than the aforementioned linear system and eigenvector approaches. Other more flexible approaches for QP formulations have been based on Lagrangian multipliers [21, 39, 38, 42], where convex (and sometimes non-differentiable) constraints have been included into the formulation for various reasons (specifically, for inclusion of performance driven criteria). In the context of previously proposed approaches, the interior point method offers computational efficiency when compared to other methods (for instance, simplex-based approaches). In many cases, the interior point method allows additional constraints to be included into the formulation (specifically linear equality/inequality constraints and/or variable bounds) without affecting the solution methodology. Furthermore, the same interior point method is sufficient for both QP and LP formulations. Although the QP and LP formulations do not include performance driven constraints [23, 39] as presented, the interior point method is easily extensible to handle the inclusion of performance constraints used by many other researchers. Therefore, we consider the interior point method to be an efficient and more effective approach than many of those previously proposed. Additionally, it appears to be extensible to more difficult formulations.

This chapter is organized as follows. In Section 4.1, we describe the basic idea behind our primal-dual interior point method for solving the QP and LP relative placement formulations as previous described in Chapter 3. We demonstrate that the main computa-

tional burden of the interior point method is the solution of a sequence of large and sparse symmetric indefinite systems of linear equations. Therefore, in practical implementations efficient solution techniques for these systems of equations are required. In Section 4.2, we describe direct and iterative methods for solving these systems of equations. Iterative methods require more consideration than direct methods when implemented. Specifically, consideration is given to the generation of an effective preconditioning matrix when using an iterative method. Generation of a preconditioning matrix using established drop tolerance techniques is described in Section 4.3. In Section 4.4, numerical results are presented to demonstrate several aspects of the QP and LP relative placement formulations. The differences in the problem sizes and storage requirements for the QP and LP formulations are presented. These results confirm the observations made previously in Chapter 3, namely that the QP results in smaller problem sizes and require less storage than the LP formulation. Additionally, the QP formulation is solved more efficiently than the LP formulation. Finally, the potential benefits of iterative versus direct methods for solving the systems of equations arising during the interior point method are illustrated. A summary of this chapter is provided in Section 4.5.

# 4.1 A Primal-Dual Interior Point Method

As previously demonstrated, both relative placement formulations can be expressed in the form of the *primal* problem

minimize

$$c^T \mathbf{x} + \frac{1}{2} \mathbf{x}^T \mathbf{Q} \mathbf{x}$$

subject to  $\mathbf{A} \mathbf{x} + \mathbf{p} = \mathbf{b},$

$\mathbf{x} + \mathbf{s} = \mathbf{u},$

$\mathbf{x}, \mathbf{s}, \mathbf{p} \ge \mathbf{0},$

(4.1)

which has the associated dual problem

maximize

$$\mathbf{b}^T \mathbf{y} + \mathbf{u}^T \mathbf{w} - \frac{1}{2} \mathbf{x}^T \mathbf{Q} \mathbf{x}$$

subject to  $\mathbf{A}^T \mathbf{y} + \mathbf{w} + \mathbf{r}_1 - \mathbf{Q} \mathbf{x} = \mathbf{c},$

$\mathbf{w} + \mathbf{r}_2 = \mathbf{0},$  (4.2)

$\mathbf{y} + \mathbf{r}_3 = \mathbf{0},$

$\mathbf{r}_1, \mathbf{r}_2, \mathbf{r}_3 \ge \mathbf{0},$

where Q is an  $n \times n$  symmetric semi-definite matrix ( $Q \ge 0$ ), A is an  $m \times n$  constraint matrix, c and u are *n*-vectors, b is an *m*-vector, and x is an *n*-vector of unknowns. For this primal-dual pair of problems,  $Q \ne 0$  implies the QP formulation whereas Q = 0 implies the LP formulation of the relative placement problem.

The primal-dual interior point method is derived by applying a logarithmic barrier function to either (or both) the primal or dual problems in order to eliminate the nonnegativity constraints. Assuming a solution that satisfies

$$\{(\mathbf{x}, \mathbf{s}, \mathbf{p}, \mathbf{y}, \mathbf{w}, \mathbf{r}_1, \mathbf{r}_2, \mathbf{r}_3) : \mathbf{x}, \mathbf{s}, \mathbf{p}, \mathbf{r}_1, \mathbf{r}_2, \mathbf{r}_3 > 0\}$$

(4.3)

is provided, the first order conditions for simultaneous optimality for the primal and dual

barrier problems are:

$$Ax + p = b$$

$$x + s = u$$

$$A^{T}y + w + r_{1} - Qx = c$$

$$w + r_{2} = 0$$

$$y + r_{3} = 0$$

$$XR_{1} = \mu e$$

$$SR_{2} = \mu e$$

$$PR_{3} = \mu e$$

where e denotes a vector of ones, and  $\mu > 0$  is the penalty parameter for the logarithmic barrier problems. The first two equations represent primal feasibility and the following three equations represent dual feasibility. The final three equations represent the  $\mu$ -complementarity conditions, and in these equations an upper case letter denotes a diagonal matrix with components of the corresponding lower case vector on its diagonal.

Assuming an initial solution satisfying (4.3) is provided, one step of Newton's method is used to to find a solution closer the solution of the first order optimality conditions. This new solution becomes the current solution and the penalty parameter  $\mu$  is reduced appropriately. This procedure is continued until  $\mu$  is sufficiently close to zero. When  $\mu$ is reduced sufficiently, it follows from the first order optimality conditions that the final solution is both primal feasible, dual feasible, and optimal for the primal-dual pair of problems in (4.1)-(4.2).

The primal-dual algorithm is therefore an iterative procedure where each iteration requires application of Newton's method to determine a search direction for updating the solution. To determine the search direction, Newton's method requires the solution of the augmented equations (the derivation of this system of equations is provided in Appendix

A) given by

$$\begin{bmatrix} -\mathbf{E} & \mathbf{A}^{T} \\ \mathbf{A} & \mathbf{F} \end{bmatrix} \begin{bmatrix} \mathbf{s}_{1} \\ \mathbf{s}_{2} \end{bmatrix} = \mathbf{K} \begin{bmatrix} \mathbf{s}_{1} \\ \mathbf{s}_{2} \end{bmatrix} = \begin{bmatrix} \zeta_{1} \\ \zeta_{2} \end{bmatrix}.$$

(4.5)

The matrices **E** and **F** are symmetric positive definite matrices,  $[\mathbf{s}_1, \mathbf{s}_2]^T$  represents the search direction, and  $[\zeta_1, \zeta_2]^T$  is some right-hand side vector. This system of equations is sparse, symmetric and indefinite. The sparsity pattern of **E** is identical to the sparsity pattern of **Q** when  $\mathbf{Q} \neq \mathbf{0}$ , otherwise it is diagonal. In both cases, **F** is diagonal. The solution of the augmented equations represents the main computational burden of each iteration of an interior point method. Efficient solution techniques for the augmented equations are required for efficient implementations of an interior point method. Further details regarding interior point methods, including methods for reducing the penalty parameter, termination criteria, and so forth can be found in [45].

# 4.2 Solving the Augmented Equations

Since each iteration of the interior point method is dominated by the solution of the augmented equations, it is necessary to consider efficient methods for their solution. We briefly note that it is not necessary to work with the augmented equations directly. We can either eliminate  $s_1$  from (4.5) and solve the reduced system of equations

$$(\mathbf{A}\mathbf{E}^{-1}\mathbf{A}^T + \mathbf{F})\mathbf{s}_2 = \zeta_2 + \mathbf{A}\mathbf{E}^{-1}\zeta_1 \tag{4.6}$$

for  $s_2$ , or eliminate  $s_2$  and solve the reduced system of equations

$$(\mathbf{A}^T \mathbf{F}^{-1} \mathbf{A} + \mathbf{E}) \mathbf{s}_1 = \mathbf{A}^T \mathbf{F}^{-1} \zeta_2 - \zeta_1$$

(4.7)

for  $s_1$ . Both of these reduced systems of equations are symmetric and positive-definite, and can be solved using any appropriate direct or iterative method [19]. In many cases, the reduced systems of equations suffer more fill than the augmented equations during a matrix factorization. Moreover, it is necessary to explicitly form the reduced systems of equations, If one uses the reduced system of equations in (4.6), it is necessary calculate the inverse of **E** which may not be easy when it has a non-diagonal sparsity pattern. If one uses the reduced system of equations in (4.7), the resulting matrix has a sparsity pattern identical to that of  $A^T A$ . For the relative placement problem, this matrix is very dense (totally dense at the beginning of the algorithm) since the first moment constraints become dense columns in the matrix  $A^T$ . Hence, we prefer to work directly with the augmented equations.

#### 4.2.1 Direct Methods