# Design of a Flexible and Modular Test Bed for Studies on Islanded Microgrids

by

Marten Pape

A thesis

presented to the University of Waterloo in fulfillment of the thesis requirement for the degree of Master of Applied Science

in

Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2015

© Marten Pape 2015

## **AUTHOR'S DECLARATION**

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

### Abstract

The last two decades in the electric power sector have been increasingly dominated by a rising interest in the integration of distributed energy resources (DERs) into electric power systems, many of them based on renewable energies. A wider-scale deployment of DERs raises questions in the design, planning and operation of electricity grids. In particular, the operational paradigms of distribution grids are about to change significantly.

One way proposed for putting small-scale DERs into the heart of an electric power system is through realizing "Microgrids". The concept of Microgrids proposes methods to allow participation of DERs in main and ancillary services on the level of distribution grids.

To foster research and development in the fields of Microgrids and grid-connected power electronic converters, test beds with adequate functionality are required. Around the world, many test beds have been created to allow experimentation and collection of experiences using full-scale, real equipment and fixed network layouts. However, these test beds are expensive, costly and large, and do not offer a high flexibility for reconfiguration.

Therefore, this thesis proposes, implements and evaluates a Microgrid test bed using the Hardware-in-the-loop approach to simulate the behavior of different types of generation, energy storage and loads in a Microgrid. Identical power electronic converter modules are used to generate the currents, voltages and powers required to imitate the AC-bus grid connection of such grid participants. Software models govern converter control and plant simulation, allowing for a fast and flexible reconfiguration of the entire test bed. This approach heavily cuts down cost, size and weight of test beds and allows a much more flexible and reproducible creation and execution of test scenarios.

### Acknowledgements

First of all, I would like to express my deepest gratitude to my supervisor, Dr. Mehrdad Kazerani. Without his steady and generous support, empathy, guidance and confidence, this thesis project could not have come to anywhere close to this. I am very happy to have had the chance to learn, experience and try many aspects of academic and practical life during this time. His thoughts, encouragement and trust have been inspiring countless times. Also, I thank Dr. Bhattacharya and Dr. Salama for providing feedback to this thesis.

I want to thank Mahmoud Allam for being such a great support as a colleague and as a friend. He has dedicated many hours in designing and implementing the CAN protocol stack that this thesis required. He also volunteered to take over the lead in assembling the fourth simulation module. We spent countless hours in the lab to discuss and reflect ideas, problems, concepts, cultures and life. The work in the lab wouldn't even have been half of the fun if he wouldn't have been around.

I want to thank, Danni Luo, who has taken a lead in the assembly of the third simulation module; Wenbao Hou who has helped me in quickly switching from one Microcontroller hardware to another when it became necessary and with the assembly of the AC breaker boxes; Zuher Alnasir, Elham Karimi and Jordan Morris for all the fun times and input in the past years and for being in the lab at any unreasonable hour to play 'the high-voltage backup guy' role.

Finally, I am grateful for great artists that stimulated great inspiration, relief, concentration and joy. Especially, I would like to thank for your presence and work to: Herman van Veen, Avishai Cohen, Chick Corea, Diana Krall, Habanot Nechama, John Surman,

Jan Gabarek, Stephan Micus, Xavier Rudd, Ketil Bjørnstad, David Darling, Xavier Naidoo, Trygve Seim, Norah Jones, Thomas Carbou, Sting, Bobby McFerrin, Anúna and Maybebop. Life is full of art and spirit. There is no life without it.

### Dedication

"We did not inherit this world from our parents ...

We are borrowing it from our children."

It is my fervent hope that the engineers, scientists, politicians, policy makers and ordinary people of today will dedicate themselves to the creation of a world where children and grandchildren will be left with air they can breathe and water they can drink, where humans and the rest of nature will nurture one another.

In dependence on Robert A. Messenger and Jerry Ventre – Photovoltaic Systems Engineering, Third Edition, CRC Press, 2010

To Heather, who has such an incredible sense for this air we breathe, the water we drink and our neighbors on earth; no matter how tiny or huge.

# Table of Contents

| AUTI   | HOR'   | S DECLARATION                                               | ii          |

|--------|--------|-------------------------------------------------------------|-------------|

| Abstr  | act    |                                                             | iii         |

| Ackno  | owled  | gements                                                     | iv          |

| Dedic  | ation  |                                                             | vi          |

| Table  | of C   | ontents                                                     | vii         |

| List o | of Fig | ures                                                        | xiv         |

| List o | of Tab | les                                                         | XX          |

| Chap   | ter 1  | Introduction                                                | 1           |

| 1.1    | Mo     | tivation                                                    | 1           |

| 1      | .1.1   | Research on Microgrids                                      | 1           |

| 1      | .1.2   | Test beds in research and development                       | 3           |

| 1      | .1.3   | Required test environments for the advancement of Microgra  | ids and its |

| comp   | onen   | ts                                                          | 4           |

| 1.2    | Bac    | kground information                                         | 6           |

| 1      | .2.1   | Hardware-in-the-loop                                        | 6           |

| 1.3    | Exi    | sting test bed approaches                                   | 7           |

| 1.4    | Mic    | erogrid test bed goal definition                            | 9           |

| 1.5    | The    | esis organization                                           | 11          |

| Chap   | ter 2  | Background review                                           | 13          |

| 2.1    | Cor    | nmon converter topologies for low-voltage grid applications | 13          |

| 2.2    | Cor    | nverter output filter for grid-connected VSI                | 17          |

| 2.3    | Cor    | ntrol objectives for grid interfacing converters            | 18          |

| 2      | .3.1   | Grid-forming converters                                     | 19          |

| 2      | .3.2   | Grid-feeding / grid-following converters                    | 19          |

| 2      | .3.3   | Grid-supporting converters                                  | 20          |

| 2.4 Co    | ntrol in the synchronous reference frame                    | 22 |

|-----------|-------------------------------------------------------------|----|

| 2.4.1     | The abc-dq0 transformation                                  | 22 |

| 2.4.2     | The dq0 controller block                                    | 24 |

| 2.4.3     | Decoupling of d and q channels                              | 25 |

| 2.4.4     | Feed-forward terms                                          | 26 |

| 2.4.5     | Controller output limiting                                  | 26 |

| 2.5 Co    | ntrol in the stationary reference frame                     | 28 |

| 2.6 Ph    | ase-locked loops for grid application                       | 30 |

| 2.7 Vol   | ltage-source based droop control                            | 31 |

| 2.7.1     | Droop control for grid-supporting converters                | 31 |

| 2.7.2     | Virtual impedance                                           | 33 |

| 2.7.3     | Power droop decoupling due to X/R ratio                     | 34 |

| 2.7.4     | Negative sequence control                                   | 35 |

| 2.8 Co    | ntrol of direct parallel connected 3-phase inverters        | 37 |

| 2.8.1     | Using $\Delta Y$ transformers                               | 37 |

| 2.8.2     | Using four converter legs and zero sequence current control | 39 |

| Chapter 3 | Test bed system structure design                            | 46 |

| 3.1 Sys   | stem component arrangement                                  | 46 |

| 3.1.1     | System component sizing                                     | 49 |

| 3.1.2     | AC Microgrid voltage                                        | 50 |

| 3.1.3     | DC-bus voltage                                              | 50 |

| 3.1.4     | Communication link                                          | 51 |

| Chapter 4 | Simulation module hardware design                           | 53 |

| 4.1 Sim   | nulation module structure                                   | 53 |

| 4.2 Pov   | wer circuit design                                          | 54 |

| 421       | Power switches                                              | 55 |

| 4.2.2        | Controllable breakers                                                   | . 58 |

|--------------|-------------------------------------------------------------------------|------|

| 4.2.3        | Converter output filter                                                 | . 59 |

| 4.3 Con      | ntrol circuit design                                                    | . 60 |

| 4.3.1        | Sensors                                                                 | . 60 |

| 4.3.2        | Simulation module control unit (SMCU) – Microcontroller                 | . 63 |

| 4.3.3        | Low voltage power supply                                                | . 65 |

| 4.4 Der      | rivation of a DC-bus voltage controller module                          | . 65 |

| 4.4.1        | Requirements                                                            | . 65 |

| 4.4.2        | Module structure                                                        | . 66 |

| 4.4.3        | Control of DC-bus voltage                                               | . 69 |

| 4.4.4        | Simulation results                                                      | . 71 |

| 4.5 Me       | chanical setup of Microgrid test bed                                    | . 74 |

| 4.6 Cos      | st analysis                                                             | . 76 |

| 4.7 Des      | sign summary                                                            | . 76 |

| Chapter 5    | Grid interfacing control topologies                                     | . 77 |

| 5.1 Inte     | erface definition for grid interfacing control topologies (Hardware-in- | the- |

| loop interfa | ce)                                                                     | . 78 |

| 5.1.1        | Energy conversion system to grid interface                              | . 78 |

| 5.1.2        | Software interface: control topology to inverter                        | . 82 |

| 5.2 Gri      | d following controller                                                  | . 82 |

| 5.2.1        | Control objective                                                       | . 82 |

| 5.2.2        | Common use                                                              | . 82 |

| 5.2.3        | Realization                                                             | . 83 |

| 5.2.4        | Simulation results                                                      | . 86 |

| 5.3 Vol      | tage-source based droop controller                                      | . 88 |

| 5.3.1        | Control objective                                                       | . 88 |

| 5.    | .3.2    | Common use                                     | . 88 |

|-------|---------|------------------------------------------------|------|

| 5.    | .3.3    | Realization                                    | . 88 |

| 5.    | .3.4    | Simulation results                             | . 92 |

| 5.4   | Cur     | rent-source based droop controller             | . 97 |

| 5.    | .4.1    | Control objective                              | . 97 |

| 5.    | .4.2    | Common use                                     | . 97 |

| 5.    | .4.3    | Realization                                    | . 97 |

| 5.    | .4.4    | Simulation results                             | 101  |

| Chapt | ter 6   | Load and generation plant modelling            | 103  |

| 6.1   | Intr    | oduction                                       | 103  |

| 6.2   | Loa     | d model                                        | 104  |

| 6.3   | Pho     | otovoltaic plant model                         | 105  |

| 6.    | .3.1    | Objective and simplifications                  | 105  |

| 6.    | .3.2    | Model structure                                | 105  |

| 6.    | .3.3    | Mathematical formulation                       | 108  |

| 6.    | .3.4    | Implementation                                 | 116  |

| 6.4   | Sto     | rage plant model                               | 116  |

| 6.    | .4.1    | Objective                                      | 116  |

| 6.    | .4.2    | Mathematical formulation                       | 117  |

| Chapt | ter 7 ' | Test bed simulation using a circuit simulator  | 120  |

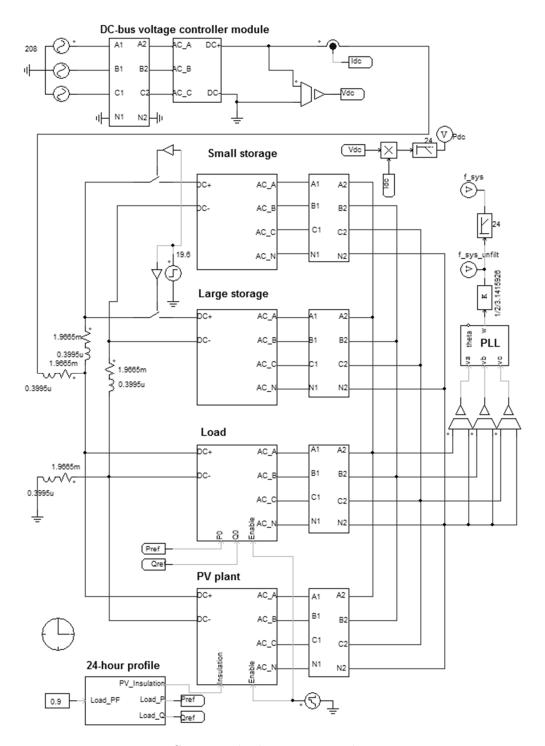

| 7.1   | Sim     | ulation setup                                  | 121  |

| 7.2   | Loa     | d and solar insolation profiles                | 123  |

| 7.3   | Res     | ults                                           | 123  |

| Chapt | ter 8   | Software design for simulation module firmware | 127  |

| 8.1   | Des     | ign goals and design principles                | 127  |

| 8.2   | Rev     | iew: software design patterns                  | 129  |

| 8.2.1     | Hardware proxy pattern                            | 129 |

|-----------|---------------------------------------------------|-----|

| 8.2.2     | Hardware adapter pattern                          | 129 |

| 8.2.3     | Observer pattern                                  | 130 |

| 8.2.4     | Asynchronous, single-event receptor state machine | 132 |

| 8.3 Per   | formance considerations                           | 134 |

| 8.4 Co    | de portability                                    | 135 |

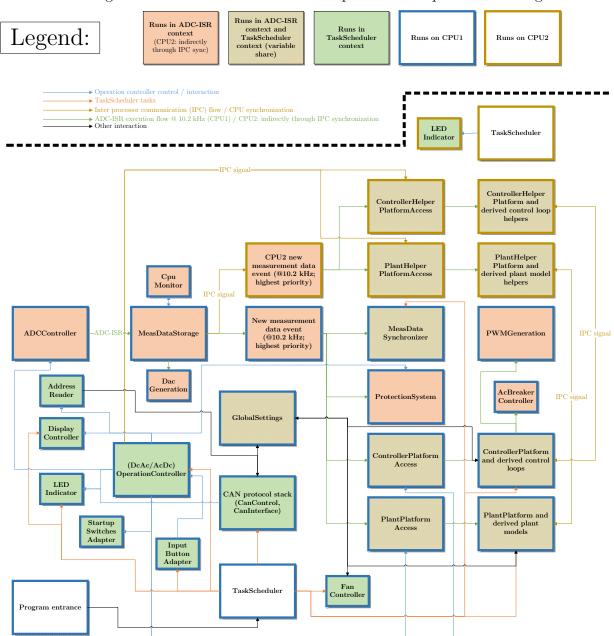

| 8.5 Imp   | plementation                                      | 137 |

| 8.5.1     | Hardware abstraction                              | 138 |

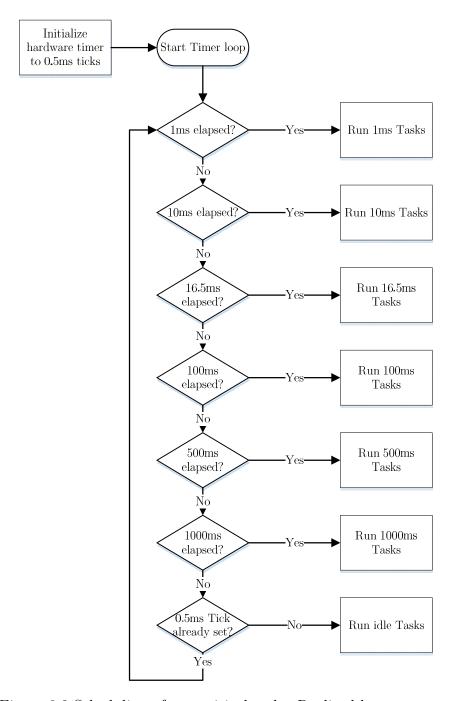

| 8.5.2     | Scheduling                                        | 138 |

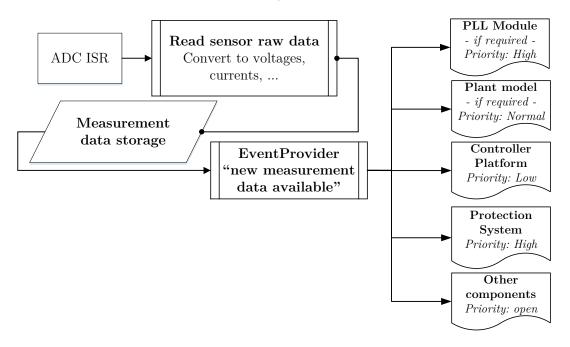

| 8.5.3     | Example: Control loop execution program flow      | 140 |

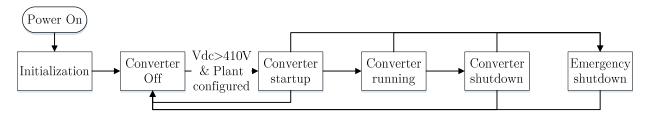

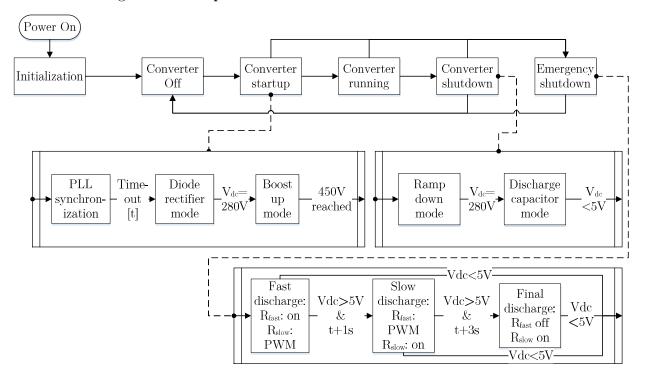

| 8.5.4     | Program state management                          | 141 |

| 8.5.5     | Global settings storage                           | 143 |

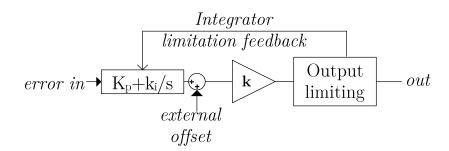

| 8.5.6     | Controller and plant model abstraction            | 144 |

| 8.5.7     | Software-based circuit protection                 | 146 |

| 8.5.8     | Additional software components                    | 147 |

| 8.5.9     | CAN communication                                 | 147 |

| 8.6 Sur   | nmary                                             | 149 |

| Chapter 9 | Software design: Test bed central controller      | 150 |

| 9.1 Des   | sign goals                                        | 150 |

| 9.2 Des   | sign patterns                                     | 151 |

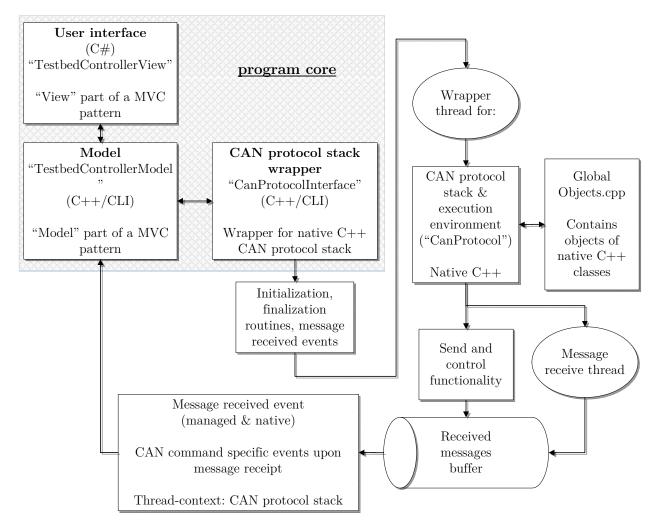

| 9.3 Arc   | chitectural choices                               | 152 |

| 9.3.1     | Programming language and framework                | 152 |

| 9.3.2     | Program module interfacing                        | 152 |

| 9.3.3     | Threading model                                   | 154 |

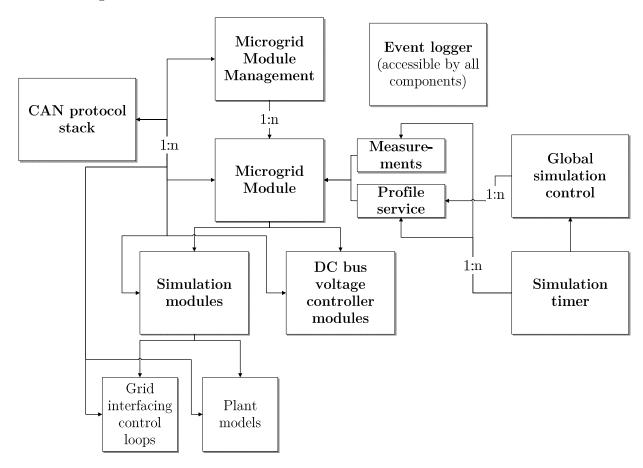

| 9.4 Imp   | plementation overview: Model                      | 155 |

| 9.4.1     | CAN communication                                 | 156 |

| 9.4.2     | MicrogridModule, SimulationModule, DcBusModule             | 156 |

|-----------|------------------------------------------------------------|-----|

| 9.4.3     | Microgrid module management                                | 157 |

| 9.4.4     | Grid interfacing control loops                             | 157 |

| 9.4.5     | Plant models                                               | 158 |

| 9.4.6     | Measurements                                               | 158 |

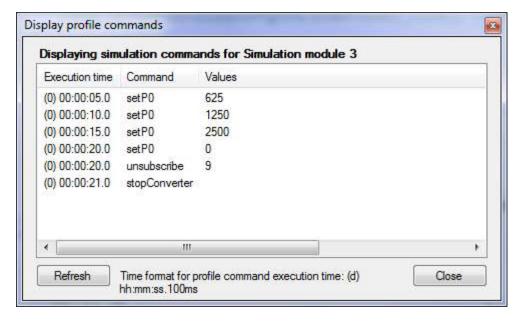

| 9.4.7     | Profile service, command file execution                    | 159 |

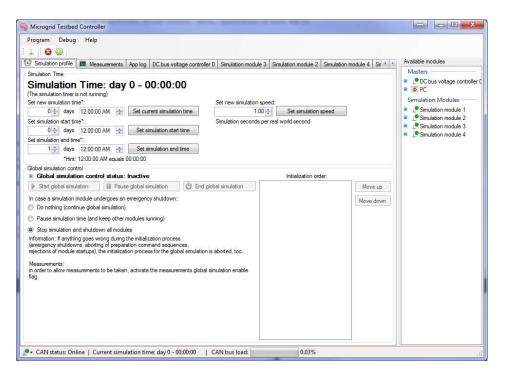

| 9.4.8     | Global simulation controller                               | 160 |

| 9.4.9     | Logging                                                    | 161 |

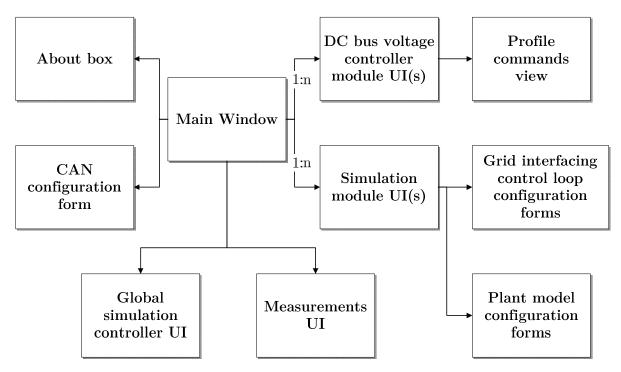

| 9.5 Im    | plementation overview: View                                | 162 |

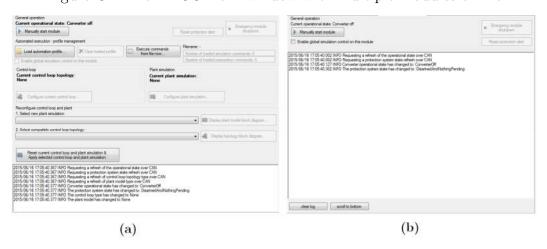

| 9.5.1     | Main window                                                | 162 |

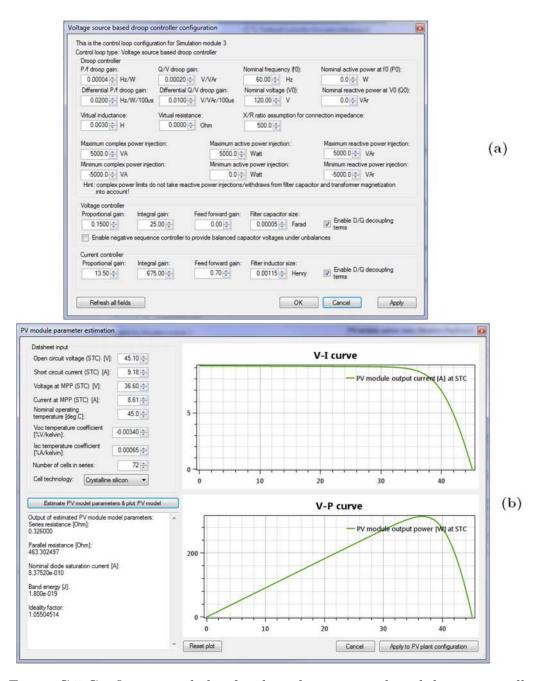

| 9.5.2     | SimulationModule, DcBusModule, control loops, plant models | 163 |

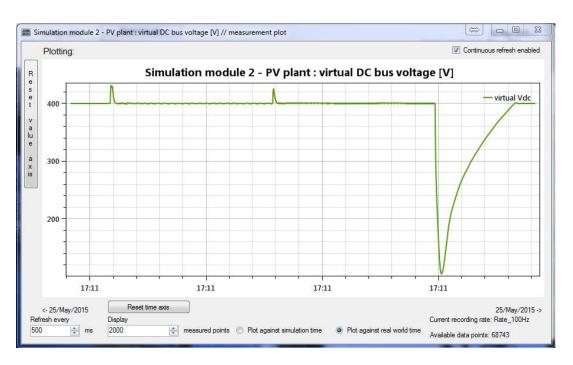

| 9.5.3     | Measurements, plotting                                     | 164 |

| 9.5.4     | Global simulation control                                  | 164 |

| 9.6 Int   | erfacing a secondary controller algorithm                  | 164 |

| 9.7 Su    | mmary                                                      | 165 |

| Chapter 1 | 0 Experimental results                                     | 166 |

| 10.1      | Grid-following converter                                   | 166 |

| 10.2      | Grid-supporting converter                                  | 170 |

| 10.2.1    | Voltage-source based droop controller                      | 170 |

| 10.2.2    | Current-source based droop controller                      | 177 |

| 10.3 I    | Load plant model                                           | 180 |

| 10.4 I    | Photovoltaic plant model                                   | 182 |

| 10.4.1    | Normal PV model operation                                  | 182 |

| 10.4.2    | Operation with PV curtailment                              | 184 |

| 10.5 I    | OC-bus voltage controller module                           | 187 |

| 10.6      | Simulation of a 24-hour grid scenario on the test bed      | 191 |

| 10.7      | Summary                                                               | 195  |

|-----------|-----------------------------------------------------------------------|------|

| Chapter   | 11 Conclusions                                                        | 196  |

| Chapter   | 12 Future work                                                        | 199  |

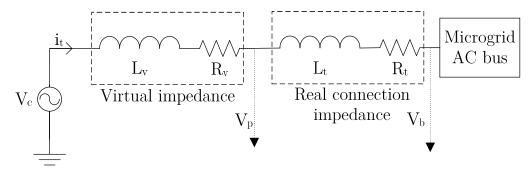

| A.1       | Virtual impedance in synchronous reference frame for voltage-source b | ased |

| droop cor | ntrollers                                                             | 201  |

| Bibliogra | aphy                                                                  | 254  |

# List of Figures

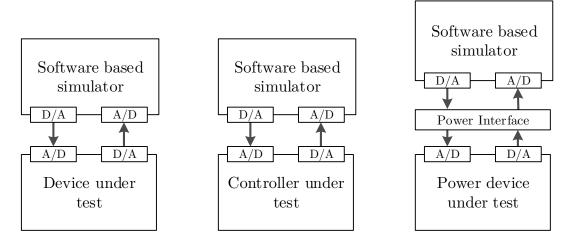

|     | Figure 1.1 General HIL, Controller HIL and Power HIL (left to right) [6]             | 7    |

|-----|--------------------------------------------------------------------------------------|------|

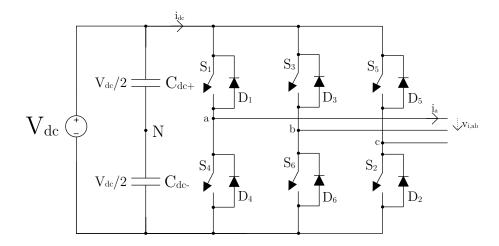

|     | Figure 2.1 Three-Phase voltage-source inverter topology                              | . 14 |

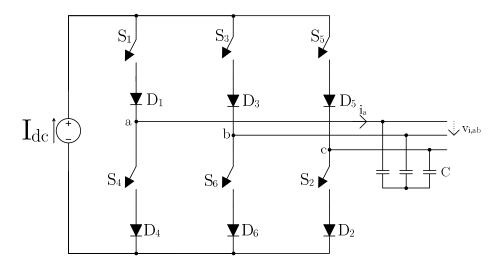

|     | Figure 2.2 Current-source inverter                                                   | . 16 |

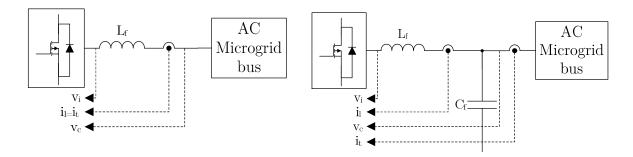

|     | Figure 2.3 L-filter                                                                  | . 17 |

|     | Figure 2.4 LC-filter                                                                 | . 17 |

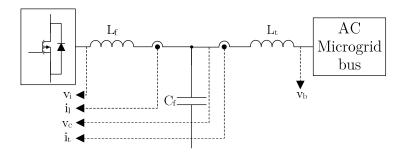

|     | Figure 2.5 LCL-filter                                                                | . 17 |

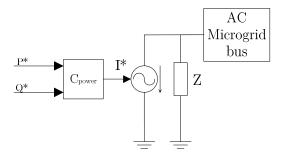

|     | Figure 2.6 Grid-forming controller representation                                    | . 19 |

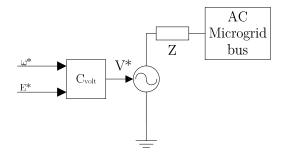

|     | Figure 2.7 Grid-feeding controller representation                                    | . 20 |

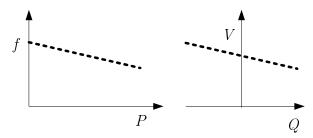

|     | Figure 2.8 Droop curves for P/f and Q/V droop                                        | . 21 |

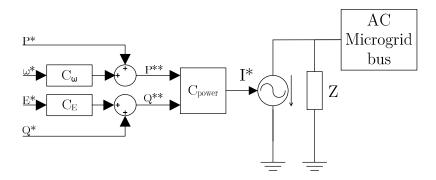

|     | Figure 2.9 Current-source based droop controller representation                      | . 22 |

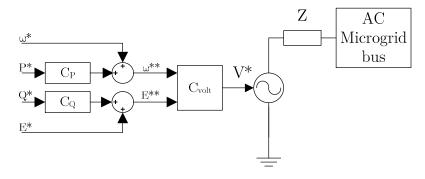

|     | Figure 2.10 Voltage-source based droop controller representation                     | . 22 |

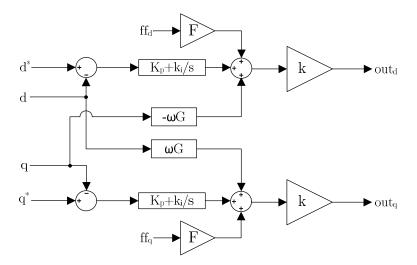

|     | Figure 2.11 dq0 controller block structure                                           | . 24 |

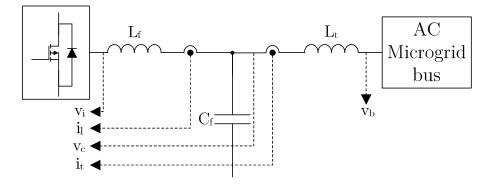

|     | Figure 2.12 Single phase representation of a converter output LCL filter             | . 25 |

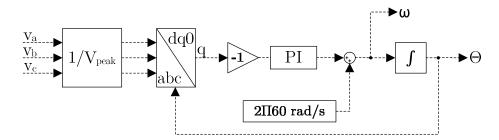

|     | Figure 2.13 Three-phase synchronous reference frame PLL structure                    | . 30 |

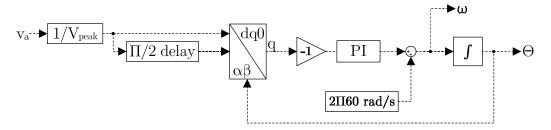

|     | Figure 2.14 Single-phase synchronous reference frame PLL structure                   | . 31 |

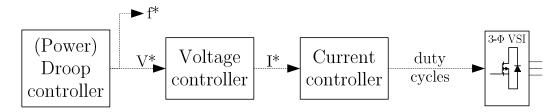

|     | Figure 2.15 General controller structure for voltage-source based droop contro       | llec |

| COI | nverters                                                                             | . 32 |

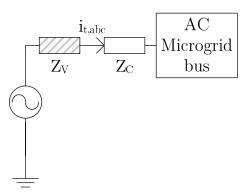

|     | Figure 2.16 Virtual impedance $ZV$                                                   | . 33 |

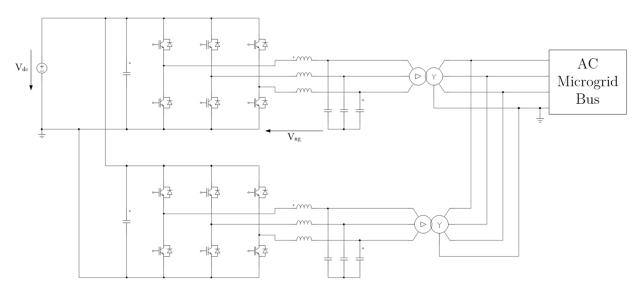

|     | Figure 2.17 Two direct parallel connected 3-phase VSIs using $\Delta Y$ transformers | . 37 |

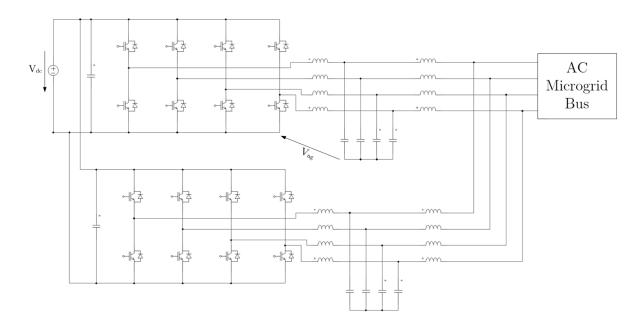

|     | Figure 2.18 Two direct parallel connected 3-phase VSIs with four legs and            | not  |

| tra | nsformer                                                                             | . 40 |

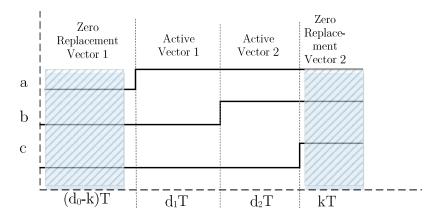

|     | Figure 2.19 ZSC current control based on modified SVM. Depicted: Instantane          | ous  |

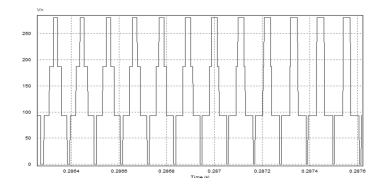

| leg | ; voltages between $Vdc$ and ground for one switching cycle in a three-leg inverter. | . 42 |

|     | Figure 2.20 <i>Vng</i> for traditional PWM for a single inverter                     | . 42 |

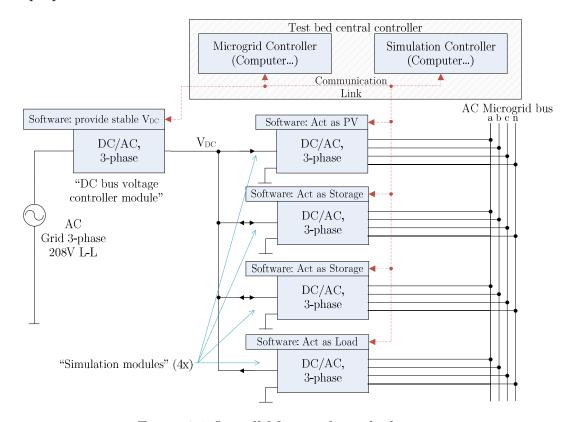

|     | Figure 3.1 Overall Microgrid test bed structure                                      | . 46 |

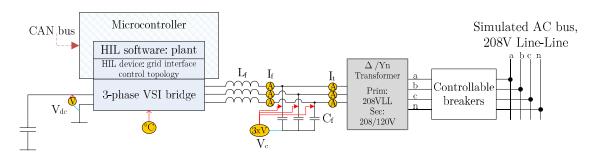

| Figure 4.1 Simulation module structure                                                 |

|----------------------------------------------------------------------------------------|

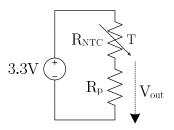

| Figure 4.2 NTC temperature sensing circuit                                             |

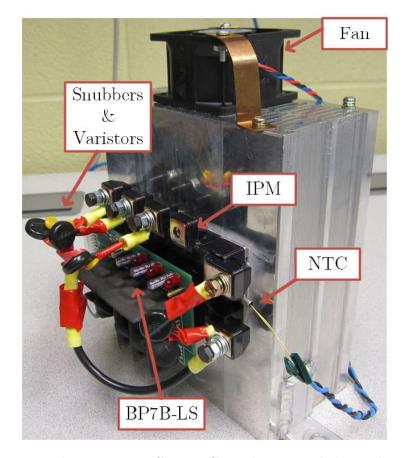

| Figure 4.3 Implementation IGBTs, IGBT drivers and thermal management 5                 |

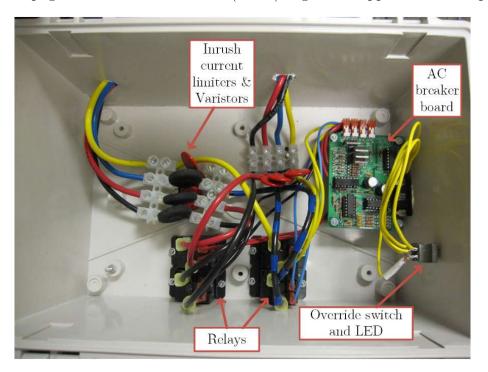

| Figure 4.4 AC breaker box (inside view)                                                |

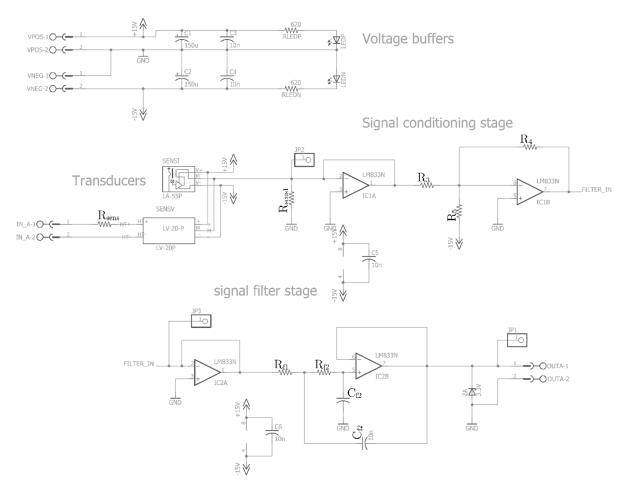

| Figure 4.5 Single-phase stage of three-phase sensor board                              |

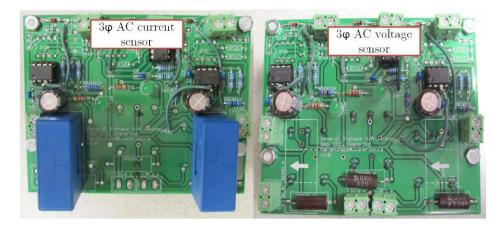

| Figure 4.6 AC sensor implementations. Some transducers on bottom side of PCB.6         |

| Figure 4.7 Microcontroller adapter board developed for TMS320F28377I                   |

| experimenter kit. Experimenter kit underneath adapter board                            |

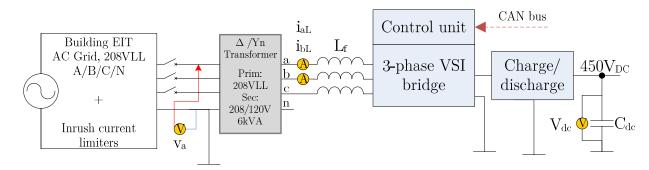

| Figure 4.8 DC-bus voltage controller module structure                                  |

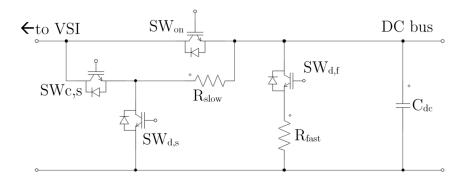

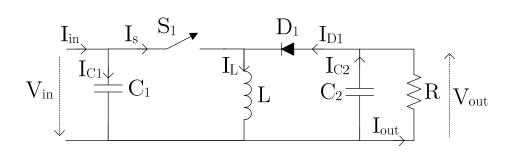

| Figure 4.9 DC-bus charge/discharge circuit                                             |

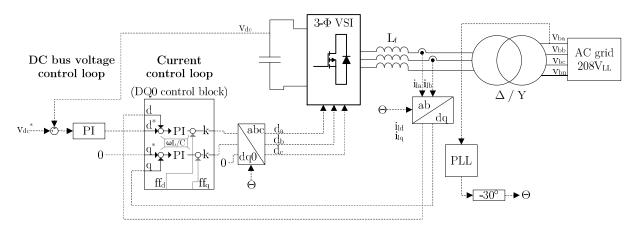

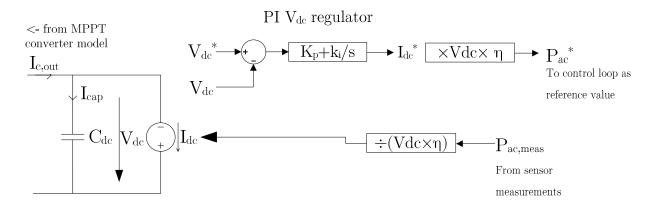

| Figure 4.10 Control loop topology of DC-bus voltage controller module 69               |

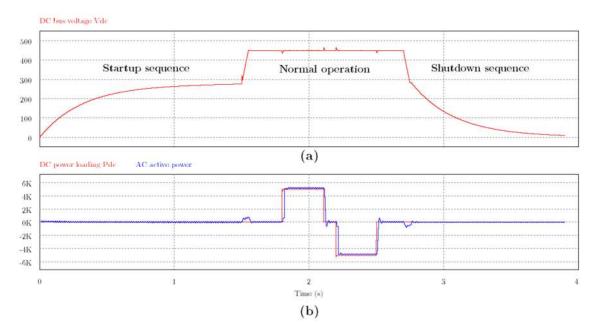

| Figure 4.11 DC-bus voltage controller module simulation: (a) $Vdc$ under full          |

| operation cycle; (b) AC power (blue) and DC power (red)                                |

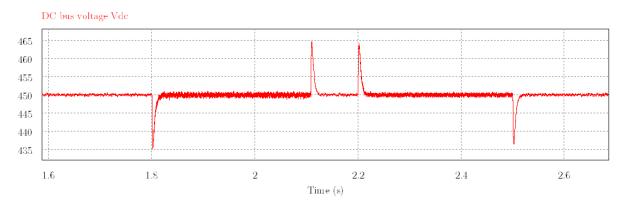

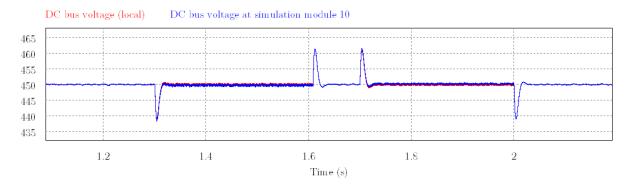

| Figure $4.12\ Vdc$ ripple and transients under no load and full load                   |

| Figure 4.13 $Vdc$ ripple and transients at simulation module 10 (blue) and at DC-bu    |

| voltage controller module (red, mostly hidden)                                         |

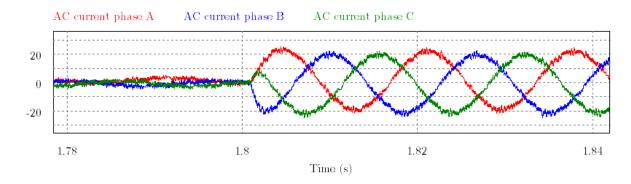

| Figure 4.14 AC currents when DC-side load goes through a step change from $0\%$ to     |

| 100% power rating                                                                      |

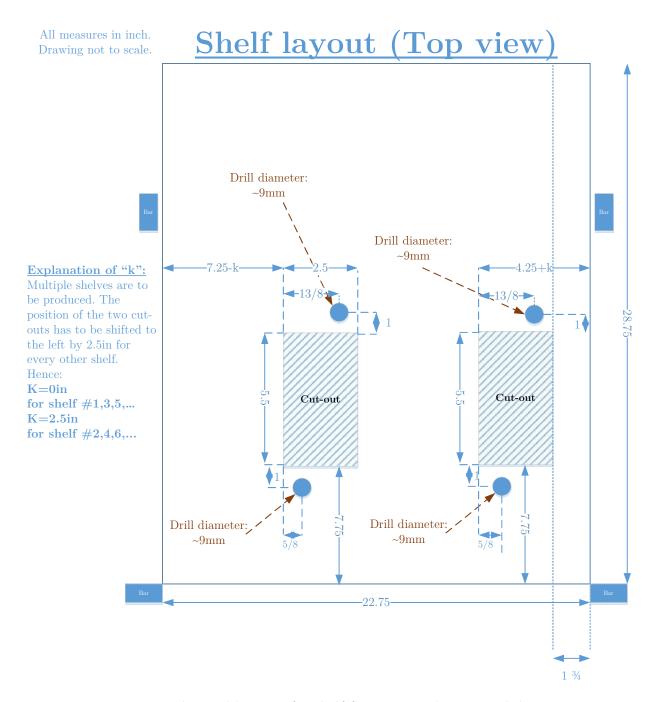

| Figure 4.15 Mechanical layout of a shelf for two simulation module converters 78       |

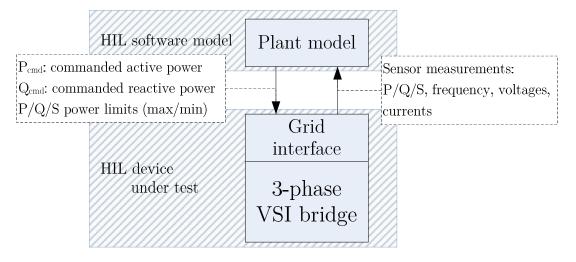

| Figure 5.1 Generalization of plant structures                                          |

| Figure 5.2 Definition of HIL interface between plant model and grid interface 8        |

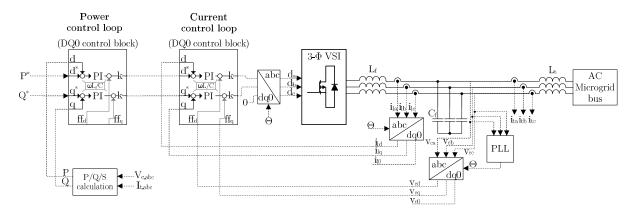

| Figure 5.3 Control loop structure using dq0 PI controllers for grid-following          |

| converters83                                                                           |

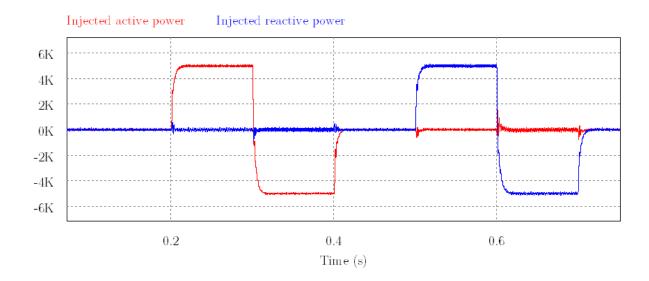

| Figure 5.4 Active and reactive power injection upon power reference steps for P $\&$ 0 |

| 8′                                                                                     |

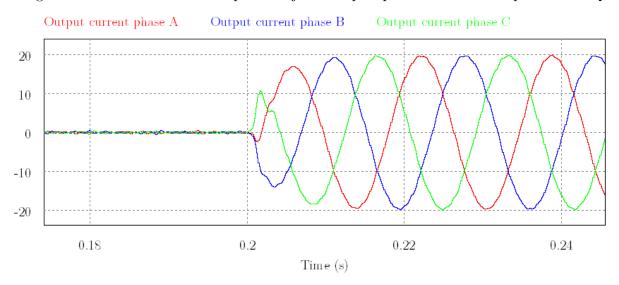

| Figure 5.5 Output currents $it, abc$ upon a reference step from P=0W to P=5000W        |

|----------------------------------------------------------------------------------------|

| (Q=0)                                                                                  |

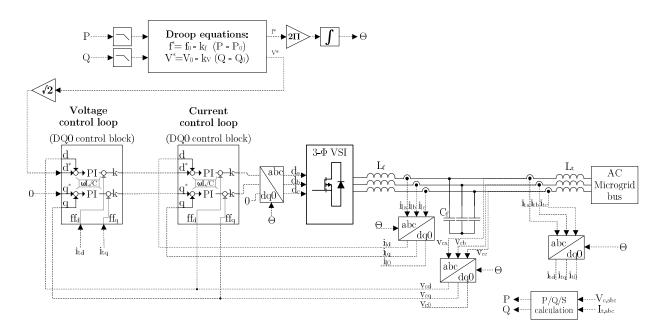

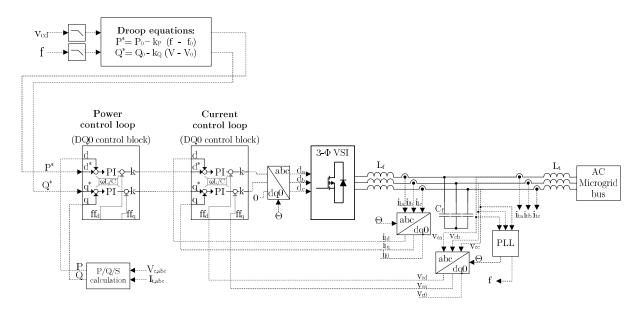

| Figure 5.6 Basic voltage-source based droop controller implementation                  |

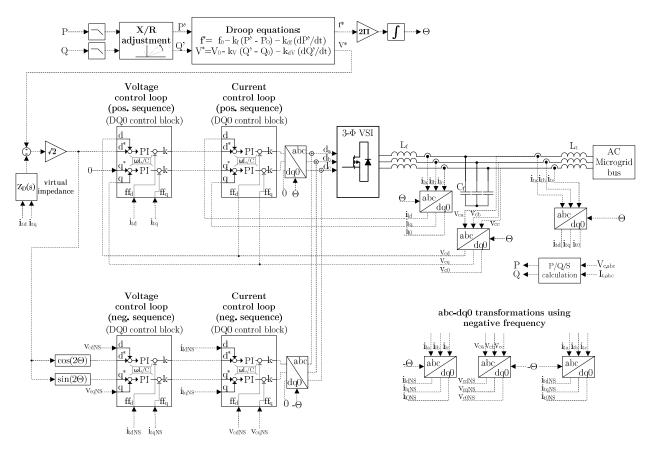

| Figure 5.7 Complete voltage-source based droop controller implementation 90            |

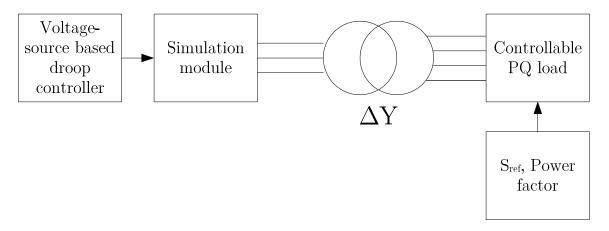

| Figure 5.8 Voltage-source based droop controller: stand-alone simulation block         |

| structure                                                                              |

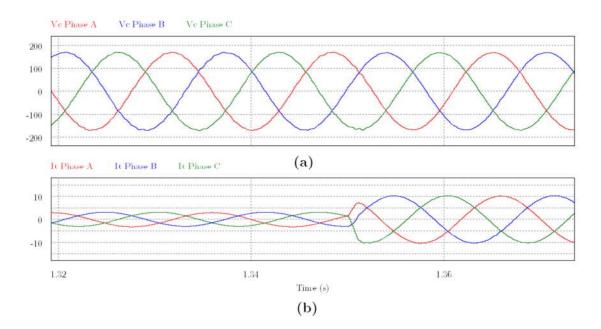

| Figure 5.9 Inverter capacitor voltages (a) and output currents (b) when PQ load step   |

| change from 0W to 2500W is performed                                                   |

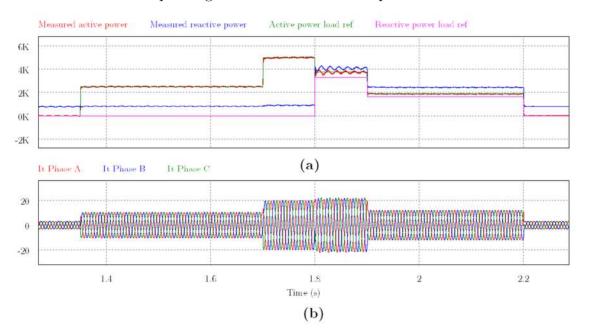

| Figure 5.10 Inverter output power and PQ power load references (a) and inverter        |

| output currents (b) for entire load schedule                                           |

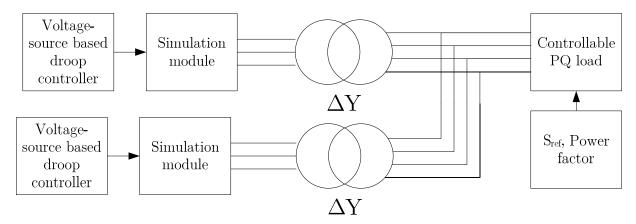

| Figure 5.11 Voltage-source based droop controller: power sharing simulation block      |

| structure                                                                              |

| Figure 5.12 Power sharing between two voltage-source droop controllers under           |

| varying load conditions                                                                |

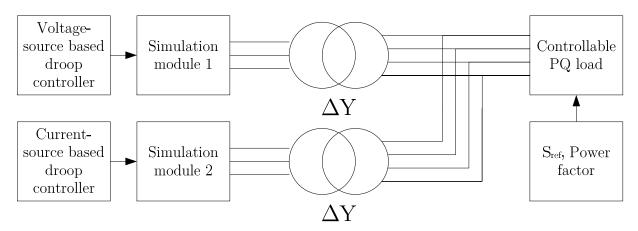

| Figure 5.13 Current-source based droop controller implementation                       |

| Figure 5.14 Simulation configuration                                                   |

| Figure 5.15 System parameters in a simulation with one voltage-source based droop      |

| controller (module 2) and one current-source based droop controller (module 1) in      |

| parallel                                                                               |

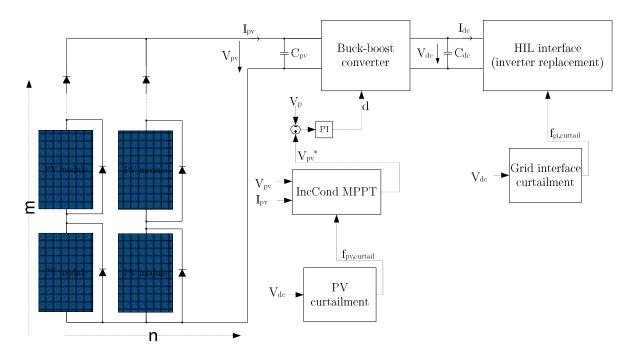

| Figure 6.1 Structure of the PV plant implemented                                       |

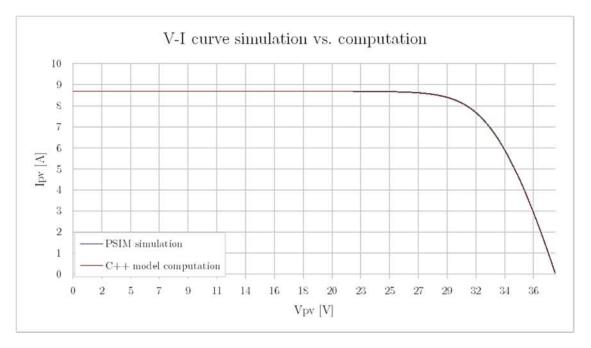

| Figure 6.2 PV model simulation in PSIM vs. computation in implemented C++              |

| model for Bosch c-SI M2453BB PV module111                                              |

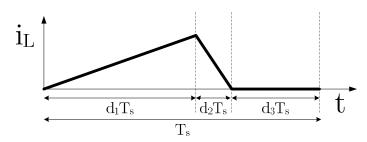

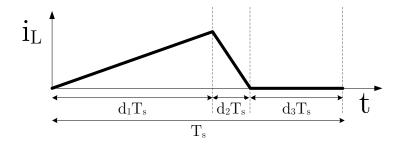

| Figure 6.3 Definition of $d1$ , $d2$ and $d3$ at the example of discontinuous inductor |

| current                                                                                |

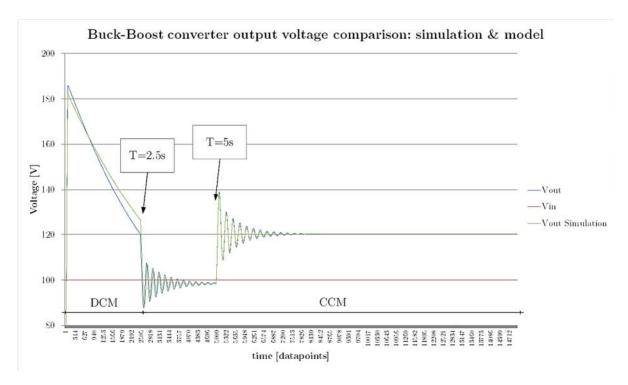

| Figure 6.4 Comparison of average model with circuit simulation. Blue: $Vout$ average   |

| model: red: Vin: Green: Vout PSIM simulation                                           |

| Figure 6.5 HIL grid interface block structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 115                                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

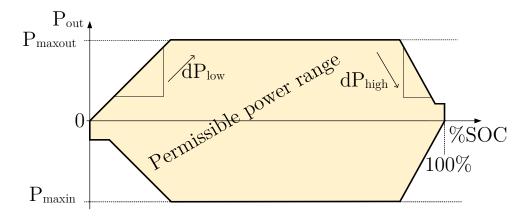

| Figure 6.6 Basic operation principle of generic storage plant                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 119                                                                       |

| Figure 7.1 PSIM test bed system simulation – main page                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 122                                                                       |

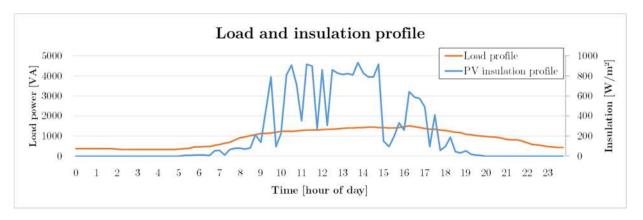

| Figure 7.2 Solar insolation and load profile for 24 hours                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 123                                                                       |

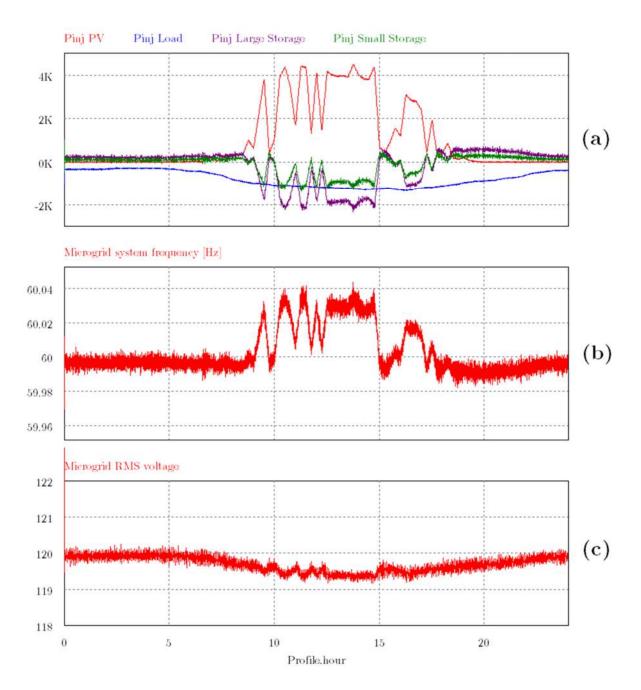

| Figure 7.3 Active power injections into grid (a), Microgrid system frequency (                                                                                                                                                                                                                                                                                                                                                                                                                                | b) and                                                                    |

| Microgrid RMS voltage (c) over the 24-hour profile                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 125                                                                       |

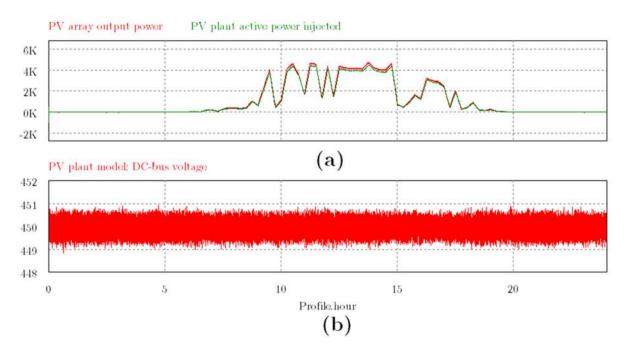

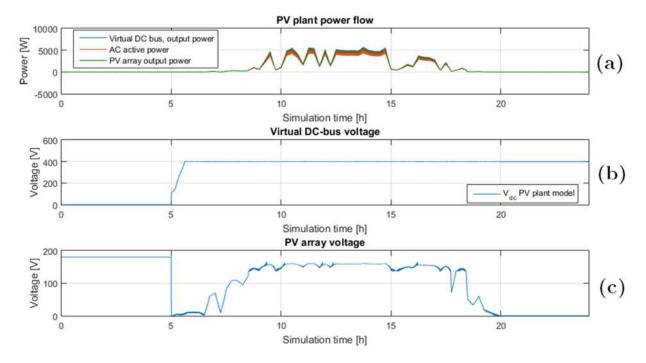

| Figure 7.4 PV plant model internal variables: power flow (a) and $Vdc$ (b)                                                                                                                                                                                                                                                                                                                                                                                                                                    | 126                                                                       |

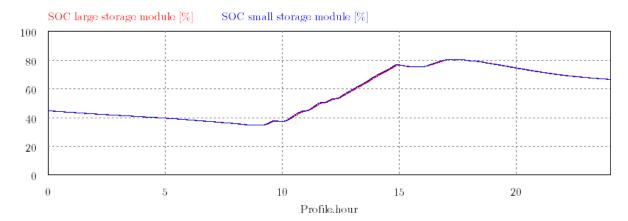

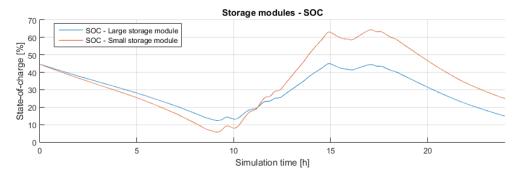

| Figure 7.5 SOC of both storage plants                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 126                                                                       |

| Figure 8.1 Program structure of SMCU firmware                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 137                                                                       |

| Figure 8.2 Scheduling of non-critical tasks. Realized by TaskScheduler                                                                                                                                                                                                                                                                                                                                                                                                                                        | 139                                                                       |

| Figure 8.3 Work flow ADC-ISR critical code execution                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 140                                                                       |

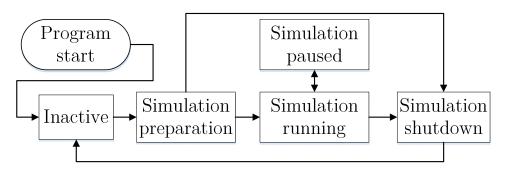

| Figure 8.4 DcAcOperationController states for simulation module                                                                                                                                                                                                                                                                                                                                                                                                                                               | 142                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | nodule                                                                    |

| Figure 8.5 AcDcOperationController states for DC-bus voltage controller n                                                                                                                                                                                                                                                                                                                                                                                                                                     | roaaro                                                                    |

| Figure 8.5 AcDcUperationController states for DC-bus voltage controller n                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                           |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 142                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 142<br>eternal                                                            |

| Figure 8.6 PI controller implementation with output limitation, scaling and ex                                                                                                                                                                                                                                                                                                                                                                                                                                | 142<br>eternal<br>145                                                     |

| Figure 8.6 PI controller implementation with output limitation, scaling and exoffset                                                                                                                                                                                                                                                                                                                                                                                                                          | 142<br>eternal<br>145<br>153                                              |

| Figure 8.6 PI controller implementation with output limitation, scaling and exoffset                                                                                                                                                                                                                                                                                                                                                                                                                          | 142<br>eternal<br>145<br>153<br>155                                       |

| Figure 8.6 PI controller implementation with output limitation, scaling and exoffset  Figure 9.1 TBCC software structure with focus on CAN protocol stack  Figure 9.2 TBCC 'model' block structure                                                                                                                                                                                                                                                                                                            | 142<br>eternal<br>145<br>153<br>155                                       |

| Figure 8.6 PI controller implementation with output limitation, scaling and exoffset  Figure 9.1 TBCC software structure with focus on CAN protocol stack  Figure 9.2 TBCC 'model' block structure  Figure 9.3 States of global simulation control                                                                                                                                                                                                                                                            | 142<br>eternal<br>145<br>153<br>155<br>160<br>162                         |

| Figure 8.6 PI controller implementation with output limitation, scaling and exoffset  Figure 9.1 TBCC software structure with focus on CAN protocol stack  Figure 9.2 TBCC 'model' block structure  Figure 9.3 States of global simulation control  Figure 9.4 TBCC 'view' block structure                                                                                                                                                                                                                    | 142<br>eternal<br>145<br>153<br>155<br>160<br>162<br>167                  |

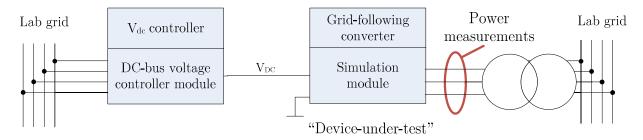

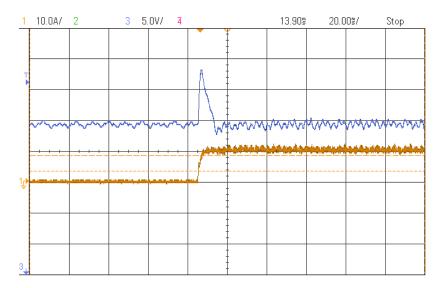

| Figure 8.6 PI controller implementation with output limitation, scaling and exoffset  Figure 9.1 TBCC software structure with focus on CAN protocol stack  Figure 9.2 TBCC 'model' block structure  Figure 9.3 States of global simulation control  Figure 9.4 TBCC 'view' block structure  Figure 10.1 Grid-following converter test configuration                                                                                                                                                           | 142<br>eternal<br>145<br>153<br>155<br>160<br>162<br>167<br>168           |

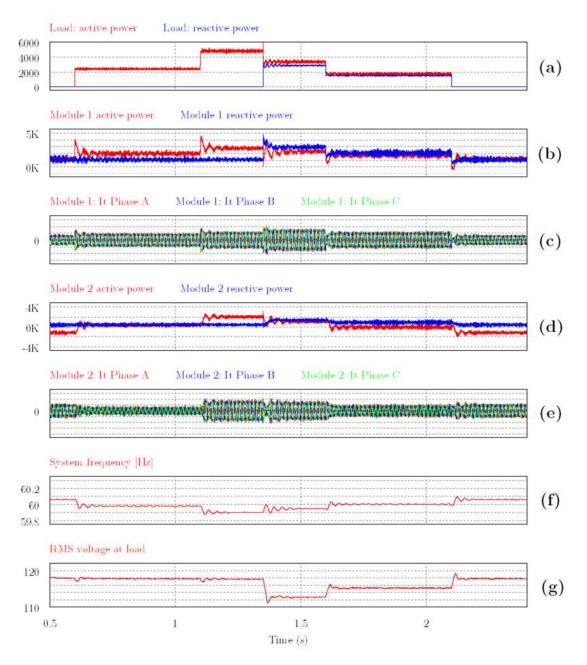

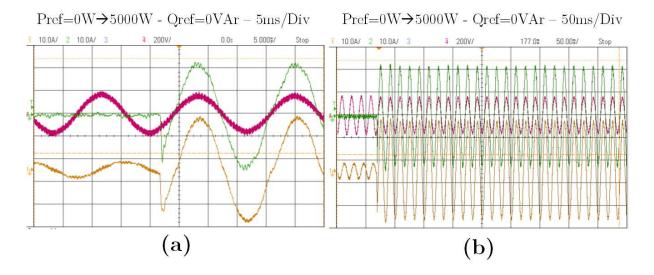

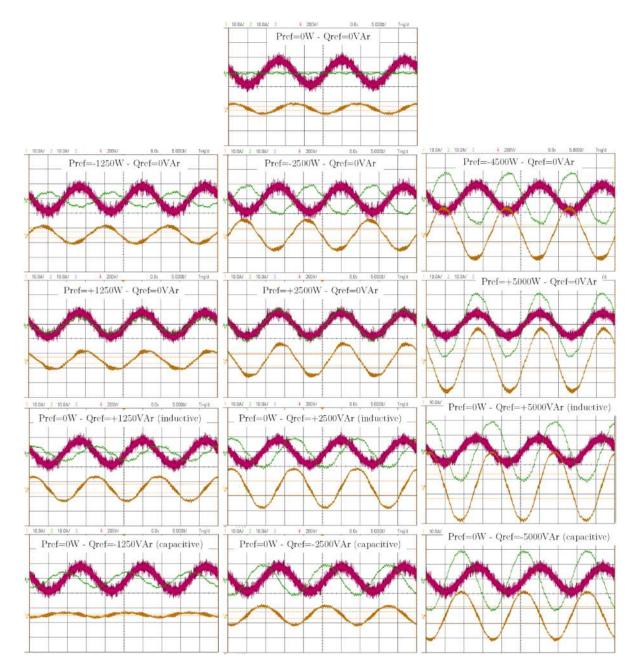

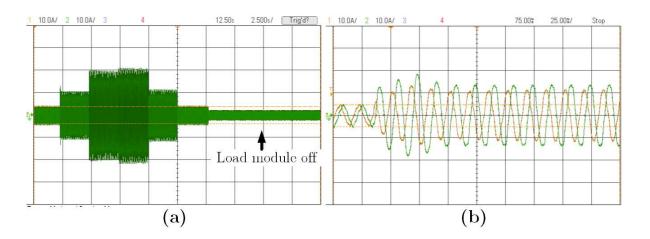

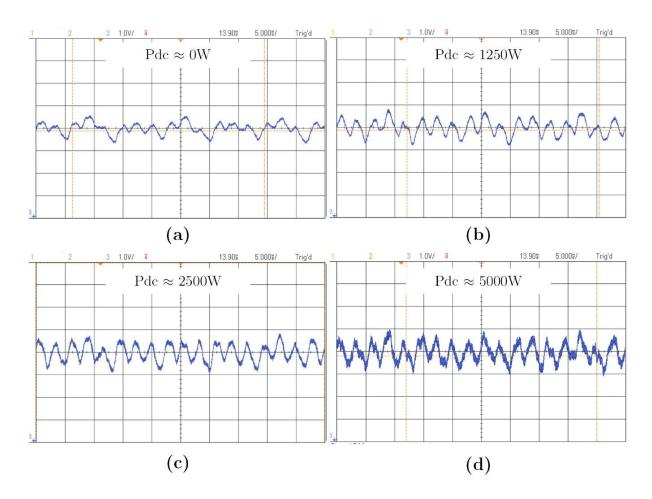

| Figure 8.6 PI controller implementation with output limitation, scaling and exoffset  Figure 9.1 TBCC software structure with focus on CAN protocol stack  Figure 9.2 TBCC 'model' block structure  Figure 9.3 States of global simulation control  Figure 9.4 TBCC 'view' block structure  Figure 10.1 Grid-following converter test configuration  Figure 10.2 Grid-following control topology: transient performance                                                                                       | 142<br>eternal<br>145<br>153<br>155<br>160<br>162<br>167<br>168<br>mance. |

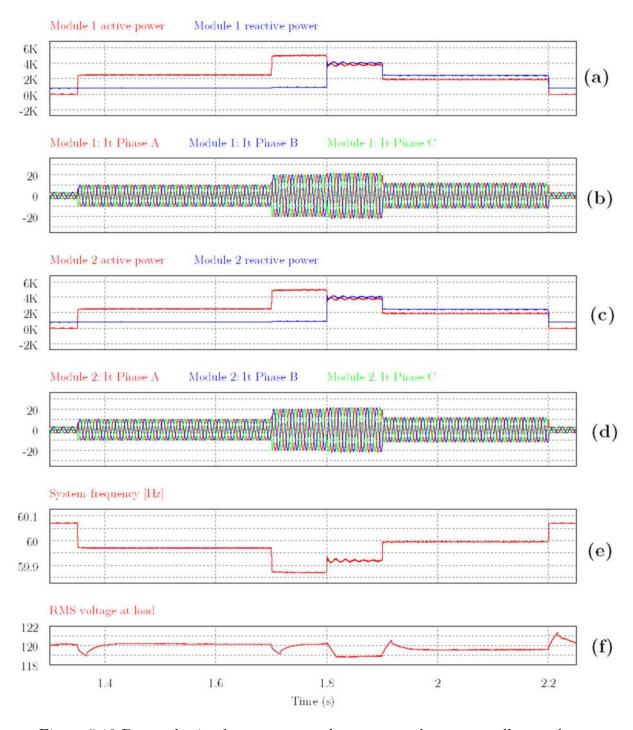

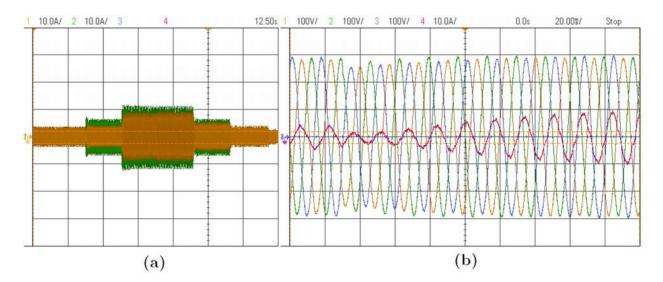

| Figure 8.6 PI controller implementation with output limitation, scaling and exoffset  Figure 9.1 TBCC software structure with focus on CAN protocol stack  Figure 9.2 TBCC 'model' block structure  Figure 9.3 States of global simulation control  Figure 9.4 TBCC 'view' block structure  Figure 10.1 Grid-following converter test configuration  Figure 10.2 Grid-following control topology: transient performance  Figure 10.3 Grid-following control topology: steady state, four quadrant performance | 142<br>eternal<br>145<br>153<br>160<br>162<br>167<br>168<br>mance.<br>169 |

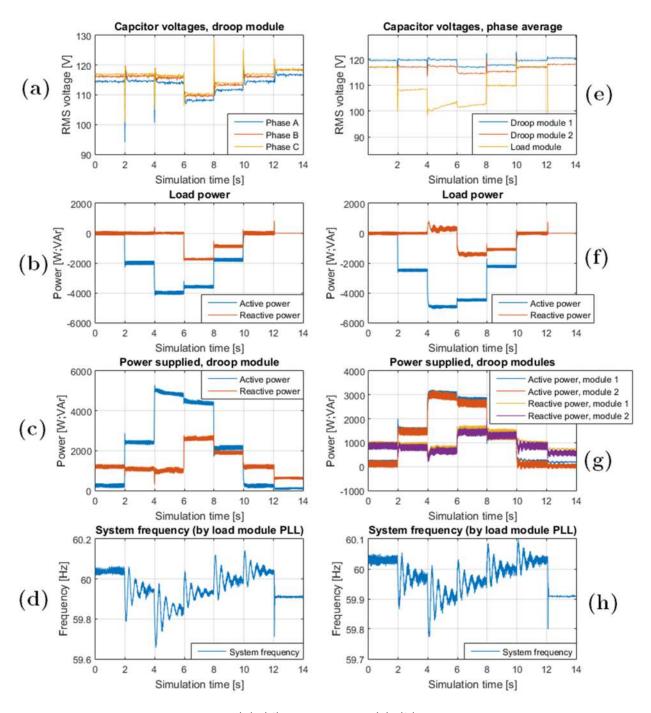

| Figure 10.5 Two voltage-source droop controlled modules in operation             | 174     |

|----------------------------------------------------------------------------------|---------|

| Figure 10.6 (a)-(d): test case 1. (e)-(h): test case 2                           | 175     |

| Figure 10.7 Voltage-source based droop controller voltages                       | 177     |

| Figure $10.8:it,ab$ for voltage-source based droop controlled module durin       | g load  |

| profile defined for test case 1                                                  | 178     |

| Figure 10.9 System voltage (a), frequency (b) and power flow (c)-(d) in a cr     | urrent- |

| source based droop and voltage-source based droop controlled islanded test grid. | 179     |

| Figure 10.10 Load plant model performance                                        | 181     |

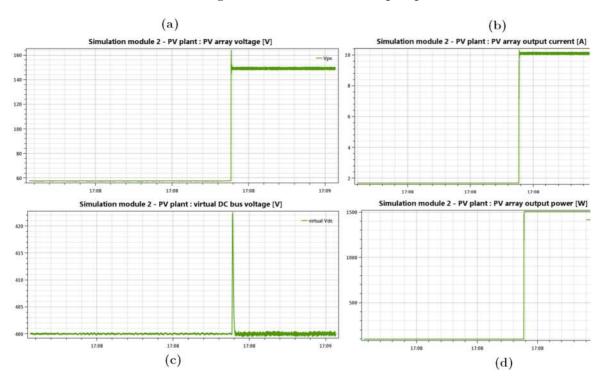

| Figure 10.11 PV plant model variables at a solar insolation step change          | e from  |

| $50 \ W/m2$ to $300 \ W/m2$                                                      | 183     |

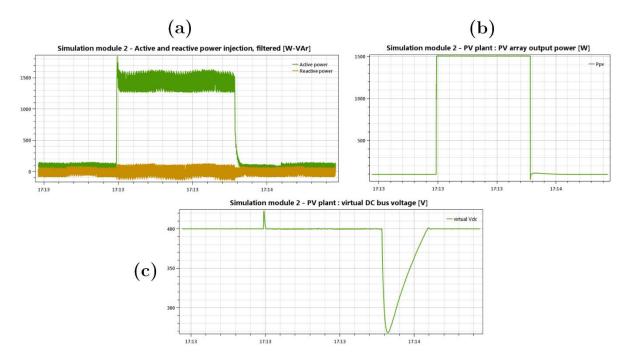

| Figure 10.12 Solar insolation step from 50 $W/m2$ to 300 $W/m2$ and back         | 184     |

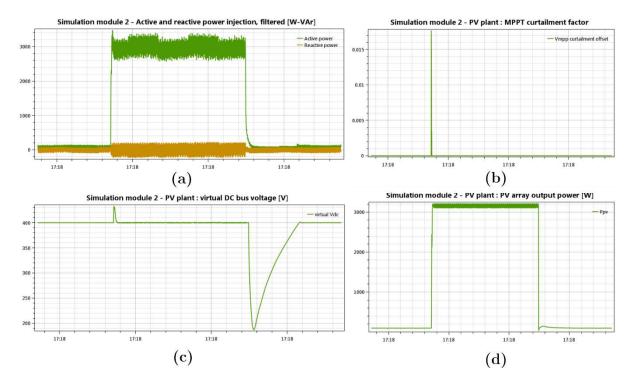

| Figure 10.13 Solar insolation step change from 50 $W/m2$ to 600 $W/m2$ and       | l back. |

| Pmax = 5000W                                                                     | 186     |

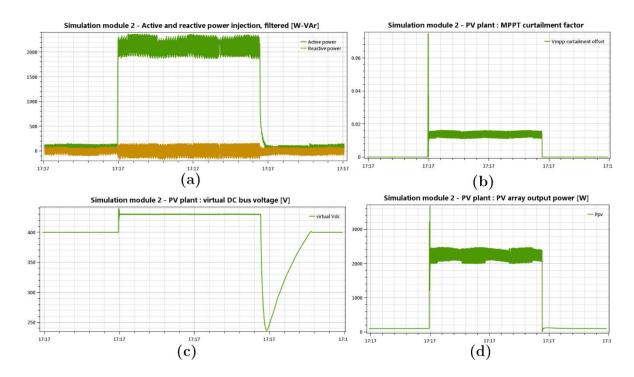

| Figure 10.14 Solar insolation step change from 50 $W/m2$ to 600 $W/m2$ and       | l back. |

| Pmax = 2000W                                                                     | 187     |

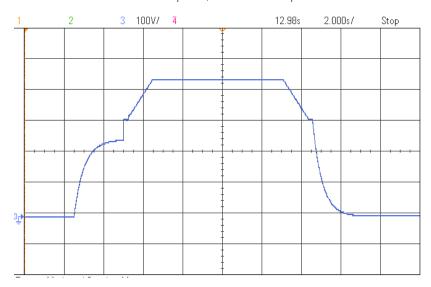

| Figure 10.15 DC-bus voltage ripples under different loading conditions           | 189     |

| Figure 10.16 DC-bus voltage (blue) during load power step change (0W to 50       | )00W).  |

|                                                                                  | 190     |

| Figure 10.17 DC-bus voltage during full operating cycle:                         | 190     |

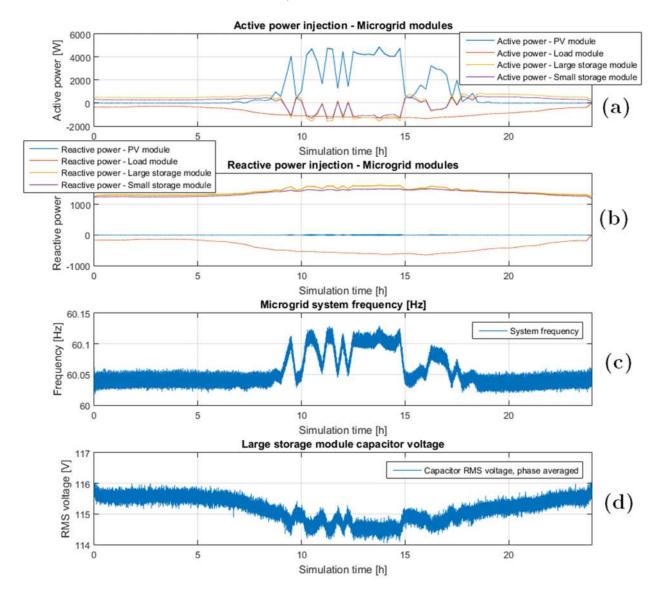

| Figure 10.18 24-hour simulation: power flows.                                    | 192     |

| Figure 10.19 24-hour simulation: PV plant variables                              | 193     |

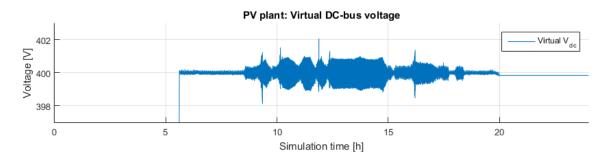

| Figure 10.20 24-hour simulation: PV plant DC-bus voltage (zoom)                  | 194     |

| Figure 10.21 24-hour simulation: storage module SOC during the day               | 194     |

| Figure A.1 Converter output circuit with virtual impedance                       | 201     |

| Figure A.2 VSI output filter circuit connected to AC Microgrid, single-line diagr       | am.  |

|-----------------------------------------------------------------------------------------|------|

|                                                                                         | .205 |

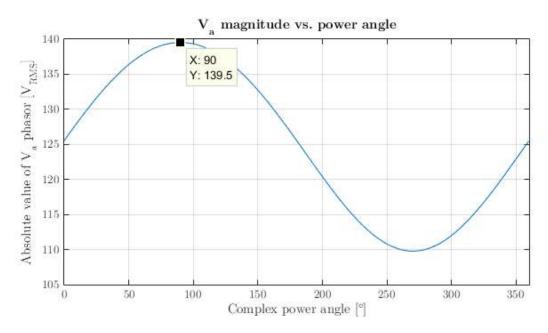

| Figure A.3 Required Va for different complex power injections                           | .206 |

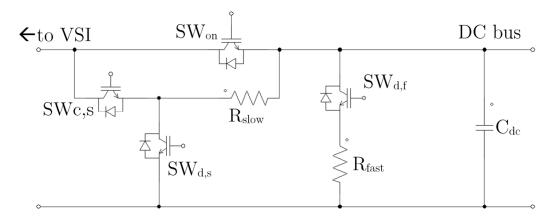

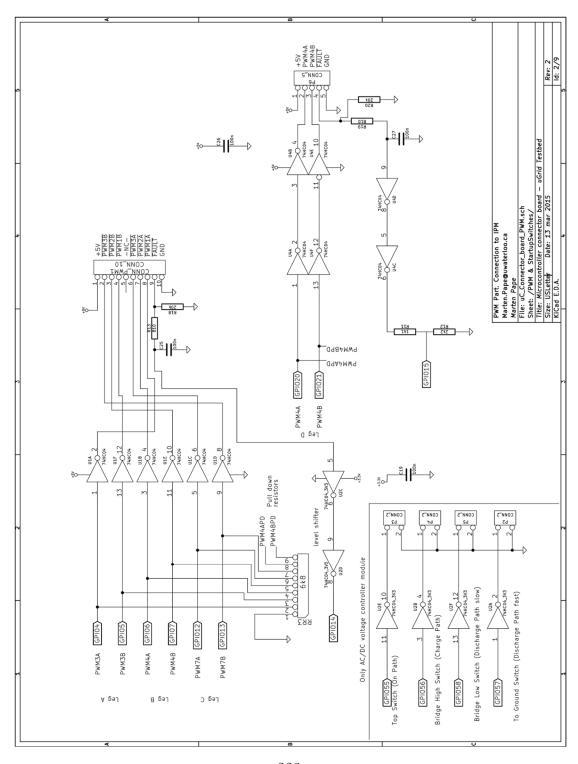

| Figure A.4 DC-bus charge/discharge circuit                                              | .206 |

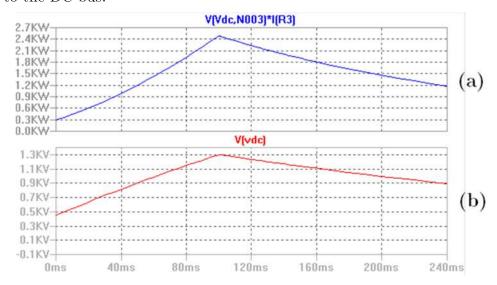

| Figure A.5 Rslow power consumption (a) and Vdc overshoot (b)                            | .209 |

| Figure A.6 Basic (ideal) circuit of a buck-boost converter                              | .211 |

| Figure A.7 Definition of $d1$ , $d2$ and $d3$ (example: inductor current discontinuous) | ous) |

|                                                                                         | .213 |

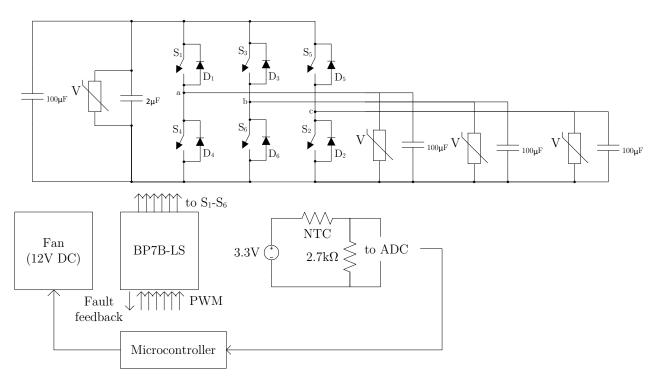

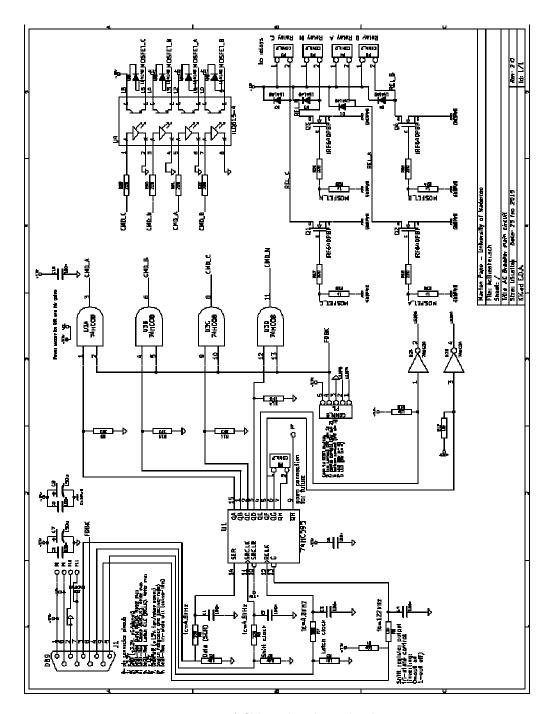

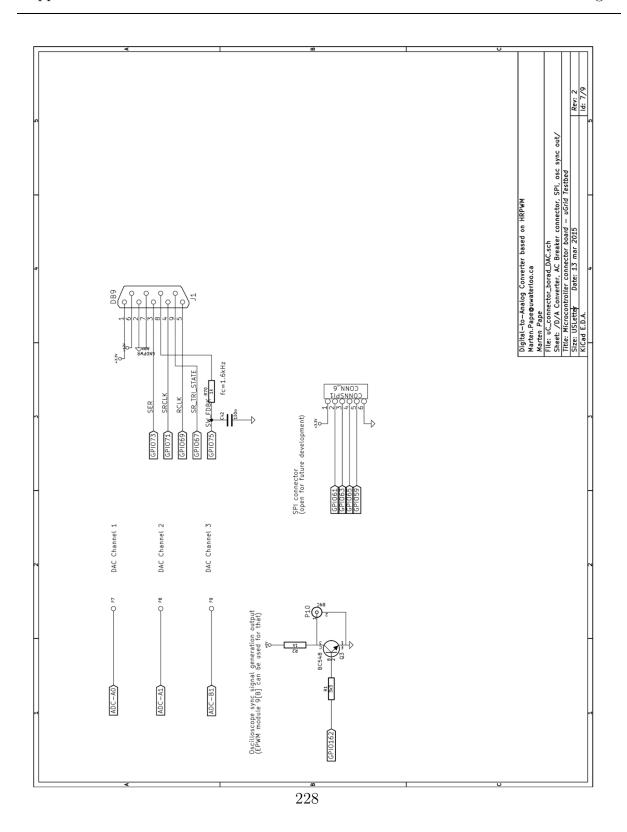

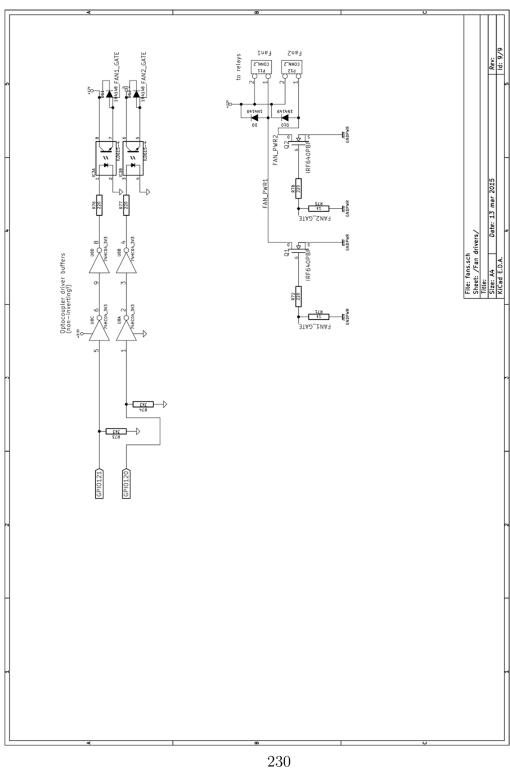

| Figure B.1 IPM circuit with snubbers, protection, temperature sensor, fan and PV        | WM   |

| control                                                                                 | .216 |

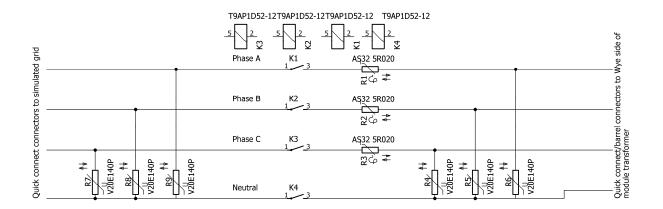

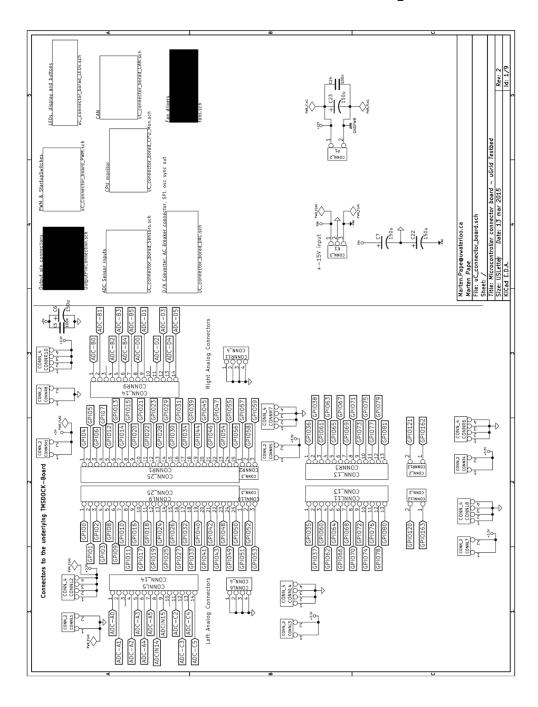

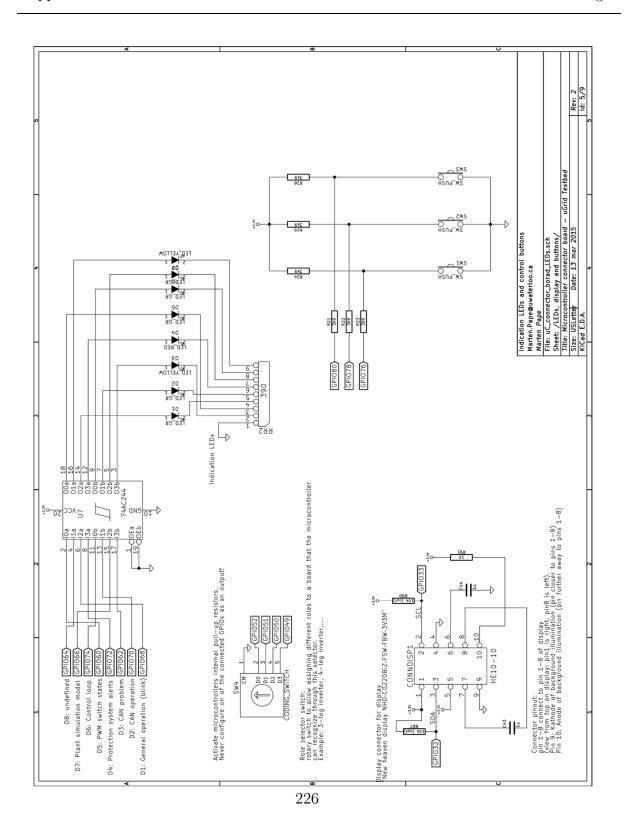

| Figure B.2 AC breaker power circuit schematic                                           | .217 |

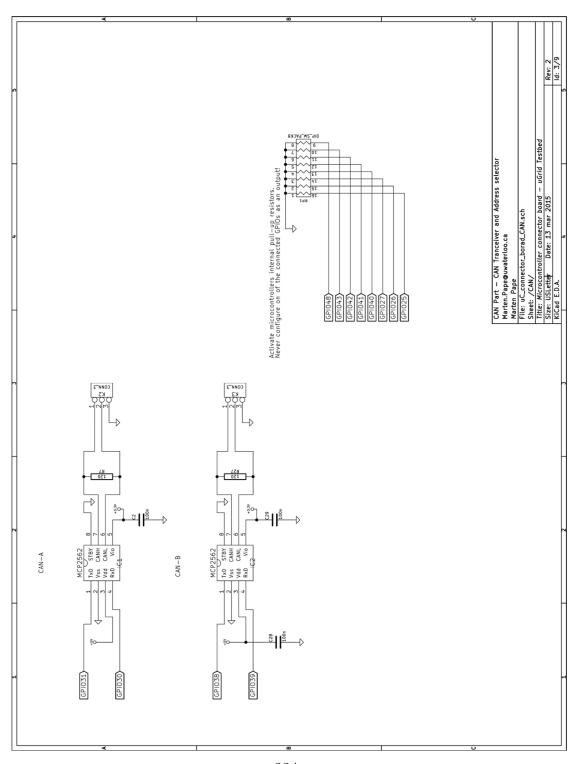

| Figure B.3 AC breaker board schematic                                                   | .218 |

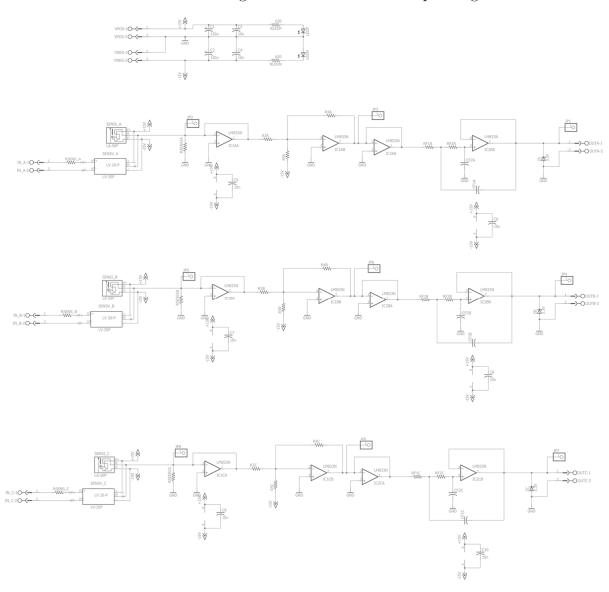

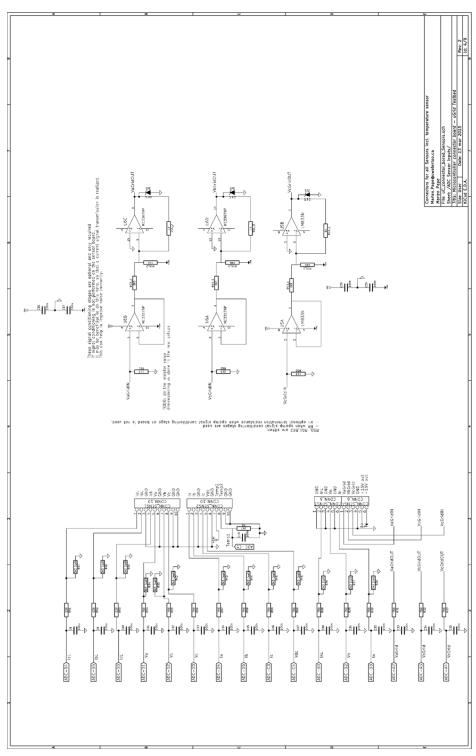

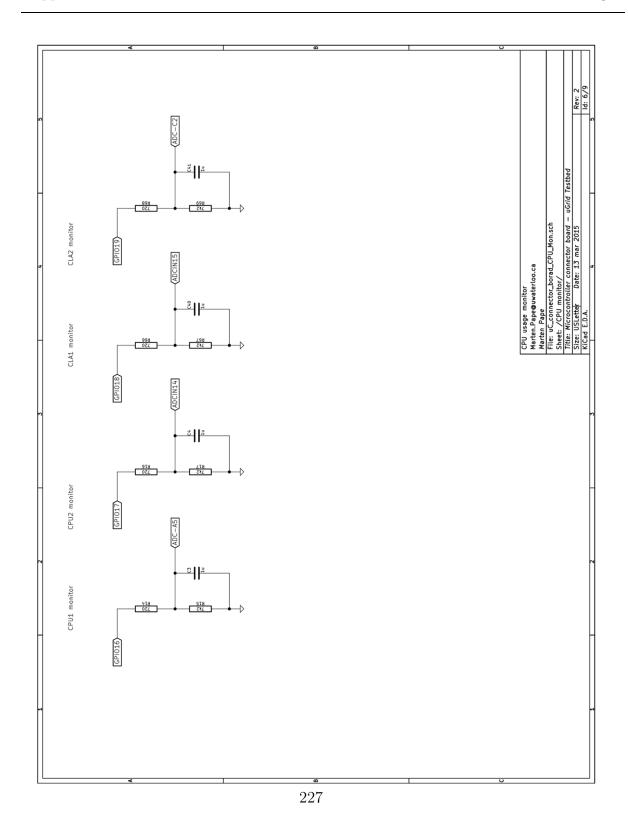

| Figure B.4 Three-phase sensor board, complete schematic                                 | .220 |

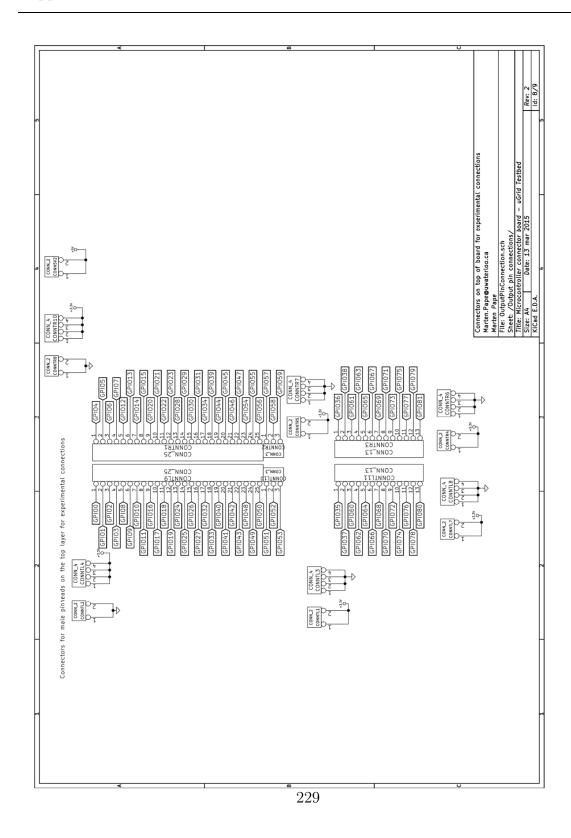

| Figure C.1 The TBCC main window with multiple modules online                            | .237 |

| Figure C.2 SimulationModuleUI (a) and DcBusModuleUI (b)                                 | .237 |

| Figure C.3 Example plot of a measurement of a PV plant variable                         | .238 |

| Figure C.4 Profile command display window with six commands loaded                      | .238 |

| Figure C.5 Configuration dialog for the voltage-source based droop controller (a),      | PV   |

| module parameter estimation after [63], [66] (b)                                        | .239 |

# List of Tables

| Table 4.1 Default   | parameterization of module's control loops                 | 70         |

|---------------------|------------------------------------------------------------|------------|

| Table 4.2 Total N   | Microgrid test bed cost (incl. DC-bus voltage controller n | nodule and |

| four simulation mod | ules)                                                      | 76         |

| Table 5.1 Parame    | eters of grid-following converter control loop topology    | 85         |

| Table 5.2 Simula    | tion load power references                                 | 86         |

| Table 5.3 Parame    | eters of voltage-source based droop controller topology    | 90         |

| Table 5.4 PQ loa    | d schedule                                                 | 92         |

| Table 5.5 Parame    | eters of current-source based droop controller topology    | 100        |

| Table 6.1 Nomen     | clature for PV cell model                                  | 108        |

| Table 6.2 Nomen     | clature for storage plant model                            | 118        |

| Table 7.1 Test be   | ed simulation configuration                                | 121        |

| Table 10.1 Load     | power references for test case 1                           | 172        |

| Table 10.2 ZIP lo   | oad configuration for presented test case                  | 180        |

| Table 10.3 PV m     | odel kev parameters                                        | 182        |

# Chapter 1

# Introduction

## 1.1 Motivation

### 1.1.1 Research on Microgrids

The last two decades in the electric power sector have been increasingly dominated by a rising interest in the integration of distributed energy resources (DERs) into electric power systems. Among DERs, many conversion types are based on renewable energy resources, such as photovoltaic energy conversion, wind power, geothermal energy or biomass. Increasing interest in the reduction of greenhouse gas (GHG) emissions and intensified research and innovation in the aforementioned conversion technologies have allowed for a wider-scale deployment, accompanied by declining deployment cost.

The traditional power system is dominated by a limited number of large-scale hydrothermal generation plants connected to transmission grids with customers typically connected to distribution grids. With the large-scale deployment of DERs, fundamental changes in the power system architecture become more relevant the higher the penetration levels of DERs become. DERs offer prominent advantages when placed close to the customer and can be scaled more efficiently in much wider ranges than is possible in the

case of large-scale hydro-thermal plants. As a result, there is an increasing need to integrate these distributed and small-scale resources into electricity grids with a reasonable system efficiency and system cost.

One way proposed for putting small-scale DERs into the heart of an electric power system is through realizing "Microgrids", a concept first introduced in [1], [2]. The initial definition for a Microgrid was given as: "A Microgrid is a cluster of micro-sources, storage systems and loads which presents itself to the grid as a single entity that can respond to central control signals" [1]. In contrast with the traditional setup of electric power systems, a Microgrid puts generation, storage and loads in potentially identical layers of grids reflecting the common deployment of DER unit in distribution grids. It can be operated in two modes: grid-connected and islanded. The grid-connected mode allows a Microgrid to interact with a main grid by using services of and providing services to the main grid at its point of common coupling (PCC). This is mostly interesting when applying the Microgrid concept to locations with already existing interconnected power systems. In the islanded mode of operation, this exchange of services with a main grid is not possible and a Microgrid has to provide all necessary services for a stable and efficient operation from within itself. Islanded operation can be intentional or unintentional. This capability can help to increase system reliability and resilience. It can also enable a larger-scale deployment of many DER units in stand-alone power systems, as used in remote communities, for example.

In order to ensure proper control of all relevant quantities in a Microgrid, various Microgrid control approaches have been proposed. Most notably, three categories can be defined: centralized control, decentralized control and hierarchical control.

"A fully centralized control relies on the data gathered in a dedicated central controller that performs the required calculations and determines the control actions for all the

units at a single point, requiring extensive communication between the central controller and controlled units. On the other hand, in a fully decentralized control, each unit is controlled by its local controller, which only receives local information and is neither fully aware of system-wide variables nor other controllers' actions" [3].

To mitigate some of these concepts' disadvantages, a combination of the aforementioned approaches has been established: hierarchical control. For Microgrids, three to four control hierarchy levels are commonly defined [4]. Level zero is concerned with local control of current and voltage of a single unit. The primary control level is realized in each generation unit employing droop-control methods or similar methods to control voltage and frequency in a stable manner at the PCC without relying on signals not locally available. The secondary control level can provide frequency and voltage restoration to nominal values, economical operation [3] and resynchronization to grid-connected mode. This level is typically implemented as a central controller. The tertiary control level then allows controlling power flow between the Microgrid and other interconnected (Micro-) grids.

The concept of Microgrids has the potential to enable a wide-scale deployment of renewable DERs at high penetration levels from a grid perspective, since it addresses all main operational issues with (renewable) DERs the power industry is facing today.

# 1.1.2 Test beds in research and development

Test beds are an essential tool in the development of new technical concepts and the refinement of existing methods. A test bed allows to conduct extensive, reproducible and transparent tests on a technical concept in pre-defined environments outside of an environment that could unintentionally cause harm to people or damage to equipment. Test beds can be used in many roles during a research and development process and even

after deployment of the developed technique. It becomes possible to verify a concept at full dynamic order on a system that (closely) replicates real environments and therefore unveils problems that might be hidden due to assumptions and simplifications induced by assumed model simplification. Test beds serve as demonstrators of concepts to technical and non-technical audiences and allow the verification of proper functionality of different concepts in a standardized environment or to verify a proper change of scope in the application of an existing concept. Lastly, test beds have also been used during the operation of a product to reproduce and examine incorrect behaviour in a safe environment observed during the product life cycle. For example, this is a common tool in space missions.

Since the Microgrid concept promotes a grid structure with fundamental differences with respect to the existing grid, with high initial and running cost and potential impact on the reliability of the electric power grid, there have to be extensive, flexible and high-quality test bed environments to advance techniques for the Microgrid environment. High complexity in proposed control architectures (level zero up to tertiary level) require a tool for testing, examination, verification and demonstration across multiple control hierarchies.

# 1.1.3 Required test environments for the advancement of Microgrids and its components

Matlab/Simulink, PSIM, Spice, PSCAD and PowerWorld are commonly used tools to replicate behaviour of grids at component and system levels in software. These tools allow a fast implementation and reconfiguration of the test environment at very low cost. Therefore, these tools are among the most popular ways to test and support developing

new concepts. However, software tools come with certain limitations. Simulation of components or systems is based on the model representation of the sub-components used in a system. These models are often subject to a trade-off between accurate replication of reality in all relevant environments, model complexity and execution speed. Limitations arise when both, the system complexity and the level of simulation details is high, available computational power is limited, the description of reality with models cannot be accurately achieved enough or too many uncertainties exist. Finally, proving the full viability of a concept becomes easier and more credible the closer the simulation is to a real case.

To mitigate previously mentioned disadvantages of software-based simulation, hard-ware-based test beds¹ are being used. These simulators allow the replication of test cases in an environment that is exactly the same as or very close to a production environment. Test beds can show the full system dynamics at real-time and high system complexity without being (much) reliant on model representations of reality. Test beds allow verification of basic assumptions in developed concepts and modeling applied in software-based simulations. They can be a natural evolution from software models towards a final product or concept. However, test beds for electricity grids tend to be costly, large in size and weight, and limited in the ability to reconfigure the test-setup. The development of a test bed can bind many resources and take an incomparable long time compared to software-based simulators.

Therefore the goal of this thesis is to develop a test bed usable in the research on Microgrid systems and Microgrid components that is:

1. Easily reconfigurable and expandable

<sup>&</sup>lt;sup>1</sup> From now on just referred to as "test beds"

- 2. Low in construction and operation cost

- 3. Able to capture the full system dynamics for Microgrid operation relevant topics from as small as power electronic switching events to as high-level as Microgrid power exchange.

More specifications on this goal, basic assumptions and limitations are given in section 1.4.

# 1.2 Background information

### 1.2.1 Hardware-in-the-loop

The hardware-in-the-loop (HIL) concept is relatively new, allowing for fast but close-to-reality test methods by combining software-based simulations with selected hardware-based simulations. The principle is to run real-time simulations in software, where accurate and good models exist, and include a hardware stage into the simulation, where models are inaccurate, hard to obtain or very complicated [5]. A software simulator interfaces a hardware-based device under test (DUT) using digital-to-analog converters and sensors for the return path (Figure 1.1). To test a controller performance, the concept of controller hardware-in-the-loop (CHIL) can be applied. In this case, a controller would be executed in the loop with a software model. More interestingly, to test power hardware equipment together with software models in real-time, power hardware-in-the-loop (PHIL) can be applied. In PHIL, the interface is supplemented with a power amplifier stage to provide the required output power needed to realize quantities from within the software model on the power device under test [6].

Figure 1.1 General HIL, Controller HIL and Power HIL (left to right) [6]

Special considerations in HIL tests have to be made on the hardware interfacing software and DUT. Digital-to-analog converters and sensors with an infinite bandwidth, resolution, accuracy and output power and zero noise do not exist. Non-ideal sensors and sensor interfaces can introduce errors into the simulation that are significant to the simulation results. Especially in PHIL simulations, the power interface - typically consisting of linear power amplifiers and power sensors - can introduce significant delays into the system, affecting stability and controller configurations [5]. Proper selection of the interfacing signals is therefore critical to the simulation performance.

# 1.3 Existing test bed approaches

Many Microgrid test beds have already been implemented around the world. Some test beds are designed as research and development tools; others are more focused on demonstration and validation purposes[7]–[18]. Most setups employ commercial products, such as photovoltaic plants, wind turbines, gas generators, battery or flywheel storage systems, fuel cells or diesel generators. These approaches offer the closest simulation of real scenarios in many terms, since no model abstractions are employed. Since all parts of a

Microgrid are realized with components used in production environments, all pending issues either have to be overcome or will appear while implementing such a test bed. Power ratings of the generators used are often in the range of 10s to 100s of kilowatts. For example, British Columbia Institute of Technology's Microgrid test bed employs two 5kW wind turbines, 300kW of photovoltaic models, thermal generation of 250kW and 550kWh of battery storage [19]. This sizing allows good estimations on project cost and specific restrictions with high-voltage, high-power components.

However, the size and cost of these components are remarkable for research and development projects and do not allow for a very wide-spread deployment of these testing facilities. For example, the cost for a Microgrid application project of comparable size has been reported to be at about \$US 15 million [20]. Furthermore, test beds that use real generators for renewable energy sources are dependent on the availability of primary energy, such as solar insolation or wind, which makes these test beds weather-dependent. This heavily impacts the reproducibility of simulations. For all setups using real generators, it is also true that the operating cost of such a test bed is considerable since all the energy that is circulated in the test bed is consumed by dummy loads.

Finally, the network layout used to implement a Microgrid test bed is often fixed ([11]–[14], [17], [18]). While this allows to perform case studies on specific similar grid setups, achieving generalized tests and comparability between different setups is difficult to achieve. For example, this is the case for the CERTS Microgrid test bed installed near Columbus, Ohio, United States. The feeders of this setup incorporate multiple feeder loops to simulate the impedance of long feeders [21].

To overcome the disadvantages of large size, high initial cost, limited flexibility in grid, load and generator configurations and dependence on environmental conditions for reproducibility, a test bed based on the hardware-in-the-loop concept has been proposed

and implemented [22]. This test bed consists of a set of voltage source inverters, a battery bank, resistive loads, a bus bar matrix and a main grid connection. The computation of generator control algorithms and generator dynamics (wind, solar...) is performed in software whereas the grid and the power stage of grid interfaces, based on voltage-source inverters (VSI), is implemented in hardware. This concept adds the flexibility to simulate a Microgrid with a flexible selection of generators, such as diesel generators, photovoltaic plants or wind turbines. Reconfiguration only requires an exchange of software models. This setup widely overcomes the aforementioned disadvantages with conventional Microgrid test beds, adding significant flexibility to the simulation platform and reducing cost. However, this test bed still employs some real components, such as resistive load banks and a battery system. This means that some of the energy circulated in the test bed to simulate a scenario is still consumed and has to be paid for. According to [23], in this setup, it is necessary to select two AC/DC converters to form a back-to-back converter configuration in order to allow active power absorption from the simulated grid. This case would be required when modeling loads, storage-equipped DERs or pure storage devices using VSI modules. Furthermore, no implementation of grid impedance representation has been reported.

# 1.4 Microgrid test bed goal definition

The goal of this thesis is to develop a flexible, simple, laboratory size research tool to provide a scalable Microgrid hardware simulation for islanded operation.

A finished test bed should provide primary simulation capabilities for:

1. Grid interface controllers. "Component-level scope". Various methods of controlling currents, voltages and power injection by a generator exist for many

purposes. A detailed study of these controller topologies should be possible without simplifications.

2. Management of Microgrid components. "System-level scope". Secondary and tertiary control levels in a Microgrid are about the management of many participants in a Microgrid. Interfaces for implementing user-defined algorithms should be available.

The simulation of generator characteristics in software models should be as accurate as required to produce correct behavior on the AC terminals of a simulated generator.

Furthermore the following topics are to be considered in the design of this test bed:

- 1. Ability to connect other components to the test bed. This can allow studies on controller design, controller topology compatibility and grid-interfacing power electronic converter design

- 2. Ability to combine various grid interfacing mechanisms with different generator models. Research on Microgrids has stimulated innovations in control algorithms for grid-connected inverters. It is of interest to provide this ability to study technical and economic feasibility of various control algorithms on different kinds of generation.

Compared to the goal definition for a finished test bed, this thesis assumes certain simplifications:

1. All Microgrid generators and loads connect to a single PCC, no network impedances and layouts are considered

2. Grid interface control algorithms assume a balanced grid. Single-phase operation is to be prepared in hardware, but not fully implemented in software and grid interface control topologies

Therefore, this thesis presents a Microgrid test bed platform based on the hardware-in-the-loop concept. It provides four VSI modules ("simulation modules") of identical design to provide an AC terminal representation of various grid components. These components are a load emulation, a photovoltaic plant emulation and generic storage modules. However, the platform is designed in a way that allows the implementation of a much wider range of plant models and grid interfaces. Each simulation module is rated at 5kVA and standard North American low-voltage distribution system voltages. This test bed reduces the hardware complexity required for the HIL simulation compared to [22], [23], increases flexibility by providing a common DC-bus for all simulation modules and removes all resistive loads and storage batteries through software emulation, which reduces the amount of energy required for a Microgrid simulation.

Software in simulation modules and on a central control computer allows the complete reconfiguration of all major parameters in the Microgrid, including selected generator models and grid interfacing algorithms.

# 1.5 Thesis organization

In the following chapters, different aspects are presented that are required to design, implement and test the proposed Microgrid test bed.

Chapter 2 introduces key concepts that are required for the realization of this test bed. Some technological choices are made in this chapter, as well.

Chapter 3 deals with the overall system structure of the proposed test bed and defines key requirements for it. In Chapter 4, the focus is on the structure and design of a 'simulation module' which represent one Microgrid participant, such as a generator or a load. Chapter 5 presents the control of these simulation modules with respect to their Microgrid AC-bus connection. All control topologies are verified in simulation, with experiments on them following later in Chapter 10.

In Chapter 6 modeling of generators and loads is given that is finally used in the software controlling each simulation module.

The test bed design phase is concluded with computer simulations of the entire test bed on a 24 hour load and generation profile in Chapter 7.

Chapter 8 and Chapter 9 discuss implementation-specific issues in the software used to control the test bed (central control) and single simulation modules. The focus is to give the overall design requirements and approaches.

Finally, Chapter 10 presents experimental results from the actual test bed to verify proper design and implementation.

Chapter 11 and Chapter 12 close this thesis with conclusions and recommendations for future work.

# Chapter 2

# Background review

# 2.1 Common converter topologies for low-voltage grid applications

This thesis requires multiple self-commuted power conversions from a single DC-bus to a three-phase AC-bus with bi-directional power flow at line voltage levels. The two most common topologies to achieve this conversion are the two-level voltage source inverter (VSI) and the three-level current-source inverter (CSI) [24].

### a. Voltage-source inverters

A voltage-source inverter, as shown in Figure 2.1, is based on unidirectional switching devices with antiparallel diodes. On the DC side, a capacitor buffers an ideally constant DC voltage. At any time, only one switch per leg can be on to avoid a shoot-through and resulting destruction of the switches due to high capacitive discharge currents. Using the concept of sinusoidal PWM (SPWM) or space vector modulation (SVM), three-phase voltages with fundamental sinusoidal components of desired magnitude and frequency (much lower than switching frequency) can be produced at points a, b and c in Figure 2.1 [24], [25]. For grid applications, this fundamental frequency is normally 50Hz or 60Hz.

Figure 2.1 Three-Phase voltage-source inverter topology

For SPWM, three control signals are produced:

$$\begin{split} v_{ctrl,a} &= m_a \sin(wt) \\ v_{ctrl,b} &= m_a \sin\left(wt - \frac{2\pi}{3}\right) \\ v_{ctrl,c} &= m_a \sin\left(wt + \frac{2\pi}{3}\right) \end{split} \tag{2.1}$$

where  $m_a$  is the modulation index, defined as  $m_a = \frac{\hat{V}_{control}}{\hat{V}_- tri}$ . The modulation index is in the range of [0,1] for linear modulation with the lowest amount of unwanted components in the frequency spectrum. A PWM signal is generated by comparing a triangular waveform of amplitude  $\hat{V}_{tri}$  with the control signals  $v_{ctrl,a}$ ,  $v_{ctrl,b}$  and  $v_{ctrl,c}$ . The resulting fundamental components of output voltages will be

$$\begin{split} v_{aN_1} &= m_a \frac{V_i}{2} \sin(\omega t) \\ v_{bN_1} &= m_a \frac{V_i}{2} \sin\left(\omega t - \frac{2\pi}{3}\right) \\ v_{cN_1} &= m_a \frac{V_i}{2} \sin\left(\omega t + \frac{2\pi}{3}\right) \end{split} \tag{2.2}$$

Low-pass filters (L, LC or LCL) are then a common tool to reduce the amount of higher order harmonics in the output currents and voltages.

Another technique, SVM is based on the approach to generate typically balanced, three-phase output voltages that are on average equal to the desired output voltage vectors for  $v_{aN_1}$ ,  $v_{bN_1}$  and  $v_{cN_1}$  [24]. This technique offers a slight improvement in the trade-off between power quality, switching frequency and switching losses. Hardware support in common microcontrollers is significantly better for (S)PWM methods, however.

Manufacturers, such as Mitsubishi/Powerex and IXYS offer a wide range of integrated 3-phase VSI bridges, called "intelligent power modules" (IPM). These modules not only include the IGBT switches and anti-parallel diodes, but also integrated gate drive circuitry and overloading protection schemes (overcurrent, over-temperature, etc.). This allows a faster development of inverters, offers more reliability in the development process and provides more protection against device destruction which is very valuable in a testing environment that is likely to experience severe overloads, transients and faults during experiments.

#### b. Current-source inverters

The current-source inverter, as shown in Figure 2.2, is the dual of the voltage-source inverter. The operating principle is that a PWM or SVM scheme controls the flow of the DC-side current between to output terminals of three legs. Therefore a CSI requires a stable and controlled DC-bus current. Each CSI leg is composed of a unidirectional switch and a series blocking diode. A capacitive output filter filters current harmonics to provide a high quality output voltage waveform. According to [24], this configuration is most favorable in medium voltage industrial applications. The major advantage of a CSI is that the output is a controlled current, instead of a controlled voltage. VSIs are

often operated with inner current control loops to provide a controlled output current at their innermost loop. CSIs provide this feature by design, without the introduction of controller delays. Furthermore, AC-side faults are potentially easier to handle because of the limited current that can be provided from the DC side. However, CSIs have higher conduction and switching losses due to series diodes in each leg and a DC-bus current that is always flowing.

There are significantly less 3-phase CSI bridge products available than for VSIs. This often results in the need to build discrete 3-phase CSI bridges which voids all advantages provided through VSI-IPMs. Also, most research and development currently focuses on the use of VSIs due to their wide spread. For these reasons, the CSI is not considered, further.

Figure 2.2 Current-source inverter

#### c. Other topologies

For higher voltage and power levels, multi-level converters have become popular in order to improve the trade-of between power quality, converter size, efficiency and cost. Since for this test-bed conversion efficiency is of lower concern and converter complexity

increases with multi-level converters, the voltages are at lower levels these are not considered further.

#### 2.2 Converter output filter for grid-connected VSI

Power filters are commonly used in the interface between PWM controlled converters and electricity grids in order to reduce the grid injection of current and voltage components at multiples of the converter switching frequency. Three different basic filter topologies are known that are depicted in

Figure 2.3 - Figure 2.5 as single phase representations [26].

Figure 2.3 L-filter

Figure 2.4 LC-filter

Figure 2.5 LCL-filter

An L-filter is the simplest filter for this application that provides an attenuation of -20dB/decade for current harmonics. A high switching frequency is therefore required in order to keep inductors at a small size and the control dynamics fast.

An LC-filter provides an attenuation of -40dB/decade. It is relatively easy to design, but a resonance at  $f_{res}=\frac{1}{2\pi}~\sqrt{\frac{1}{L_fC_f}}$  can cause waveform distortions. The filter transfer function is

$$F_{LC}(s) = \frac{1}{s^2 L_f C_f + s L_f + 1} \tag{2.3}$$

Real or virtual damping can reduce the resonance effects of this filter ([27]).

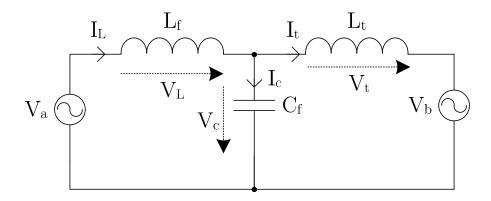

The LCL-filter adds another inductor to the filter setup, providing an effective attenuation of -60dB/decade. This filter setup allows further improvement of the trade-off between filter component size, control dynamics and switching frequency. Filter design of such filters is often complicated due to the interaction of  $L_t$  with other grid impedances that can cause variable resonant frequencies [28]. Often, LC filters indirectly become LCL filters because of the leakage inductance of an isolation transformer that is used to connect an inverter to the grid. Due to the high ripple contents in  $i_l$ , transformers are commonly not used as replacements for  $L_f$ .

#### 2.3 Control objectives for grid interfacing converters

The generation of  $v_{ctrl}$  signals for a VSI is typically done by closed loop control. Depending on the requirements on the role of a VSI in the grid, different control loops can be used. A common classification of converters in AC Microgrids has been provided by [29] and is presented in this section. According to this publication, the role of a power converter can be one of the following three kinds: grid-forming, grid-supporting and grid-following.

#### 2.3.1 Grid-forming converters

The role of a grid-forming power converter is to provide stable frequency and voltage references to the Microgrid, mimicking a slack bus. It can be modeled by a controlled voltage source with a series connection impedance, as shown in Figure 2.6. This role provides one way to operate a Microgrid in islanded mode and perform a resynchronization to grid-connected mode. It must be noted that this role has strong requirements on the active and reactive power capabilities of the used grid interface and generation plant.

Figure 2.6 Grid-forming controller representation

#### 2.3.2 Grid-feeding / grid-following converters<sup>2</sup>

A grid-feeding converter can be modeled as a current source with a parallel impedance connected to an AC Microgrid bus, as depicted in Figure 2.7. A controller controls active and reactive power injection into this bus based on local measurements of injected current, bus voltage level and bus frequency. The role of this converter representation is to inject a predetermined amount of active and reactive power into the local bus, without active participation in voltage or frequency control. For example, this is commonly used

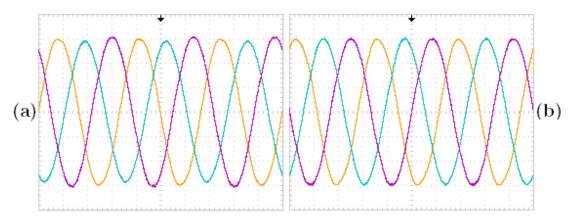

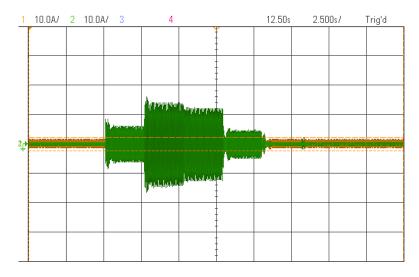

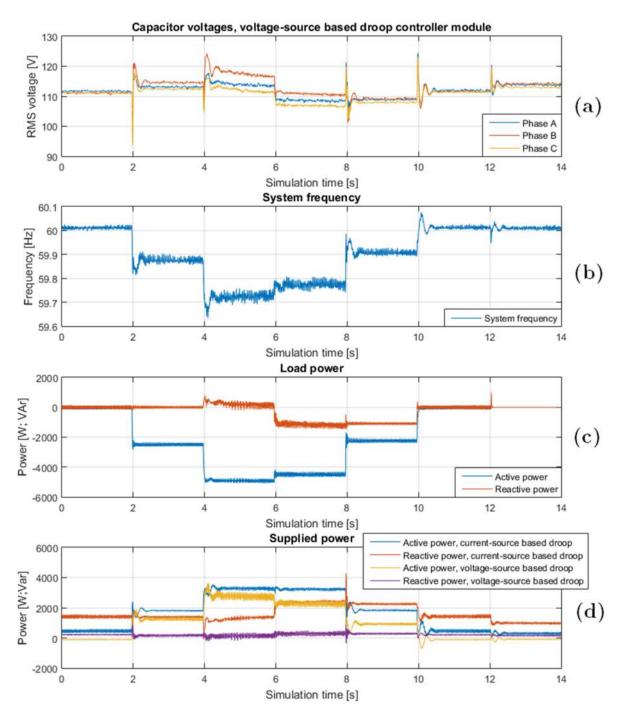

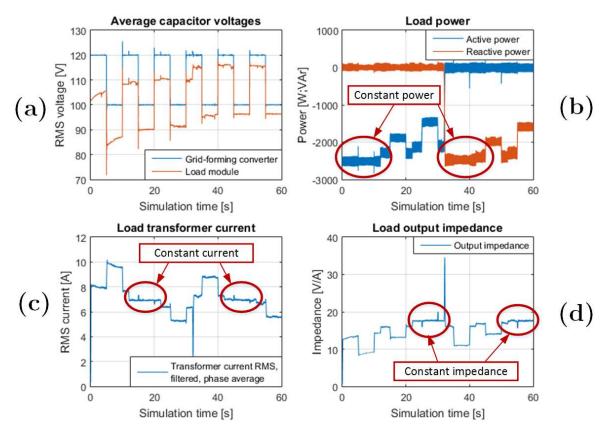

$<sup>^2</sup>$  The terms "grid-feeding converter" and "grid-following converter" are used interchangeably in this thesis.